ASIX AX88655P Datasheet

AX88655 P

5-Port 10/100/1000BASE-T Ethernet Switch

5-Port Gigabit Ethernet Switch with Embedded Memory

Document No.: AX88655-1.0 / V1.0 / Mar, 12,2002

Features

• 5-Port Gigabit Ethernet switch integrating MACs,

packet buffer memory and switching engine with

GMII/MII interface

• Full Duplex 1000 Mbit/s.

• Full and Half Duplex 10/100 Mbit/s

• Supports auto-sensing or manual selection for

speed and duplex capability with an embedded

MPU

• Store-and-forward operation support

• Performs full wire-speed switching with no HOL

blocking

• Broadcast storm control

• Quality-of-Service provisioning on 802.1P tag and

port-pairs with two priority queues

• Embedded 128K Byte SRAM for packet buffer

Product Description

The AX88655 is a 5-Port 10/100/1000 Mbps Ethernet switch with GMII or MII Interface. The switch controller

provides network system manufacturers the ideal platform for building smart and cost-effective backbone switches for

small to medium sized businesses.

The AX88655 5-Port 10/100/100 BASE-T single chip switch controllers combine the benefits of network simplicity,

flexibility and high integration. Its highly integrated feature set enables network system manufacturers to build smart

switches for the fast-growing small to medium business market segment.

Benefits of AX88655 Switches are below.

Ø Simplicity

Provides a smart, simple and low maintenance plug-and-play network interconnect system for small to

medium size businesses

Ø Flexibility

Highly scalable configuration allows system manufacturers to enable or disable a range of features to best meet

their target price point

Ø Integration

Highly integrated design drives down overall switch manufacturing costs.

Target Applications

ü 5-Port Gigabit Layer 2 Switches for workgroup

ü High-port count Layer 2 switches with trunking

ü High performance solution of Ethernet backbone

• Integrated two-way Address-Lookup engine and

table for 4K MAC addresses

• Programmable aging mechanism for the two-way

4K MAC addresses table

• Full-duplex IEEE 802.3x flow control

• Half-duplex back pressure flow control

• Port trunking for high-bandwidth links

• Provides 5 GPIO ports

• Provides EEPROM interface for auto-configuration

• System clock input is one 27MHz Crystal and one

125MHz Oscillator

• 2.5 and 3.3V operations

• 3.3 I/Os and packaged in 256-pin PQFP

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify the product specification without notice. No

liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

ASIX ELECTRONICS CORPORATION First Released Date: 01/31/2002

4F, NO.8, Hsin Ann Rd., Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

TEL: 886-3-579-9500 FAX: 886-3-563-9799 http://www.asix.com.tw

Always contact ASIX for possible updates before starting a design.

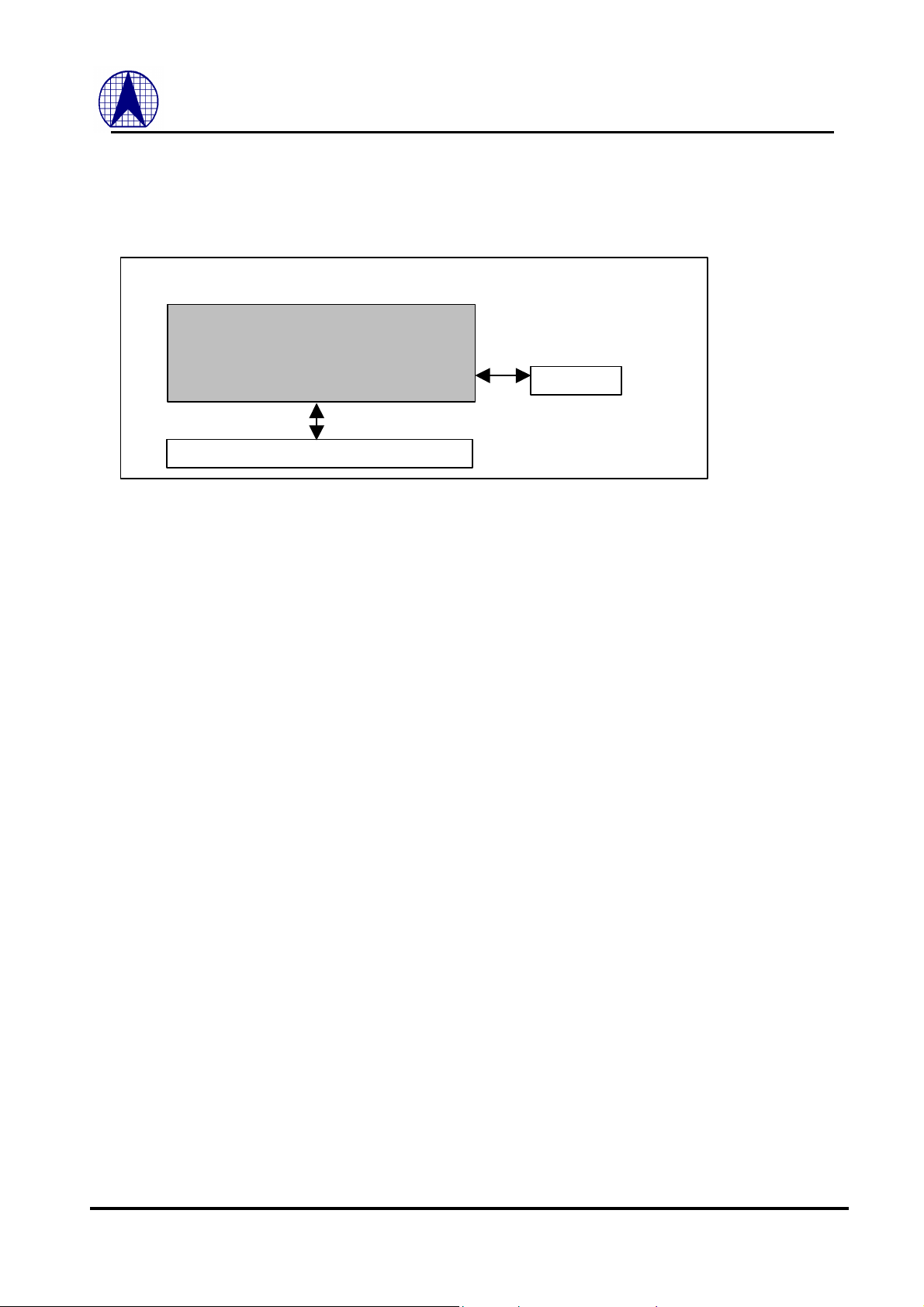

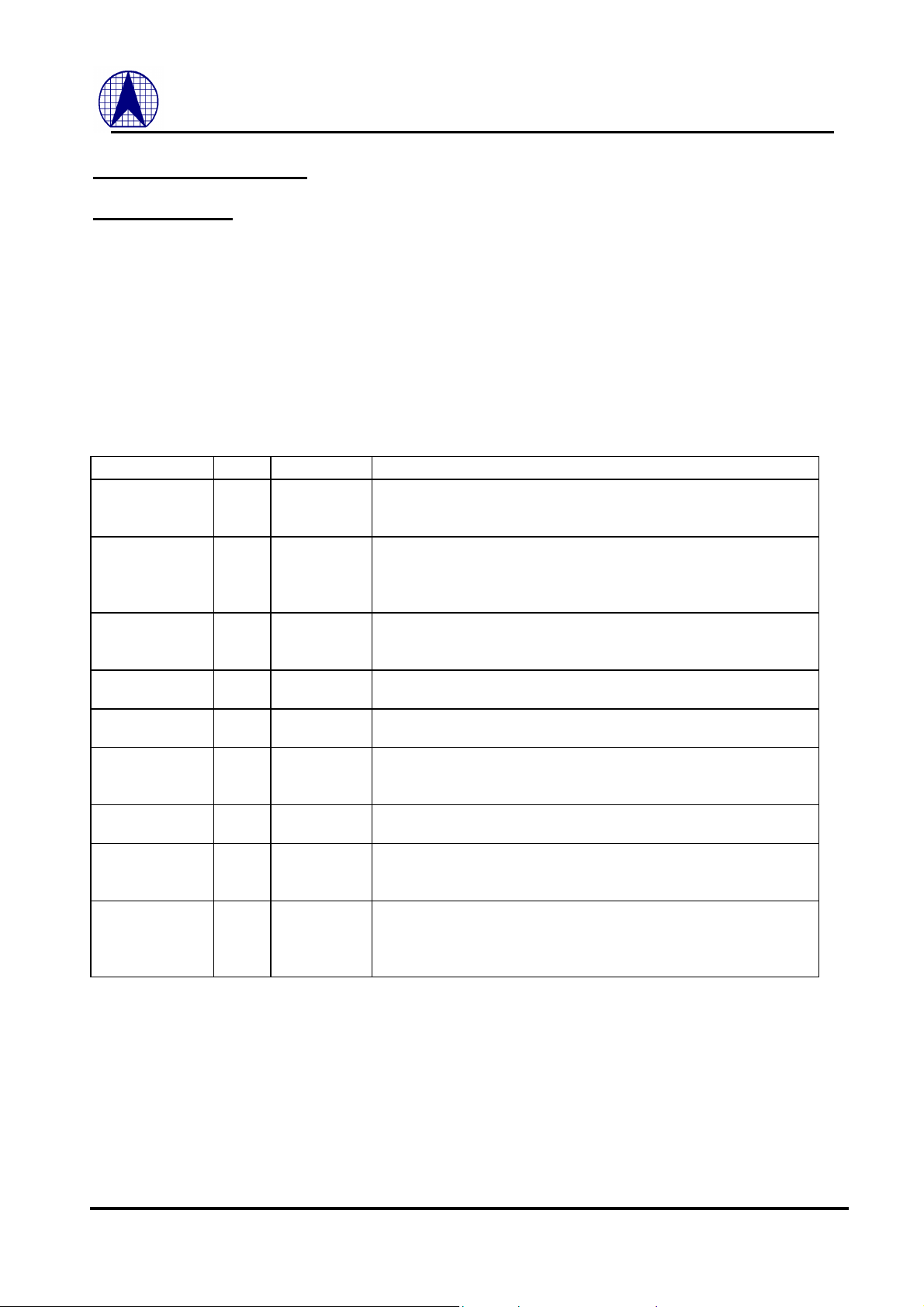

System Block Diagram

Switch Controller

5 * 10/100/1000 Mbps PHYs

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

AX88655P

EEPROM

2

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

CONTENTS

1.0 AX88655 OVERVIEW............................................................................................................. 6

1.1 GENERAL DESCRIPTION ..................................................................................................................... 6

1.2 AX88655 BLOCK DIAGRAM................................................................................................. 6

1.3 PIN CONNECTION DIAGRAM............................................................................................................. 7

2.0 I/O DEFINITION ............................................................................................................................................... 8

2.1 GMII/MII INTERFACE ........................................................................................................................ 8

2.1.1 GMII Interface Port 0 ................................................................................................................................ 8

2.1.2 GMII Interface Port 1 ................................................................................................................................ 9

2.1.3 GMII Interface Port 2 ................................................................................................................................ 9

2.1.4 GMII Interface Port 3 ................................................................................................................................ 9

2.1.5 GMII Interface Port 4 .............................................................................................................................. 10

2.2 MISCELLANEOUS................................................................................................................................. 10

3.0 FUNCTIONAL DESCRIPTION................................................................................... 12

3.1 INTRODUCTION..................................................................................................................................... 12

3.2 PACKET FILTERING AND FORWARDING PROCESS................................................................. 12

3.3 MAC ADDRESS ROUTING, LEARNING AND AGING PROCESS.......................................... 12

3.4 FULL DUPLEX 802.3X FLOW CONTROL..................................................................................... 12

3.5 HALF DUPLEX BACK PRESSURE CONTROL.............................................................................. 12

3.6 MII POLLING......................................................................................................................................... 12

3.7 PORT-BASED QOS: PORT-PAIR ................................................................................................... 13

4.0 REGISTER DESCRIPTIONS......................................................................................... 14

4.1 REGISTER 00.................................................................................................................................................... 14

4.2 REGISTER 01.................................................................................................................................................... 14

4.3 REGISTER 02.................................................................................................................................................... 14

4.4 REGISTER 03.................................................................................................................................................... 15

4.5 REGISTER 04.................................................................................................................................................... 15

4.6 REGISTER 05.................................................................................................................................................... 15

4.7 REGISTER 06.................................................................................................................................................... 15

4.8 REGISTER 07.................................................................................................................................................... 15

4.9 REGISTER 08.................................................................................................................................................... 15

4.10 REGISTER 09.................................................................................................................................................. 15

4.11 REGISTER 0A................................................................................................................................................. 15

4.12 REGISTER 0B................................................................................................................................................. 16

4.13 REGISTER 0C................................................................................................................................................. 16

4.14 REGISTER 0D................................................................................................................................................. 16

4.15 REGISTER 0E ................................................................................................................................................. 16

4.16 REGISTER 0F.................................................................................................................................................. 17

4.17 REGISTER 10.................................................................................................................................................. 17

4.18 REGISTER 11.................................................................................................................................................. 18

4.19 REGISTER 12.................................................................................................................................................. 18

4.20 REGISTER 13.................................................................................................................................................. 18

4.21 REGISTER 14.................................................................................................................................................. 18

3

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

5.0 ELECTRICAL SPECIFICATION AND TIMING..................................... 19

5.1 ABSOLUTE MAXIMUM RATINGS................................................................................................... 19

5.2 GENERAL OPERATION CONDITIONS............................................................................................ 19

5.3 DC CHARACTERISTICS..................................................................................................................... 19

5.4 AC SPECIFICATIONS........................................................................................................................... 20

5.4.1 X_IN Signal Timing.................................................................................................................................. 20

5.4.2 Reset Signal Timing ................................................................................................................................. 20

5.4.3 GMII Transmit/Receive Signals Timing.................................................................................................... 21

5.4.4 100 Mbps MII Transmit/Receive Signals Timing ...................................................................................... 22

5.4.5 10 Mbps MII Transmit/Receive Signals Timing ........................................................................................ 23

6.0 PACKAGE INFORMATION.......................................................................................... 25

APPENDIX A: SYSTEM APPLICATIONS............................................................... 26

A.1 AX88655 AS 5-PORT SOHO HIGH TRAFFIC POWER USER SWITCH ...................................................................... 26

A.2 AX88655 AS 5-PORT SMART SWITCH (DIP SWITCH CONFIGURABLE)................................................................. 26

A.3 AX88655 FOR 10/100MBPS ETHERNET BACKBONE.......................................................................................... 27

A.4 AX88655 FOR SUPER SERVER TRUNKING APPLICATION.................................................................................... 27

APPENDIX B: DESIGN NOTE.............................................................................................. 28

B.1 USING MII I/F CONNECTS TO MAC.................................................................................................................. 28

APPENDIX C: WEIGHT SETTING FOR QOS..................................................... 29

DEMONSTRATION CIRCUIT (A) : AX88658 SMART SWITCH... 30

4

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

FIGURES

FIG-1 AX88655 BLOCK DIAGRAM...........................................................................................................6

FIG-2 AX88655 PIN DIAGRAM................................................................................................................... 7

5

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

1.0 AX88655 Overview

1.1 General Description

The AX88655 Gigabit switch controller supports five 10/100/1000 Mbps ports in wire-speed operation. The AX88655

Gigabit switch controller provides five 10/100/1000 Ethernet ports with GMII/MII interface. For each ports, the

AX88655 supports GMII (802.3ab) interface with full-duplex operation at Gigabit speed, full- or half-duplex operation

at 10/100 Mbps speed and polls the status of PHYs with an embedded MPU.

Embedded 128K bytes SRAM as a packet buffer operates with an internal 90MHz clock. For efficient utilization of the

packet buffer, there are 1024 128-byte page-links totally in the buffer.

The device supports 4K internal MAC addresses which are shared by all ports with an embedded 32K byte SSRAM. The

learning/routing engine is implemented with a two-way hash/linear algorithm to reduce possibility of routing collision.

Basically the AX88655 supports non-blocking wire speed forwarding rate and no Head-of-Line (HOL) blocking issue.

The AX88655 provides two flow-control mechanisms to avoid loss of data: an optional jamming based backpressure flow

control in the half-duplex operation and IEEE 802.3x in the full-duplex mode.

To support Quality of Service (QoS), each output port has two priority queues and their assignment can be based on the

802.1p priority field or Port-Pair setting. Each output port retrieves the frames from the shared buffer based on queuing

and sends them to the transmitting (Tx) FIFO.

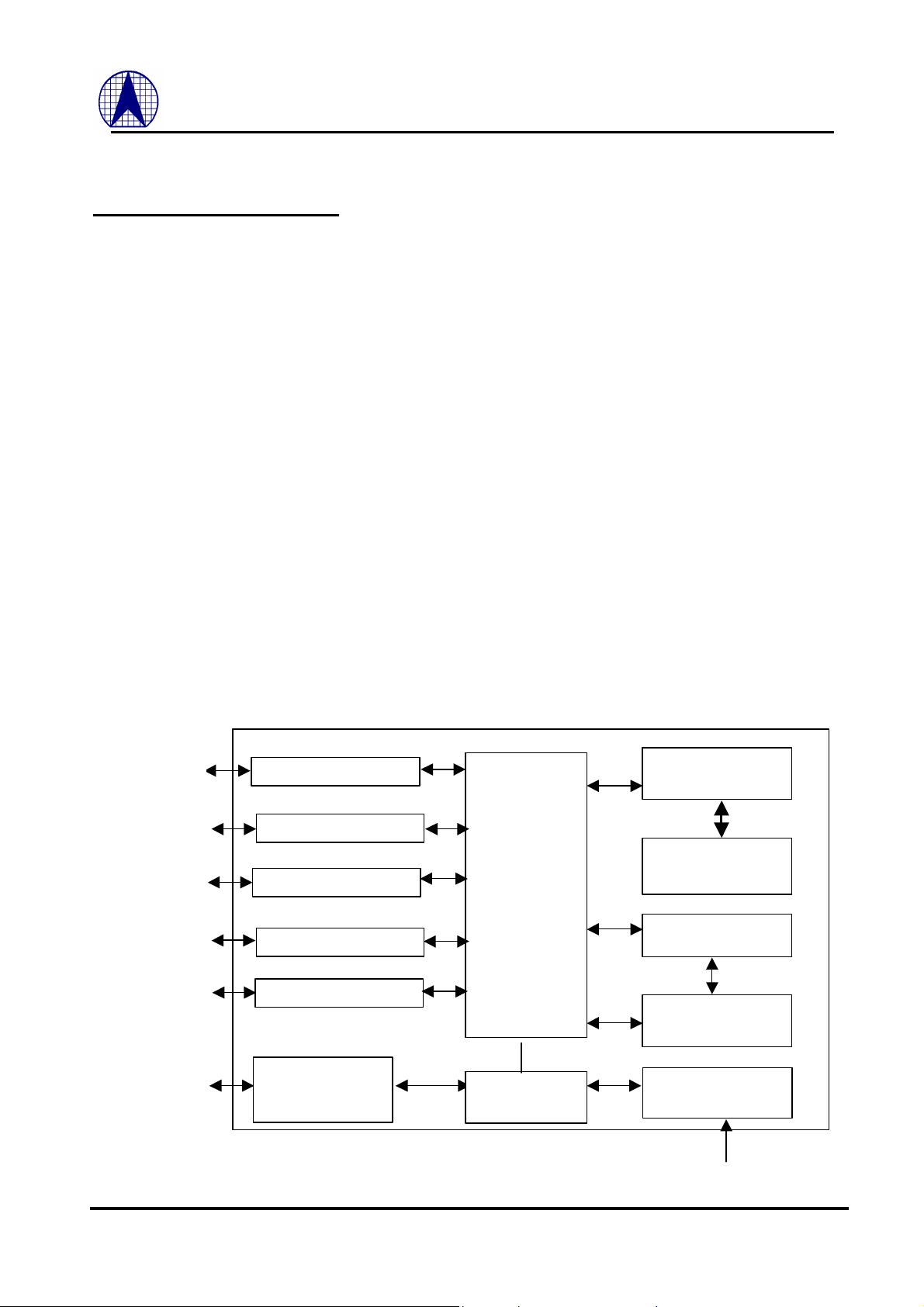

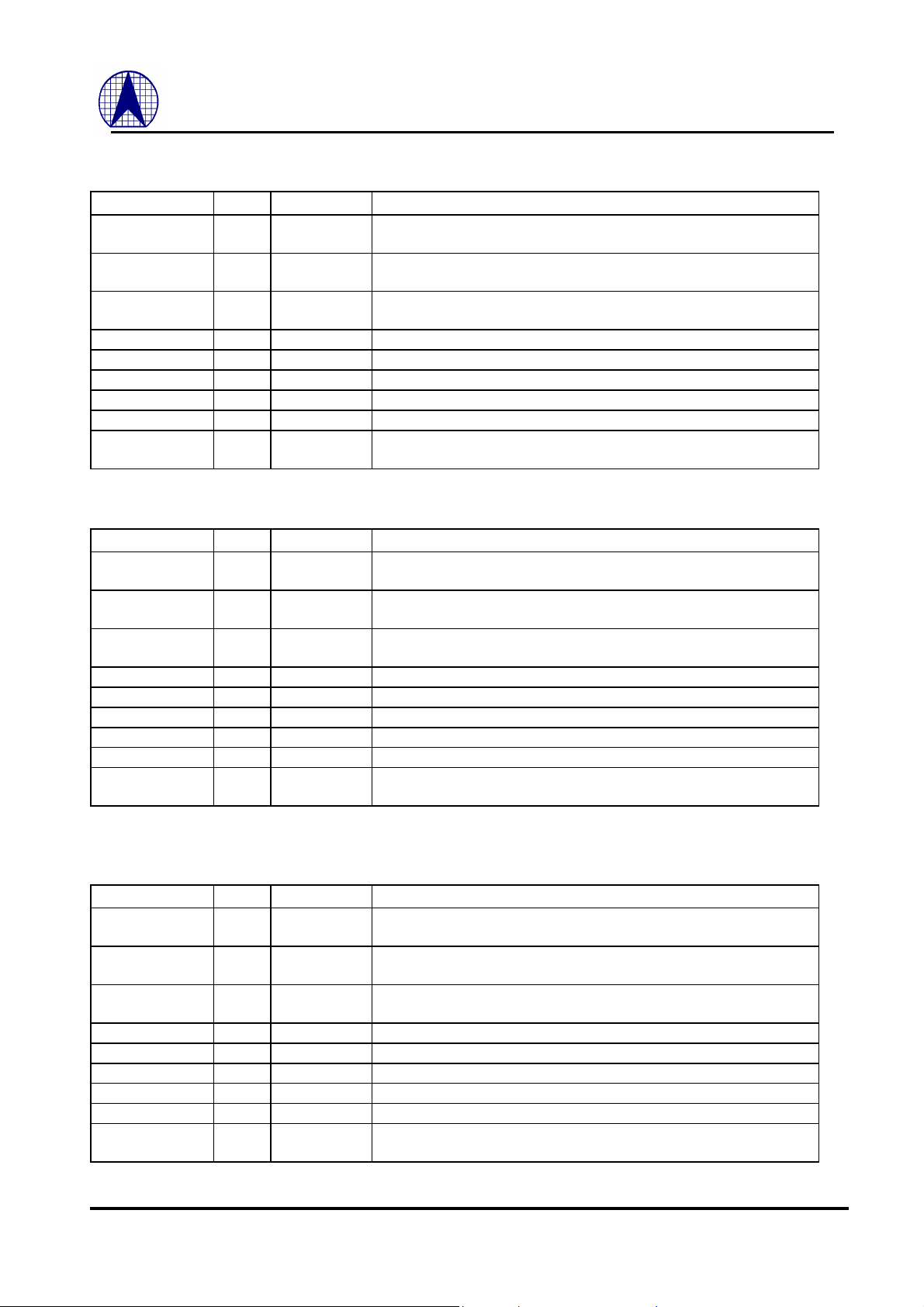

1.2 AX88655 Block Diagram

GMII PHY

GMII PHY

GMII PHY

GMII PHY

GMII PHY

GPIO

10/100/1000 MAC

10/100/1000 MAC

10/100/1000 MAC

10/100/1000 MAC

10/100/1000 MAC

General Purpose

I/O Interface (GPIO)

High Speed

Switch Fabric

Configuration

Logic

Routing /Learning

Engine

Address Look-up Table

Buffer Manager

Packet

Buffer

EEPROM

Interface

Fig-1 AX88655 Block Diagram

6

ASIX ELECTRONICS CORPORATION

TX_EN0

AVDD25D

TX_CLK1

RX_DV1

NC

TXD1[1]

NC

TXD1[2]

VSS

RXD1[6]

NC

COL1

AVDD25A

NC

TXD0[4]

RXD1[4]

NC

VSS

NC

VDD25

VSS

NC

AVSS25D

RXD1[2]

RXD1[1]

NC

TXD1[3]

GTX_CLK1

RX_CLK1

FILTER

NC

NC

VSS

NC

TXD0[6]

VDD33

RXD1[7]

X_IN

NC

RXD1[5]

TXD0[5]

VSS

NC

NC

VSS

VSS

AVSS25A

NC

VSS

RXD1[3]

CRS1

X_OUT

TXD1[4]

NC

VDD25

VDD25

NC

VSS

TXD0[7]

AVBB25

NC

RXD1[0]

TXD1[1]

VSS

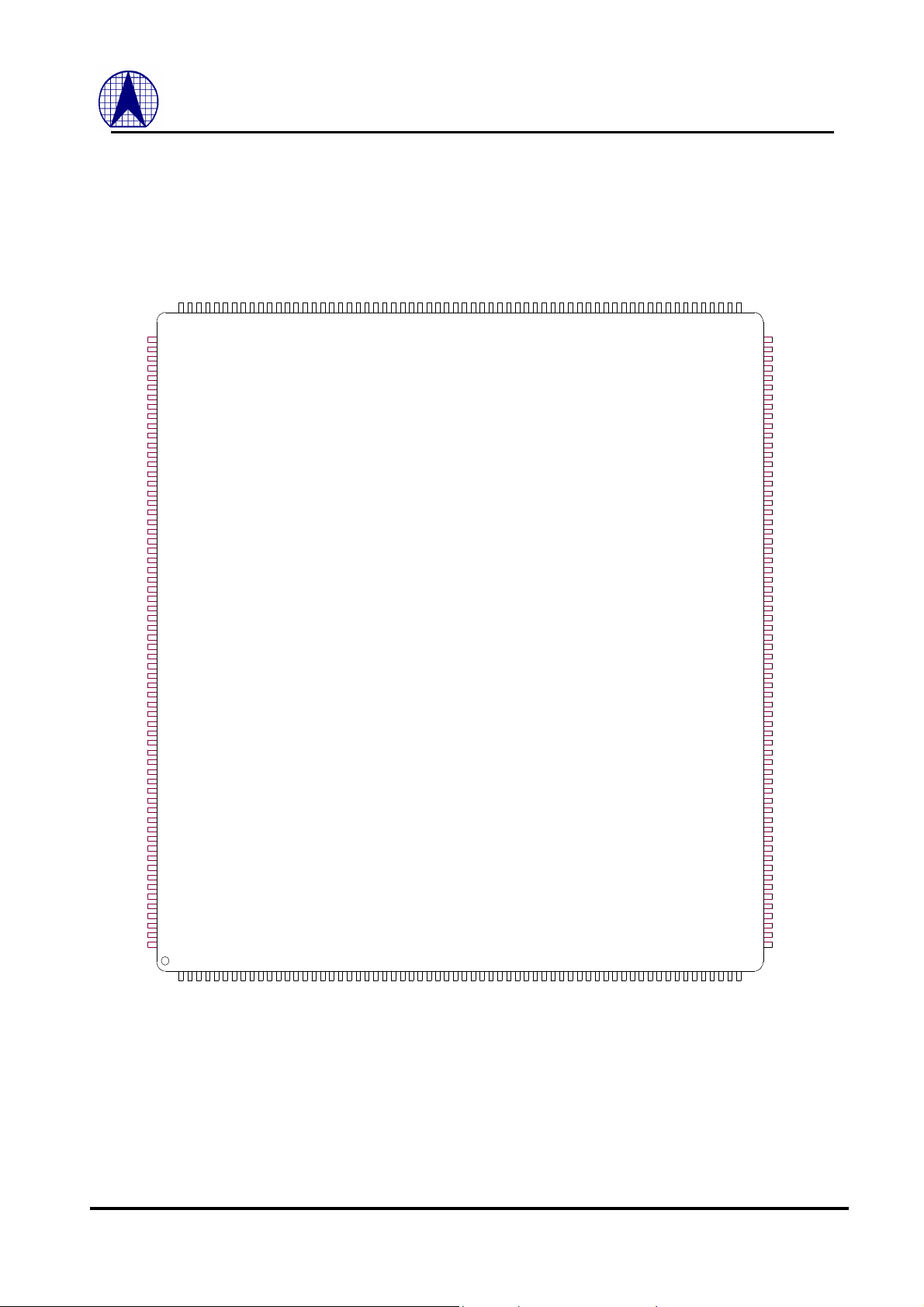

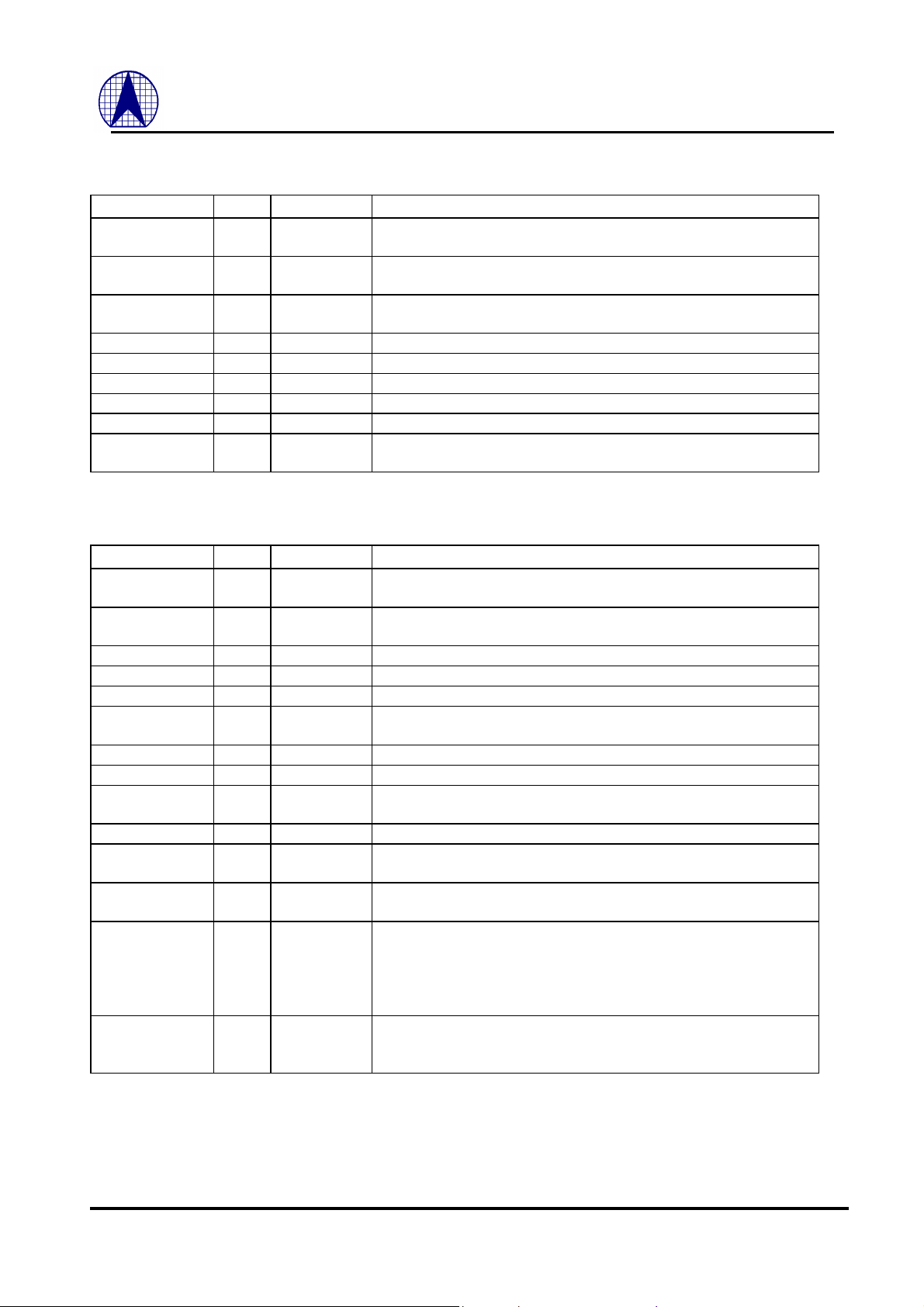

1.3 Pin Connection Diagram

VSS

VSS

VSS

NC

VDD25

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VSS

VDD25

NC

NC

VSS

VSS

VSS

VSS

NC

NC

NC

NC

VSS

VSS

VSS

NC

VDD25

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VSS25

VDD25

CRS0

COL0

RXD0[0]

RXD0[1]

RXD0[2]

RXD0[3]

RXD0[4]

RXD0[5]

RXD0[6]

RXD0[7]

RX_CLK0

RX_DV0

VSS

GTX_CLK0

VDD25

TX_CLK0

TXD0[0]

TXD0[1]

TXD0[2]

TXD0[3]

NC

NC

NC

NC

VSS

VSS

VSS

VSS

191

190

192

188

189

187

186

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

1

2

185

7

5

8

3

6

4

NC

184

9

VDD25

NC

182

183

10

GPIO3

VSS

GPIO0

GPIO2

GPIO4

GPIO1

NC

NC

NC

175

179

178

177

176

174

173

181

180

10/100/1000Mbps

Switch Controller

12

11

14

13

20

19

15

16

17

18

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

VSS

SYSCLK

169

168

NC

167

MDC

MDIO

166

165

SDC

164

SDIO

VDD25

163

162

GCLK

161

NC

172

/RST

VDD33

171

170

AX88655P

Ethernet

29

21

23

24

22

25

31

27

30

26

32

28

VSS

VSS

/GCLK_EN

/SYSCLK_EN

158

160

159

157

35

34

33

36

SID4

156

37

SID3

155

38

SID1

SID2

154

39

153

40

SID0

VDD25

152

151

41

42

TX_EN4

VSS

150

149

43

44

TXD4[6]

TXD4[7]

148

147

45

46

TXD4[4]

TXD4[5]

TXD4[3]

145

144

146

47

48

49

TXD4[0]

TXD4[1]

TXD4[2]

143

142

141

51

52

50

TX_CLK4

GTX_CLK4

VSS

VDD25

139

138

140

137

54

55

53

56

RX_DV4

RXD4[7]

RX_CLK4

135

136

134

57

59

58

RXD4[5]

RXD4[4]

RXD4[6]

132

133

131

62

61

60

RXD4[3]

RXD4[2]

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

96

RXD4[1]

RXD4[0]

COL4

CRS4

VDD25

VSS

TX_EN3

TXD3[7]

TXD3[6]

TXD3[5]

TXD3[4]

TXD3[3]

TXD3[2]

TXD3[1]

TXD3[0]

TX_CLK3

VDD25

GTX_CLK3

VSS

RX_DV3

RX_CLK3

RXD3[7]

RXD3[6]

RXD3[5]

RXD3[4]

RXD3[3]

RXD3[2]

RXD3[1]

RXD3[0]

COL3

CRS3

VDD25

VSS25

TX_EN2

TXD2[7]

TXD2[6]

TXD2[5]

TXD2[4]

TXD2[3]

TXD2[2]

TXD2[1]

TXD2[0]

TX_CLK2

VDD25

GTX_CLK2

VSS

RX_DV2

RX_CLK2

RXD2[7]

RXD2[6]

RXD2[5]

RXD2[4]

RXD2[3]

RXD2[2]

RXD2[1]

RXD2[0]

COL2

CRS2

VDD25

VSS25

TX_EN1

TXD1[7]

TXD1[6]

TXD1[5]

Fig-2 AX88655 Pin Diagram

7

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

When TX_EN0 is asserted, data on TXD0[7:0] are

transmitted onto PHY. TX_EN0 is synchronous to GTX_CLK0 in

T

Synchronous to the rising of GTX_CLK0 in

T mode. And synchronous to rising edge of TX_CLK0 in

and TXD0[3:0] are

Active high to indicate that there is collision

Active high if there is carrier on medium. In half

CRS0 is also asserted during transmission and

Active high to indicate that data presented on

is running at 1000/100/10

T mode respectively. RX_DV0 and RXD0[7:0] are synchronous

Data received by the PHY are presented on RXD0 and

d in

T

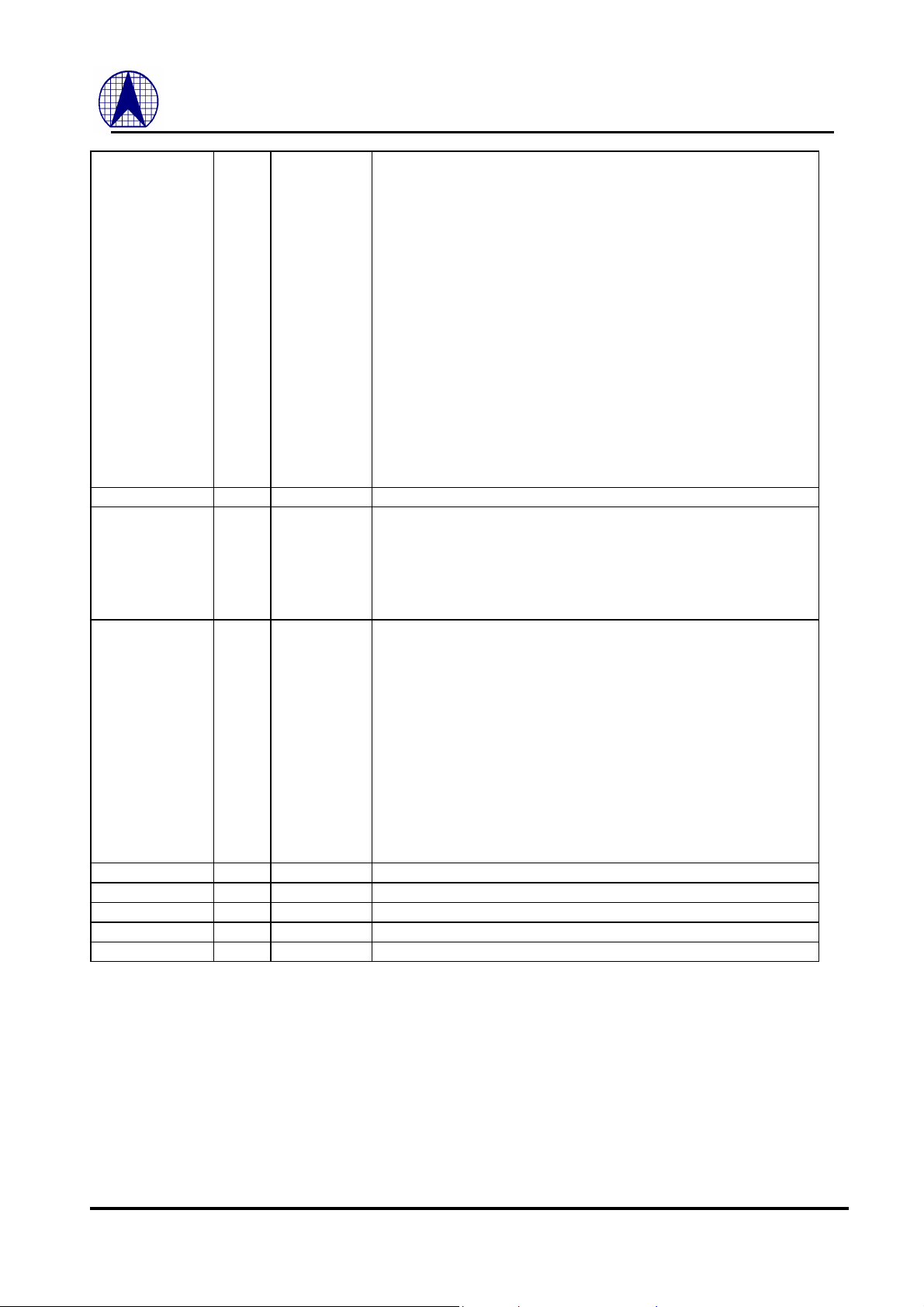

2.0 Pin Descriptions

2.0 I/O Definition

The following terms describe the AX88655 pin-out:

All pin names with the “/” suffix are asserted low.

The following abbreviations are used in following Tables.

I Input PU Pull Up

O Output PD Pull Down

I/O Input/Output P Power Pin

OD Open Drain

2.1 GMII/MII Interface

2.1.1 GMII Interface Port 0

Signal Name I/O Pin No. Description

GTX_CLK0 O

TX_EN0

TXD0[7:0]

TX_CLK0 I/PD

COL0 I/PD

CRS0 I/PD

RX_DV0 I 248

RX_CLK0 I 247

RXD0[7:0]

O

O

I/PD

250

5

4 – 1,

256 – 253

252

238

237

246 - 239

125MHz Clock Output: it is a continuous 125 MHz clock output to

giga-PHY operating at 1000BASE-T. That is, it is a timing reference

for TX_EN0 and TXD0[7:0]

Transmit Enable:

1000BASE-T mode and synchronous to TX_CLK0 in 10/100BASEmode.

Transmit Data:

1000BASE10/100BASE-T mode.

MII Transmit Clock Input: TX_EN0

synchronous to the rising edge of this clock in 10/100BASE-T mode.

Collision Detect:

occurred in half duplex mode. In full duplex mode COL0 is always low.

Carrier Sense:

duplex mode

asynchronous to any clock.

Receive Data Valid:

RXD0[7:0] is valid and synchronous to RX_CLK0.

Receive Clock Input: 125, 25 and 2.5 MHz

BASEto rising edge of this clock.

Receive Data:

synchronous to RX_CLK0. RXD0[3:0] is vali

10/100/1000BASE-T and RXD[7:4] is valid only in 1000BASEmodes.

8

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

2.1.2 GMII Interface Port 1

Signal Name I/O Pin No. Description

GTX_CLK1 O

TX_EN1

TXD1[7:0]

TX_CLK1 I/PD

COL1 I/PD

CRS1 I/PD

RX_DV1 I 55

RX_CLK1 I 54

RXD1[7:0]

O

O

I/PD

57

68

67 – 60

59

45

44

53 - 46

125MHz Clock Output: Please references section 2.1.1.

Transmit Enable: Please references section 2.1.1.

Transmit Data: Please references section 2.1.1.

MII Transmit Clock Input: Please references section 2.1.1.

Collision Detect: Please references section 2.1.1.

Carrier Sense: Please references section 2.1.1.

Receive Data Valid: Please references section 2.1.1.

Receive Clock Input: Please references section 2.1.1.

Receive Data: Please references section 2.1.1.

2.1.3 GMII Interface Port 2

Signal Name I/O Pin No. Description

GTX_CLK2 O

TX_EN2

TXD2[7:0]

TX_CLK2 I/PD

COL2 I/PD

CRS2 I/PD

RX_DV2 I 82

RX_CLK2 I 81

RXD2[7:0]

O

O

I/PD

84

95

94 – 87

86

72

71

80 - 73

125MHz Clock Output: Please references section 2.1.1.

Transmit Enable: Please references section 2.1.1.

Transmit Data: Please references section 2.1.1.

MII Transmit Clock Input: Please references section 2.1.1.

Collision Detect: Please references section 2.1.1.

Carrier Sense: Please references section 2.1.1.

Receive Data Valid: Please references section 2.1.1.

Receive Clock Input: Please references section 2.1.1.

Receive Data: Please references section 2.1.1.

2.1.4 GMII Interface Port 3

Signal Name I/O Pin No. Description

GTX_CLK3 O

TX_EN3

TXD3[7:0]

TX_CLK3 I/PD

COL3 I/PD

CRS3 I/PD

RX_DV3 I 109

RX_CLK3 I 108

RXD3[7:0]

O

O 121 – 114

I/PD

111

122

113

99

98

107 - 100

125MHz Clock Output: Please references section 2.1.1.

Transmit Enable: Please references section 2.1.1.

Transmit Data: Please references section 2.1.1.

MII Transmit Clock Input: Please references section 2.1.1.

Collision Detect: Please references section 2.1.1.

Carrier Sense: Please references section 2.1.1.

Receive Data Valid: Please references section 2.1.1.

Receive Clock Input: Please references section 2.1.1.

Receive Data: Please references section 2.1.1.

9

ASIX ELECTRONICS CORPORATION

This is a clock source of PLL. The

ded

generated by

PHY Management Data Input and

EEPROM Serial Clock. (Note: It is

MPU can identify the switch and PHYs with this ID.

The 5 GPIOs can be programmed for special

. (Note: The function is not released to user normally.

2.1.5 GMII Interface Port 4

Signal Name I/O Pin No. Description

GTX_CLK4 O

TX_EN4

TXD4[7:0]

TX_CLK4 I/PD

COL4 I/PD

CRS4 I/PD

RX_DV4 I 136

RX_CLK4 I 135

RXD4[7:0]

O

O 148 – 141

I/PD

138

149

140

126

125

134 - 127

125MHz Clock Output: Please references section 2.1.1.

Transmit Enable: Please references section 2.1.1.

Transmit Data: Please references section 2.1.1.

MII Transmit Clock Input: Please references section 2.1.1.

Collision Detect: Please references section 2.1.1.

Carrier Sense: Please references section 2.1.1.

Receive Data Valid: Please references section 2.1.1.

Receive Clock Input: Please references section 2.1.1.

Receive Data: Please references section 2.1.1.

2.2 Miscellaneous

Signal Name I/O Pin No. Description

X_IN I 35

X_OUT O 36

GCLK I 161

SYSCLK I 168

/GCLK _EN I/PU

/SYSCLK_EN I/PU

FILTER I 40

/RST I 170

MDIO I/O/PU

MDC O 166

SDIO I/O/PU

SDC I/O/PU

SID[4:0] I/PD

GPIO[4:0] I/O/PU 180 - 176

157

158

165

163

164

I/PD

I/PD

I/UP

I/UP

156,

155,

154,

153,

152

Crystal or OSC 27MHz Input:

PLL will generate a 90MHz internal clock.

Crystal 27MHz Output: This pin should be floating with single-en

external clock.

OSC 125MHz Input: 125MHz Clock for GMII

System Clock Input: 85 ~ 90MHz Clock for switch kernel

GCLK Enable: 0) use GCLK; 1) Reserved

System Clock Enable: 0) use SYSCLK; 1) 90MHz

internal PLL circuit from X_IN clock source.

FILTER: For internal PLL circuit use.

Reset: Active Low

Station Management Data In/Out:

Output.

Station Management Data Clock Out: PHY Management Clock.

EEPROM Data In/Out: EEPROM Serial Data Input and Output.

EEPROM Data Clock In/Out:

output pin if the embedded MPU is active; otherwise as input pin)

Switch ID:

Default is “00011b”.

General Purpose I/O:

application

Please contact with ASIX directly if any requirement)

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

10

ASIX ELECTRONICS CORPORATION

8, 9, 41, 15, 16,

NC N/A

17, 21, 23, 24,

25, 26, 27, 28,

29, 30, 31, 32,

43, 167, 172,

VDD33 I 34, 171,

VDD25 P 7, 22,

VSS P 6, 10, 11, 12,

AVBB25 P 37

AVDD25A P 38

AVSS25A P 39

AVDD25D P 42

AVSS25D P 41

173, 174, 175,

183, 184, 189,

190, 191, 192,

196, 198, 199,

200, 201, 202,

203, 204, 205,

206, 207, 210,

211, 216, 217,

218, 219, 223,

225, 226, 227,

228, 229, 230,

231, 232, 233,

234

58, 70, 85,

97, 112, 124,

139, 151, 162,

182, 197, 209,

224, 236, 251

13, 18, 19, 20,

33, 56, 69,

83,96, 110,

123, 137, 150,

157, 159, 160,

167, 169, 181,

185, 186, 187,

188, 193, 194,

195, 208, 212,

213, 214, 215,

220, 221, 222,

235, 249

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

NC: No Connect.

3.3V +/-5% Supply Voltage.

2.5V +/-5% Supply Voltage.

Ground

Ground for PLL

2.5V +/-5% Supply Voltage for PLL.

Ground for PLL

2.5V +/-5% Supply Voltage for PLL.

Ground for PLL

11

ASIX ELECTRONICS CORPORATION

AX88655 P 5-Port 10/100/1000BASE-T Ethernet Switch

3.0 Functional Description

3.1 Introduction

In general, the AX88655 device is a highly integrated Layer 2 switch. It supports five 10/100/1000 ports with on-chip

MACs. It also supports integrated switching logic, packet queuing memory and packet storage memory. The AX88655

is capable of routing-and-forwarding packets at wire speed on all ports regardless of packet size.

It is a low cost solution for five ports Gigabit Ethernet backbone switch design. No CPU interface is required; After power

on reset, AX88655 provide an auto load configuration setting function through a 2 wire serial EEPROM interface to

access external EEPROM device, and AX88655 can easily be configured to support trunking, QoS, IEEE 802.3x flow

control threshold setting, broadcast storm control ...etc functions. An overview of AX88658’s major functional blocks is

shown in Fig-1.

3.2 Packet Filtering and Forwarding Process

The switch use simple store-and-forward algorithm as packet switching method. After receives incoming packets, the

packets will be stored to the embedded memory first. The AX88655 searches in the Address-Lookup Table with DA of

the packet. The packet will be forward to its destination port, if this packet’s DA hits; otherwise this packet will be

broadcasted. Of course, only good packets will be forward. Conditions of good packets are below:

1. CRC is correct.

2. 64 Bytes < PacketLength < 1518/1522 Bytes

3. Not local packets, That is, it is a local packets if its SourcePort is its DestinationPort.

4. Not PAUSE or other control packets.

5. Not the same trunking group.

3.3 MAC Address Routing, Learning and Aging Process

The switch supports 4K MAC entries for switching. Two-way dynamic address learning is performed by each good

unicast packet is completely received. And linear/XOR hash algorithm of the static address learning is achieved by

EEPROM configuration. On the other hand, the routing process is performed whenever the packet’s DA is captured. If

the DA can not get a hit result, the packet is going to broadcast.

Only the learned address entries are scheduled in the aging machine. If one station does not transmit any packet for a

period of time, the belonging MAC address will be kicked out from the address table. The aging out time can be program

automatically through the EEPROM configuration. (Default value is 300 seconds)

3.4 Full Duplex 802.3x Flow Control

In full duplex mode, AX88655 supports the standard flow control mechanism defined in IEEE 802.3x standard. It

enables the stopping of remote node transmissions via a PAUSE frame information interaction. When space of the packet

buffer is less than the initialization setting threshold value, AX88655 will send out a PAUSE-ON packet with pause time

equal to “xFFF” to stop the remote node transmission. And then AX88655 will send out a PAUSE-OFF packet with

pause time equal to zero to inform the remote node to retransmit packet if has enough space to receive packets.

3.5 Half Duplex Back Pressure Control

In half duplex mode, AX88655 provide a backpressure control mechanism to avoid dropping packets during network

conjection situation. When space of the packet buffer is less than the initialization setting threshold value, AX88655 will

send a JAM pattern in the input port when it senses an incoming packet, thus force a collision to make the remote node

transmission back off and will effectively avoid dropping packets. And then AX88655 will not send out a JAM packet

any more if has enough space to receive one packet.

3.6 MII Polling

The AX88655 supports PHY management through the serial MDIO/MDC interface. That is, the AX88655 access related

12

ASIX ELECTRONICS CORPORATION

Loading...

Loading...