ASIX AX88195P Datasheet

Features

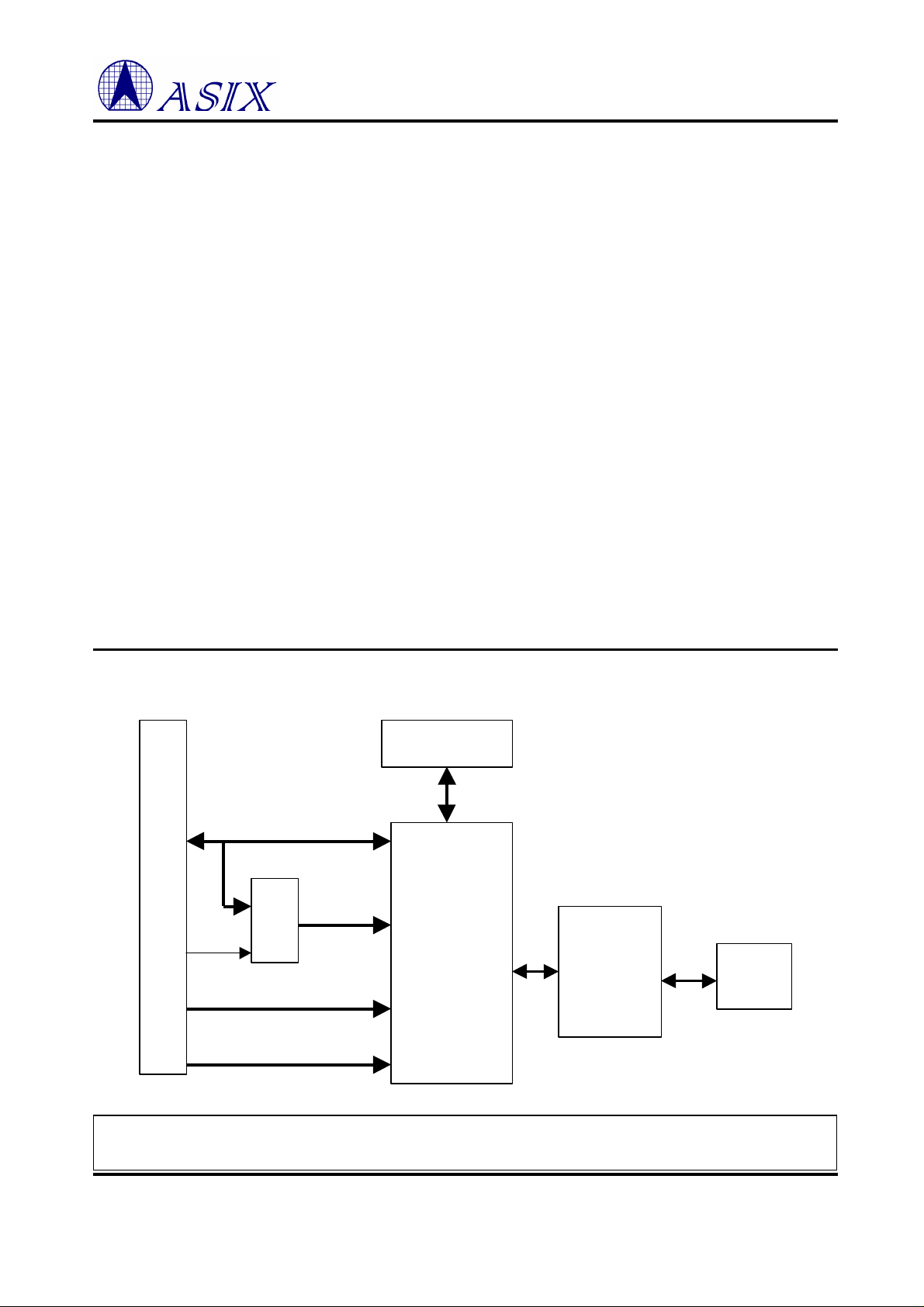

CPU

LATCH

Addr L

Addr H

Ctl BUS

SRAM

AX88195P

10/100BASE Local CPU Bus Fast Ethernet MAC Controller

Document No.: AX195-17 / V1.7 / May. 12 ’00

• IEEE 802.3u 100BASE-T, TX, and T4 Compatible

• Single chip local CPU bus 10/100Mbps Fast

Ethernet MAC Controller

• NE2000 register level compatible instruction

• Support both 8 bit and 16 bit local CPU interfaces

include MCS-51 series, 80186 series and MC68K

series CPU

• Support both 10Mbps and 100Mbps data rate

• Support both full-duplex or half-duplex operation

• Provides a MII port for both 10/100Mbps operation

• External and internal loop-back capability

• Two external 32K*8 Asynchronous SRAMs

required for packet buffer

• 128-pin LQFP low profile package

• 25MHz Operation, Dual 5V and 3.3V CMOS

process with 5V I/O tolerance. Or pure 3.3V

operation

*IEEE is a registered trademark of the Institute of Electrical and Electronic

Engineers, Inc.

*All other trademarks and registered trademark are the property of their

respective holders.

• Support EEPROM interface to store MAC address

Product description

The AX88195 Fast Ethernet Controller is a high performance and highly integrated local CPU bus Ethernet Controller.

The AX88195 supports both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80x86 series, MC68K series

CPU and ISA bus. The AX88195 implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 /

IEEE802.3u LAN standard and supports both 10Mbps/100Mbps media-independent interface (MII) to simplify the

design. Two low cost 32k*8 SRAM is required for packet buffer.

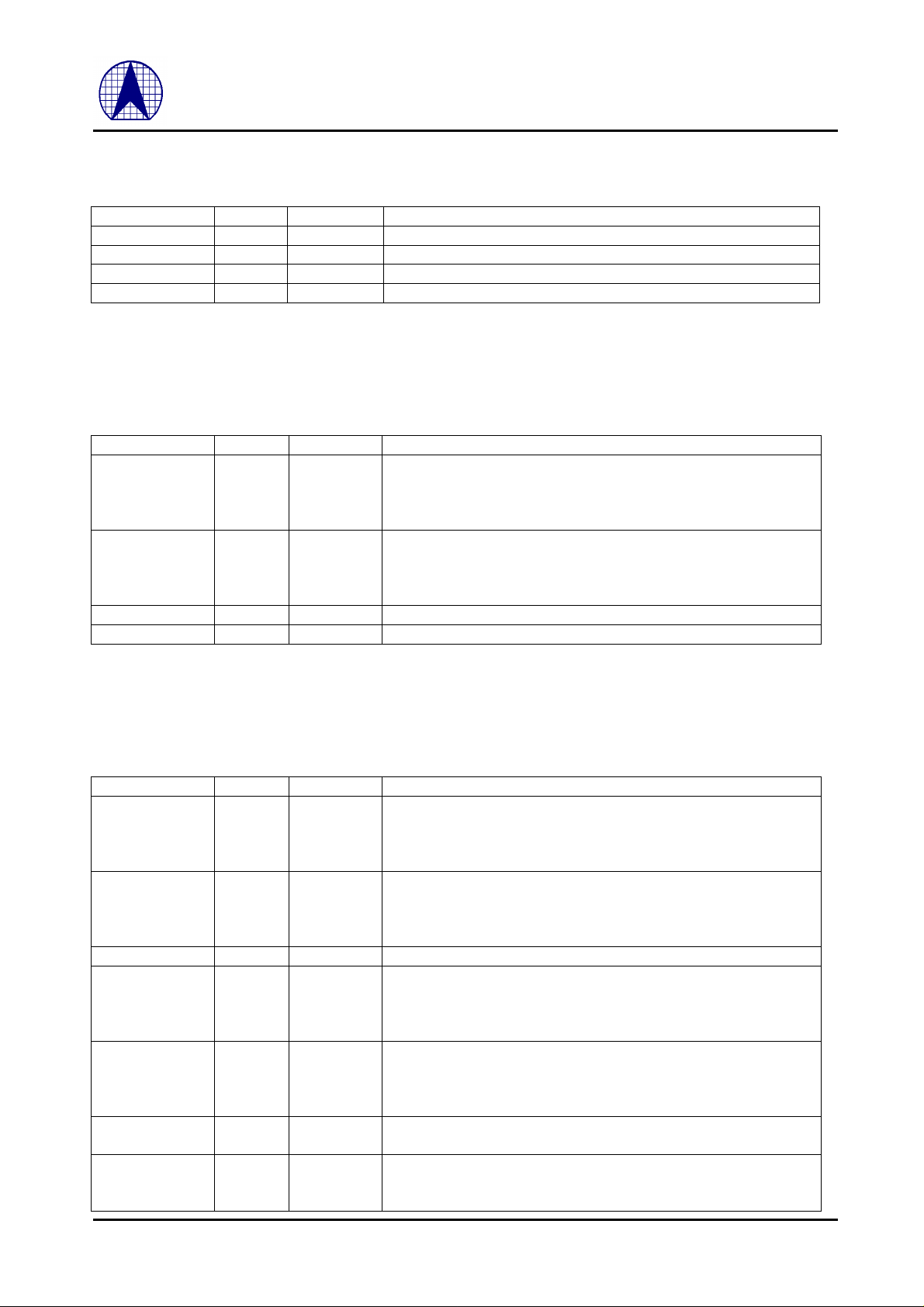

System Block Diagram

BUFFER

AD BUS

AX88195

PHY/TxRx RJ45

Always contact ASIX for possible updates before starting a design.

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify product specification without notice. No liability

is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

ASIX ELECTRONICS CORPORATION First Released Date : Oct/02/1998

2F, NO.13, Industry East Rd. II, Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

TEL: 886-3-579-9500 FAX: 886-3-579-9558 http://www.asix.com.tw

AX88195 Local CPU Bus Fast Ethernet MAC Controller

CONTENTS

1.0 INTRODUCTION .............................................................................................................................................. 4

1.1 GENERAL DESCRIPTION:..................................................................................................................................... 4

1.2 AX88195 BLOCK DIAGRAM:.............................................................................................................................. 4

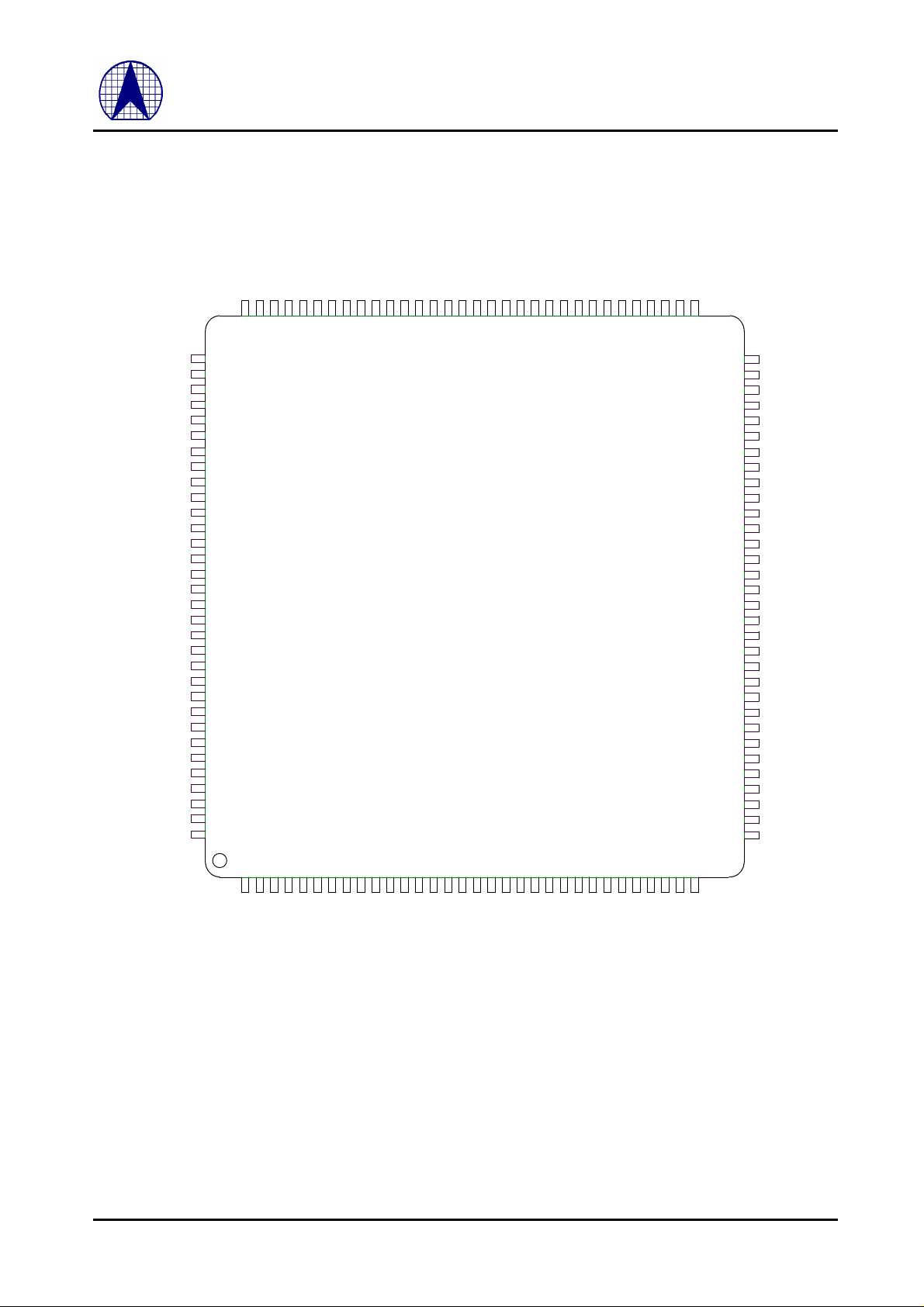

1.3 AX88195 PIN CONNECTION DIAGRAM ............................................................................................................... 5

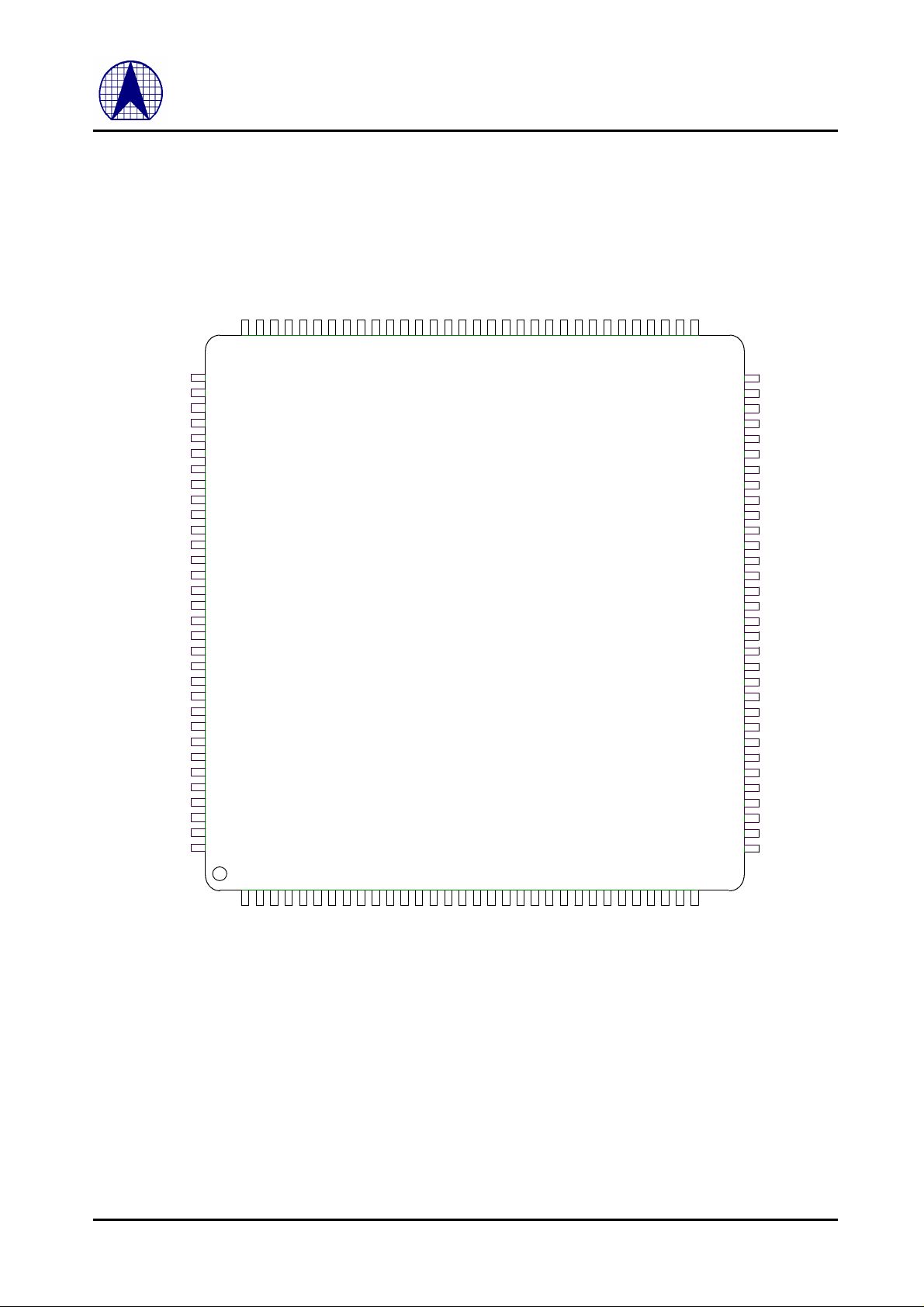

1.3.1 AX88195 Pin Connection Diagram for ISA Bus Mode................................................................................ 6

1.3.2 AX88195 Pin Connection Diagram for 80x86 Mode ................................................................................... 7

1.3.3 AX88195 Pin Connection Diagram for MC68K Mode................................................................................ 8

1.3.4 AX88195 Pin Connection Diagram for MCS-51 Mode ............................................................................... 9

2.0 SIGNAL DESCRIPTION................................................................................................................................. 10

2.1 LOCAL CPU BUS INTERFACE SIGNALS GROUP................................................................................................... 10

2.2 MII INTERFACE SIGNALS GROUP........................................................................................................................ 11

2.3 EEPROM SIGNALS GROUP .............................................................................................................................. 12

2.4 SRAM INTERFACE PINS GROUP......................................................................................................................... 12

2.5 MISCELLANEOUS PINS GROUP............................................................................................................................ 12

2.6 POWER ON CONFIGURATION SETUP SIGNALS CROSS REFERENCE TABLE ................................................................ 13

3.0 MEMORY AND I/O MAPPING...................................................................................................................... 14

3.1 EEPROM MEMORY MAPPING.......................................................................................................................... 14

3.2 I/O MAPPING................................................................................................................................................... 14

3.3 SRAM MEMORY MAPPING .............................................................................................................................. 14

4.0 REGISTERS OPERATION............................................................................................................................. 15

4.1 COMMAND REGISTER (CR) OFFSET 00H (READ/WRITE)................................................................................... 17

4.2 INTERRUPT STATUS REGISTER (ISR) OFFSET 07H (READ/WRITE)..................................................................... 17

4.3 INTERRUPT MASK REGISTER (IMR) OFFSET 0FH (WRITE)................................................................................. 18

4.4 DATA CONFIGURATION REGISTER (DCR) OFFSET 0EH (WRITE)....................................................................... 18

4.5 TRANSMIT CONFIGURATION REGISTER (TCR) OFFSET 0DH (WRITE)................................................................ 18

4.6 TRANSMIT STATUS REGISTER (TSR) OFFSET 04H (READ) ................................................................................ 19

4.7 RECEIVE CONFIGURATION (RCR) OFFSET 0CH (WRITE) .................................................................................. 19

4.8 RECEIVE STATUS REGISTER (RSR) OFFSET 0CH (READ) .................................................................................. 19

4.9 INTER-FRAME GAP (IFG) OFFSET 16H (READ/WRITE) ...................................................................................... 20

4.10 INTER-FRAME GAP SEGMENT 1(IFGS1) OFFSET 12H (READ/WRITE)............................................................... 20

4.11 INTER-FRAME GAP SEGMENT 2(IFGS2) OFFSET 13H (READ/WRITE)............................................................... 20

4.12 MII/EEPROM MANAGEMENT REGISTER (MEMR) OFFSET 14H (READ/WRITE).............................................. 20

4.13 TEST REGISTER (TR) OFFSET 15H (WRITE) ................................................................................................... 20

5.0 CPU I/O READ AND WRITE FUNCTIONS.................................................................................................. 21

5.1 ISA BUS TYPE ACCESS FUNCTIONS. ................................................................................................................... 21

5.2 80186 CPU BUS TYPE ACCESS FUNCTIONS......................................................................................................... 21

5.3 MC68K CPU BUS TYPE ACCESS FUNCTIONS. ..................................................................................................... 22

5.3 MCS-51 CPU BUS TYPE ACCESS FUNCTIONS..................................................................................................... 22

6.0 ELECTRICAL SPECIFICATION AND TIMINGS........................................................................................ 23

6.1 ABSOLUTE MAXIMUM RATINGS........................................................................................................................ 23

6.2 GENERAL OPERATION CONDITIONS................................................................................................................... 23

6.3 DC CHARACTERISTICS..................................................................................................................................... 23

6.4 A.C. TIMING CHARACTERISTICS....................................................................................................................... 24

6.4.1 XTAL / CLOCK........................................................................................................................................ 24

6.4.2 Reset Timing............................................................................................................................................ 24

6.4.3 ISA Bus Access Timing ............................................................................................................................. 25

6.4.4 80186 Type I/O Access Timing................................................................................................................. 26

2

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

6.4.5 68K Type I/O Access Timing.................................................................................................................... 27

6.4.6 8051 Bus Access Timing........................................................................................................................... 28

6.4.7 MII Timing ............................................................................................................................................... 29

6.4.8 Asynchronous Memory I/F Access Timing................................................................................................ 30

7.0 PACKAGE INFORMATION........................................................................................................................... 31

APPENDIX A: APPLICATION NOTE 1............................................................................................................. 32

A.1 USING CRYSTAL.............................................................................................................................................. 32

A.2 USING OSCILLATOR......................................................................................................................................... 32

A.3 DUAL POWER (5V AND 3.3V/3.0V) APPLICATION ............................................................................................. 33

A.4 SINGLE POWER (3.3V/3.0V) APPLICATION........................................................................................................ 33

A.5 DUAL POWER (5V AND 3.3V) APPLICATION WITH 3.3V PHY............................................................................. 34

APPENDIX B: APPLICATION NOTE 2............................................................................................................. 35

B.1 ADVANCE APPLICATION FOR USING CRYSTAL................................................................................................... 35

APPENDIX C: APPLICATION NOTE FOR RDY IS NOT APPLICABLE ...................................................... 36

ERRATA OF AX88195 V1..................................................................................................................................... 37

FIGURES

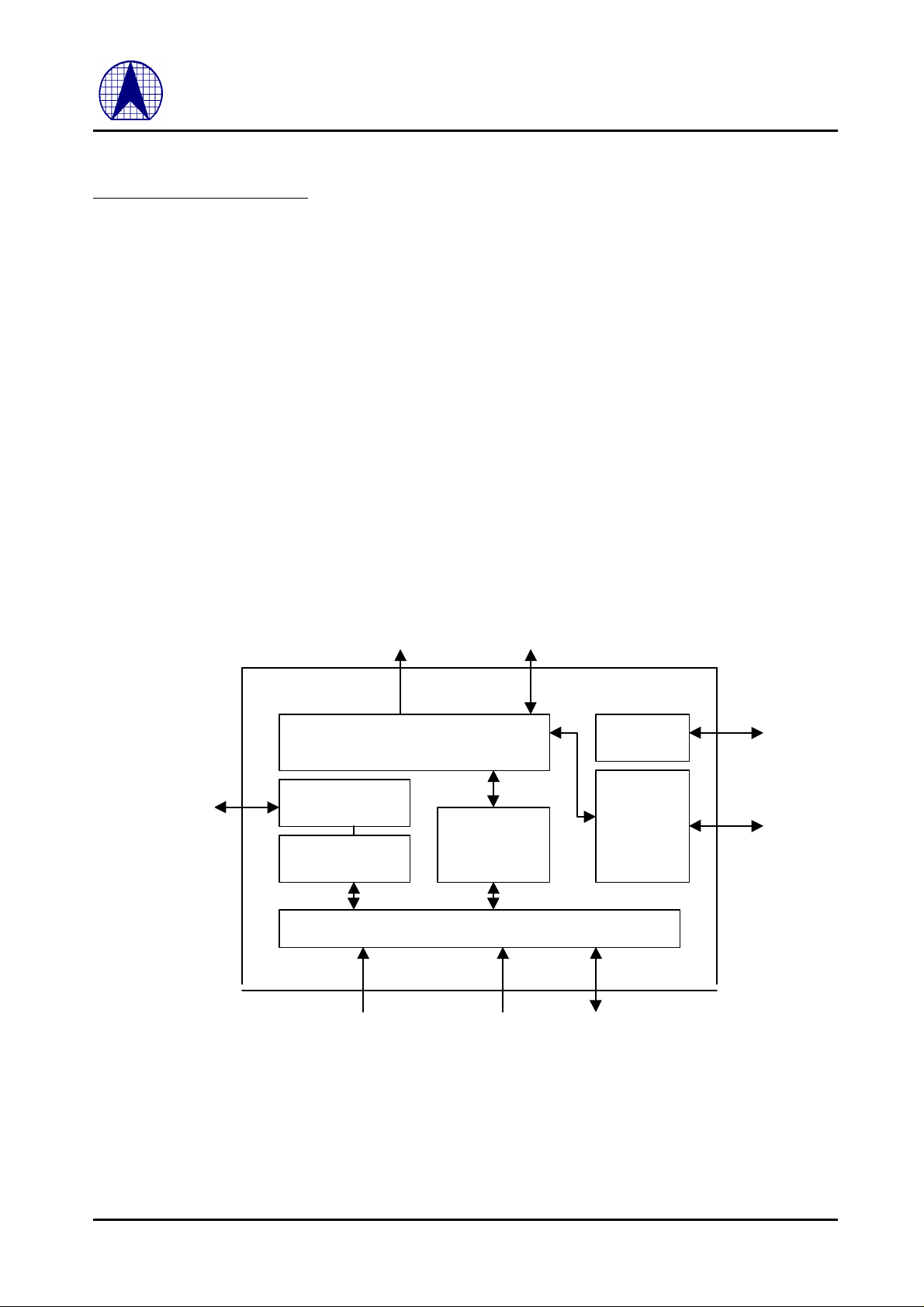

FIG - 1 AX88195 BLOCK DIAGRAM ............................................................................................................................. 4

FIG - 2 AX88195 PIN CONNECTION DIAGRAM.............................................................................................................. 5

FIG - 3 AX88195 PIN CONNECTION DIAGRAM FOR ISA BUS MODE............................................................................... 6

FIG - 4 AX88195 PIN CONNECTION DIAGRAM FOR 80X86 MODE .................................................................................. 7

FIG - 5 AX88195 PIN CONNECTION DIAGRAM FOR MC68K MODE................................................................................ 8

FIG - 6 AX88195 PIN CONNECTION DIAGRAM FOR MCS-51 MODE............................................................................... 9

TABLES

TAB - 1 LOCAL CPU BUS INTERFACE SIGNALS GROUP.................................................................................................. 11

TAB - 2 MII INTERFACE SIGNALS GROUP..................................................................................................................... 11

TAB - 3 EEPROM BUS INTERFACE SIGNALS GROUP..................................................................................................... 12

TAB - 4 SRAM INTERFACE PINS GROUP...................................................................................................................... 12

TAB - 5 MISCELLANEOUS PINS GROUP......................................................................................................................... 13

TAB - 6 POWER ON CONFIGURATION SETUP TABLE ..................................................................................................... 13

TAB - 7 I/O ADDRESS MAPPING ................................................................................................................................. 14

TAB - 8 LOCAL MEMORY MAPPING ............................................................................................................................ 14

TAB - 9 PAGE 0 OF MAC CORE REGISTERS MAPPING.................................................................................................. 15

TAB - 10 PAGE 1 OF MAC CORE REGISTERS MAPPING................................................................................................ 16

3

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

1.0 Introduction

Registers

I/F

SD[15:0]

SA[9:0]

Ctl BUS

MII I/F

MEMD[15:0]

MEMA[15:1]

EEDO

1.1 General Description:

The AX88195 provides industrial standard NE2000 registers level compatable instruction set. Various drivers

are easy acquired, maintenance and usage. No much additional effort to be paid. Software is easily port to

various embedded system with no pain and tears

The AX88195 Fast Ethernet Controller is a high performance local CPU bus Ethernet Controller. The AX88195

supports both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80x86 series, MC68K series CPU

and ISA bus. The AX88196 implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 /

IEEE802.3u LAN standard and supports both 10Mbps/100Mbps media-independent interface (MII) to simplify

the design.

AX88195 use 128-pin LQFP low profile package, 25MHz operation, dual 5V and 3.3V CMOS process with 5V

I/O tolerance or pure 3.3V operation.

1.2 AX88195 Block Diagram:

EECS

EECK

EEDI

Fig - 1 AX88195 Block Diagram

SEEPROM

NE2000

SRAM

Arbiter

Remote

DMA

FIFOs

Host Interface

STA

MAC

Core

4

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

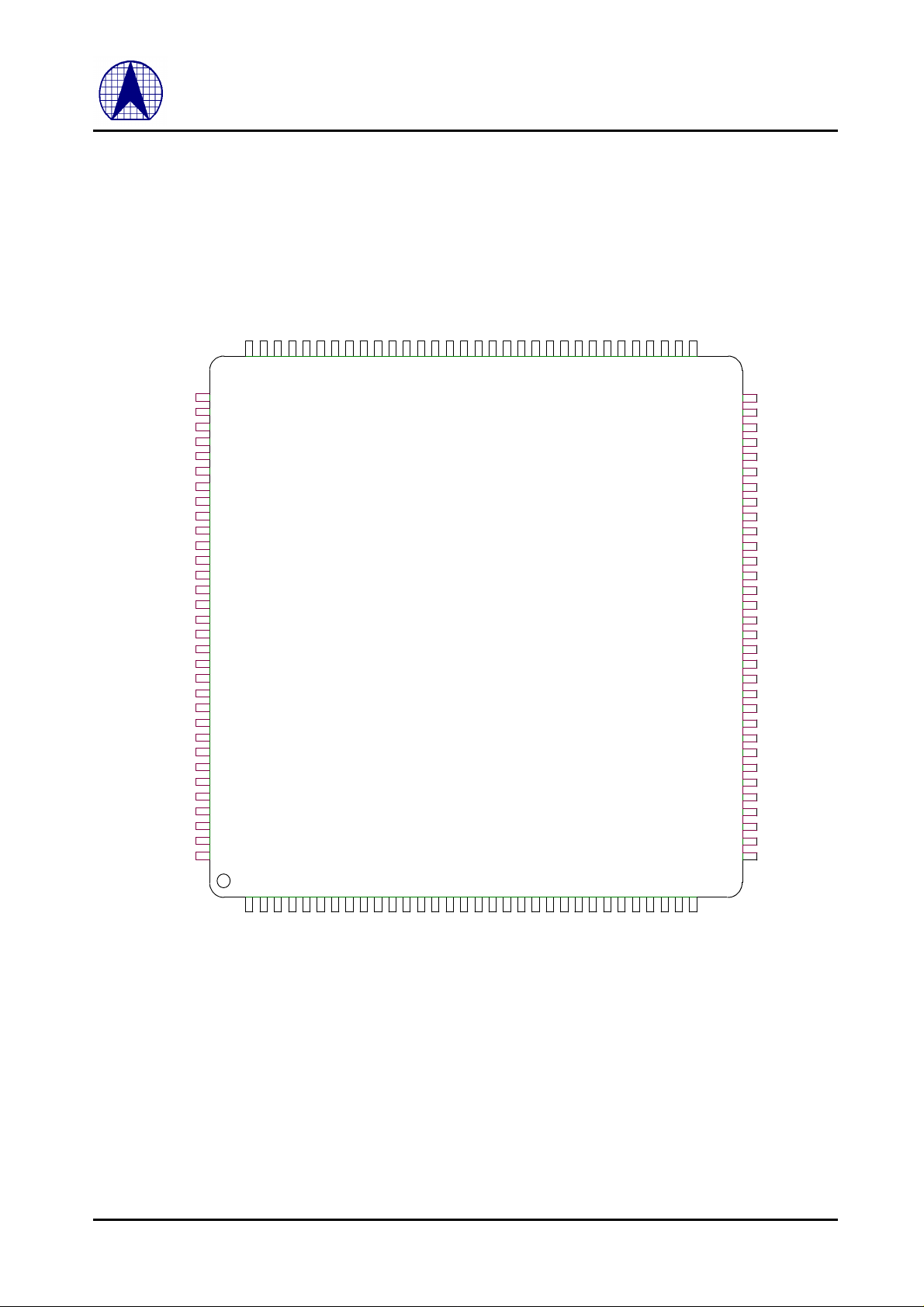

1.3 AX88195 Pin Connection Diagram

R/W

/LDS

/UDS

/IRQ

The AX88195 is housed in the 128-pin plastic light quad flat pack. Fig - 2 shows the AX88195 pin

connection diagram.

TX_EN

TXD[1]

TXD[2]

TXD[3]

LVDD

CLKO25M

VSS

LCLK/XTALIN

XTALOUT

VSS

EECS

EECK

EEDI

EEDO

LVDD

SAL[0]

SAL[1]

SAL[2]

SAH[0]

SAH[1]

SAH[2]

SAX[0]

SAX[1]

VSS

/IOCS16

SAX[2]

SAX[3]

/CS

AEN/PSEN

RDY/DTACK

/RESET

RESET

LVDD

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

TXD[0]

TX_CLK

96

95

94

VSS

93

MDC

MDIO

RXD[3]

RXD[2]

RXD[1]

90

8892858983

RXD[0]

CRS

RX_CLK

86

87

COL

84

AX88195

LOCAL CPU BUS

10/100BASE MAC

CONTROLLER

3

4

1

2

8

7

6

5

9

12

13

11

10

RX_DV

RX_ER

VSS

829181

16

15

14

MEMD[0]

MEMD[1]

MEMD[2]

MEMD[3]

78

77

797480

19

17

20

18

MEMD[4]

MEMD[5]

MEMD[6]

HVDD

75

73

76

24

21

23

22

MEMD[7]

MEMD[8]

MEMD[9]

VSS

71

72

70

69

26

25

28

27

MEMD[12]

MEMD[10]

MEMD[11]

MEMD[13]

66

65

68

67

32

31

29

30

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

HVDD

MEMD[14]

MEMD[15]

MEMA[1]

MEMA[2]

VSS

MEMA[3]

MEMA[4]

MEMA[5]

MEMA[6]

LVDD

MEMA[7]

MEMA[8]

MEMA[9]

MEMA[10]

VSS

MEMA[11]

MEMA[12]

MEMA[13]

MEMA[14]

LVDD

MEMA[15]

/MEMRD

/MEMWR

VSS

NC

SD[0]

SD[1]

SD[2]

SD[3]

VSS

SD[4]

NC

SA[1]

SA[0]

SA[3]

SA[2]

SA[5]

SA[4]

SA[6]

SA[7]

SA[9]

SA[8]

VSS

IRQ

NC

/IORD

/IOWR

NC

/BHE

HVDD

SD[14]

SD[13]

SD[15]

VSS

SD[12]

Fig - 2 AX88195 Pin Connection Diagram

5

ASIX ELECTRONICS CORPORATION

SD[9]

SD[11]

SD[10]

SD[8]

HVDD

SD[7]

SD[6]

SD[5]

AX88195 Local CPU Bus Fast Ethernet MAC Controller

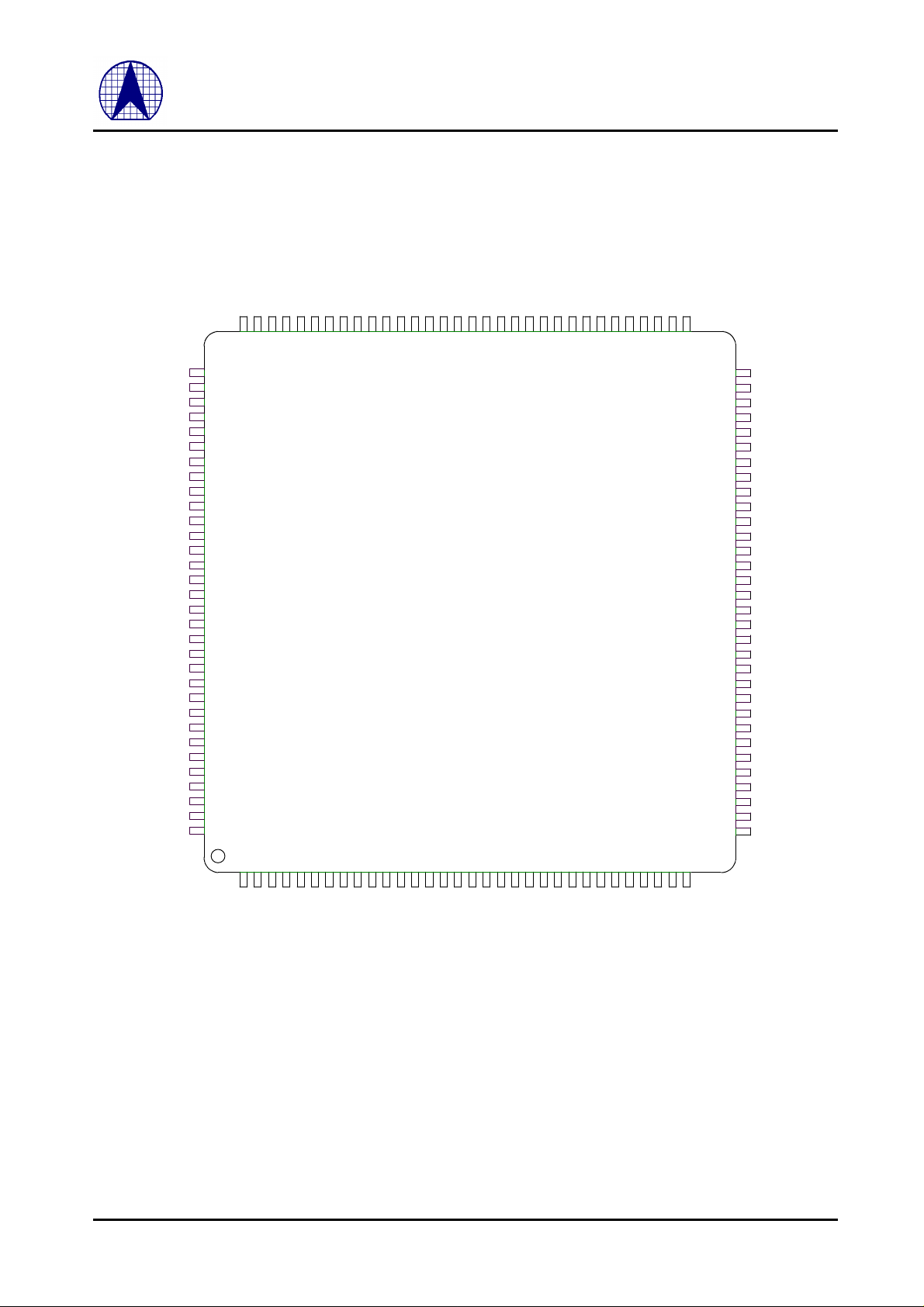

1.3.1 AX88195 Pin Connection Diagram for ISA Bus Mode

SA[1]

HVDD

HVDD

SA[0]

SA[3]

SA[2]

SA[5]

SA[4]

SA[6]

SA[7]

SA[9]

SA[8]

/IOWR

SD[15]

SD[14]

SD[13]

SD[12]

SD[11]

SD[10]

SD[9]

SD[8]

SD[6]

SD[5]

SD[7]

/BHE

/IORD

TX_EN

TXD[1]

TXD[2]

TXD[3]

LVDD

CLKO25M

VSS

LCLK/XTALIN

XTALOUT

VSS

EECS

EECK

EEDI

EEDO

LVDD

SAL[0]

SAL[1]

SAL[2]

SAH[0]

SAH[1]

SAH[2]

SAX[0]

SAX[1]

VSS

/IOCS16

SAX[2]

SAX[3]

/CS

AEN

RDY

/RESET

RESET

LVDD

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

TXD[0]

TX_CLK

96

95

94

VSS

93

MDC

MDIO

RXD[3]

RXD[2]

RXD[1]

90

8892858983

RXD[0]

CRS

RX_CLK

86

87

COL

84

AX88195

LOCAL CPU BUS

10/100BASE MAC

CONTROLLER

( for ISA Bus I/F )

RX_DV

RX_ER

VSS

829181

MEMD[0]

MEMD[1]

MEMD[2]

MEMD[3]

78

77

797480

MEMD[4]

MEMD[5]

MEMD[6]

HVDD

75

73

76

MEMD[7]

MEMD[8]

71

72

MEMD[9]

MEMD[10]

MEMD[11]

VSS

70

68

67

69

MEMD[12]

MEMD[13]

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

HVDD

MEMD[14]

MEMD[15]

MEMA[1]

MEMA[2]

VSS

MEMA[3]

MEMA[4]

MEMA[5]

MEMA[6]

LVDD

MEMA[7]

MEMA[8]

MEMA[9]

MEMA[10]

VSS

MEMA[11]

MEMA[12]

MEMA[13]

MEMA[14]

LVDD

MEMA[15]

/MEMRD

/MEMWR

VSS

NC

SD[0]

SD[1]

SD[2]

SD[3]

VSS

SD[4]

3

4

1

2

Fig - 3 AX88195 Pin Connection Diagram for ISA Bus Mode

8

7

6

5

9

10

11

VSS

IRQ

12

13

NC

15

14

6

16

17

NC

NC

19

18

24

21

23

22

20

VSS

ASIX ELECTRONICS CORPORATION

26

25

27

28

29

30

31

32

AX88195 Local CPU Bus Fast Ethernet MAC Controller

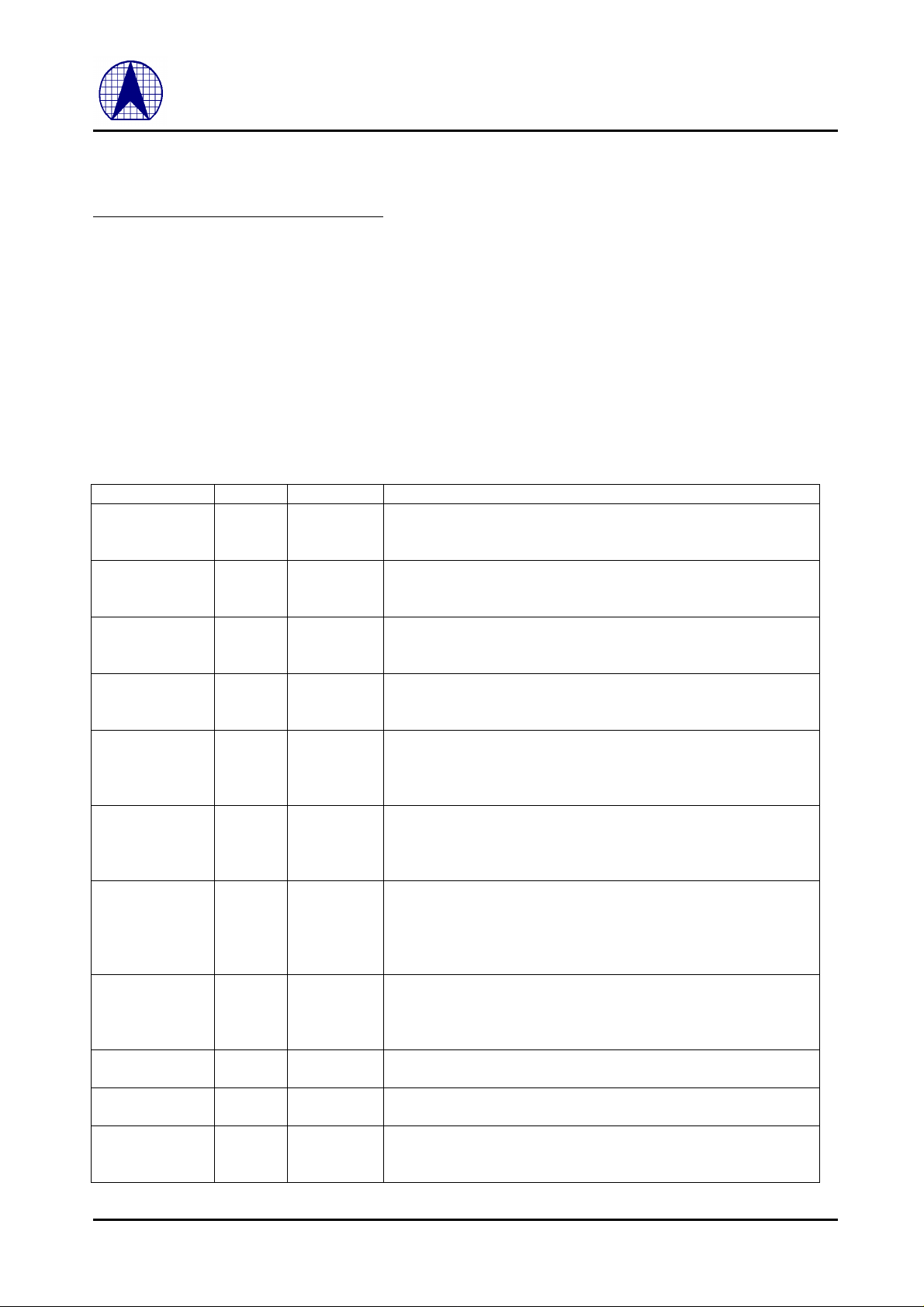

1.3.2 AX88195 Pin Connection Diagram for 80x86 Mode

SA[1]

HVDD

HVDD

SA[0]

SA[3]

SA[2]

SA[5]

SA[4]

SA[6]

SA[7]

SA[9]

SA[8]

/IOWR

SD[15]

SD[14]

SD[13]

SD[12]

SD[11]

SD[10]

SD[9]

SD[8]

SD[6]

SD[5]

SD[7]

/BHE

/IORD

TX_EN

TXD[1]

TXD[2]

TXD[3]

LVDD

CLKO25M

VSS

LCLK/XTALIN

XTALOUT

VSS

EECS

EECK

EEDI

EEDO

LVDD

SAL[0]

SAL[1]

SAL[2]

SAH[0]

SAH[1]

SAH[2]

SAX[0]

SAX[1]

VSS

NC

SAX[2]

SAX[3]

/CS

NC

RDY

/RESET

RESET

LVDD

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

TXD[0]

TX_CLK

96

95

94

VSS

93

MDC

MDIO

RXD[3]

RXD[2]

RXD[1]

90

8892858983

RXD[0]

CRS

RX_CLK

86

87

COL

84

AX88195

LOCAL CPU BUS

10/100BASE MAC

CONTROLLER

(for x86 Interface)

RX_DV

RX_ER

VSS

829181

MEMD[0]

MEMD[1]

MEMD[2]

MEMD[3]

78

77

797480

MEMD[4]

MEMD[5]

MEMD[6]

HVDD

75

73

76

MEMD[7]

72

MEMD[8]

MEMD[9]

MEMD[10]

VSS

71

70

68

69

MEMD[12]

MEMD[11]

MEMD[13]

66

65

67

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

HVDD

MEMD[14]

MEMD[15]

MEMA[1]

MEMA[2]

VSS

MEMA[3]

MEMA[4]

MEMA[5]

MEMA[6]

LVDD

MEMA[7]

MEMA[8]

MEMA[9]

MEMA[10]

VSS

MEMA[11]

MEMA[12]

MEMA[13]

MEMA[14]

LVDD

MEMA[15]

/MEMRD

/MEMWR

VSS

NC

SD[0]

SD[1]

SD[2]

SD[3]

VSS

SD[4]

3

4

1

2

Fig - 4 AX88195 Pin Connection Diagram for 80x86 Mode

8

7

6

5

9

10

11

VSS

IRQ

12

13

NC

15

14

7

16

17

NC

NC

19

18

24

21

23

22

20

VSS

ASIX ELECTRONICS CORPORATION

26

25

27

28

29

30

31

32

AX88195 Local CPU Bus Fast Ethernet MAC Controller

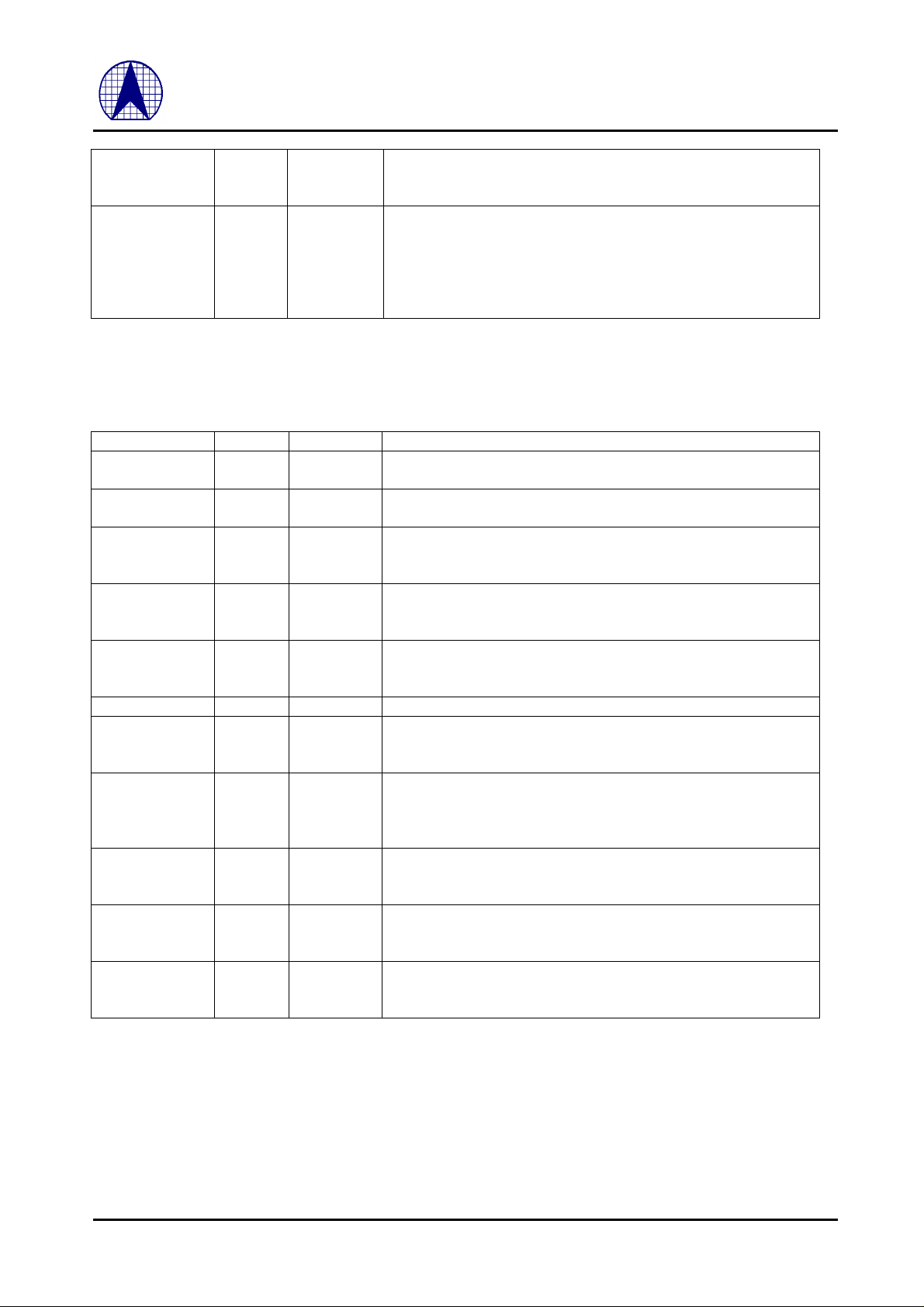

1.3.3 AX88195 Pin Connection Diagram for MC68K Mode

SA[1]

HVDD

HVDD

SA[3]

SA[2]

SA[5]

SA[4]

SA[6]

SA[7]

SA[9]

SA[8]

SD[15]

SD[14]

SD[13]

SD[12]

SD[11]

SD[10]

SD[9]

SD[8]

SD[6]

SD[5]

SD[7]

/LDS

/UDS

/IRQ

TX_EN

TXD[1]

TXD[2]

TXD[3]

LVDD

CLKO25M

VSS

LCLK/XTALIN

XTALOUT

VSS

EECS

EECK

EEDI

EEDO

LVDD

SAL[0]

SAL[1]

SAL[2]

SAH[0]

SAH[1]

SAH[2]

SAX[0]

SAX[1]

VSS

NC

SAX[2]

SAX[3]

/CS

NC

/DTACK

/RESET

RESET

LVDD

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

TXD[0]

TX_CLK

96

95

94

VSS

93

MDC

MDIO

RXD[3]

RXD[2]

RXD[1]

90

8892858983

RXD[0]

CRS

RX_CLK

86

87

COL

84

AX88195

LOCAL CPU BUS

10/100BASE MAC

CONTROLLER

(for 68K Interface)

3

4

1

2

8

7

6

5

9

12

13

11

10

RX_DV

RX_ER

VSS

829181

16

15

14

MEMD[0]

MEMD[1]

MEMD[2]

MEMD[3]

78

77

797480

19

17

20

18

MEMD[4]

MEMD[5]

MEMD[6]

HVDD

75

73

76

24

21

23

22

MEMD[7]

MEMD[8]

71

72

26

25

MEMD[9]

MEMD[10]

MEMD[11]

VSS

70

68

67

69

28

29

27

30

MEMD[12]

MEMD[13]

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

HVDD

MEMD[14]

MEMD[15]

MEMA[1]

MEMA[2]

VSS

MEMA[3]

MEMA[4]

MEMA[5]

MEMA[6]

LVDD

MEMA[7]

MEMA[8]

MEMA[9]

MEMA[10]

VSS

MEMA[11]

MEMA[12]

MEMA[13]

MEMA[14]

LVDD

MEMA[15]

/MEMRD

/MEMWR

VSS

NC

SD[0]

SD[1]

SD[2]

SD[3]

VSS

SD[4]

NC

NC

R/W

NC

VSS

VSS

NC

Fig - 5 AX88195 Pin Connection Diagram for MC68K Mode

8

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

1.3.4 AX88195 Pin Connection Diagram for MCS-51 Mode

SA[1]

VSS

HVDD

HVDD

SA[0]

SA[3]

SA[2]

SA[5]

SA[4]

SA[6]

SA[7]

SA[9]

SA[8]

/IOWR

SD[6]

SD[5]

SD[7]

/IORD

/IRQ

TX_EN

TXD[1]

TXD[2]

TXD[3]

LVDD

CLKO25M

VSS

LCLK/XTALIN

XTALOUT

VSS

EECS

EECK

EEDI

EEDO

LVDD

SAL[0]

SAL[1]

SAL[2]

SAH[0]

SAH[1]

SAH[2]

SAX[0]

SAX[1]

VSS

NC

SAX[2]

SAX[3]

/CS

/PSEN

NC

/RESET

RESET

LVDD

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

TXD[0]

TX_CLK

96

95

94

VSS

93

MDC

MDIO

RXD[3]

RXD[2]

RXD[1]

90

8892858983

RXD[0]

CRS

RX_CLK

86

87

COL

84

AX88195

LOCAL CPU BUS

10/100BASE MAC

CONTROLLER

(for 8051 Interface)

3

4

1

2

8

7

6

5

9

12

13

11

10

RX_DV

RX_ER

VSS

829181

16

15

14

MEMD[0]

MEMD[1]

MEMD[2]

MEMD[3]

78

77

797480

19

17

20

18

MEMD[4]

MEMD[5]

MEMD[6]

HVDD

75

73

76

24

21

23

22

MEMD[7]

MEMD[8]

MEMD[9]

71

72

70

26

25

MEMD[10]

VSS

68

69

28

29

27

MEMD[12]

MEMD[11]

MEMD[13]

66

65

67

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

HVDD

MEMD[14]

MEMD[15]

MEMA[1]

MEMA[2]

VSS

MEMA[3]

MEMA[4]

MEMA[5]

MEMA[6]

LVDD

MEMA[7]

MEMA[8]

MEMA[9]

MEMA[10]

VSS

MEMA[11]

MEMA[12]

MEMA[13]

MEMA[14]

LVDD

MEMA[15]

/MEMRD

/MEMWR

VSS

NC

SD[0]

SD[1]

SD[2]

SD[3]

VSS

SD[4]

VSS

NC

NC

NC

NC

NCNCNC

NC

NC

Fig - 6 AX88195 Pin Connection Diagram for MCS-51 Mode

9

ASIX ELECTRONICS CORPORATION

NCNCNC

AX88195 Local CPU Bus Fast Ethernet MAC Controller

2.0 Signal Description

The following terms describe the AX88195 pin-out:

All pin names with the “/” suffix are asserted low.

The following abbreviations are used in following Tables.

I Input PU Pull Up

O Output PD Pull Down

I/O Input/Output P Power Pin

OD Open Drain

2.1 Local CPU Bus Interface Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

SAL[2:0] I/PD 113 – 111 System Address Select Low : Signals SAL[2:0] are additional address

signal input lines which active low enable higher I/O address decoder

on chip.

SAH[2:0] I/PU 116 – 114 System Address Select High : Signals SAH[2:0] are additional

address signal input lines which active high enable higher I/O

address decoder on chip.

SAX[3:0] I/PU 122 – 121

118 – 117

SA[9:1],

SA[0]/UDS

/BHE

or

/LDS

SD[15:0] I/O 20 – 23,

IREQ/IREQ O 12 Interrupt Request : When ISA BUS or 80186 CPU mode is select.

RDY/DTACK OD 125 Ready : This signal is set low to insert wait states during Remote

/CS I 123 Chip Select

/IORD I 15 I/O Read :The host asserts /IORD to read data from AX88195 I/O

/IOWR

or

R/W

I 10 – 1 System Address : Signals SA[9:0] are address bus input lines which

I 18 Bus High Enable or Lower Data Strobe : Bus High Enable is active

25 – 28,

30 – 33,

35 – 38

I 14 I/O Write :The host asserts /IOWR to write data into AX88195 I/O

System Address Select Low/High : Signals SAX[3:0] are additional

address signal input lines which active low/high depend on power on

setting to enable higher I/O address decoder on chip.

lower I/O spaces on chip. SA[0] also means Upper Data Strobe

(/UDS) active low signal in 68K application mode.

low signal in some 16 bit application mode which enable high bus

(SD[15:8]) active. The signal also name as Lower Data Strobe (/LDS)

for 68K application mode.

System Data Bus : Signals SD[15:0] constitute the bi-directional

data bus.

IREQ is asserted high to indicate the host system that the chip

requires host software service. When MC68K or MCS-51 CPU

mode is select. /IREQ is asserted low to indicate the host system that

the chip requires host software service.

DMA transfer.

/Dtack : When Motorola CPU type is select, the pin is active low

inform CPU that data is accepted.

When the /CS signal is asserted, the chip is selected.

space. When Motorola CPU type is select , the pin is useless.

space. When Motorola CPU type is select, the pin is active high for

read operation at the same time.

10

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

/IOCS16 OD 120 I/O is 16 Bit Port : The /IOIS16 is asserted when the address at the

range corresponds to an I/O address to which the chip responds, and

the I/O port addressed is capable of 16-bit access.

AEN

or

/PSEN

Tab - 1 Local CPU bus interface signals group

I/PD 124 Address Enable : The signal is asserted when the address bus is

available for DMA cycle. When negated (low), AX88195 an I/O slave

device may respond to addresses and I/O command.

PSEN : This signal is active low for 8051 program access. For I/O

device, AX88195, this signal is active high to access the chip. This

signal is for 8051 bus application only.

2.2 MII interface signals group

SIGNAL TYPE PIN NO. DESCRIPTION

RXD[3:0] I 90 – 87 Receive Data : RXD[3:0] is driven by the PHY synchronously with

respect to RX_CLK.

CRS I 85 Carrier Sense : Asynchronous signal CRS is asserted by the PHY

when either the transmit or receive medium is non-idle.

RX_DV I 83 Receive Data Valid : RX_DV is driven by the PHY synchronously

with respect to RX_CLK. Asserted high when valid data is present on

RXD [3:0].

RX_ER I 82 Receive Error : RX_ER ,is driven by PHY and synchronous to

RX_CLK, is asserted for one or more RX_CLK periods to indicate to

the port that an error has detected.

RX_CLK I 86 Receive Clock : RX_CLK is a continuous clock that provides the

timing reference for the transfer of the RX_DV,RXD[3:0] and

RX_ER signals from the PHY to the MII port of the repeater.

COL I 84 Collision : this signal is driven by PHY when collision is detected.

TX_EN O 95 Transmit Enable : TX_EN is transition synchronously with respect to

the rising edge of TX_CLK. TX_EN indicates that the port is

presenting nibbles on TXD [3:0] for transmission.

TXD[3:0] O 99 – 96 Transmit Data : TXD[3:0] is transition synchronously with respect to

the rising edge of TX_CLK. For each TX_CLK period in which

TX_EN is asserted, TXD[3:0] are accepted for transmission by the

PHY.

TX_CLK I 94 Transmit Clock : TX_CLK is a continuous clock from PHY. It

provides the timing reference for the transfer of the TX_EN and

TXD[3:0] signals from the MII port to the PHY.

MDC O 92 Station Management Data Clock : The timing reference for MDIO.

All data transfers on MDIO are synchronized to the rising edge of this

clock. MDC is a 2.5MHz frequency clock output.

MDIO I/O/PU 91 Station Management Data Input / Output : Serial data input/output

transfers from/to the PHYs . The transfer protocol conforms to the

IEEE 802.3u MII specification.

Tab - 2 MII interface signals group

11

ASIX ELECTRONICS CORPORATION

AX88195 Local CPU Bus Fast Ethernet MAC Controller

2.3 EEPROM Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

EECS O 106 EEPROM Chip Select : EEPROM chip select signal.

EECK O 107 EEPROM Clock : Signal connected to EEPROM clock pin.

EEDI O 108 EEPROM Data In : Signal connected to EEPROM data input pin.

EEDO I/PU 109 EEPROM Data Out : Signal connected to EEPROM data output pin.

Tab - 3 EEPROM bus interface signals group

2.4 SRAM Interface pins group

SIGNAL TYPE PIN NO. DESCRIPTION

MEMA[15:1] O 43, 45 – 48,

50 –53’

55 – 58,

60 – 61

MEMD[15:0] I/O/PU 62 – 63,

65 – 68,

70 – 74,

76 – 80

/MEMRD O 42 SRAM Read

/MEMWR O 41 SRAM Write

SRAM Address :

SRAM Data :

Tab - 4 SRAM Interface pins group

2.5 Miscellaneous pins group

SIGNAL TYPE PIN NO. DESCRIPTION

LCLK/XTALIN I 103 CMOS Local Clock : A 25Mhz clock, +/- 100 ppm, 40%-60% duty

cycle.

Crystal Oscillator Input : A 25Mhz crystal, +/- 25 ppm can be

connected across XTALIN and XTALOUT.

XTALOUT O 104 Crystal Oscillator Output : A 25Mhz crystal, +/- 25 ppm can be

connected across XTALIN and XTALOUT. If a single-ended external

clock (LCLK) is connected to XTALIN, the crystal output pin should

be left floating.

CLKO25M O 101 Clock Output 25MHz : This clock is source from LCLK/XTALIN.

RESET I/PD 127 Reset

Reset is active high then place AX88195 into reset mode immediately.

During Falling edge the AX88195 loads the power on setting data.

User can select either RESET or /RESET for applications.

/RESET I/PU 126 /Reset

Reset is active low then place AX88195 into reset mode immediately.

During rising edge the AX88195 loads the power on setting data.

User can select either RESET or /RESET for applications.

NC N/A 13, 16, 17,39No Connection : for manufacturing test only.

LVDD P 44, 54,

100, 110,

128

Power Supply : +3.3V DC.

12

ASIX ELECTRONICS CORPORATION

Loading...

Loading...