ASIX AX81190 Datasheet

ASIX ELECTRONICS CORPORATION Ver. 0.7

4F, NO.8, Hsin ANN Rd., Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

TEL: 886-3-579-9500

FAX: 886-3-579-9558 http://www.asix.com.tw

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

802.11b PCI/CARDBUS/PCMCIA Bus WLAN MAC Controller

Document No.: AX81190-07 / V0.7 / MAR. 15 ’03

Features

• Single chip multiple bus WLAN MAC Controller

• IEEE 802.11b wireless LAN (WLAN) Compatible

• Compliant with 802.11b protocol such as DCF,

PCF, WEP, Power management, etc.

• Embedded two 8K * 16 bit SRAMs for Tx and Rx

Packet Buffers

• Compliant with PCI Bus Standard Ver 2.1(slave

mode)/PCMCIA Bus standard.

• Support PCI 16-bit accsee for Registers and 32-bit

accsee for Data

• Support both 1/2/5.5/11 Mbps data rate

• Support both full-duplex (Test) or half-duplex

operation

• Provides an industrial standard interface to

interface with baseband processer and IF/RF chips.

• Support 256 bytes EEPROM (used for saving

Configuration Information and address ID)

• Support automatic loading of MAC ID and Adapter

Configuration from EEPROM on power-on

initialization

• 128-pin TQFP low profile package

• 33/44MHz, 2.5Vcore/3.3V IO operation with 5V

tolerance

*IEEE is a registered trademark of the Institute of Electrical and

Electronic Engineers, Inc.

*All other trademarks and registered trademark are the property of their

respective holder.

Product description

The AX81190 is a high performance multiple bus WLAN MAC Controller. The AX81190 contains a 16 bit PCMCIA

interfaces (32-bit PCI/CARDBUS) to host CPU and compliant with PCMCIA Bus Standard Ver 2.2. The AX81190

implements

1Mbps, 2Mbps, 5.5Mbps and 11Mbps WLAN function based on DSSS (Direct Sequence Spread

Spectrum) of IEEE802.11 /IEEE802.11b WLAN standard. The AX81190 supports an industrial standard(such as Intersil

/RFMD/RaLink) interface for baseband processer and IF/RF chips to simplify the design.

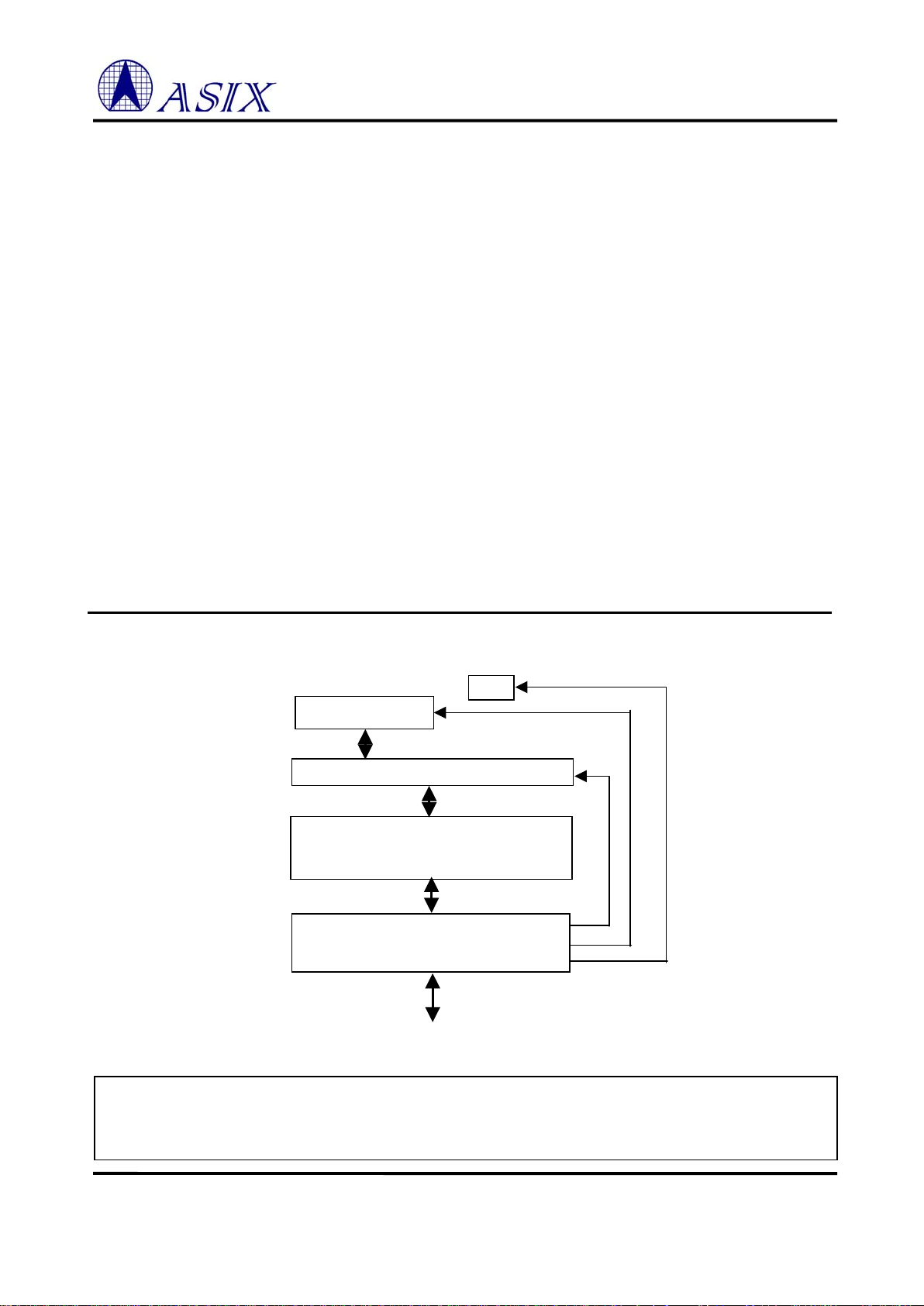

SYSTEM BLOCK DIAGRAM

Always contact ASIX for possible updates before starting a design.

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify product

specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent

accompany the sale of the product.

MAC -- AX81190

RaLink 2430 or

BB -- RFMD R3000 or

RF

PCI/CARDBUS

PCMCIA

ASIX ELECTRONICS CORPORATION

2

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

CONTENTS

1.0 INTRODUCTION ...........................................................................................................6

1.1 GENERAL DESCRIPTION ............................................................................................................6

1.2 AX81190 BLOCK DIAGRAM .................................................................................................6

1.3 AX81190 PIN CONNECTION DIAGRAM.......................................................................7

1.3.1 AX88119 Pin Connection Diagram for PCMCIA Bus Mode ..............................7

1.3.2 AX81190 Pin Connection Diagram for PCI/CardBus Mode...............................8

2.0 SIGNAL DESCRIPTION ...................................................................................9

2.1 PCMCIA BUS INTERFACE SIGNALS GROUP........................................................... 9

2.2 PCI/CARDBUS BUS INTERFACE SIGNALS GROUP .......................................10

2.3 EEPROM SIGNALS GROUP..................................................................................................11

2.4 SERIAL PORT INTERFACE SIGNALS GROUP............................................................11

2.5 BASEBAND PROCESSER CONTROLLER INTERFACE SIGNALS GROUP11

2.6 POWER CONTROL INTERFACE SIGNALS GROUP ................................................12

2.7 SYNTHESIZER CONTROL SIGNAL INTERFACE PINS GROUP ........................12

2.8 MISCELLANEOUS PINS GROUP............................................................................................ 12

3.0 REGISTERS OPERATION .........................................................................14

3.1 PCI CONFIGURATION REGISTER......................................................................................14

3.1.1 Device vendor register -- offset 00h .................................................................................14

3.1.2 Command register – offset 04h ...........................................................................................14

3.1.3 Status register – offset 06h..................................................................................................... 14

3.1.4 Revision ID register – offset 08h........................................................................................14

3.1.5 Class code register – offset 09h.......................................................................................... 15

3.1.6 Base IO address register – offset 10h..............................................................................15

3.1.7 Base Memory address register – offset 14h.................................................................15

3.1.8 CIS pointer – offset 28h ...........................................................................................................15

3.1.9 Subsystem ID – 2Ch................................................................................................................... 15

3.1.10 Interrupt register – 3Ch........................................................................................................15

3.2 PCMCIA CONFIGURATION REGISTER....................................................................... 16

3.2.1 COR register – 0800h............................................................................................................... 16

3.2.2 CCR register – 0802h.............................................................................................................. 16

3.2.3 IO base (LSB) – 0804h............................................................................................................. 16

3.2.4 IO base (MSB) – 0806h............................................................................................................16

3.3 IO PORT..................................................................................................................................................17

3.3.1 CSR index port base................................................................................................17

ASIX ELECTRONICS CORPORATION

3

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

3.3.2 CSR data port base + 2.............................................................................................17

3.3.3 Tx Data access control port base + 4............................................................. 17

3.3.4 Tx data buffer port base + 6............................................................................. 17

3.3.5 Rx Data access control port base + 8............................................................. 17

3.3.6 Rx data buffer port base + ah ...........................................................................17

3.3.7 Soft reset port base + eh .............................................................................................17

3.3.8 Interrupt status port base + 10h ...........................................................................17

3.3.9 Interrupt mask port base + 12h ........................................................................... 18

3.3.10 Rx page status port base + 14h........................................................................18

3.3.11 Tx page status port1 base + 16h .....................................................................18

3.3.12 Tx page status port2 base + 18h .....................................................................19

3.3.13 BBP_index port base + 1ah ............................................................................19

3.3.14 BBP_data out port base + 1ch .........................................................................19

3.3.15 BBP_data in port base + 1eh .............................................................................19

3.3.16 Synthesizer control port base + 20h .............................................................19

3.3.17 Synthesizer data port0 base + 22h.................................................................19

3.3.18 Synthesizer data port1 base + 24h.................................................................19

3.3.19 EE_data port base + 26h..................................................................................20

3.3.20 EE_cmd/addr port base + 28h ...................................................................... 20

3.3.21 EE_status_type port base + 2ah .....................................................................20

3.4 MAC CONFIGURATION STATUS REGISTERS.........................................................21

3.4.1 CSR1 – MAC Physical address0 (PADR[15:0])....................................................... 21

3.4.2 CSR2 – MAC Physical address1 (PADR[31:16])....................................................21

3.4.3 CSR3 – MAC Physical address2 (PADR[47:32])....................................................21

3.4.4 CSR4 – BSSID Matching Register0, BSSID[15:0]..................................................21

3.4.5 CSR5 – BSSID Matching Register1, BSSID[31:16]............................................... 21

3.4.6 CSR6 – BSSID Matching Register2, BSSID[47:32]............................................... 21

3.4.7 CSR7 ~ CSR9 are reserved. .................................................................................................21

3.4.10 CSR10 – Multicast filter pattern1................................................................................... 21

3.4.11 CSR11 – Multicast filter pattern2................................................................................... 21

3.4.12 CSR12 – Multicast filter pattern3................................................................................... 21

3.4.13 CSR13 – Multicast filter pattern4................................................................................... 21

3.4.12 CSR14 ~ CSR15 are reserved. .......................................................................................22

3.4.16 CSR16 – clock pattern.......................................................................................................... 22

3.4.17 CSR17 – Wait md_rdy duration...................................................................................... 22

3.4.18 CSR18 – Short Interframe space timing register ,SIFS.................................... 22

3.4.19 CSR19 – Distributed Interframe space timing register, DIFS/PIFS......... 22

3.4.20 CSR20 ~ CSR 21 – Reserved. ............................................................................................22

3.4.22 CSR22 – SlotTime Register (SLOT) .............................................................................22

3.4.23 CSR23 – Backoff timing........................................................................................................22

3.4.24 CSR24 – RF3000 modulation duration (Testing)..................................................22

3.4.25 CSR25 – Power Testing and misc...................................................................................22

ASIX ELECTRONICS CORPORATION

4

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

3.4.26 CSR26 – TXVGC adjust register (support RF3000 only).................................23

3.4.27 CSR27 – Tx Beacon/probe response enable register ..........................................23

3.4.28 CSR28 – TBTT Compensation Register ......................................................................23

3.4.29 CSR29 – Rx filtering Register ...........................................................................................23

3.4.30 CSR30 – TX Power Ramp-up Control Register1................................................... 24

3.4.31 CSR31 – TX Power Ramp-up Control Register2................................................... 24

3.4.32 CSR32 – TX Power Ramp Control Register3 ..........................................................24

3.4.33 CSR33 – TX Power Ramp Control Register4 ..........................................................24

3.4.34 CSR34 – TX Power Ramp Control Register5 ..........................................................24

3.4.35 CSR35 – BeaconPeriod (BP).............................................................................................24

3.4.36 CSR36 – Tx Retry counter ...................................................................................................24

3.4.37 CSR37 – MAC feature register......................................................................................... 24

3.4.38 CSR38 is Reserved ...................................................................................................................25

3.4.39 CSR39 – Transmit page control register.................................................................... 25

3.4.40 CSR40 – TX Rate control register.................................................................................. 25

3.4.41 CSR41 – response time-out register ..............................................................................26

3.4.42 CSR42 – RSSI-SQ location register...............................................................................26

3.4.43 CSR43 – TSF compensate register................................................................................. 26

3.4.44 CSR44 – Calibration adjust register.............................................................................26

3.4.45 CSR45 – BBP PLCP Service/Signal field location register ( for Intersil

3861/3863)

...................................................................................................................................................26

3.4.46 CSR46 – BBP PLCP Length field location register (for Intersil

3861/3863)

...................................................................................................................................................26

3.4.47 CSR47 is Reserved ...................................................................................................................27

3.4.48 CSR48 – Software reset duration.................................................................................... 27

3.4.49 CSR49 – CFP duration register.......................................................................................27

3.4.50 CSR50 – ATIM duration register ....................................................................................27

3.4.51 CSR51 – 802.11 protocol status.......................................................................................27

3.4.52 CSR52 – MAC mode status................................................................................................. 27

3.4.53 CSR53 – BBP mode.................................................................................................................27

3.4.54 CSR54 – SPI chip address...................................................................................................28

3.4.55 CSR55 ~ CSR59 reserved ................................................................................................... 28

3.4.60 CSR60 CRC32 counter.......................................................................................................... 28

3.4.61 CSR61 is reserved.................................................................................................................... 28

3.4.62 CSR62 – NAV timer.................................................................................................................28

3.4.63 CSR63 – TSF timer register0 (TSFR[15:0]) ............................................................28

3.4.64 CSR64 – TSF timer register1 (TSFR[31:16]).......................................................... 28

3.4.65 CSR65 – TSF timer register2 (TSFR[47:32]).......................................................... 28

3.4.66 CSR66 – TSF timer register3 (TSFR[63:48]).......................................................... 28

3.4.67 CSR67 ~ CSR69 Reserved................................................................................................... 28

3.4.70 CSR70 – Not my unicast frame counter.......................................................................28

3.4.71 CSR71 – broadcast and multicast counter ................................................................29

ASIX ELECTRONICS CORPORATION

5

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

3.4.72 CSR72 – RSSI-SQ value........................................................................................................ 29

3.4.73 CSR73 – Outbuf/Inbuf current page pointer ............................................................29

3.4.74 CSR74: TX Power Ramp-down Control Register1...............................................29

3.4.75 CSR75: TX Power Ramp-down Control Register2...............................................29

3.4.76 CSR76: TX Power Ramp-down Control Register3...............................................29

3.4.77 CSR77: TX Power Ramp-down Control Register4...............................................29

3.4.78 CSR78: RX_PE de-asserted duration........................................................................... 29

3.4.79 CSR79: Min size of RX packet ..........................................................................................30

3.4.80 CSR80: GPIO status control.............................................................................................. 30

3.4.81 CSR81: GPIO data port........................................................................................................ 30

3.4.82 CSR82: wep control ................................................................................................................30

3.4.83 WEP key matrix (csr83 ~ csr110, 16 bit registers)............................................... 30

4.0 PCMCIA DEVICE ACCESS FUNCTIONS.................... 31

4.1 ATTRIBUTE MEMORY ACCESS FUNCTIONS............................................................ 31

4.2 I/O ACCESS FUNCTIONS...........................................................................................................31

5.0 ELECTRICAL SPECIFICATION AND

TIMINGS

.................................................................................................................................................32

5.1 ABSOLUTE MAXIMUM RATINGS...................................................................................... 32

5.2 GENERAL OPERATION CONDITIONS.............................................................................32

5.3 DC CHARACTERISTICS............................................................................................................. 32

5.4 A.C. TIMING CHARACTERISTICS.....................................................................................33

5.4.1 CLOCK.............................................................................................................................................. 33

5.4.2 PCMCIA Reset Timing............................................................................................................. 33

5.4.3 PCMCIA Attribute Memory Read Timing..................................................................... 34

5.4.4 PCMCIA Attribute Memory Write Timing....................................................................35

5.4.5 PCMCIA I/O Read Timing.....................................................................................................36

5.4.6 PCMCIA I/O Write Timing.................................................................................................... 37

5.4.7 Synthesizer Timings.................................................................................................................... 38

5.4.8 Serial Port Timings ....................................................................................................................39

5.4.9 TX Path Waveforms....................................................................................................................40

5.4.10 RX Path Waveforms ................................................................................................................ 41

6.0 PACKAGE INFORMATION....................................................................42

APPENDIX A: APPLICATION NOTE 1........................................ 43

A.1 EXTERNAL EEPROM FORMAT .......................................................................................43

ASIX ELECTRONICS CORPORATION

6

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

1.0 Introduction

1.1 General Description

The AX81190 Wireless LAN Controller is a high performance PCMCIA/PCI bus WLAN Controller. The

AX81190 contains a 16 bit PCMCIA (32 bit PCI) interfaces to host CPU. The AX81190 implement 1Mbps,

2Mbps, 5.5Mbps and 11Mbps WLAN function based on IEEE802.11 /IEEE802.11b WLAN standard. The

AX81190 supports indudtrial standard MAC to Baseband controller interface to simplify the design. The

AX81190 is built in two 8K*16 bit SRAM for Tx and Rx packet buffer to reduce system cost and size.

AX81190 is also implemented WEP (hardwared) function, supports 64/128 bit key to reduce computing

load of CPU.

AX81190 use 128-pin TQFP low profile package, 33/44MHz operation frequency, 2.5V core/3.3V CMOS

process with 5V I/O tolerance.

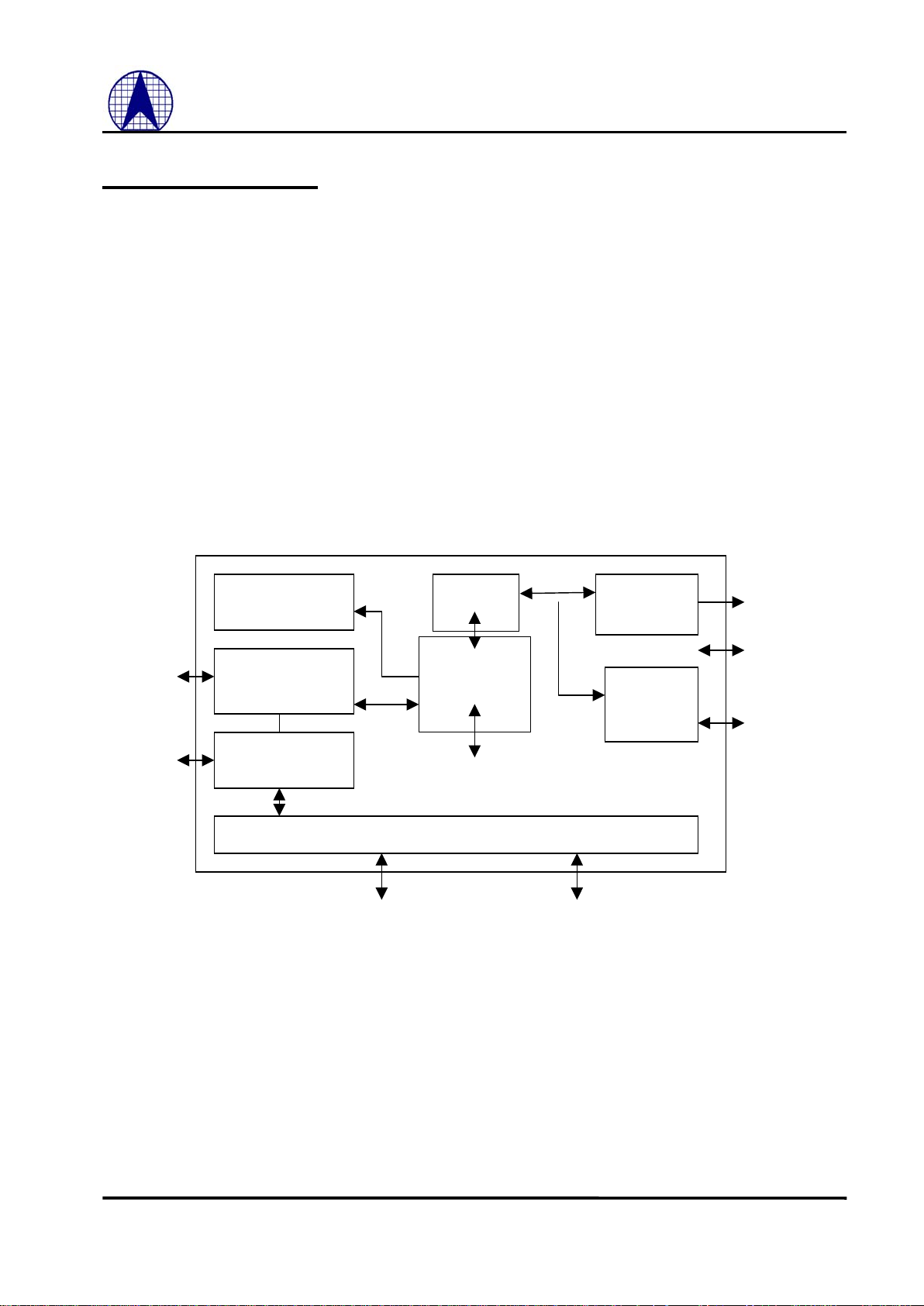

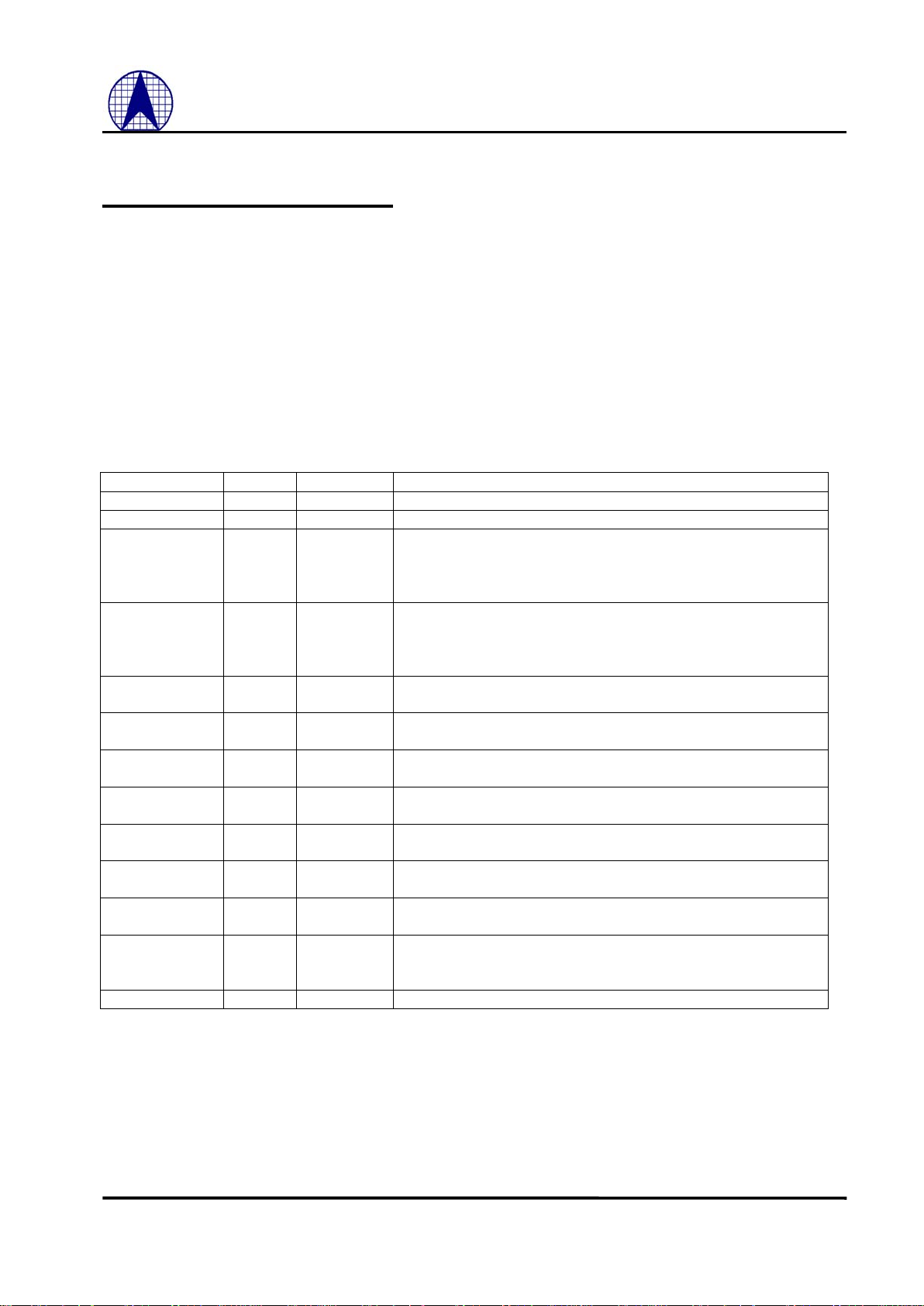

1.2 AX81190 Block Diagram

Two 8K*16 SRAM

MAC

Engine

S-EEPROM

LOADER IF

Registers

Buffer

Management

And FIFO

Power

Controller

Serial

I/F

Host Interface

EECS

EECLK

EEDI

EEDO

GPIO

PA_PE

. . .

BBP I/F

RF I/F

Ctrl BUS AD[31:0]

ASIX ELECTRONICS CORPORATION

7

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

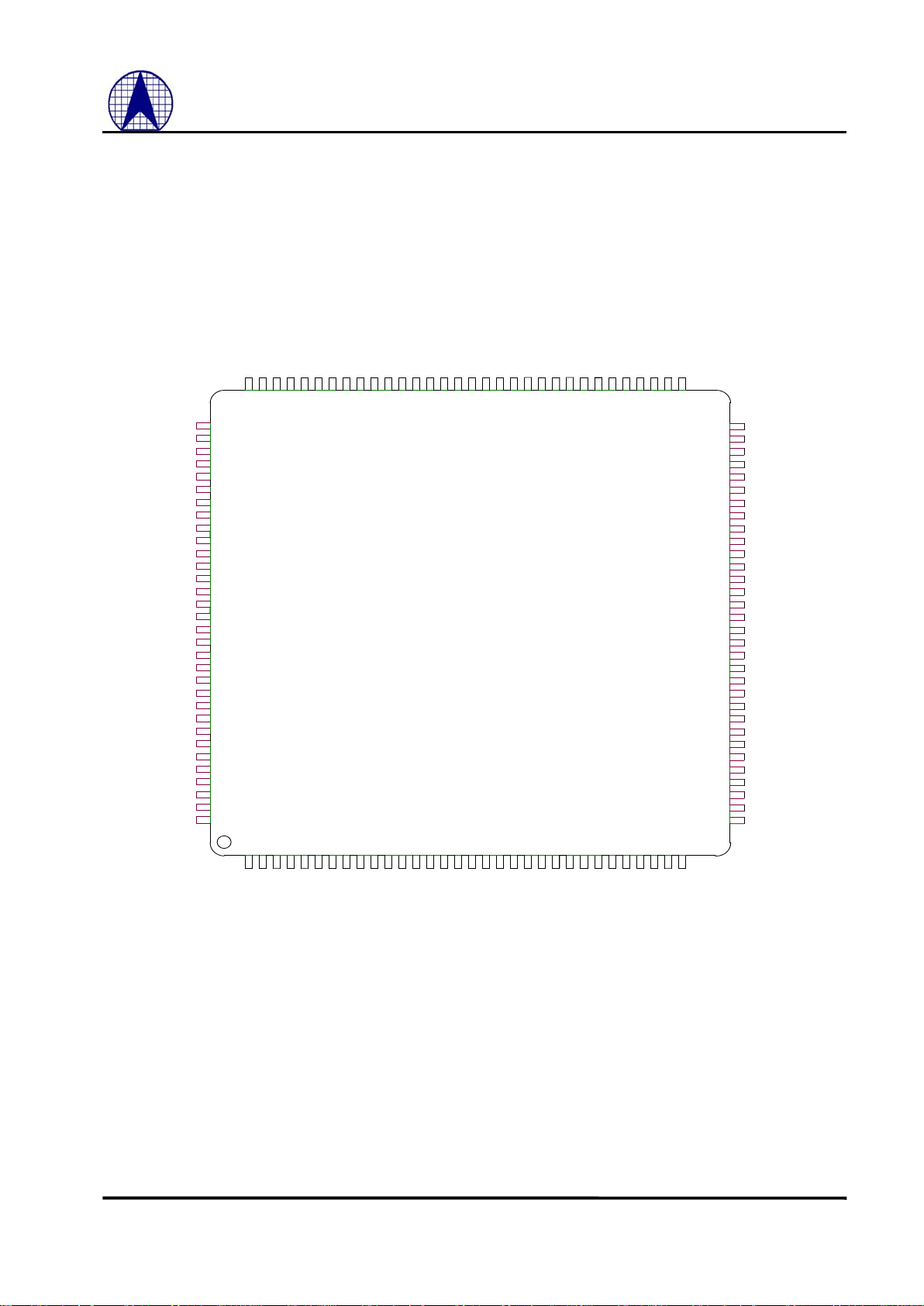

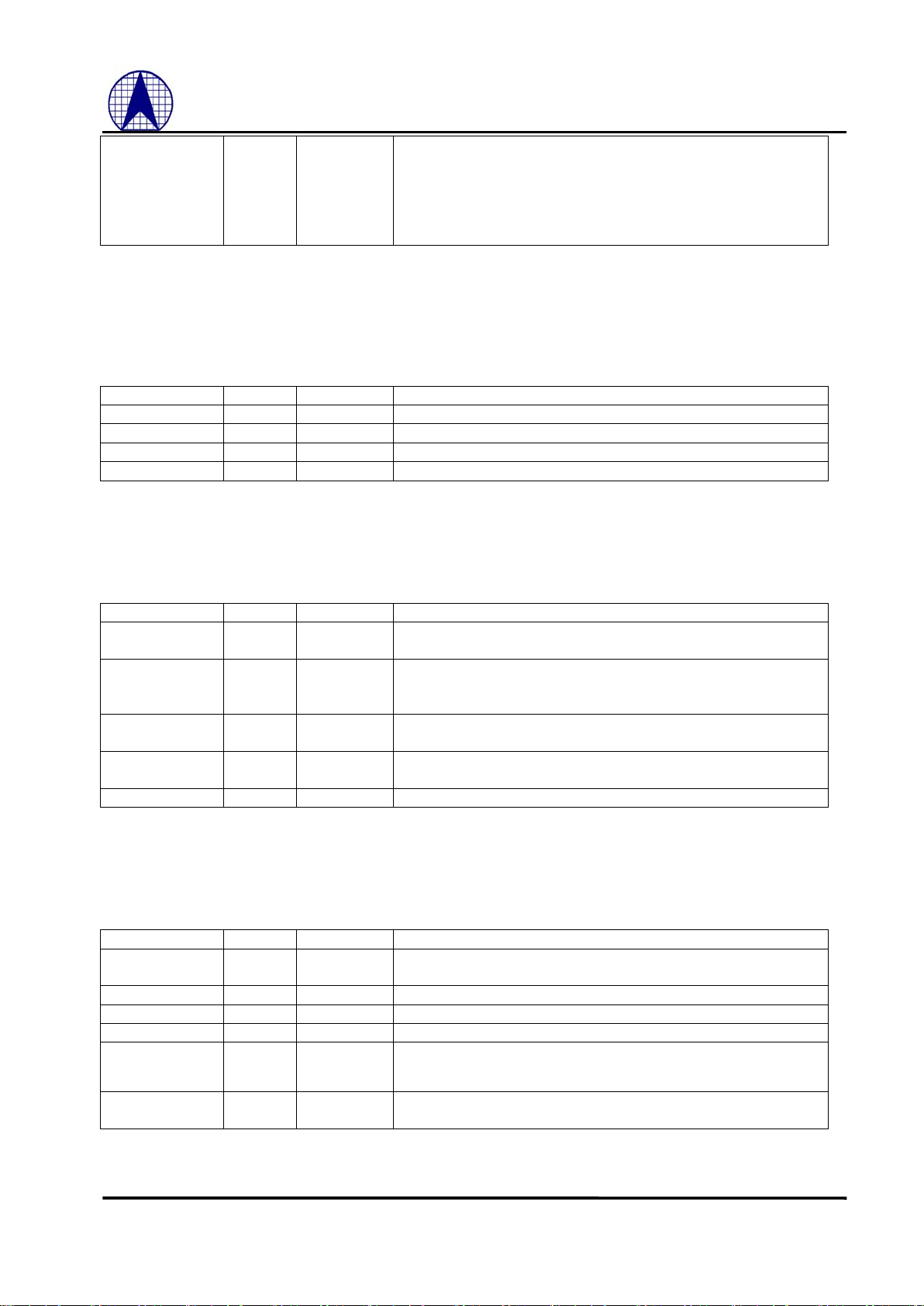

1.3 AX81190 Pin Connection Diagram

The AX81190 is housed in the 128-pin plastic quad flat pack

Fig - 1 AX81190 Pin Connection

Diagram

shows the AX81190 pin assignment.

1.3.1 AX88119 Pin Connection Diagram for PCMCIA Bus Mode

Fig - 1 AX81190 Pin Connection Diagram for PCMCIA Bus Mode

VSS1

IREQ#

10

VSS1

EEPM_DIS

TXD

A15

EECS

VSS1

GPIO2

GPIO0

SPI_DO

120

90

101

D8

81

51

62

86

A13

115

36

100

29

23

14

CCA

RF_PE

70

VDD2

GPIO3

LED1

40

D3

PE2

116

VSS1

BBPMODE0

D7

VSS2

D12

105

2

55

11

21

REG#

EECL

K

VDD2

SYNCLK

106

13

LED2

33

LE_IF#

99

CS#

117

D11

43

73

41

127

71

VDD1

SCLK

6

VDD2

D15

HRST

D1

AX81190

A3

78

92

MD_RDY

RSTPHY#

WE#

25

BBPMODE1 A1

VSS2

60

93

102

104

111

GPIO4

125

31

95

A14

VDD2

16

66

97

80

4

118

89

109

61

3

( PCMCIA )

TXCLK

67

NC

VSS1

82

49

12

VDD2

WAIT#

A5

34

D6

32

HBUSMODE

27

56

D0

108

OE#

MT0

A8

103

SYNDATA

CBSE

L

RX_PE

IOIS16#

91

69

PA_PE

85

A4

A0

VDD1

A2

44

57

48

VDD2

75

64

126

EED

O

MT1

113

79

RXCLK

84

VSS2

110

128

119

VDD1

RXD

NC

D14

VDD1

114

83

53

98

26

VDD1

VDD2

30

19

63

TX_RDY

EED

I

VDD1

SD

VSS2

65

VSS1

A11

VSS1

15

112

A6

VDD1

38

TX_PE

68

VSS1

77

D13

VSS2

D9

45

24

20

22

50

LE_RF#

47

NC

VDD1

8

124

39

88

121

59

D2

RW#

VSS2

VSS1

CAL_EN

VSS2

VSS1

37

TR_SW#

76

GPIO1

52

IORD#

94

42

IOWR#

96

7

VDD2

35

A7

107

87

D5

VDD1

46

A12

122

D4

CE1#

TR_SW

18

VSS2

NC

74

17

1

9

A9

D10

54

PE1

HCLK

GPIO5

72

A10

28

58

123

NC

5

ASIX ELECTRONICS CORPORATION

8

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

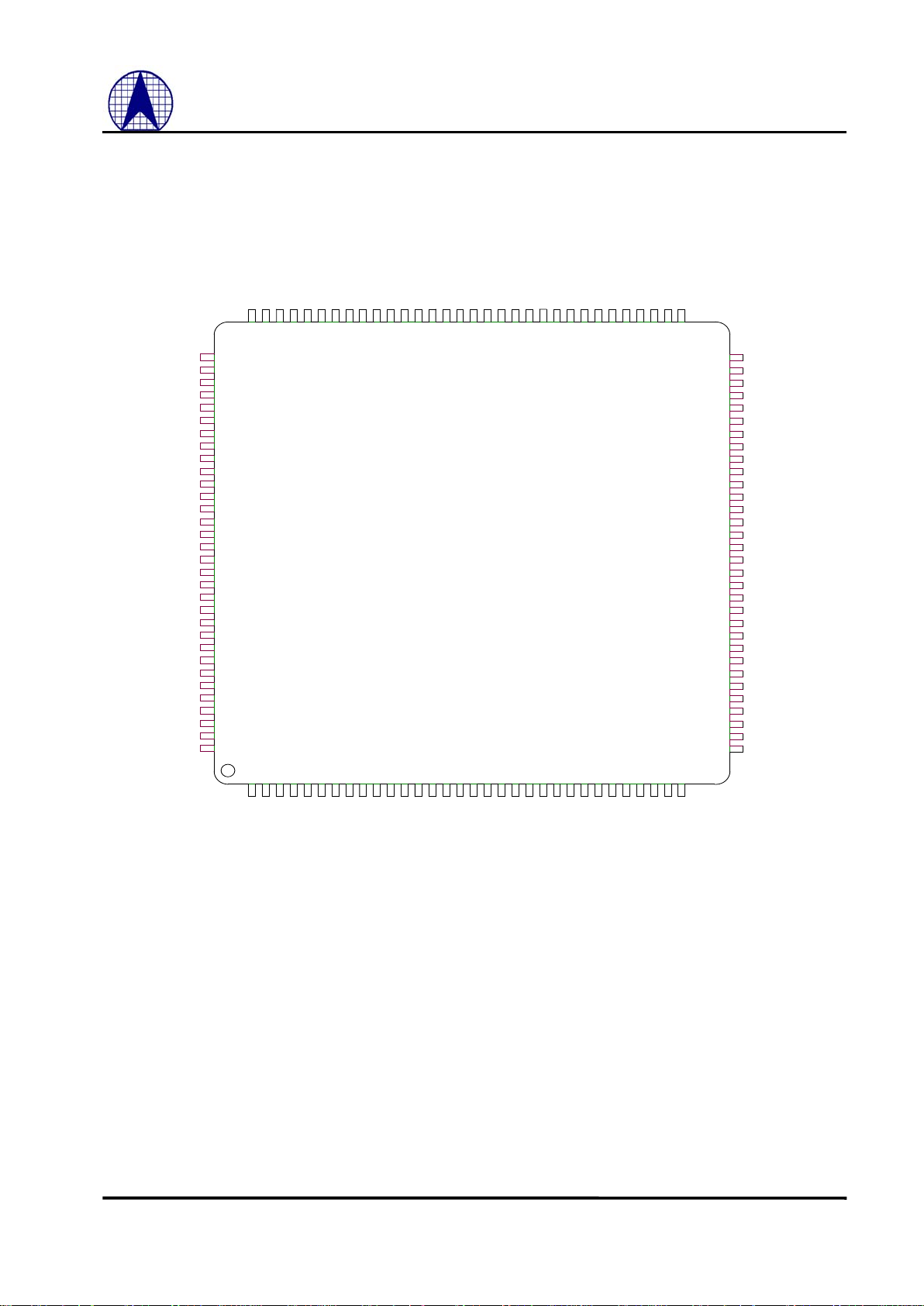

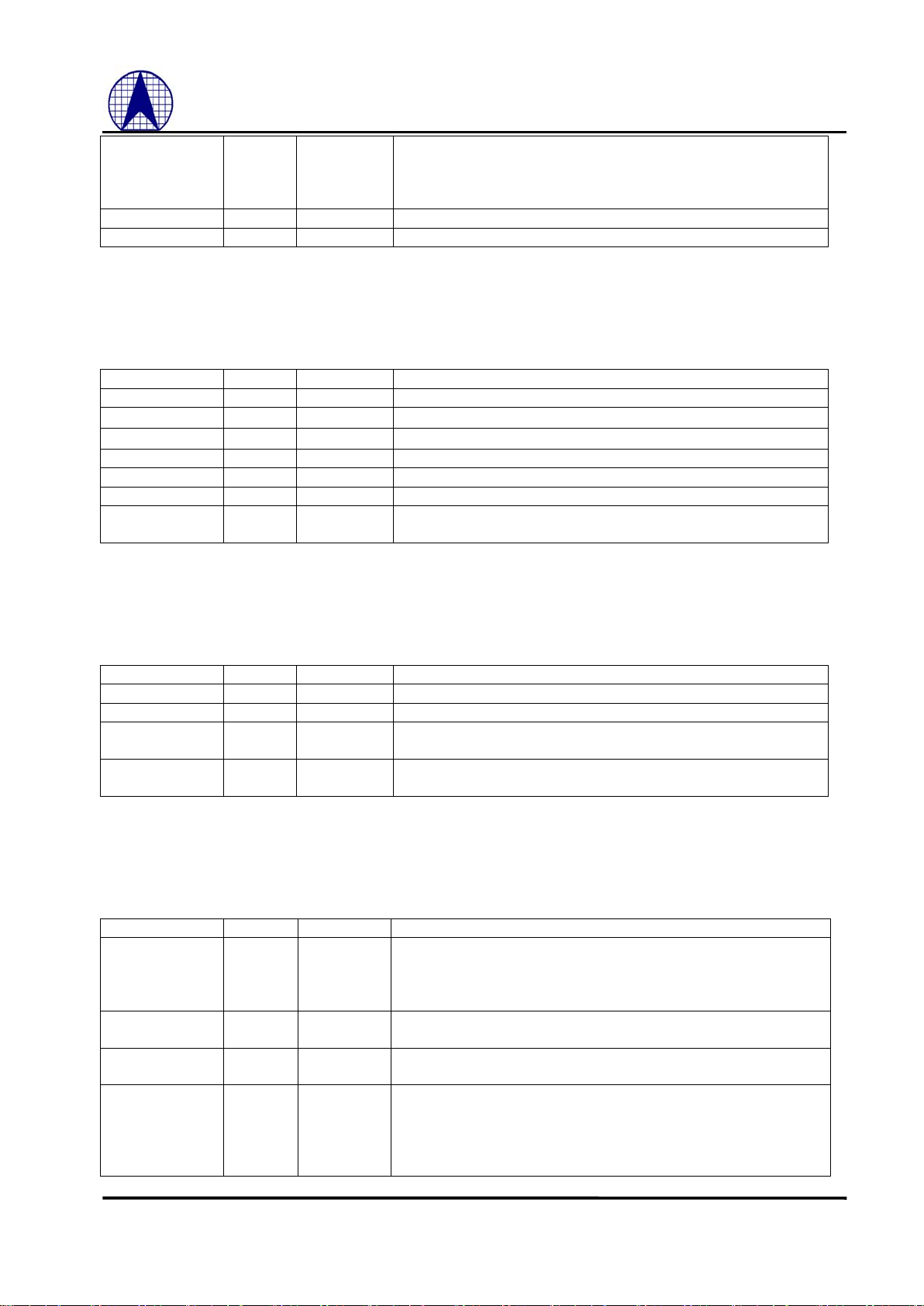

1.3.2 AX81190 Pin Connection Diagram for PCI/CardBus Mode

Fig - 2 AX81190 Pin Connection Diagram for PCI/CARDBUS

AD0

59

121

RF_PE

RSTPHY#

109

98

VDD1

PERR#

VSS1

74

99

50

EECL

K

26

AD12

9

PAR

93

GPIO3

VSS2

AD30

VDD1

AD5

86

AD7

AD2

STOP#

NC

120

AD14

VSS2

SD

AX81190

34

6

MT0

RX_PE

CS#

76

84

44

29

32

VSS1

RXCLK

15

AD9

111

78

21

83

123

68

AD20

AD19

70

RW#

91

VSS1

100

7

105

VSS2

128

PA_PE

107

IRDY#

EECS

BBPMODE0

75

46

16

19

CXBE0

#

39

TR_SW#

106

SYNDATA

CBSE

L

VDD1

AD15

8

127

31

AD21

TX_RDY

PE1

73

VSS1

67

63

GPIO5

VSS1

90

VDD1

3

22

47

18

AD11

AD28

125

13

AD17

79

81

( PCI )

115

AD26

HBUSMODE

57

2

17

AD29

VDD2

112

20

117

AD16

AD6

1

95

AD8

49

55

27

AD22

LE_IF#

116

102

60

HRST#

LE_RF#

EEPM_DIS

69

TRDY#

66

35

23

VDD2

AD1

10

MT1

77

VDD2

SYNCLK

124

VDD1

CCA

AD31

48

TXCLK

89

126

GPIO2

CXBE1

#

103

43

DEVSEL#

VSS1

VDD1

AD13

11

VSS1

28

37

53

62

VSS2

GPIO4

AD25

36

114

14

EED

I

AD18

52

87

CXBE2#

108

30

96

CAL_EN

113

TX_PE

FRAME#

VDD2

65

58

GPIO1

INTR#

VSS2

TXD

AD23

RXD

92

41

45

AD4

VSS2

122

SPI_DO

VSS2

82

85

119

38

HCLK

88

PE2

VDD2

42

64

110

CXBE3#

101

AD10

5

VDD1

LED2

94

AD24

80

12

VSS1

VSS1

VDD2

71

VSS2

25

EED

O

VSS1

VDD2

MD_RDY

TR_SW

72

54

24

IDSEL

SCLK

51

104

VDD2

BBPMODE1

VDD1

97

GPIO0

56

LED1

61

40

VDD1

AD27

33

4

AD3

118

ASIX ELECTRONICS CORPORATION

9

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

2.0 Signal Description

The following terms describe the AX81190 pin-out:

All pin names with the “#” suffix are asserted low.

The following abbreviations are used in following Tables.

I Input PU Internal Pull Up

O Output PD Internal Pull Down

I/O Input/Output P Power Pin

OD Open Drain

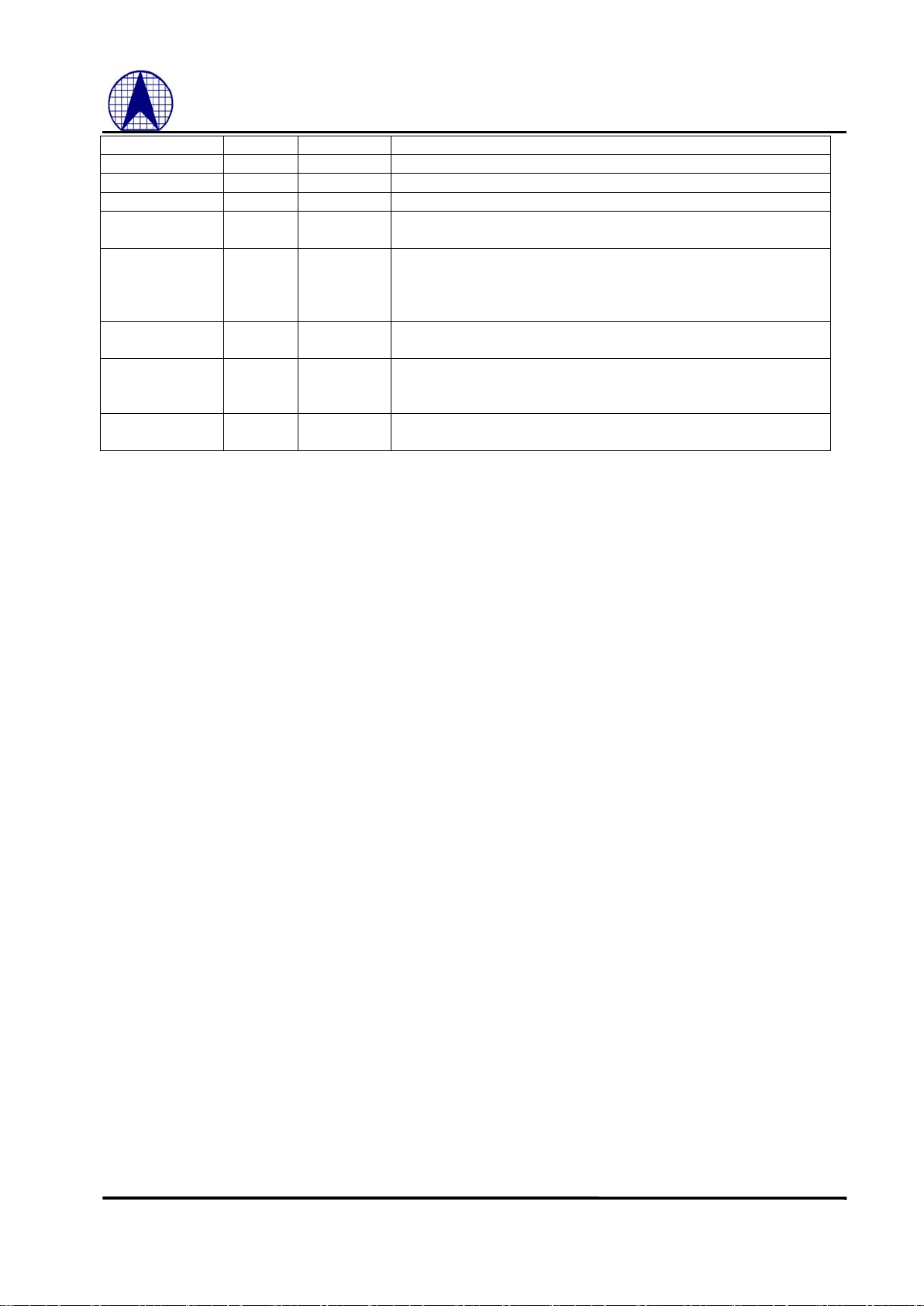

2.1 PCMCIA Bus Interface Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

HCLK I 28 Reference clock. 33Mhz or 44Mhz.

HRST I 26 Reset signal. Active high for PCMCIA.

A[15:0] I 61,62,33,34,

36,37,39,40,

44,45,46,47,

49,50,52,53

System Address : Signals A[15:0] are address bus input lines which

enable direct address of up to 64K memory and I/O spaces on card.

D[15:0] I/O 68,69,70,73,

74,76,77,78,

81,83,84,85,

86,88,89,91

System Data Bus : Signals D[15:0] constitute the bi-directional data

bus.

IREQ# O 24 Interrupt Request : IREQ# is asserted to indicate the host system that

the PC Card device requires host software service.

WAIT# O 64 Wait : This signal is set low to insert wait states during Remote DMA

transfer.

REG# I 42 Attribute Memory and I/O Space Select : When the REG# signal is

asserted, access is limited to Attribute Memory and to the I/O space.

IORD# I 55 I/O Read : The host asserts IORD# to read data from AX81190 I/O

space.

IOWR# I 41 I/O Write : The host asserts IOWR# to write data into AX81190 I/O

space.

OE# I 32 Output Enable : The OE# line is used to gate Memory Read data from

memory on PC Card

WE# I 30 Write Enable : The WE# signal is used for strobing Memory Write

data into the memory on PC Card.

IOIS16# O 56 I/O is 16 Bit Port : The IOIS16# is asserted when the address at the

socket corresponds to an I/O address to which the card responds, and

the I/O port addressed is capable of 16-bit access.

CE1# I 80 Card Enable : The CE1# enables even numbered address bytes.

PCMCIA bus interface signals group

ASIX ELECTRONICS CORPORATION

10

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

2.2 PCI/CARDBUS Bus Interface Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

HCLK I 28 The clock provides the timing for the AX81190 related PCI bus

transactions. All the bus signals are sampled on the rising edge of

HCLK. The max frequency is 33MHz.

HRST# I 26 Resets the AX81190 to its initial state. This signal must be asserted

for at least 10 active PCI clock cycles. When is the reset state, all PCI

output pins are put into tri-state and all PCI o/d signals are floated.

FRAME# I/O 56 The FRAME# Signal is driven by the master to indicate the beginning

and duration of an access. FRAME# Asserts to indicate the beginning

of a bus transaction. While FRAME# is asserted, data transfers

continue. When FRAME# deasserts the next data phase is the final

data phase transaction.

IRDY# I/O 58

Initiator ready Indicates the bus master ability to complete the

current data phase of the transaction.

A data phase is completed on any rising edge of the clock When both

IRDY# and target ready TRDY# are asserted. Wait cycles are

inserted until both IRDY# and TRDY# are asserted together.

TRDY# I/O 59 Target ready indicates the target ability to complete the current data

p

hase of the transaction. A data phase is completed on any clock when

b

oth TRDY# and IRDY# are asserted. Wait cycles are inserted until

both IRDY# and TRDY# are asserted together.

DEVSEL# I/O 61 Device select Is asserted by the AX81190 of the current bus access hit

to AX81190

STOP# I/O 62 Stop indicator indicates that the current target is requesting the bus

master to stop the current transaction.

PAR I/O 65 Parity is an even parity bit for the AD[31:0] AD and CXBE[3:0]#.

During address and data phases, parity is calculated on all the

AD[31:0] AND CXBE[3:0]# lines whether or not any of these lines

carry meaningful information.

IDSEL I 42 Initialization devise select asserts To indicate that the host is issuing a

configuration cycle to the AX81190. For cardbus application, this pin

always is pulled high with VDD1.

AD[31:0] I/O 30,32,33,34,

36,37,39,40,

44,45,46,47,

49,50,52,53,

68,69,70,73,

74,76,77,78,

81,83,84,85,

86,88,89,91

Address and data bits are multiplexed on the same pins. During the

address phase, the AD[31:0] contain a physical address (32 bits).

During, data phases, AD[31:0] contain 32 bits of data.

CXBE[3:0]# I/O 41,55,66,80 BUS COMMAND and BYTE ENABLE Are multiplexed on the same

PCI pins. During the address phase of the transaction, CXBE[3:0]#

Provide the BUS COMMAND. During the data phase, CXBE[3:0]#

Provide the BYTE ENABLE. The BYTE ENABLE determines

which byte lines carry valid data., CXBE0# Applies to byte 0, and

CXBE3# Applies to byte 3.

PERR# I/O 63 Parity error asserts when a data parity error is detected. when a parity

error is detected, the AX81190 asserts PERR#. This pin must be

pulled up with VDD2 by an external resistor.

ASIX ELECTRONICS CORPORATION

11

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

INTR# O/D 24 Interrupt request asserts When one of the appropriate bits of Interrupt

Status Register sets and causes an interrupt, provided that the

corresponding mask bit in Interrupt Mask Register is not asserted.

Interrupt request deasserts by writing an “1” into the appropriate

Interrupt Status Register bit.

This pin must be pulled up with VDD2 by an external resistor.

PCI/CARDBUS bus interface signals group

2.3 EEPROM Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

EECS O 96 EEPROM Chip Select : EEPROM chip select signal.

EECLK O 94 EEPROM Clock : Signal connected to EEPROM clock pin.

EEDI O 93 EEPROM Data In : Signal connected to EEPROM data input pin.

EEDO I/PD 92 EEPROM Data Out : Signal connected to EEPROM data output pin.

EEPROM bus interface signals group

2.4 Serial Port Interface Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

SCLK O 9 SCLK is the clock for SD serial bus. The data on SD is latched in

rising edge.

SD I/O/PD 10 SD is serial bi-directional data bus, which is used to transfer address

and data to/from BBP internal register for Intersil type BBP.

This signal is input only for RFMD type BBP.

SPI_DO O 12 SPI_DO is serial data output only bus, which is used to transfer

address and data to RFMD type BBP.

RW# O 7 To control the direction when MAC reads or writes data on SD bus. A

high level indicates a read cycle and low level indicates a write cycle.

CS# O 8 MAC selects BBP to be as target.

Serial port interface signals group

2.5 Baseband Processer Controller interface signals group

SIGNAL TYPE PIN NO. DESCRIPTION

TXD O 1 MAC transmits data to BBP. The data is valid in rising edge of

TXCLK.

TXCLK I 2 The clock from BBP is to be valid TXD.

TX_RDY I 111 BBP indicates the valid data phase.

TX_PE O 117 To control the transmitted phase.

CCA I 113 MAC will monitor this signal to determine whether it can transmit

data or not.

RXD I 4 RXD is an input from BBP. The data is sent serially with LSB first

and the data is frame aligned with RX_RDY.

ASIX ELECTRONICS CORPORATION

12

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

RXCLK I 5 This is the bit clock input from BBP. This clock is used to transfer

header information and payload data through the RXD serial bus.

RXCLK becomes active after SFD has been detected. Data (RXD)

should be samples on rising edge.

MD_RDY I 114 BBP indicates header data and data packet are ready to be transferred.

RX_PE O 115 MAC enables BBP to qualify receive stage.

Baseband Processer interface signals group

2.6 Power Control Interface Signals Group

SIGNAL TYPE PIN NO. DESCRIPTION

CAL_EN O 125 Calibration mode enable.

TR_SW#

O 120 Transmit & Receive Switch Control. Active low.

TR_SW

O 119 Transmit & Receive Switch Control. Active High.

PA_PE O 122 Power Amplifier control pin,. Active high.

RF_PE O 121 Power enable pin to RF and IF components.

PE1 O 13 Power enable1 for I/Q Modulation/Demodulation

PE2 O 15 Power enable2 for I/Q Modulation /Demodulation

Power Control interface signals group

2.7 Synthesizer control signal Interface pins group

SIGNAL TYPE PIN NO. DESCRIPTION

SYNDATA O 128 Serial data for front-end chip synthesizer.

SYNCLK O 127 Serial clock for front-end chip synthesizer.

LE_IF# O 123 Load (latch) Enable to IF synthesizer. MAC selects IF as target for

serial access.

LE_RF# O 124 Load (latch) Enable RF synthesizer. MAC selects RF as target for

serial access

Channel Activity Status Interface pins group

2.8 Miscellaneous pins group

SIGNAL TYPE PIN NO. DESCRIPTION

RSTPHY# O 14 MAC will reset BBP when it monitors the system-reset occurred. Due

to power management issue, MAC will drive BBP into stand-

b

y mode

by RSTPHY# signal driven low for Intersil-like BBP or high for

RFMD-like BBP.

HbusMode I/PU 106 Pull high with VDD2 for PCI/CARDBUS operation

Pull low with VSS2 for PCMCIA operation.

CBSEL I/PD 71 Pull high for CRADBUS operation. In Cardbus mode, Both

HbusMode and CBSEL are also pulled high.

BBPMODE[1:0] I/PU 108,109 BBP interface selection.

2’b00: For Intersil-like interface.

2’b01: For RFMD-like interface.

2’b10: Reserved

2’b11: For RaLink BBP.

ASIX ELECTRONICS CORPORATION

13

AX81190 PCI/CARDBUS/PCMCIA Bus WLAN MAC

LED1 O 17 Indicates in transmitted state.

LED2 O 19 Indicates in received state.

EEPM_DIS I/PD 97 Reserved, pull down with VSS2 for normal operation.

MT[1:0] I/PD 99,100 Memory Test, pull down with VSS2 (2’b00) for normal operation.

GPIO[5:0] I/O/PD 21,22,102,

103,104,105

General pins are cotrolled by software.

VDD1 P 11,16,25,38,

54,72,79,110,

126

Power Supply: +2.5V DC.

VDD2 P 20,31,48,60,

82,87,98,116

Power Supply: +3.3V DC.

VSS1 P 3,18,27,35,51

,57,67,90,107

,112

Ground pin for +2.5V.

VSS2 P 6,23,29,43,75

,95,101,118

Ground pin for +3.3V.

Miscellaneous pins group

Loading...

Loading...