ASI SRAM MT5C6405 Service Manual

Austin Semiconductor, Inc.

SRAM

MT5C6405

16K x 4 SRAM

SRAM MEMORY ARRAY

AVAILABLE AS MILITARY

SPECIFICATIONS

• SMD 5962-86859

• MIL-STD-883

FEATURES

• High Speed: 12, 15, 20, 25, 35, 45, 55, and 70ns

• Battery Backup: 2V data retention

• High-performance, low-power CMOS double-metal

process

• Single +5V (+10%) Power Supply

• Easy memory expansion with CE\

• All inputs and outputs are TTL compatible

OPTIONS MARKING

• Timing

12ns access -12

15ns access -15

20ns access -20

25ns access -2 5

35ns access -3 5

45ns access -45*

55ns access -55*

70ns access -70*

PIN ASSIGNMENT

(Top View)

24-Pin DIP (C)

(300 MIL)

1

2

3

4

5

6

7

8

9

10

11

12

A5NCNC

Vss

OE\

NC

24

23

22

21

20

19

18

17

16

15

14

13

Vcc

WE\

NC

DQ1

Vcc

A4

A3

A2

A1

A0

NC

DQ4

DQ3

DQ2

DQ1

WE\

26

NC

25

A4

24

A3

23

A2

22

A1

21

A0

20

DQ4

19

DQ3

18

DQ2

A5

A6

A7

A8

A9

A10

A11

A12

A13

CE\

OE\

Vss

28-Pin LCC (EC)

3 2 1 28 27

A6

4

A7

5

A8

6

A9

7

A10

8

A11

9

A12

10

A13

11

CE\

12

13 14 15 16 17

• Package(s)

Ceramic DIP (300 mil) C No. 106

Ceramic LCC E C No. 204

• Operating T emperature Ranges

Industrial (-40oC to +85oC) IT

Military (-55oC to +125oC) XT

• 2V data retention/low power L

*Electrical characteristics identical to those provided for the 35ns

access devices.

For more products and information

please visit our web site at

www.austinsemiconductor .com

MT5C6405

Rev. 2.0 5/01

GENERAL DESCRIPTION

The Austin Semiconductor SRAM family employs

high-speed, low-power CMOS designs using a four-transistor

memory cell. Austin Semiconductor SRAMs are fabricated

using double-layer metal, double-layer polysilicon

technology.

For flexibility in high-speed memory applications, Austin

Semiconductor offers chip enable (CE\) and output enable

(OE\) capability. These enhancements can place the outputs

in High-Z for additional flexibility in system design.

Writing to these devices is accomplished when write

enable (WE\) and CE\ inputs are both LOW. Reading is

accomplished when WE\ remains HIGH and CE\ and OE\ go

LOW . The device of fers a reduced power standby mode when

disabled. This allows system designs to achieve low standby

power requirements.

All devices operate from a single +5V power supply and

all inputs and outputs are fully TTL compatible.

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

1

Austin Semiconductor, Inc.

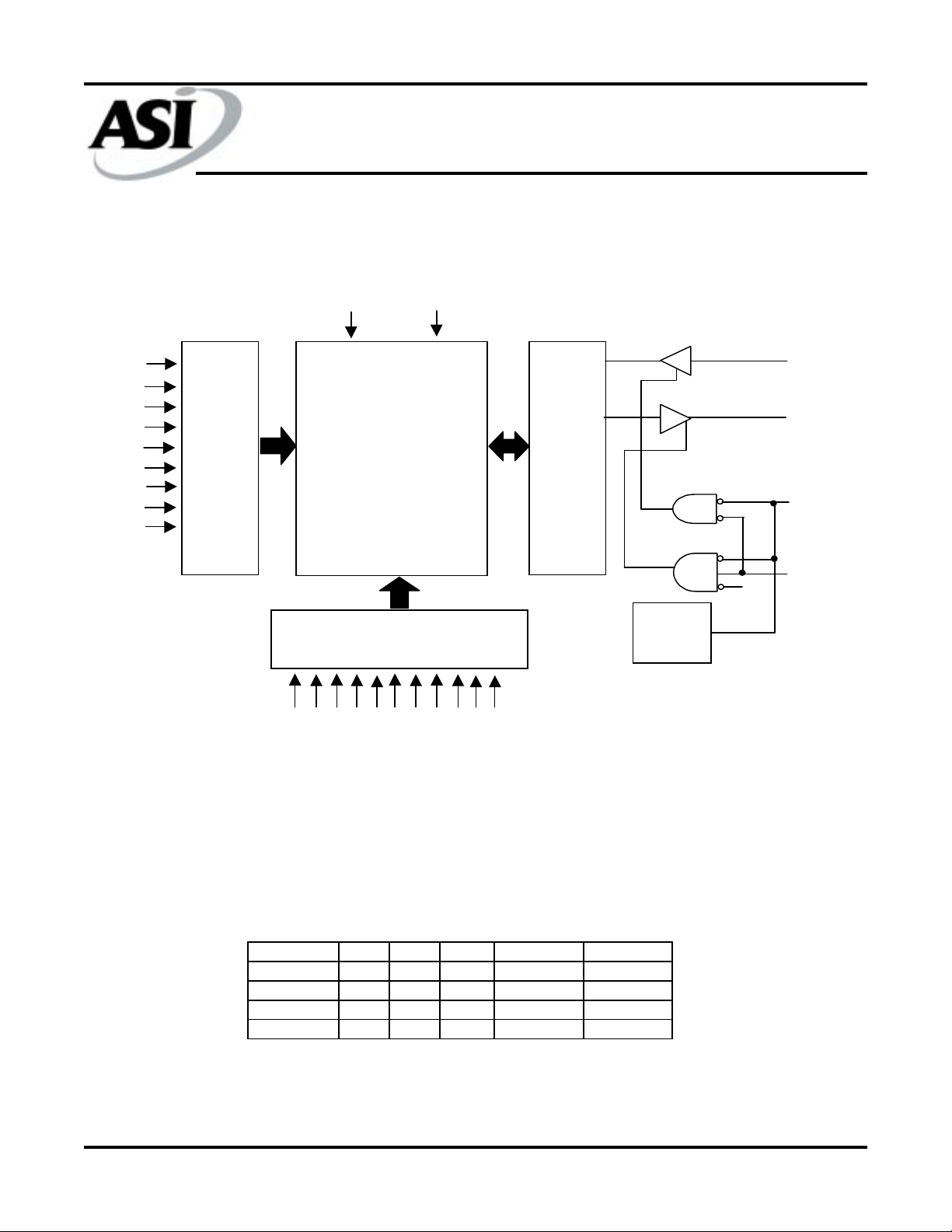

FUNCTIONAL BLOCK DIA GRAM

V

CC

GND

SRAM

MT5C6405

A

D

A

A

A

A

A

A

A

ROW DECODER

1,048,576-BIT

MEMORY ARRAY

I/O CONTROL

Q

CE\

A

(LSB)

COLUMN DECODER

OE\

POWER

DOWN

(LSB)

WE\

A A A A A A A A A A

MT5C6405

Rev. 2.0 5/01

TRUTH TABLE

MODE OE\ CE\ WE\ DQ POWER

STANDBY X H X HIGH-Z STANDBY

READ L L H Q ACTIVE

READ H L H HIGH-Z ACTIVE

WRITE X L L D ACTIVE

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

Austin Semiconductor, Inc.

SRAM

MT5C6405

ABSOLUTE MAXIMUM RATINGS*

Voltage on any Input or DQ Relative to Vss....-0.5V to +7.0V

Storage Temperature…...................................-65oC to +150oC

Power Dissipation.................................................................1W

Max Junction T emperature..................................................+175°C

Lead T emperature (soldering 10 seconds)........................+260oC

Short Circuit Output Current...........................................20mA

1 All voltage referenced to Vss.

*Stresses greater than those listed under "Absolute Maximum

1

Ratings" may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

these or any other conditions above those indicated in the

operation section of this specification is not implied. Exposure

to absolute maximum rating conditions for extended periods

may affect reliability .

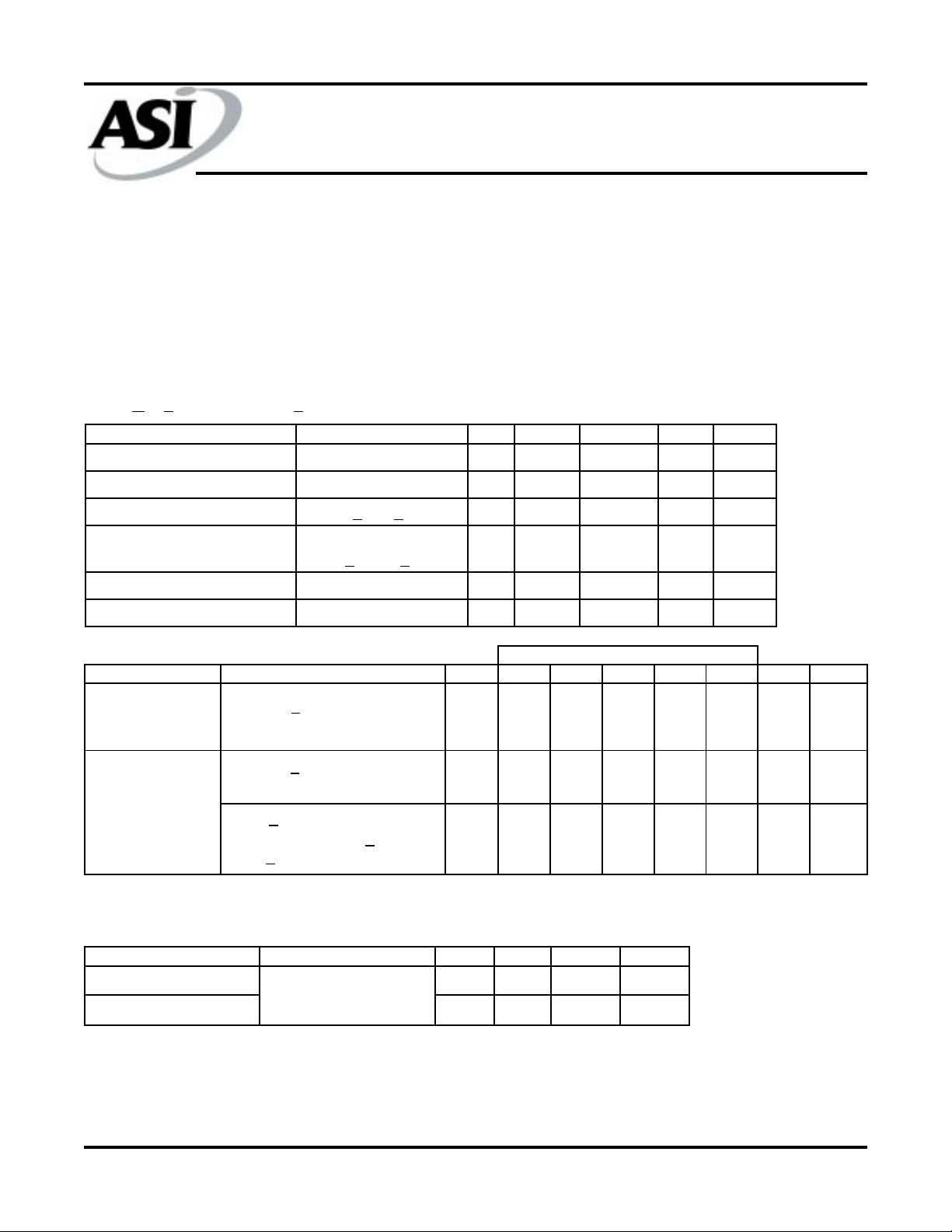

ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

(-55oC < TC < 125oC; VCC = 5V +10%)

DESCRIPTION CONDITIONS SYM MIN MAX UNITS NOTES

Input High (Logic 1) Voltage

Input Low (Logic 0) Voltage

Input Leakage Current

Output Leakage Current

Output High Voltage

Output Low Voltage

0V <

VIN < V

CC

Outputs Disabled

0V < V

I

OH

I

OL

< V

OUT

CC

= -4.0mA V

= 8.0mA V

V

V

IL

IL

OH

OL

2.2 Vcc+0.5V V 1

IH

-0.5 0.8 V 1, 2

IL

-10 10 µA

I

-10 10 µA

O

2.4 V 1

0.4 V 1

PARAMETER

Power Supply

Current: Operating

Power Supply

Current: Standby

CONDITIONS

VIL; VCC = MAX

CE\ <

Output Open

VIH; VCC = MAX

CE\ >

f = 0 Hz

(V

CE\ >

All Other Inputs <

or >

-0.2); VCC = MAX

CC

(VCC - 0.2V), f = 0 Hz

0.2V

SYM -12 -15 -20 -25 -35 UNITS NOTES

I

I

SBT1

I

SBC2

140 125 110 100 90 mA 3

cc

50 45 40 35 30 mA

25 25 25 25 25 mA

CAPACITANCE

DESCRIPTION CONDITIONS SYM MAX UNITS NOTES

Input Capacitance C

Output Capacitance C

= 25oC, f = 1MHz

T

A

Vcc = 5V

I

O

8pF 4

10 pF 4

MAX

MT5C6405

Rev. 2.0 5/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

SRAM

MT5C6405

Austin Semiconductor, Inc.

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Note 5) (-55oC < TC < 125oC; VCC = 5V +10%)

DESCRIPTION

READ CYCLE

READ cycle time

Address access time

Chip Enable access time

Output hold from address change

Chip Enable to output in Low-Z

Chip disable to output in High-Z

Chip Enable to power-up time

Chip disable to power-down time

Output Enable access time

Output Enable to output in Low-Z

Output disable to output in High-Z

WRITE CYCLE

WRITE cycle time

Chip Enable to end of write

Address valid to end of write

Address setup time

Address hold from end of write

WRITE pulse width

Data setup time

Data hold time

Write disable to output in Low-Z

Write Enable to output in High-Z

-12

SYMBOL UNITS

t

t

t

t

t

LZCE

t

HZCE

t

t

t

AOE

t

LZOE

t

HZOE

t

t

t

t

t

t

t

t

t

LZWE

t

HZWE

MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX

RC

AA

ACE

OH

12 15 20 25 35 ns

12 15 20 25 35 ns

12 15 20 25 35 ns

22222 ns

22222 ns7

7 8 10 12 15 ns 6, 7

PU

PD

00000 ns

12 15 20 25 35 ns

6 7 8 10 15 ns

00008 ns

6 7 8 10 15 ns 6

WC

CW

AW

AS

AH

WP

DS

DH

12 15 20 25 35 ns

10 12 15 20 25 ns

10 12 15 20 25 ns

00000 ns

00000 ns

10 12 15 20 25 ns

7 8 10 12 15 ns

00000 ns

22222 ns7

060708010015ns 6, 7

-35-25-20-15

NOTES

MT5C6405

Rev. 2.0 5/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

4

Loading...

Loading...