ASAHI KASEI AK4397 User Manual

[AK4397]

AK4397は、DVD-Audioの192kHzサンプリングモードに対応した高性能プレミアム32ビットDACです。

ΔΣ変調器には新開発のアドバンスト・マルチビット方式を採用、従来のシングルビット方式の優れた低

歪特性に加えて、さらに広いダイナミックレンジを実現しています。内蔵のポストフィルタにはスイッ

チトキャパシタフィルタ(SCF)を採用し、クロックジッタによる精度の劣化を改善します。ディジタル

入力は192kHzのPCM入力とDSD入力の両方に対応しており、DVD-Audio, SACD等のシステムに最適で

す。AK4397はAK4393/4/5/6と機能的な互換性を持ちかつ低消費電力を実現します

• 128倍オーバサンプリング

• サンプリングレート: 30kHz ∼ 216kHz

• 32ビット8倍ディジタルフィルタ(スローロールオフ オプション) 内蔵

- Ripple: ±0.005dB, Attenuation: 75dB

• 強ジッタ耐力

• 低歪差動出力

• DSD入力対応

• 32, 44.1, 48kHz対応ディジタルディエンファシス内蔵

• ソフトミュート

• ディジタルATT(リニア 256ステップ)

• THD+N: −103dB

• DR, S/N: 120dB

• オーディオI/Fフォーマット: 24/32ビット前詰め, 16/20/24/32ビット後詰め, I

• マスタクロック 通常速 : 256fs, 384fs, 512fs, 768fs or 1152fs

• 電源電圧: 4.75 ∼ 5.25V

• ディジタル入力レベル: TTL

• パッケージ: 44ピンLQFP

High Performance Premium 32-Bit DAC

概 要

特 長

2倍速 : 128fs, 192fs, 256fs or 384fs

4倍速 : 128fs or 192fs

DSD : 512fs or 768fs

AK4397

2

S, DSD

MS0616-J-02 2009/02

- 1 -

[AK4397]

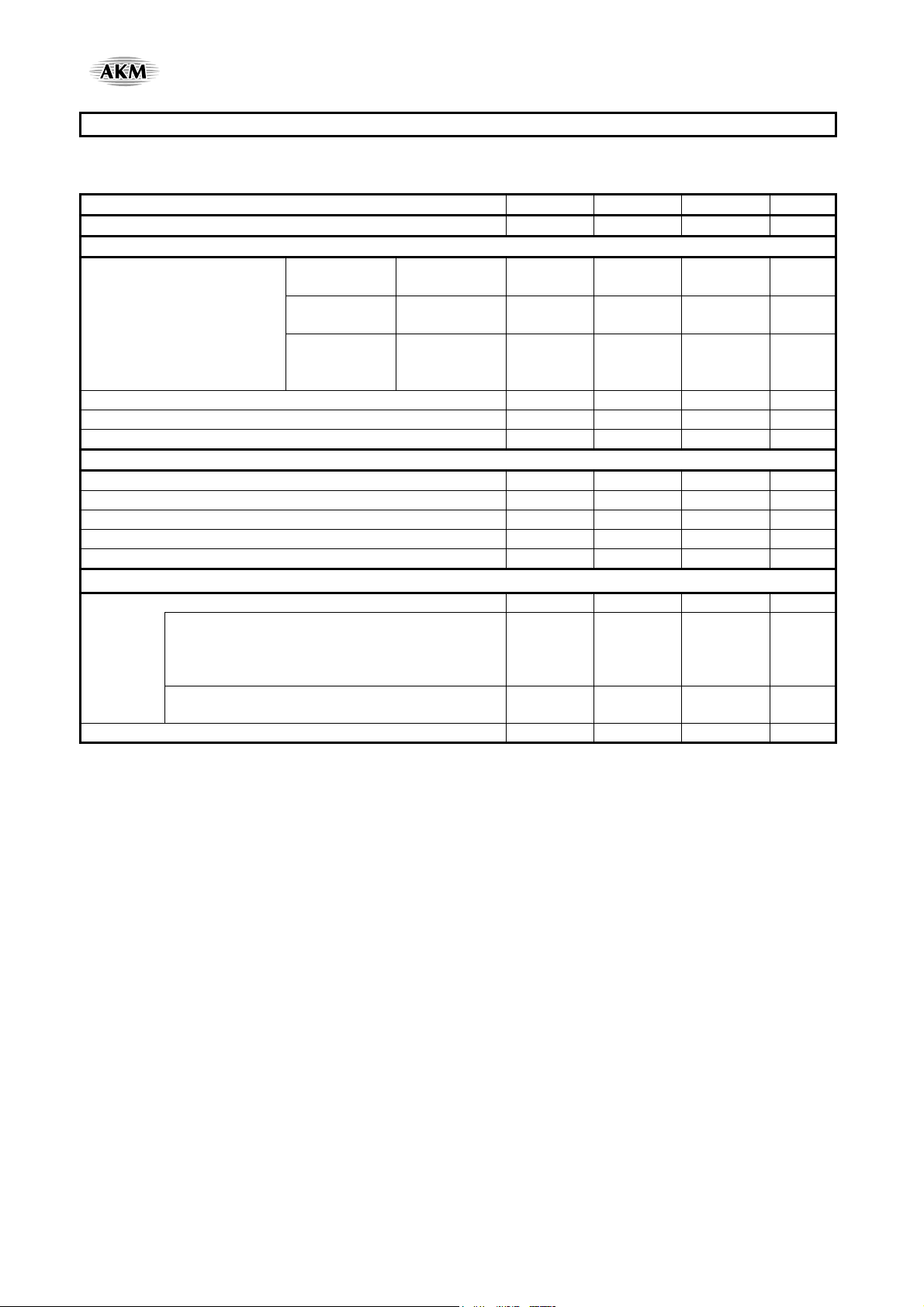

■ ブロック図

DVDD VSS4 VSS3AVDD VDDL

ACKS

BICK/DCLK

LRCK/DSDR

SDATA/DSDL

PDN SMUTE DFS0

De-emphasis

PCM

Data

Interface

De-emphasis

DATT

Soft Mute

DATT

Soft Mute

8X

Interpolator

8X

Interpolator

VREFLH VREFLL

VSS2

ΔΣ

Modulator

ΔΣ

Modulator

SCF

SCF

AOUTL+

AOUTL-

AOUTR+

AOUTR-

DIF0/DCLK

DIF1/DSDL

DIF2/DSDR

CAD0

CAD1

Control Register

CSN

CCLK CDT I P/S MCLK

DSD

Data

Interface

Clock Divid e r

Block Diagram

VDDR

VSS1

VREFHR

De-emphasis

Control

DEM0

DEM1

TST1/DZFL

VREFLR

MS0616-J-02 2009/02

- 2 -

[AK4397]

K

R

K

K

A

A

■ オーダリングガイド

AK4397EQ −10 ∼ +70°C 44pin LQFP (0.8mm pitch)

AKD4397 AK4397評価用ボード

■ ピン配置

AOUTLN

VSS2 32

VDDL 31

VREFHL 30

VREFLL 29

NC 28

VREFLR 27

VREFHR 26VDDR 25

VSS1 24

AOUTRN 23

AOUTLP

NC

NC 36

NC 37

NC

NC 39

VSS3 40

AVDD 41

MCLK

VSS4 43

NC 44

34

35

38

42

33

1

DVDD

AK4397EQ

Top View

3

2

PDN

4

BICK/DCL

SDATA/DSDL

22

21

20

19

18

17

16

15

14

13

12

7

5

6

LRCK/DSD

SMUTE/CSN

DFS0/CAD0

8

DEM0/CCL

10

9

11

DIF0/DCL

DIF1/DSDL

DEM1/CDT1

OUTRP

NC

NC

NC

NC

TST2/CAD1

TST1/DZFL

CKS/DZFR

P/S

NC

DIF2/DSDR

- 3 -

MS0616-J-02 2009/02

[AK4397]

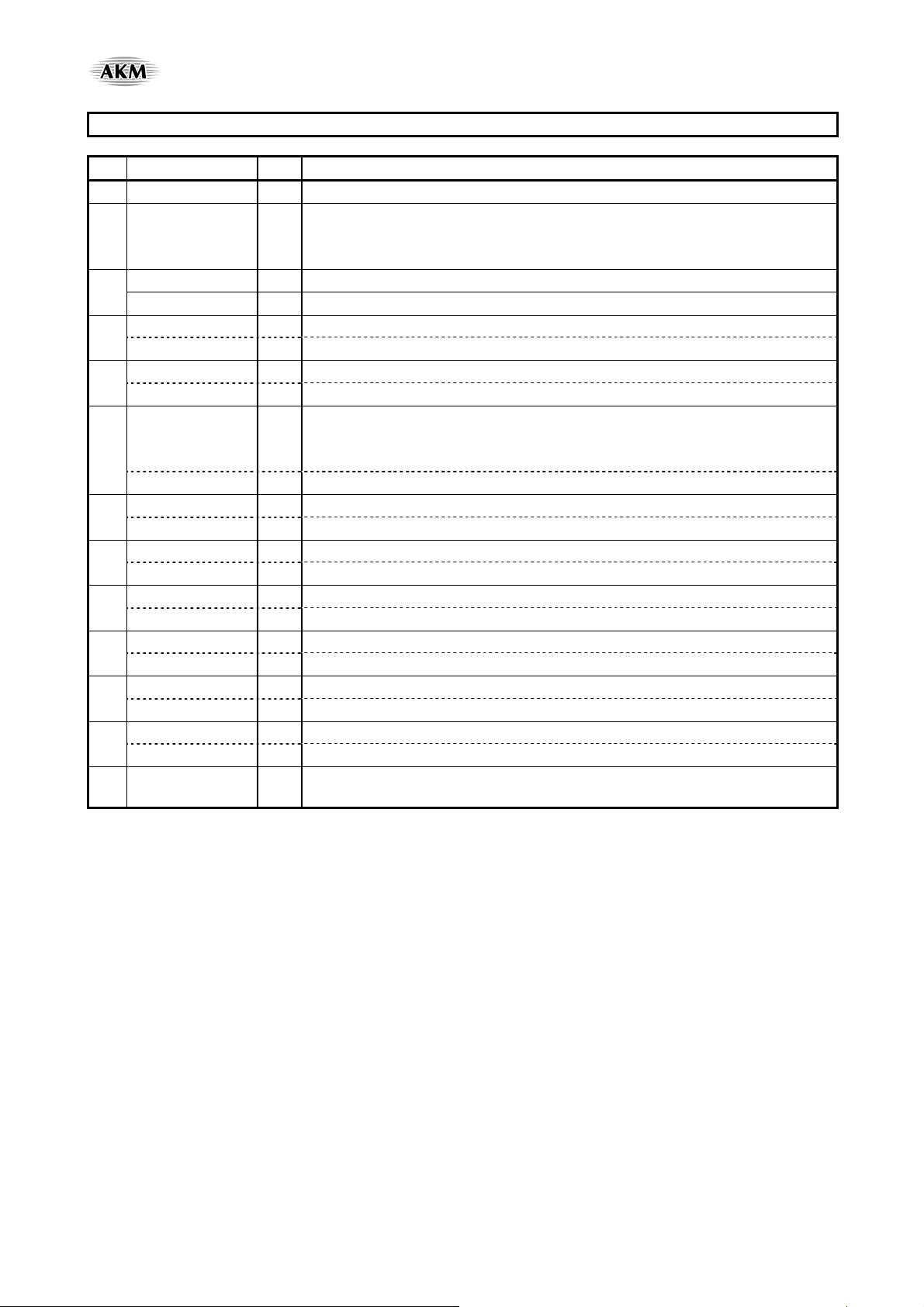

ピン/機能

No. Pin Name I/O Function

1 DVDD - Digital Power Supply Pin, 4.75 ∼ 5.25V

Power-Down Mode Pin

2 PDN I

BICK I Audio Serial Data Clock Pin in PCM Mode

3

DCLK I DSD Clock Pin in DSD Mode

SDATA I Audio Serial Data Input Pin in PCM Mode

4

DSDL I DSD Lch Data Input Pin in DSD Mode

LRCK I L/R Clock Pin in PCM Mode

5

DSDR I DSD Rch Data Input Pin in DSD Mode

SMUTE I

6

CSN I Chip Select Pin in Serial Mode

DFS0 I Sampling Speed Mode Select Pin in Parallel Mode (Internal pull-down pin)

7

CAD0 I Chip Address 0 Pin in Serial Mode (Internal pull-down pin)

DEM0 I De-emphasis Enable 0 Pin in parallel mode

8

CCLK I Control Data Clock Pin in serial mode

DEM1 I De-emphasis Enable 1 Pin in Parallel Mode

9

CDTI I Control Data Input Pin in Serial Mode

DIF0 I Digital Input Format 0 Pin in PCM Mode

10

DCLK I DSD Clock Pin in DSD Mode

DIF1 I Digital Input Format 1 Pin in PCM Mode

11

DSDL I DSD Lch Data Input Pin in DSD Mode

DIF2 I Digital Input Format 2 Pin in PCM Mode

12

DSDR I DSD Rch Data Input Pin in DSD Mode

13 NC -

Note: All input pins except internal pull-up/down pins should not be left floating.

When at “L”, the AK4397 is in power-down mode and is held in reset.

The AK4397 should always be reset upon power-up.

Soft Mute Pin in Parallel Mode

When this pin goes “H”, soft mute cycle is initiated.

When returning “L”, the output mute releases.

No internal bonding.

Connect to GND.

MS0616-J-02 2009/02

- 4 -

[AK4397]

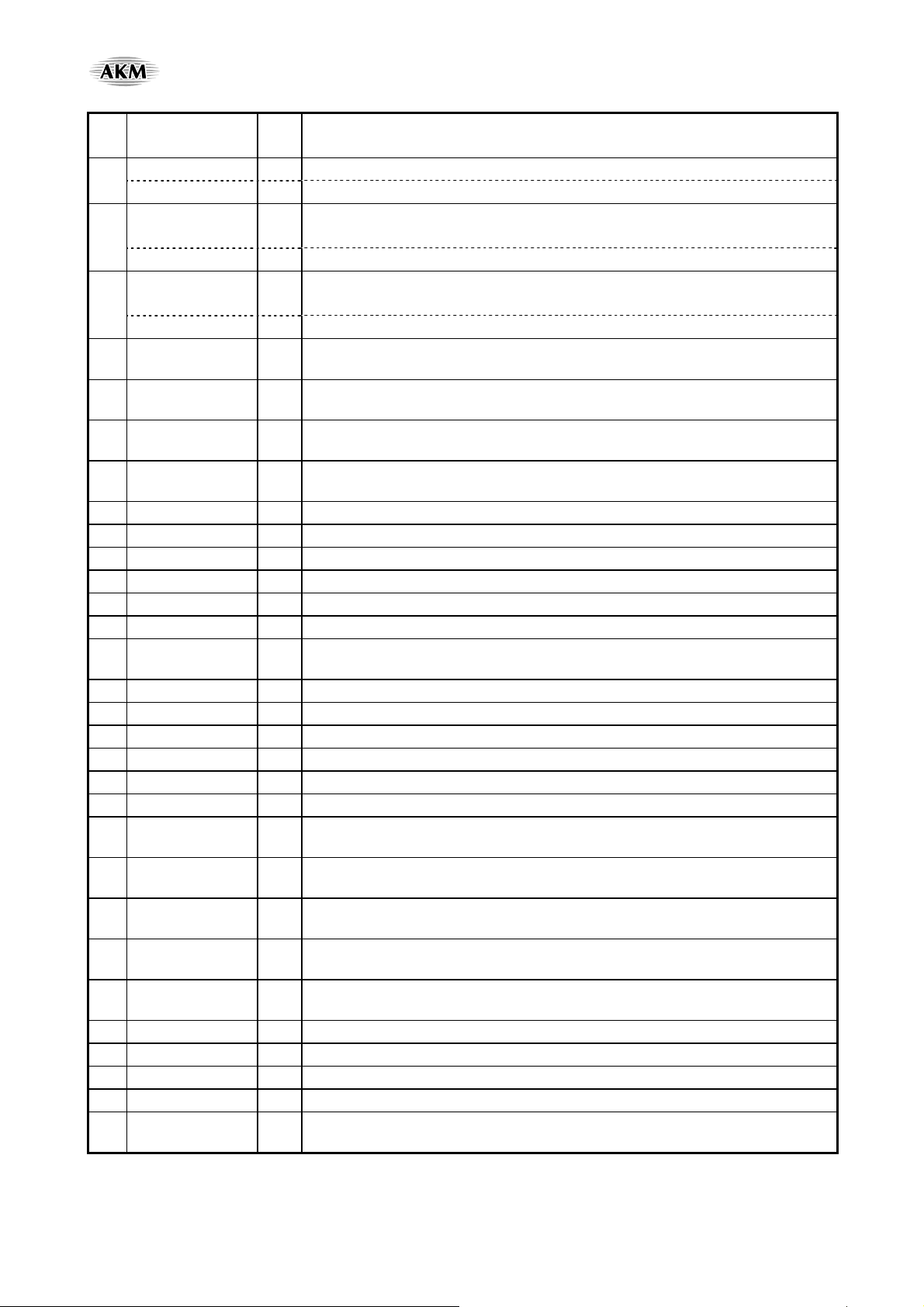

14 P/S I

ACKS I Master Clock Auto Setting Mode Pin in Parallel Mode

15

DZFR O Rch Zero Input Detect Pin in Serial Mode

TST1 O

16

Parallel/Serial Select Pin (Internal pull-up pin)

“L”: Serial Mode, “H”: Parallel Mode

Test 1 Pin in Parallel Mode

Should be open.

DZFL O Lch Zero Input Detect Pin in Serial Mode

TST2 I

17

Test 2 Pin in Parallel Mode (Internal pull-down pin)

Connect to GND.

CAD1 I Chip Address 1 Pin in Serial Mode (Internal pull-down pin)

18 NC -

19 NC -

20 NC -

21 NC -

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

22 AOUTRP O Rch Positive Analog Output Pin

23 AOUTRN O Rch Negative Analog Output Pin

24 VSS1 - Ground Pin

25 VDDR - Rch Analog Power Supply Pin, 4.75 ∼ 5.25V

26 VREFHR I Rch High Level Voltage Reference Input Pin

27 VREFLR I Rch Low Level Voltage Reference Input Pin

28 NC -

No internal bonding.

Connect to GND.

29 VREFLL I Lch Low Level Voltage Reference Input Pin

30 VREFHL I Lch High Level Voltage Reference Input Pin

31 VDDL - Lch Analog Power Supply Pin, 4.75 ∼ 5.25V

32 VSS2 - Ground Pin

33 AOUTLN O Lch Negative Analog Output Pin

34 AOUTLP O Lch Positive Analog Output Pin

35 NC -

36 NC -

37 NC -

38 NC -

39 NC -

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

No internal bonding.

Connect to GND.

40 VSS3 - Ground Pin

41 AVDD - Analog Power Supply Pin, 4.75 ∼ 5.25V

42 MCLK I Master Clock Input Pin

43 VSS4 - Ground Pin

44 NC -

No internal bonding.

Connect to GND.

Note: All input pins except internal pull-up/down pins should not be left floating.

MS0616-J-02 2009/02

- 5 -

[AK4397]

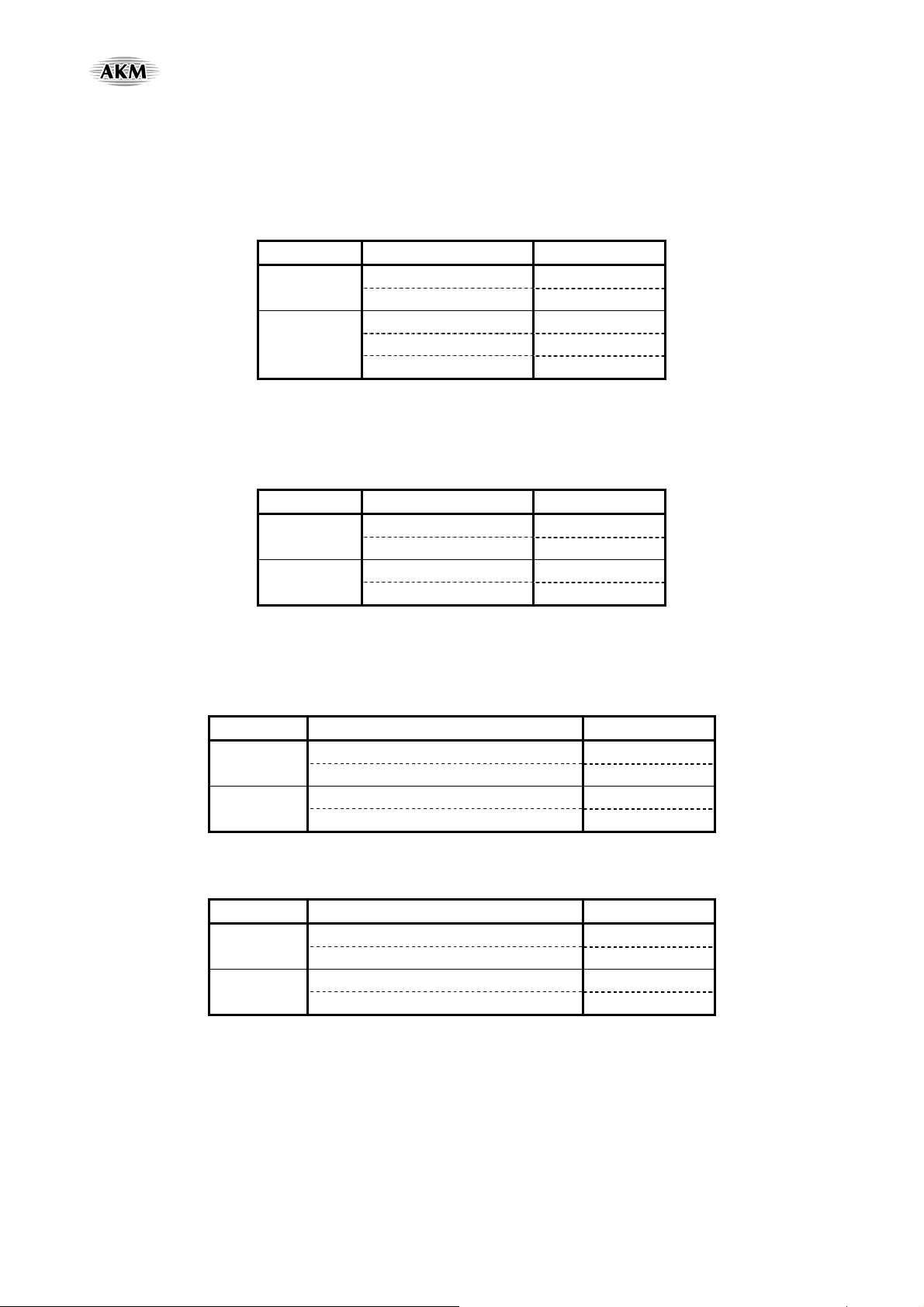

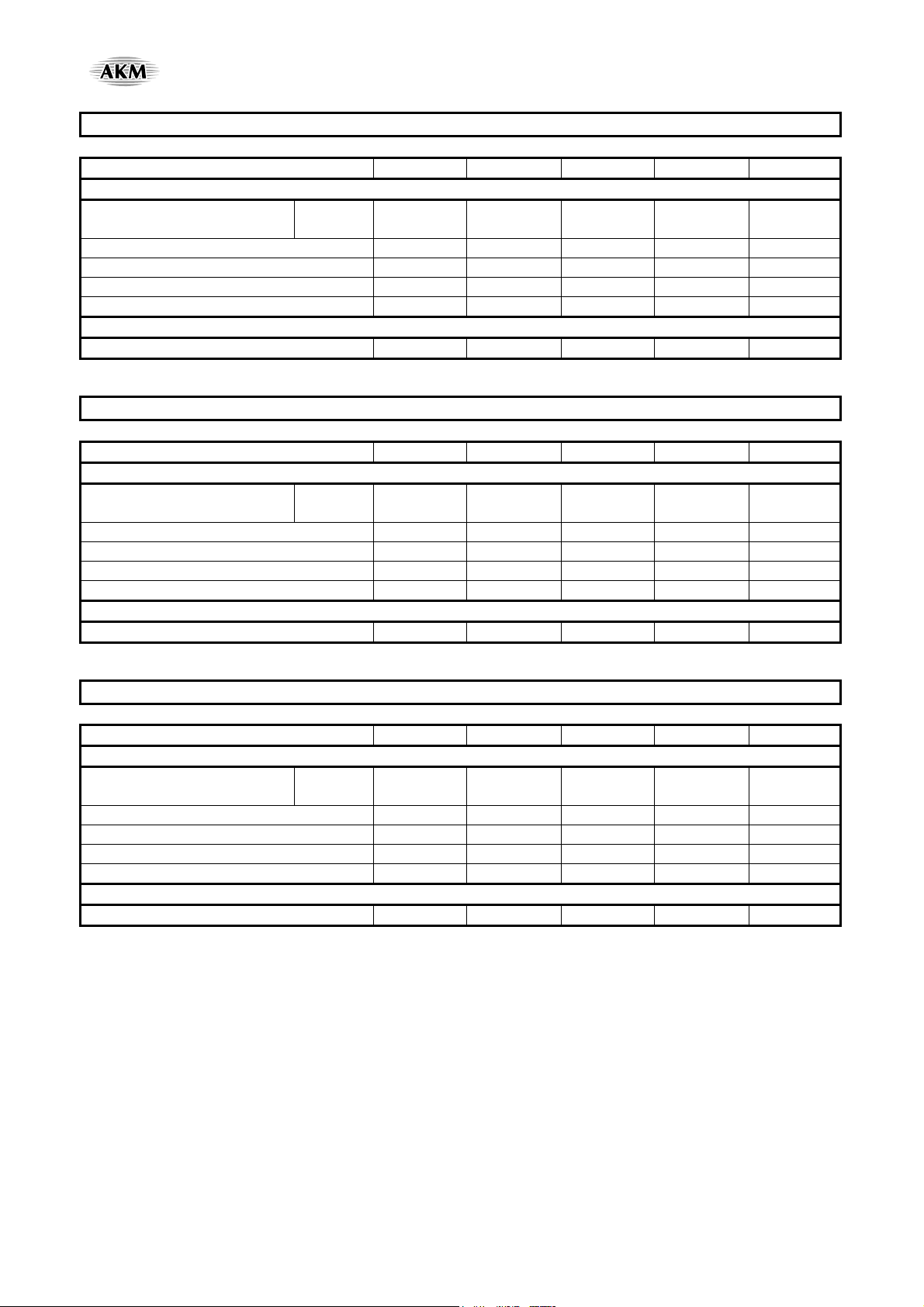

■ 使用しないピンの処理について

使用しない入出力ピンは下記の設定を行い、適切に処理して下さい。

(1) パラレルモード (PCMモードのみ)

区分 ピン名 設定

Analog

Digital

(2) シリアルモード

1. PCMモード

区分 ピン名 設定

Analog

Digital

2. DSDモード

・#3, #4, #5ピンのDCLK, DSDL, DSDRを使用する場合

区分 ピン名 設定

Analog

Digital

・#10, #11, #12ピンのDCLK, DSDL, DSDRを使用する場合

区分 ピン名 設定

Analog

Digital

AOUTLP, AOUTLN

AOUTRP, AOUTRN オープン

DCLK(#10), DSDL(#11), DSDR(#12) VSS4に接続

DZFL, DZFR オープン

AOUTLP, AOUTLN

AOUTRP, AOUTRN オープン

DCLK(#3), DSDL(#4), DSDR(#5) VSS4に接続

DZFL, DZFR オープン

AOUTLP, AOUTLN

AOUTRP, AOUTRN オープン

SMUTE VSS4に接続

TST1 オープン

TST2 VSS4に接続

AOUTLP, AOUTLN

AOUTRP, AOUTRN オープン

DIF2, DIF1, DIF0 VSS4に接続

DZFL, DZFR オープン

オープン

オープン

オープン

オープン

MS0616-J-02 2009/02

- 6 -

[AK4397]

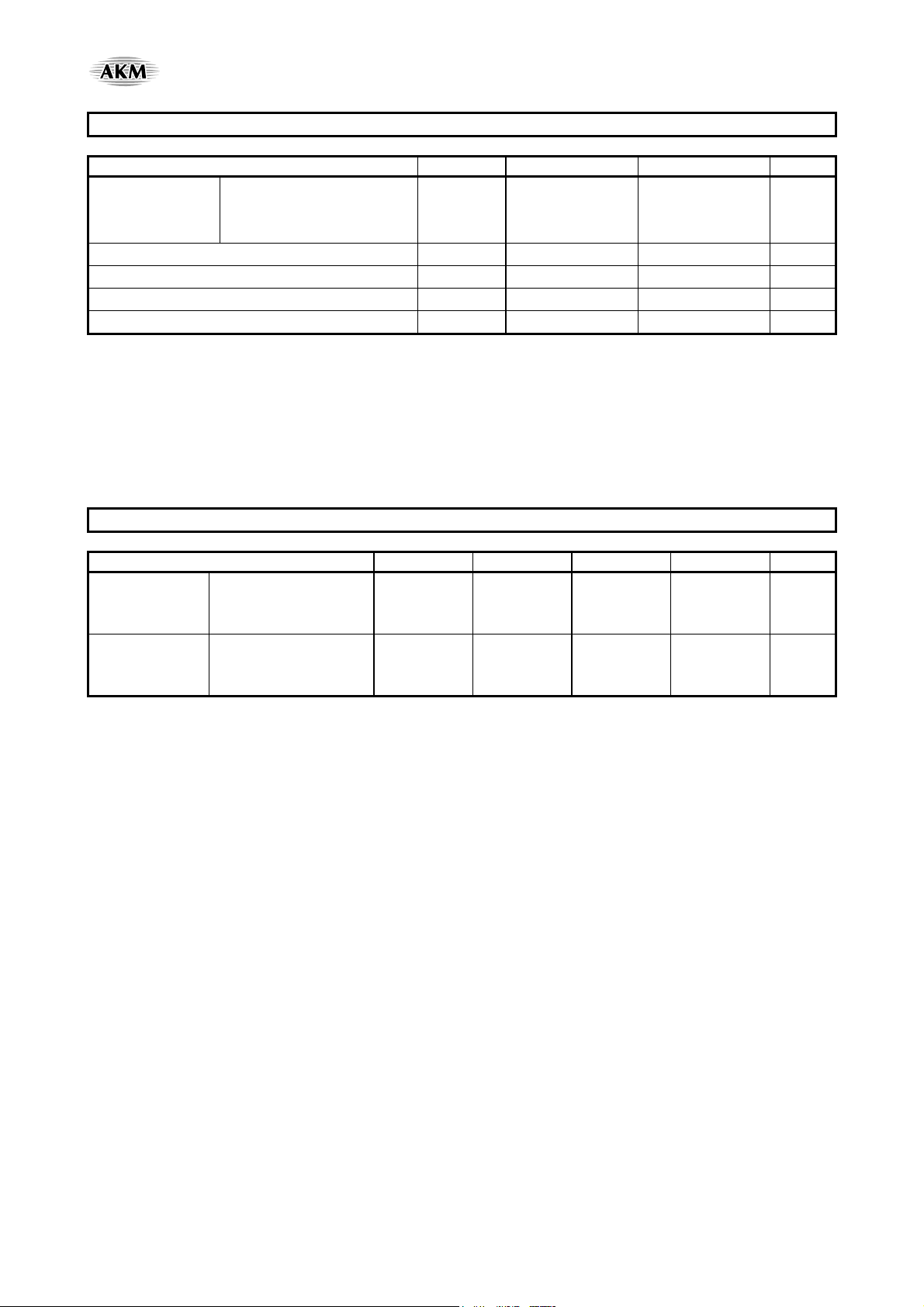

絶対最大定格

(VSS1-4 =0V; Note 1)

Parameter Symbol min max Units

Power Supplies:

Input Current, Any Pin Except Supplies IIN - ±10 mA

Digital Input Voltage VIND −0.3 DVDD+0.3 V

Ambient Temperature (Power applied) Ta −10 70 °C

Storage Temperature Tstg −65 150 °C

Note 1. 電圧は全てグランドピンに対する値です。

Note 2. VSS1-4 は同じアナロググランドに接続して下さい。

注意 : この値を超えた条件で使用した場合、デバイスを破壊することがあります。

また通常の動作は保証されません。

Analog

Analog

Digital

AVDD

VDDL/R

DVDD

−0.3

-0.3

−0.3

6.0

6.0

6.0

V

V

V

推奨動作条件

(VSS1-4 =0V; Note 1)

Parameter Symbol min typ max Units

Power Supplies

(

Note 3)

Voltage

Reference

(

Note 4)

Note 1. 電圧は全てグランドピンに対する値です。

Note 3. AVDD, VDDL/R, DVDDの電源立ち上げシーケンスを考慮する必要はありません。

Note 4. アナログ出力電圧は(VREFH − VREFL)の電圧に比例します。

AOUT (typ.@0dB) = (AOUT+) − (AOUT−) = ±2.8Vpp × (VREFHL/R − VREFLL/R)/5.

注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので

十分ご注意下さい。

Analog

Analog

Digital

“H” voltage reference

“L” voltage reference

VREFH − VREFL

AVDD

VDDL/R

DVDD

VREFHL/R

VREFLL/R

ΔVREF

4.75

4.75

4.75

AVDD−0.5

VSS

3.0

5.0

5.0

5.0

-

-

-

5.25

5.25

5.25

AVDD

-

AVDD

V

V

V

V

V

V

MS0616-J-02 2009/02

- 7 -

[AK4397]

アナログ特性

(Ta=25°C; AVDD=VDDL/R=DVDD=5.0V; VSS1-4 =0V; VREFHL/R=AVDD, VREFLL/R= VSS;

Input data = 24bit; R

Measurement bandwidth = 20Hz ~ 20kHz; External Circuit:

≥ 1kΩ; BICK=64fs; Signal Frequency = 1kHz; Sampling Frequency = 44.1kHz;

L

Figure 18; unless otherwise specified.)

Parameter min typ max Units

Resolution - - 24 Bits

Dynamic Characteristics (Note 5)

THD+N

fs=44.1kHz

BW=20kHz

fs=96kHz

BW=40kHz

fs=192kHz

BW=40kHz

BW=80kHz

0dBFS

−60dBFS

0dBFS

−60dBFS

0dBFS

−60dBFS

−60dBFS

-

-

-

-

-103

-57

100

-54

100

-54

-51

-93

-

-

-

-

-

-

dB

dB

dB

dB

dB

dB

dB

Dynamic Range (−60dBFS with A-weighted) (Note 6) 114 120 dB

S/N (A-weighted) (Note 7) 114 120 dB

Interchannel Isolation (1kHz) 100 110 dB

DC Accuracy

Interchannel Gain Mismatch - 0.15 0.3 dB

Gain Drift (Note 8) - 20 - ppm/°C

Output Voltage (Note 9) ±2.65 ±2.8 ±2.95 Vpp

Load Capacitance - - 25 pF

Load Resistance (Note 10) 1 - - kΩ

Power Supplies

Power Supply Current

Normal operation (PDN pin = “H”)

AVDD + VDDL/R

DVDD (fs ≤ 96kHz)

DVDD (fs = 192kHz)

Power down (PDN pin = “L”) (

AVDD+VDDL/R+DVDD

Note 11)

-

-

-

-

32

21

27

10

47

-

41

100

mA

mA

mA

μA

Power Supply Rejection (Note 12) - 50 - dB

Note 5. Audio Precision System Two使用。平均値測定。測定結果は評価ボードマニュアルを参照下さい。

Note 6.

Note 7.

Figure 18 (回路例2)使用時。 101dB at 16bit data and 118dB at 20bit data.

Figure 18 (回路例2)使用時。 S/N比は入力ビット長に依存しません。

Note 8. (VREFH − VREFL)の電圧は+5V一定。

Note 9. フルスケール電圧(0dB)。出力電圧は(VREFHL/R − VREFLL/R)の電圧に比例します。

AOUT (typ.@0dB) = (AOUT+) − (AOUT−) = ±2.8Vpp × (VREFHL/R − VREFLL/R)/5.

Note 10. Load Resistanceについては、AC負荷(DCカット用コンデンサあり)に対して1k ohm (min)です。

照してください。DC負荷(DCカット用コンデンサなし)に対して1.5k ohm (min)です。

Figure 17を参照してくださ

Figure 18を参

い。Load Resistanceはグランドに対する値です。アナログ特性は出力ピンに接続される容量性負荷に敏感な

ため、容量性負荷が極力小さくなるようにしてください。

Note 11. パワーダウン時、P/S pin = DVDD、それ以外の外部クロック(MCLK, BICK, LRCK)を含む

全てのディジタル入力をVSS4に固定した場合の値です。

Note 12. VREFHL/R pinを+5Vに固定して、AVDD, DVDDに1kHz, 100mVppの正弦波を重畳した場合の値です。

MS0616-J-02 2009/02

- 8 -

[AK4397]

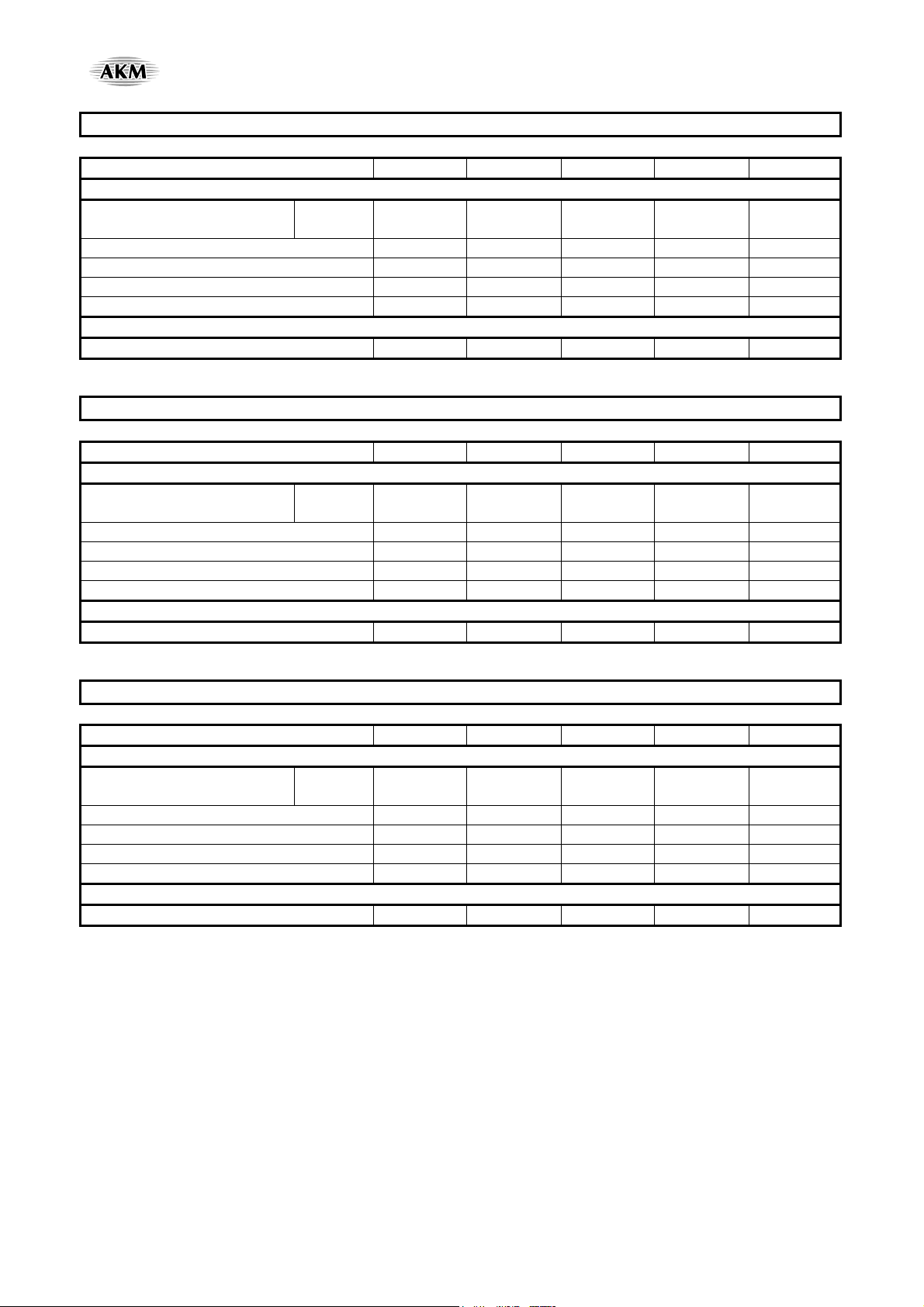

シャープロールオフ・フィルタ特性(fs = 44.1kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; Normal Speed Mode; DEM=OFF; SLOW bit=“0”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 13) ±0.01dB

−6.0dB

Stopband (Note 13) SB 24.1 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 75 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 20.0kHz - ±0.2 - dB

PB

0

-

22.05

20.0

-

kHz

kHz

シャープロールオフ・フィルタ特性(fs = 96kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; Double Speed Mode; DEM=OFF; SLOW bit=“0”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 13) ±0.01dB

−6.0dB

Stopband (Note 13) SB 52.5 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 75 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 40.0kHz - ±0.3 - dB

PB

0

-

48.0

43.5

-

kHz

kHz

シャープロールオフ・フィルタ特性(fs = 192kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; Quad Speed Mode; DEM=OFF; SLOW bit=“0”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 13) ±0.01dB

−6.0dB

Stopband (Note 13) SB 105 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 75 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 80.0kHz - +0/−1 - dB

Note 13.通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、PB = 0.4535 × fs(@±0.01dB)、SB =

0.546 × fsです。

Note 14. ディジタルフィルタによる演算遅延で、16/20/24ビットデータが入力レジスタにセットされてからアナログ信号が

出力されるまでの時間です。

PB

0

-

96.0

87.0

-

kHz

kHz

MS0616-J-02 2009/02

- 9 -

[AK4397]

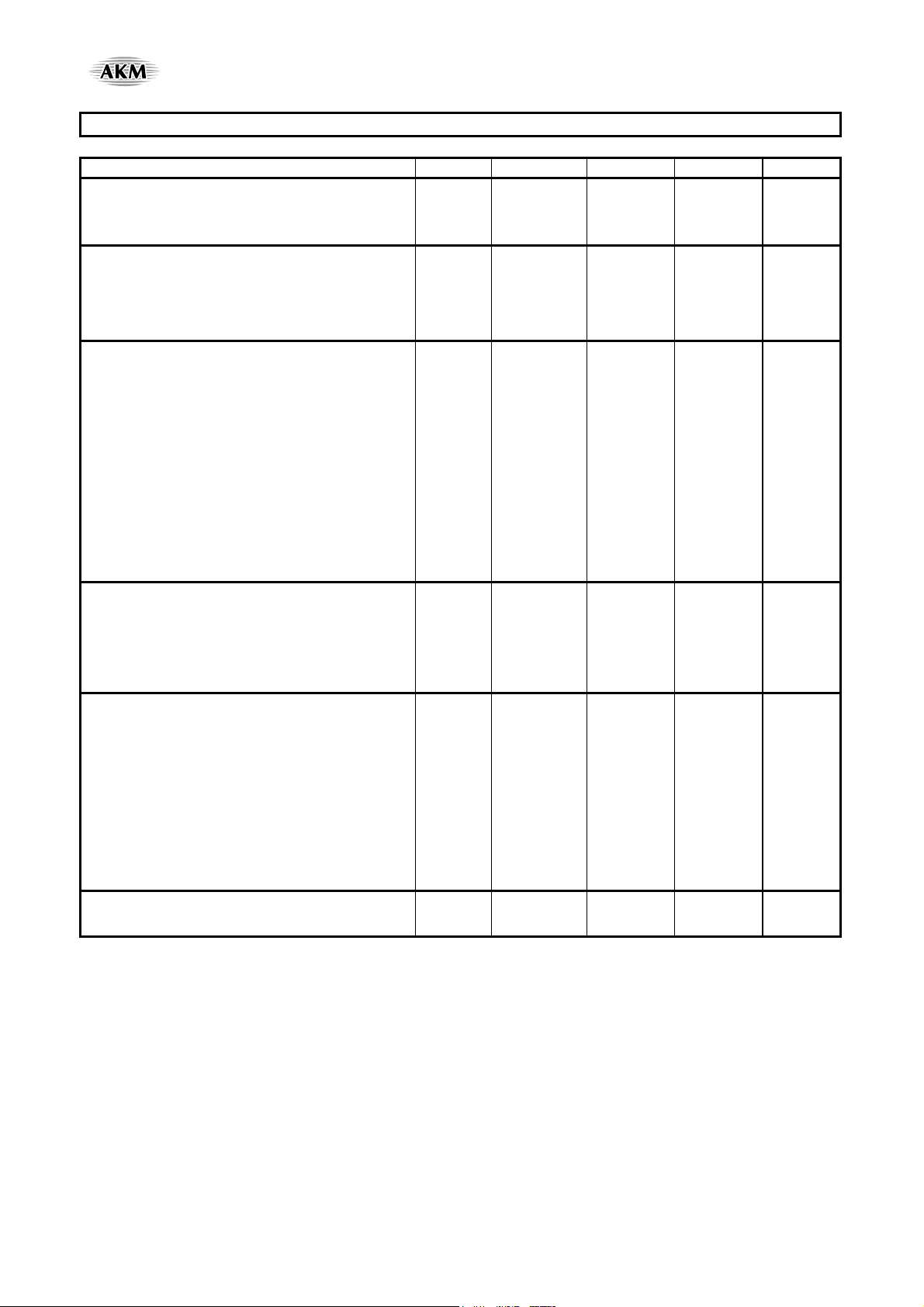

スローロールオフ・フィルタ特性(fs = 44.1kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; Normal Speed Mode; DEM=OFF; SLOW bit=“1”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 15) ±0.04dB

−3.0dB

Stopband (Note 15) SB 39.2 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 72 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 20.0kHz - +0/−5 - dB

PB

0

-

18.2

8.1

-

kHz

kHz

スローロールオフ・フィルタ特性(fs = 96kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; DEM=OFF; SLOW bit=“1”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 15) ±0.04dB

−3.0dB

Stopband (Note 15) SB 85.3 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 72 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 40.0kHz - +0/−4 - dB

PB

0

-

39.6

17.7

-

kHz

kHz

スローロールオフ・フィルタ特性(fs = 192kHz)

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V; Quad Speed Mode; DEM=OFF; SLOW bit=“1”)

Parameter Symbol min typ max Units

Digital Filter

Passband (Note 15) ±0.04dB

−3.0dB

Stopband (Note 15) SB 171 kHz

Passband Ripple PR ±0.005 dB

Stopband Attenuation SA 72 dB

Group Delay (Note 14) GD - 28 - 1/fs

Digital Filter + SCF

Frequency Response: 0 ∼ 80.0kHz - +0/−5 - dB

Note 15.通過域、阻止域の周波数はfs(システムサンプリングレート)に比例し、PB = 0.185 × fs(@±0.04dB)、

SB = 0.888 × fsです。

PB

0

-

79.1

35.5

-

kHz

kHz

MS0616-J-02 2009/02

- 10 -

[AK4397]

DC特性

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V)

Parameter Symbol min typ max Units

High-Level Input Voltage

Low-Level Input Voltage

High-Level Output Voltage (Iout=−100μA)

Low-Level Output Voltage (Iout=100μA)

Input Leakage Current (Note 16) Iin - - ±10 μA

Note 16. DFS0 pinは内部でプルダウン,またP/S pinは内部でプルアップされています。(typ. 100kΩ)このため、DFS0

pin, P/S pinは除きます。

VIH

VIL

VOH

VOL

2.4

-

DVDD−0.5

-

-

-

-

-

-

0.8

-

0.5

V

V

V

V

MS0616-J-02 2009/02

- 11 -

[AK4397]

スイッチング特性

(Ta=25°C; AVDD=VDDL/R=4.75 ∼ 5.25V, DVDD=4.75 ∼ 5.25V)

Parameter Symbol min typ max Units

Master Clock Timing

Frequency

Duty Cycle

LRCK Frequency (Note 17)

Normal Speed Mode

Double Speed Mode

Quad Speed Mode

Duty Cycle

PCM Audio Interface Timing

BICK Period

Normal Speed Mode

Double Speed Mode

Quad Speed Mode

BICK Pulse Width Low

BICK Pulse Width High

BICK “↑” to LRCK Edge (

LRCK Edge to BICK “↑” (

SDATA Hold Time

SDATA Setup Time

DSD Audio Interface Timing

DCLK Period

DCLK Pulse Width Low

DCLK Pulse Width High

DCLK Edge to DSDL/R (

Control Interface Timing

CCLK Period

CCLK Pulse Width Low

Pulse Width High

CDTI Setup Time

CDTI Hold Time

CSN High Time

CSN “↓” to CCLK “↑”

CCLK “↑” to CSN “↑”

Reset Timing

PDN Pulse Width (

Note 17. 通常速モード、2倍速モード、4倍速モードを切り替えた場合はPDN pinまたはRSTN bitで

リセットして下さい。

Note 18. この規格値はLRCKのエッジとBICKの“↑”が重ならないように規定しています。

Note 19. データ送信側に要求される値です。

Note 20. 電源投入時はPDN pinを“L”から“H”にすることでリセットがかかります。DFS1-0 bitを

切り替えた場合はRSTN bitでリセットして下さい。

Note 18)

Note 18)

Note 19)

Note 20)

fCLK

dCLK

fsn

fsd

fsq

Duty

tBCK

tBCK

tBCK

tBCKL

tBCKH

tBLR

tLRB

tSDH

tSDS

tDCK

tDCKL

tDCKH

tDDD

tCCK

tCCKL

tCCKH

tCDS

tCDH

tCSW

tCSS

tCSH

tPD

7.7

40

30

54

108

45

1/128fsn

1/64fsd

1/64fsq

30

30

20

20

20

20

1/64fs

160

160

−20

200

80

80

50

50

150

50

50

150

41.472

60

54

108

216

55

20

MHz

%

kHz

kHz

kHz

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MS0616-J-02 2009/02

- 12 -

Loading...

Loading...