Page 1

1

2

3

4

5

6

7

8

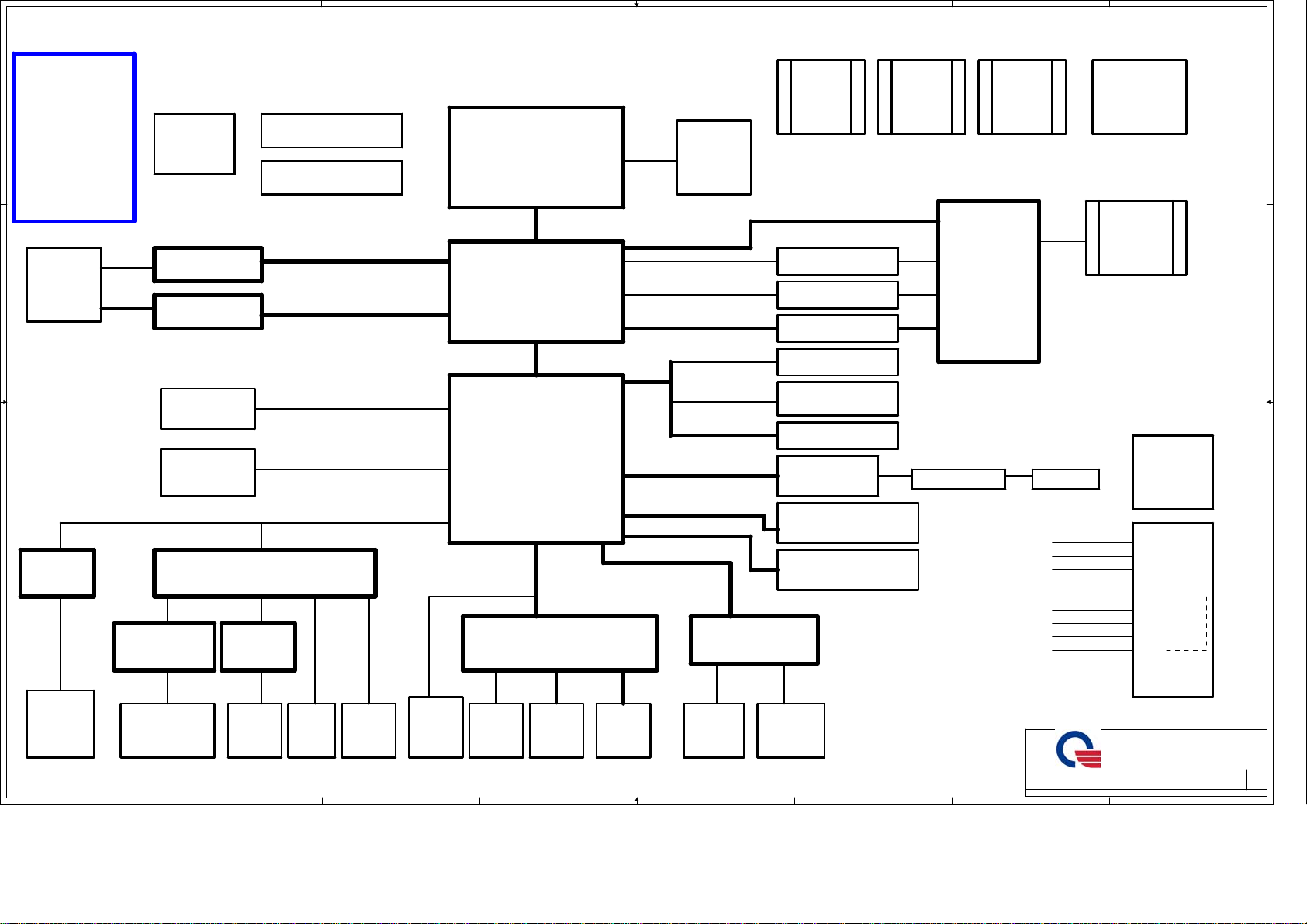

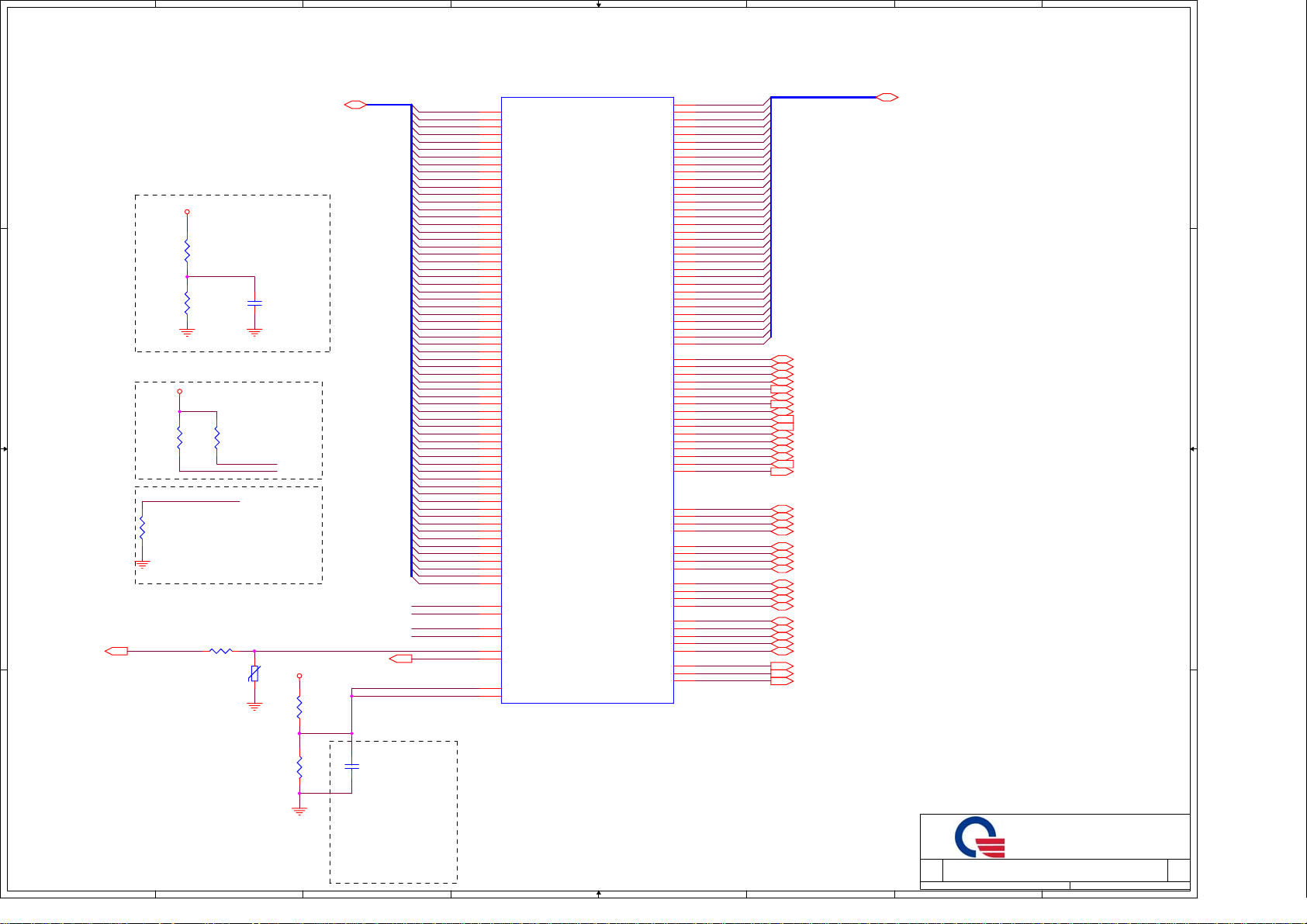

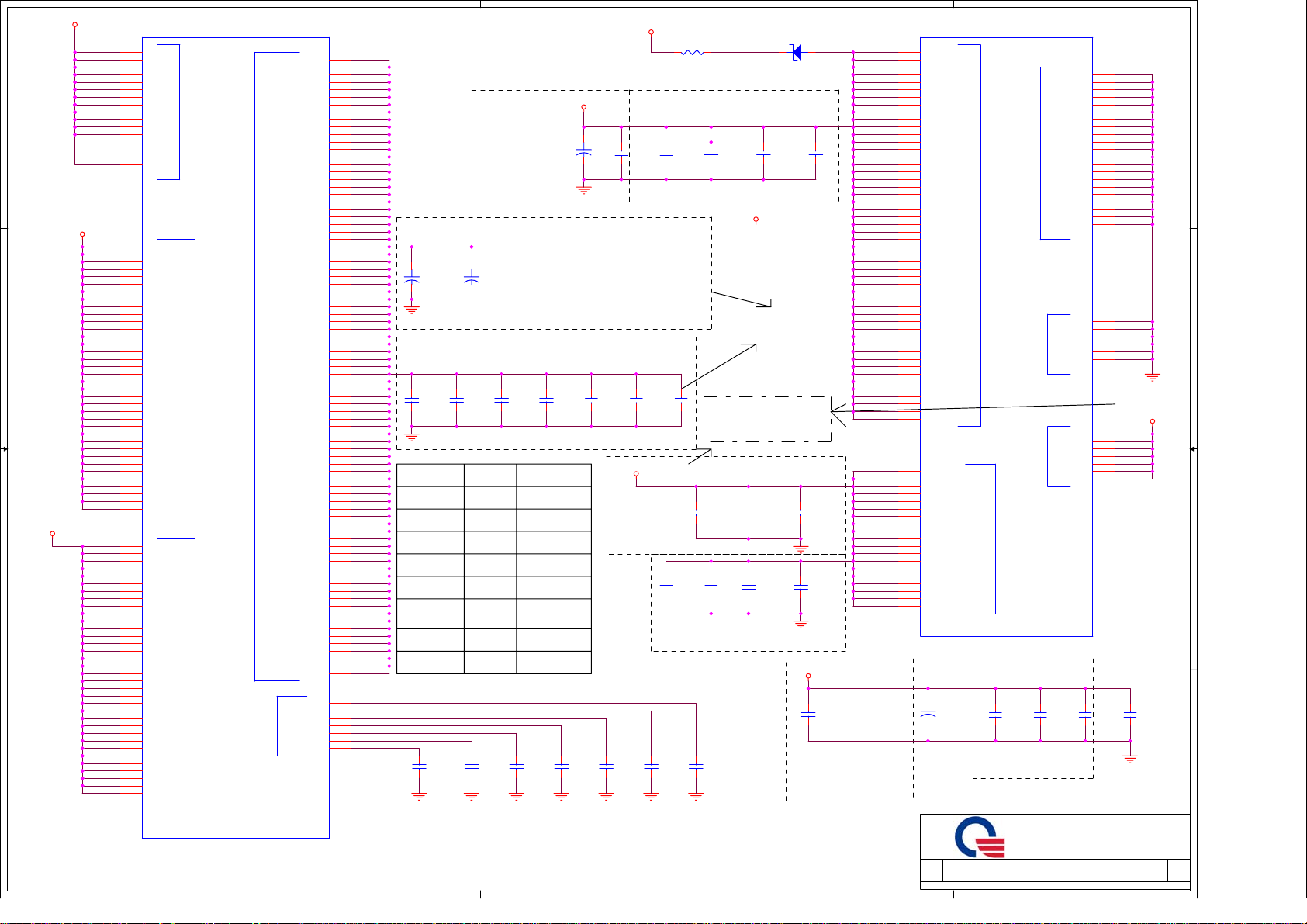

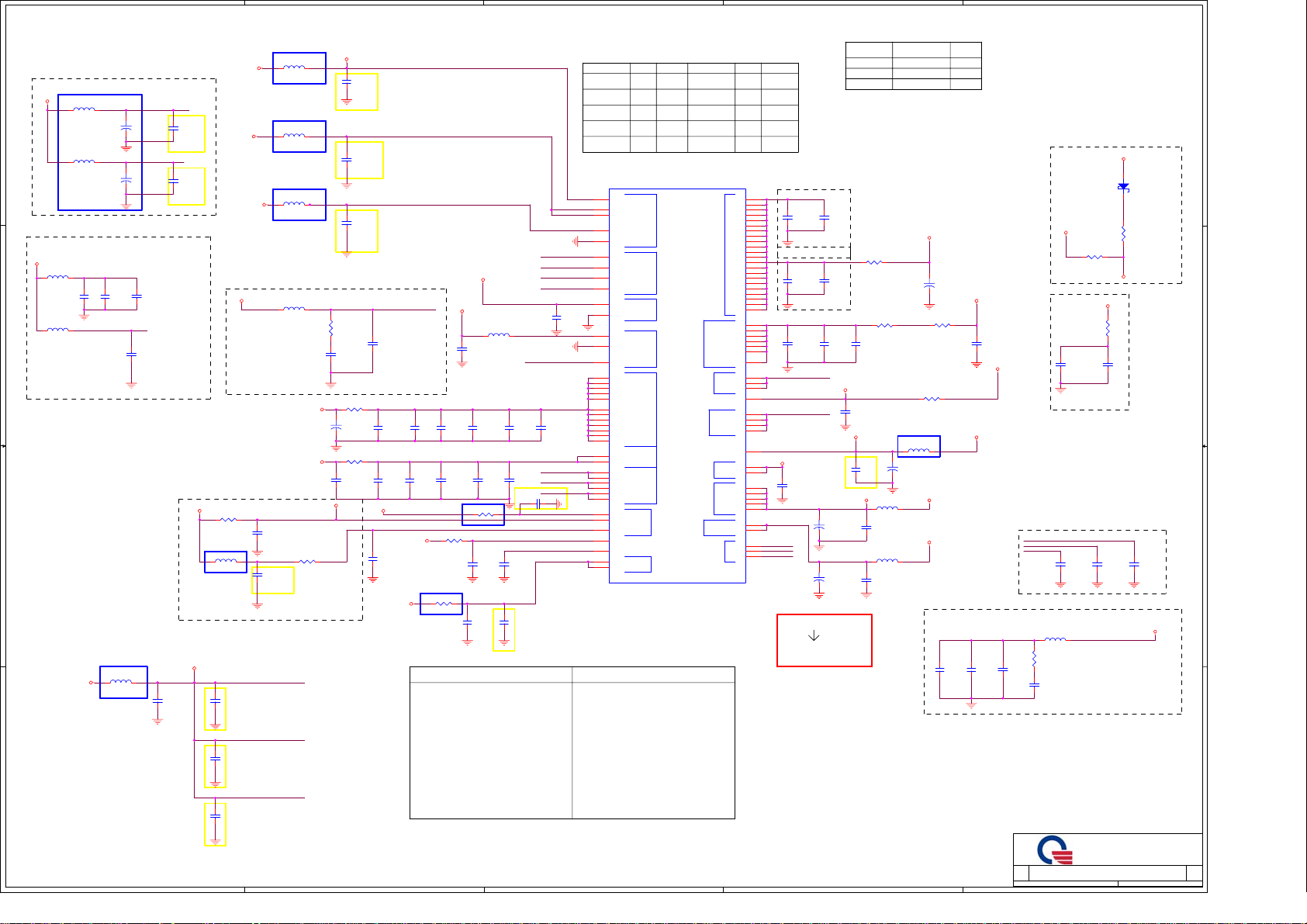

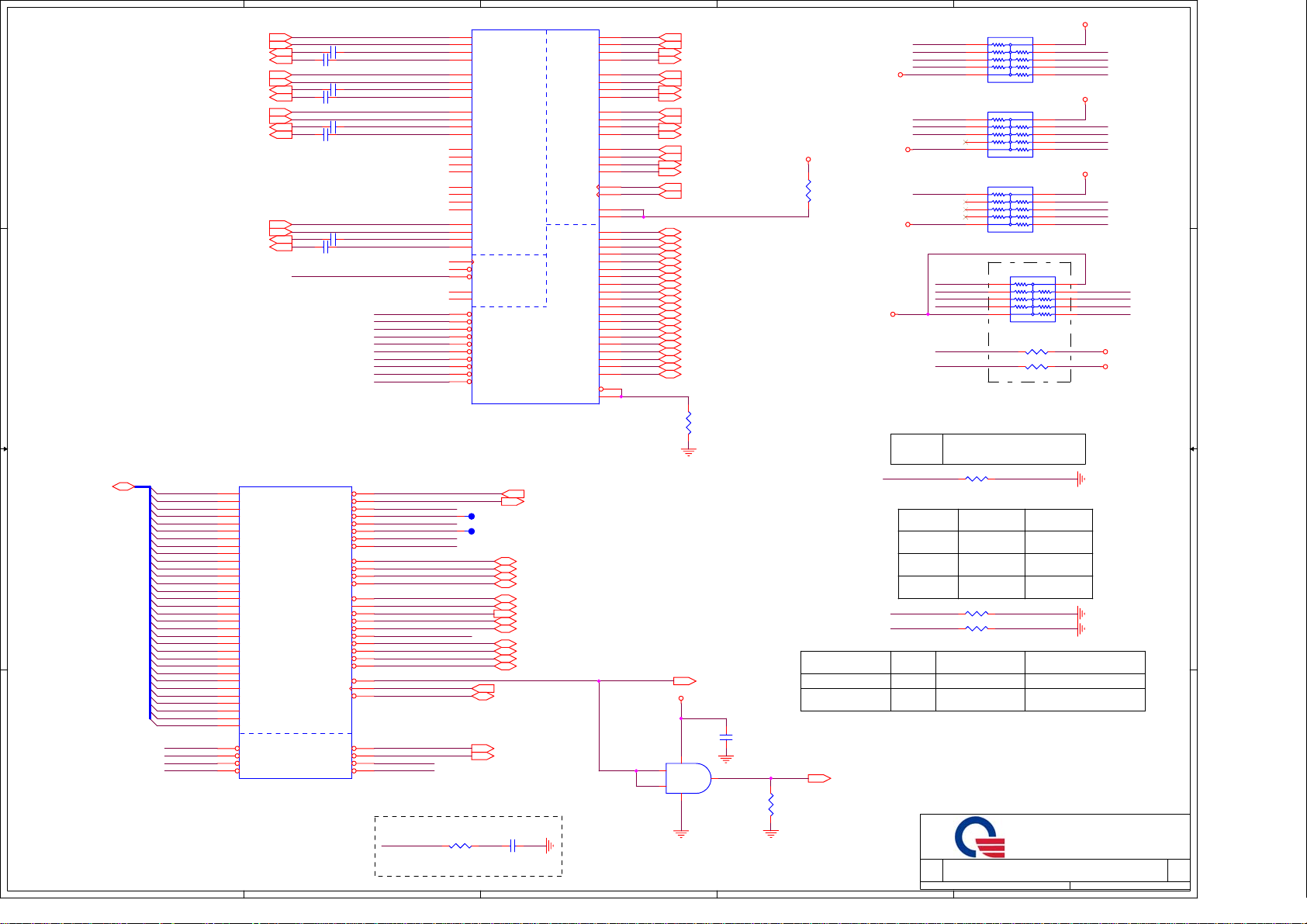

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : SGND1

A A

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : IN3

LAYER 7 : SGND2

RUN POWER

SW

PG 43

AC/BATT

CONNECTOR

BATT

CHARGER

PG 40

PG 40

LAYER 8 : BOT

DDRII VR

B B

PG 39

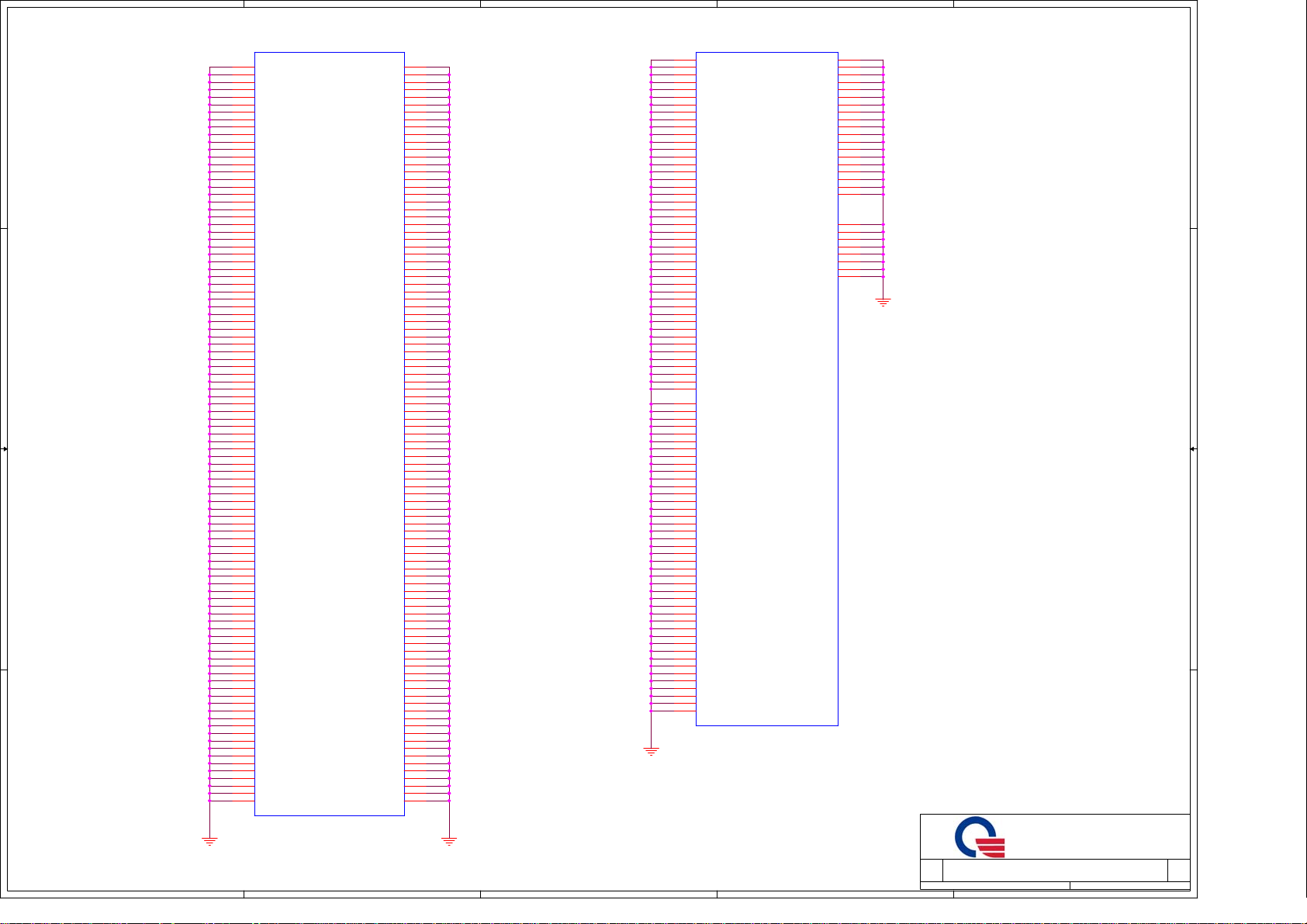

DDRII-SODIMM1

PG 16,17

DDRII-SODIMM2

PG 16,17

SATA - HDD

DDRII 533/667

DDRII 533/667

SATA0

PG 31

Internal ODD

PATA 100

CD-ROM

PG 31

C C

Azalia

MDC DAA

PG 34

Realtek

ALC268

PG 32

Audio Amplifier HP Amplifier

TPA0312

PG 33

MAX4411

PG 33

TW7- DESIGN

31TW7MB00XX

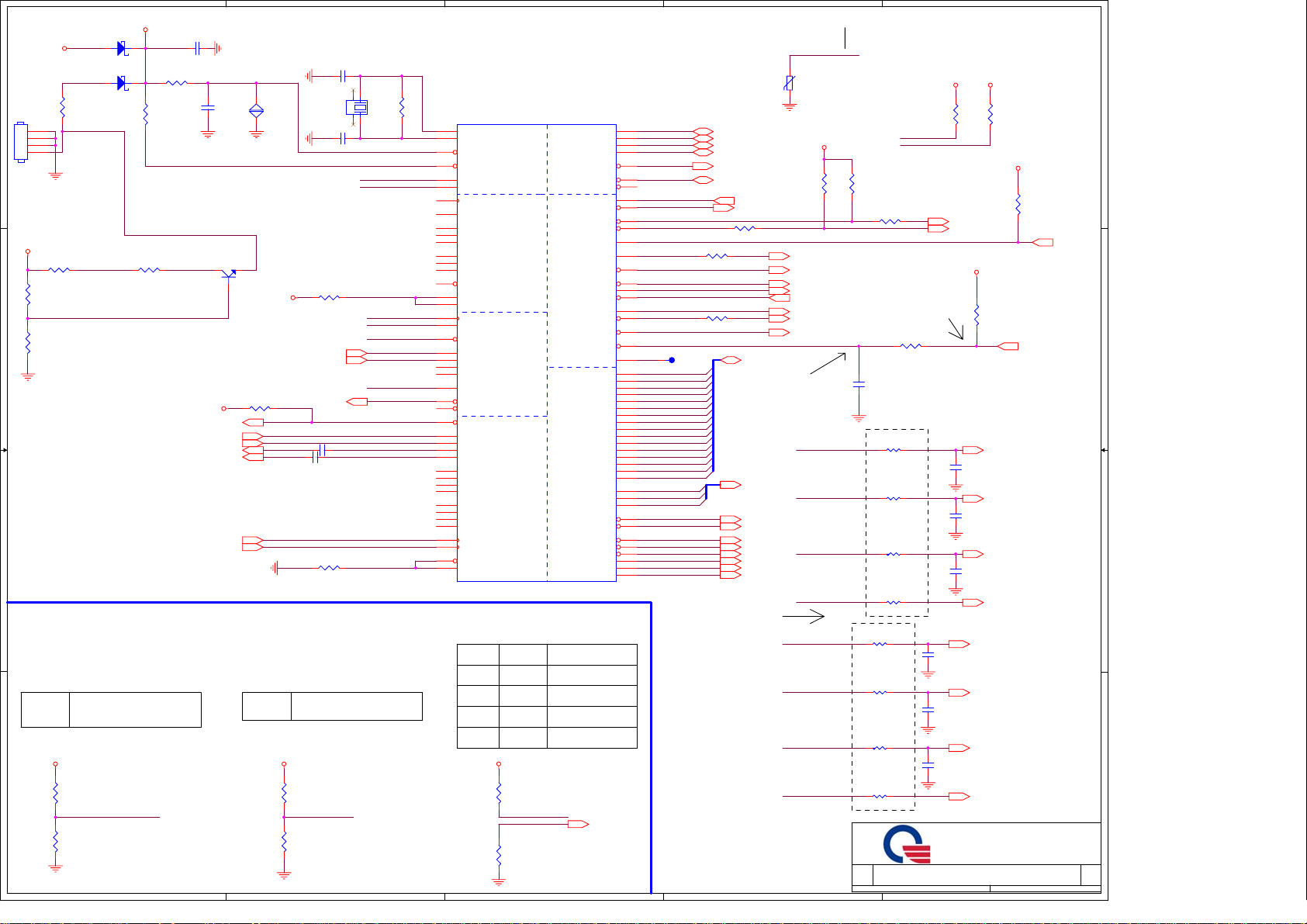

Merom

35W

(478 Micro-FCPGA)

PG 3,4

FSB 667/800

Crestline (G)MCH

965GM/PM

1299 FCBGA 35X35

PG

5,6,7,8,9,10,11

DMI X4

ICH8-M

652 BGA 31X31

PG 12,13,14,15

LPC

KBC

ENE KB3926 A01

USB2.0

(P0~P7)

PCI Bus 33MHz

PG 38

CPU VR

PG 37

LVDS(2 Channel)

TVOUT

VGA

USB2.0 (P5)

USB2.0 (P0~P1,P4)

USB2.0 (P3)

PCI-E, 1X

PCI-E, 1X

PCI-E, 1X

TI PC7402

DC/DC

3VSUS

5VSUS

PG43

PCI-Express X16

Panel Connector

S-Video

VGA,DVI

Bluetooth

USB2.0 I/O

Ports

Camera

Marvell

LAN

8055,8038

Mini PCI-E Card *2

PCI Express Mini Card

Express Card x1

NEW CARD

PG 29,30

PG 26

PG 23

PG 24

PG 24

PG 35

PG 26

PG 23

DC/DC

3VPCU

5VPCU

PG38

PG 35

PG 35

nVIDIA

NB8M-GS

533 BGA

23X23

10~13W

DDRII

16M*16(128MB)

32M*16(256MB)

(Bank*4)

64 Bit Bandwidth

Magnetics

DC/DC

+1.05V

+1.5V

PG37

PG 18~22

PG 27

RJ45

ICS9LPRS365BGLFT

PG 27

Power On

Power Input

LPT PORT

COM PORT

LAN

VGA

Headphone

1394

USB X 2

CLOCKS

PG 2

DC/DC

VGA CORE

1.15V

PG42

Function Board

RQ6

Replicator

Daughter Board

Conn

1

PG 28

USB

PG 37

154Friday, April 13, 2007

8

3A

Touch

Pad

PG 36

4

X-Bus

SPI

ROM

PG 38

IEEE1394 Card reader

CONN

PG 29

5

PG 30

Size Document Number Rev

6

Date: Sheet of

Daughter

D D

Internal Speaker

RJ11+USB

PG 33

1

Audio

Jacks

PG 30

Green Blue Pink

2

LineBoard

PG 33

Mic

Jacksin

PG 32

TPM1.2

PG 40

3

Key

Matrix

PG 36

SVID

Block Diagram

7

152D

0763SSID

PROJECT : TW7

Quanta Computer Inc.

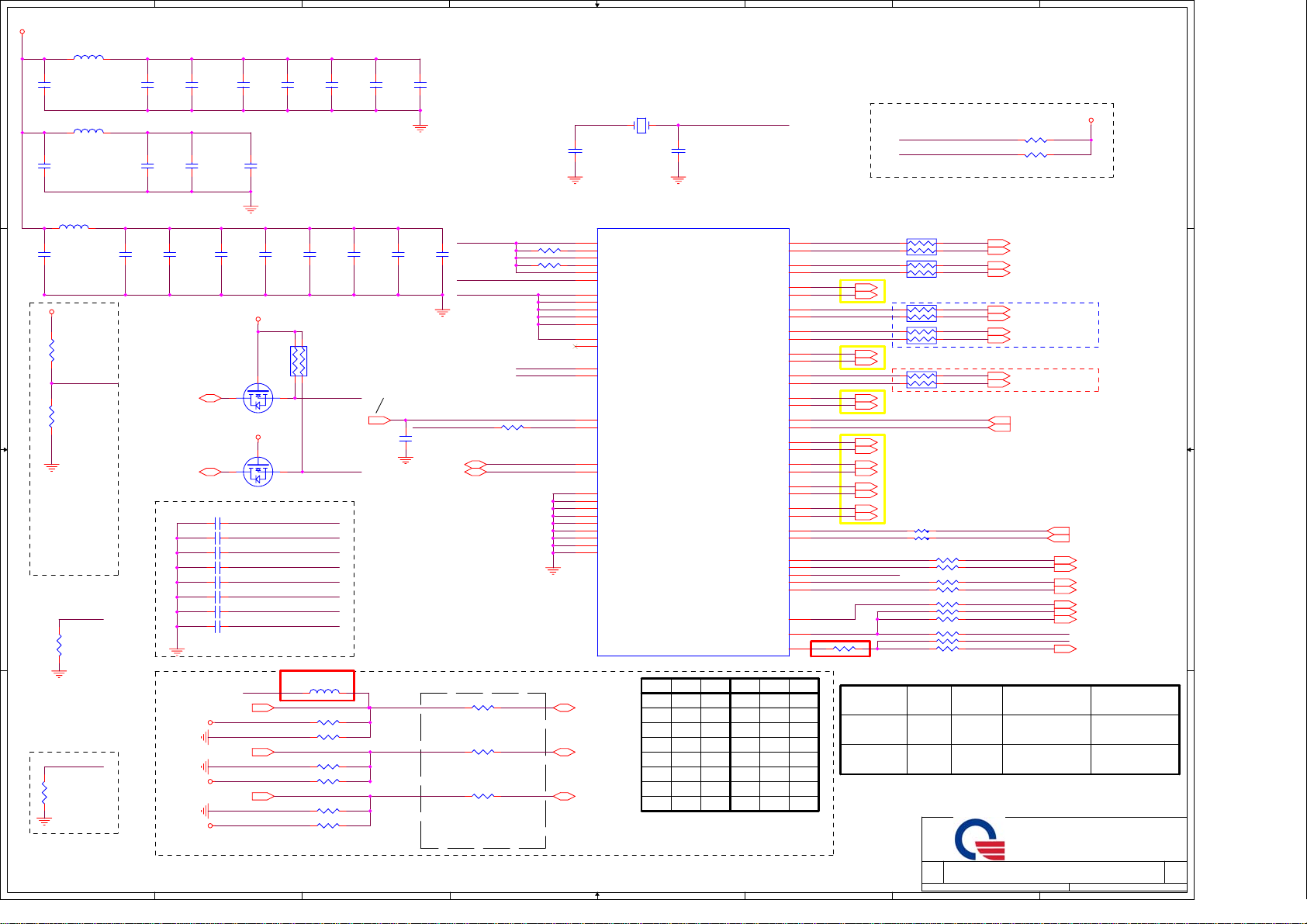

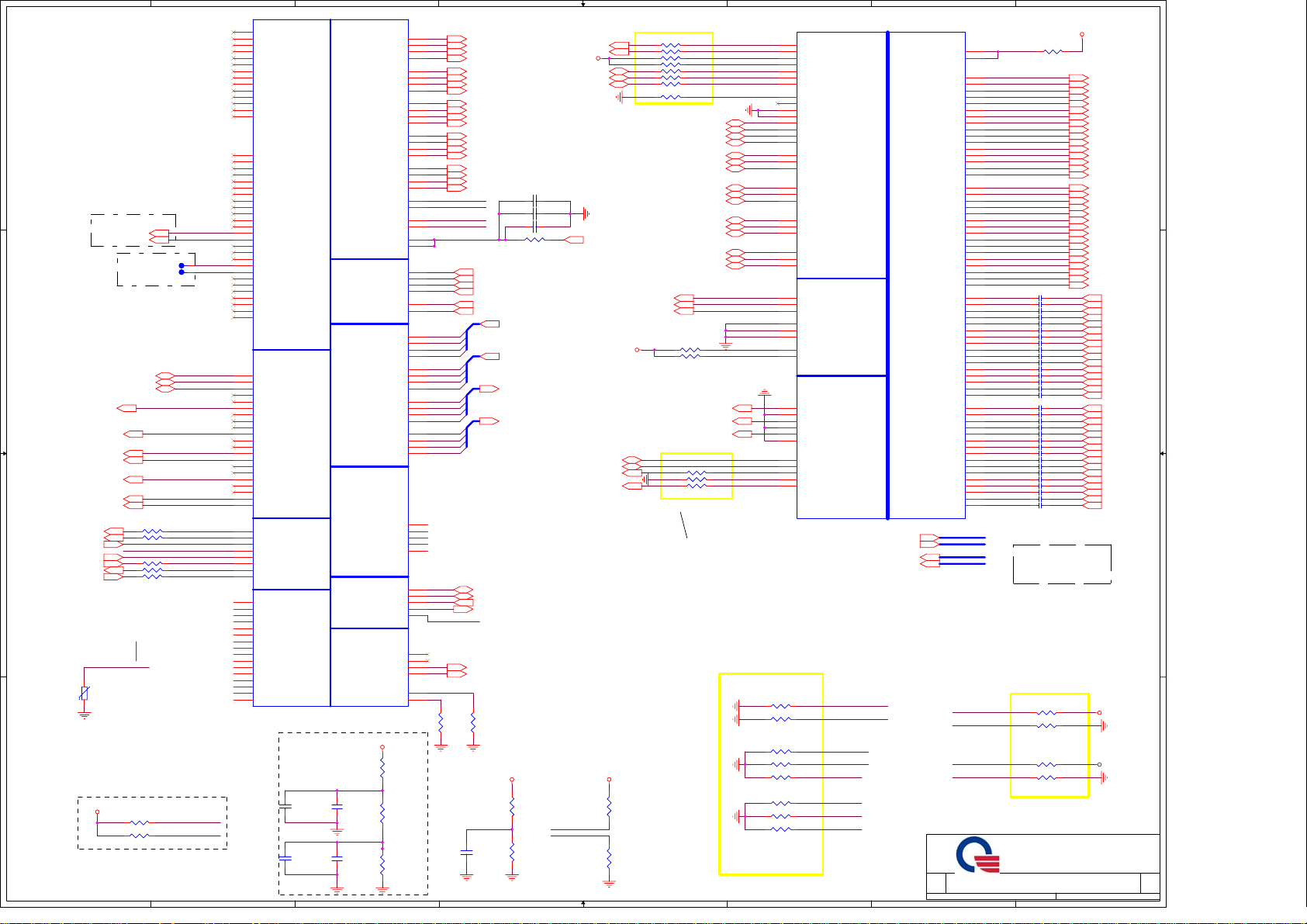

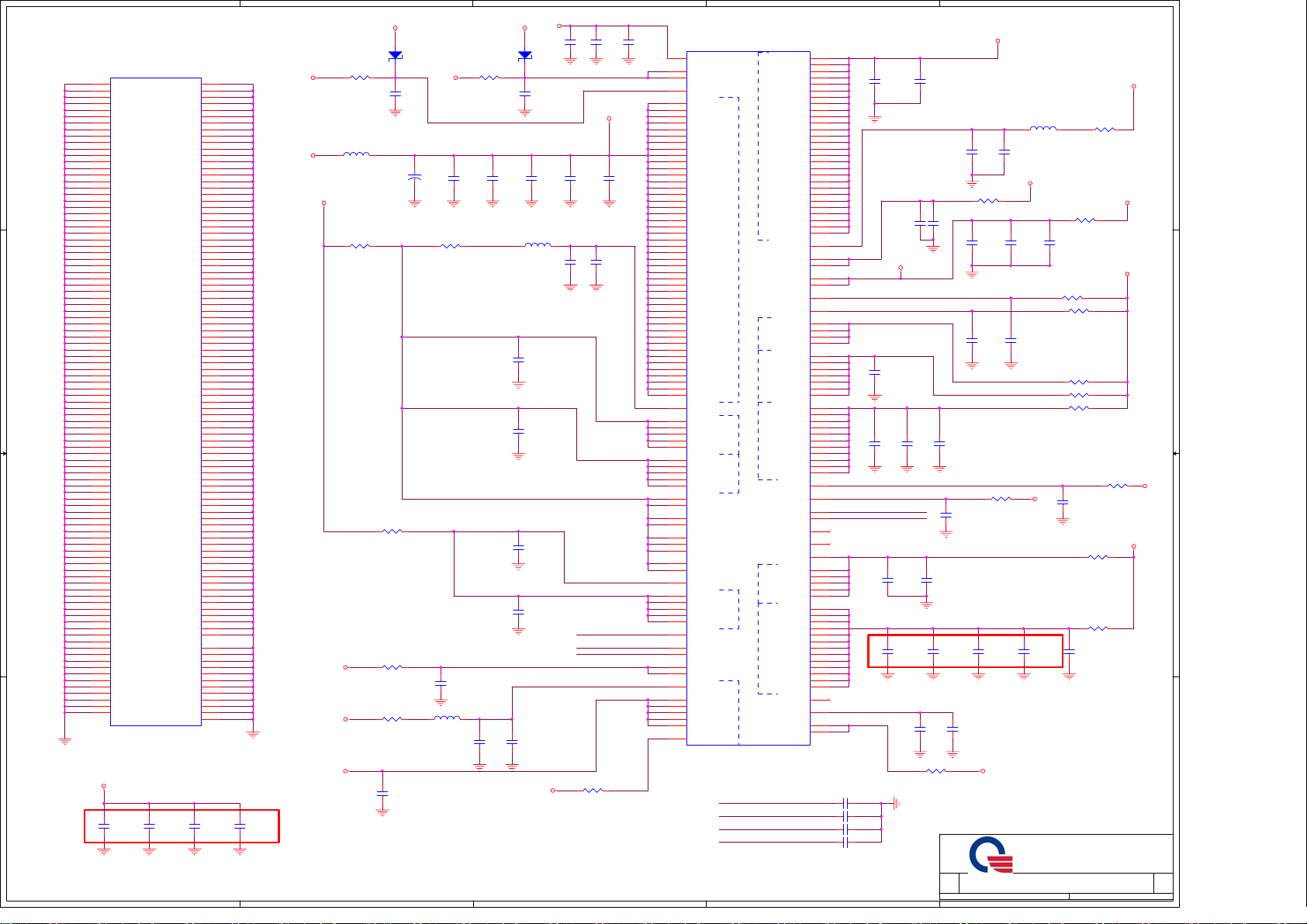

Page 2

1

+3V

120 ohms@100Mhz

L44

1 2

BLM18PG121SN1D

12

C816

0.1U/10V_4

A A

1 2

BLM18PG121SN1D

12

C808

0.1U/10V_4

L46

C534

4.7U/6.3V_6

C541

4.7U/6.3V_6

2

+CK_VDD_MAIN

C814

4.7U/6.3V_6

VDDCPU

C542

4.7U/6.3V_6

12

C850

0.1U/10V_4

12

C537

0.1U/10V_4

12

C527

0.1U/10V_4

12

C815

0.1U/10V_4

3

12

C827

0.1U/10V_4

12

C552

0.1U/10V_4

4

5

6

7

8

02

5 * 3.2

CLK_XTAL_IN

12

C812

22P/50V_4

Y5

1 2

14.318MHZ

BG614318F33

12

C813

22P/50V_4

CLK_XTAL_OUT

14.318MHz

30PPM,CL=20PF

CLK_3GPLLREQ#

NEW-CARD_CLK_REQ#

R602 10K_4

R610 10K_4

+3V

12

12

120 ohms@100Mhz

L45

1 2

BLM18PG121SN1D

12

C806

0.1U/10V_4

C547

4.7U/6.3V_6

C550

4.7U/6.3V_6

12

C824

0.1U/10V_4

+3V

B B

C C

R265

10K_4

1 2

PCI_MINIPCI

R266

*4.7K_4

0=overclocking

of CPU and

SRC Allowed

1 = overclocking

of CPU and SRC

not Allowed

FCTSEL1

R289

10K_4

1 2

0=UMA

1 = External VGA

Q28

2N7002E

PDAT_SMB[14,36]

PCLK_SMB[14,36]

3

Q27

2N7002E

3

C522 10P/50V_4

C518 10P/50V_4

C818 10P/50V_4

C810 10P/50V_4

C817 10P/50V_4

C533 10P/50V_4

C526 10P/50V_4

C513 10P/50V_4

for EMI

CPU Clock select

CPU_MCH_BSEL0[3]

+1.05V

ITP_EN

12

D D

R300

10K_4

Disable

ITP

1

CPU_MCH_BSEL1[3] MCH_BSEL1 [6]

+1.05V

CPU_MCH_BSEL2[3] MCH_BSEL2 [6]

+1.05V

2

+CK_VDD_MAIN2

12

C856

0.1U/10V_4

+3V

2

+3V

2

CLK_7402_48M

CLK_ICH_48M

PCLK_TPM

CLK_PCI_KB3926

CLK_PCI_PCCARD

CLK_PCI_ICH

PCLK_LPC_DEBUG

CLK_ICH_14M

BLM18AG601SN1D

FSLA_BSEL0

12

C830

0.1U/10V_4

2

4

RP60

4P2R-S-2.2K

1

3

CGDAT_SMB

1

CK_PWG[14]

1

L89

1 2

CPU_MCH_BSEL0

R267 *10K_4

R270 1K/F

R290 *0_4

R284 1K/F

R269 *0_4

R275 1K/F

12

C834

0.1U/10V_4

12

C835

0.1U/10V_4

+CK_VDD_MAIN

12

C847

0.1U/10V_4

VDDCPU

+CK_VDD_MAIN2

遠離螺絲孔

CK_PWG

CPU_MCH_BSEL1

C821

4.7P/50V_4

CGCLK_SMB[16,35]

CGDAT_SMB[16,35]

R571 4.7K_4

RTM875T-606-LFT(AL000875K06)

R268 0_4

R287 0_4

R272 0_4

<FAE>

1K to NB only when

XDP is implement.No

XDP can use 0 ohm

3

R570 0_4

R568 0_4

CLK_XTAL_IN

CLK_XTAL_OUT

CGCLK_SMB

CGDAT_SMBCGCLK_SMB

4

FSB

U35

16

VDDPLL3

9

VDD48

2

VDDPCI

61

VDDREF

39

VDDSRC

55

VDDCPU

20

VDDPLL3I/O

26

VDDSRCI/O

45

VDDSRCI/O

36

VDDSRCI/O

49

VDDCPU_IO

48

NC

60

X1

59

X2

56

CK_PWRGD/PD#

57

FSLB/TEST_MODE

64

SCLK

63

SDATA

15

GND

19

GND

11

GND48

52

GNDCPU

8

GNDPCI

58

GNDREF

23

GNDSRC

29

GNDSRC

42

GNDSRC

ICS9LPRS365BGLFT

MCH_BSEL0 [6]

CPU_BCLK

54

CK505

27MHz_Nonss/SRCCLK1/SE1

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUT2_ITP/SRCT8

CPUT2_ITP/SRCC8VDD96I/O

DOTT_96/SRCT0

DOTC_96/SRCC0

27Mhz_ss/SRCCLC1/SE2

SRCCLKT2/SATACL

SRCCLKC2/SATACL

SRCCLKT3/CR#_C

SRCCLKC3/CR#_D

SRCCLKT4

SRCCLKC4

PCI_STOP#

CPU_STOP#

SRCCLKT6

SRCCLKC6

SRCCLKT7/CR#_F

SRCCLKC7/CR#_E

SRCCLKT9

SRCCLKC9

SRCCLKT10

SRCCLKC10

SRCCLKT11/CR#_H

SRCCLKC11/CR#_G

PCICLK0/CR#_A

PCICLK1/CR#_B

PCICLK2/TME

PCICLK3

PCICLK4/27_SELECT

PCI_F5/ITP_EN

USB_48MHZ/FSLA

FSLC/TST_SL/REF

CPU_BCLK#

53

MCH_BCLK

51

MCH_BCLK#

50

47

4612

DOT96

13

DOT96#

14

DOT96_SSC

17

DOT96_SSC#

18

21

22

PCIE_VGA

24

PCIE_VGA#

25

27

28

38

37

41

40

44

43

30

31

34

35

NEW-CARD_CLK_REQ#_R

33

CLK_3GPLLREQ#_R

32

R_PCLK_KB3926

1

PCI_PCCARD

3

PCI_MINIPCI

4

PCICLK3

5

FCTSEL1

6

ITP_EN

7

10

R278 0_4

62

CRB-->2.2KBSEL0,BSEL2

FSC FSB

1330

0

0

0

00

1

1

1

FSA CPU SRC PCI

1100

10

1

1

0

1

0

033

0

1

0

1

1

5

133

166

200

266

333

400

RSVD

100

100

100

100

100

100

100

100

GCLK_SEL = FCTSEL1

33

33

33

33

33

33

6

0=UMA

1 = External

VGA

RP61 4P2R-S-0

4

2

RP63 4P2R-S-0

4

2

CLK_PCIE_MINI2 [35]

CLK_PCIE_MINI2# [35]

RP62 4P2R-S-0

2

4

RP64 4P2R-S-0

2

4

CLK_PCIE_SATA [12]

CLK_PCIE_SATA# [12]

RP68 *4P2R-S-0

2

4

CLK_PCIE_LAN [26]

CLK_PCIE_LAN# [26]

CLK_PCIE_ICH [13]

CLK_PCIE_ICH# [13]

CLK_PCIE_MINI1 [35]

CLK_PCIE_MINI1# [35]

CLK_MCH_3GPLL [6]

CLK_MCH_3GPLL# [6]

CLK_PCIE_EXPCARD [36]

CLK_PCIE_EXPCARD# [36]

R605 475/F

R601 475/F

R563 33

R566 33

R567 33

R285 33

R301 33

R282 22_4

R277 22_4

FSA

R273 4.7K_4

FSC

R279 4.7K_4

R271 33

FCTSEL1

(PIN13)

PIN20

DOT96T

SRCT0 SRCC0 27Mout-NSS 27Mout-SS

Size Document Number Rev

Date: Sheet of

3

1

3

1

1

3

1

3

1

3

NEW-CARD_CLK_REQ#

CLK_3GPLLREQ#

CLK_CPU_BCLK [3]

CLK_CPU_BCLK# [3]

CLK_MCH_BCLK [5]

CLK_MCH_BCLK# [5]

MCH_DREFCLK [6]

MCH_DREFCLK# [6]

DREF_SSCLK [6]

DREF_SSCLK# [6]

CLK_PCIE_VGA [18]

CLK_PCIE_VGA# [18]

PM_STPPCI# [14]

PM_STPCPU# [14]

FSLA_BSEL0

CPU_MCH_BSEL2

PIN21

SRCT1/LCDT_100DOT96C

PROJECT : TW7

Quanta Computer Inc.

CLOCK GENERATOR

7

NEW-CARD_CLK_REQ# [36]

CLK_3GPLLREQ# [6]

B2A-->Add L89,R278

PIN24

CLK_PCI_KB3926 [39]

CLK_PCI_PCCARD [29]

PCLK_TPM [41]

PCLK_LPC_DEBUG [35]

CLK_PCI_ICH [13]

CLK_7402_48M [30]

CLK_ICH_48M [14]

CLK_ICH_14M [14]

PIN25

SRCT1/LCDT_100

254Friday, April 13, 2007

8

2A

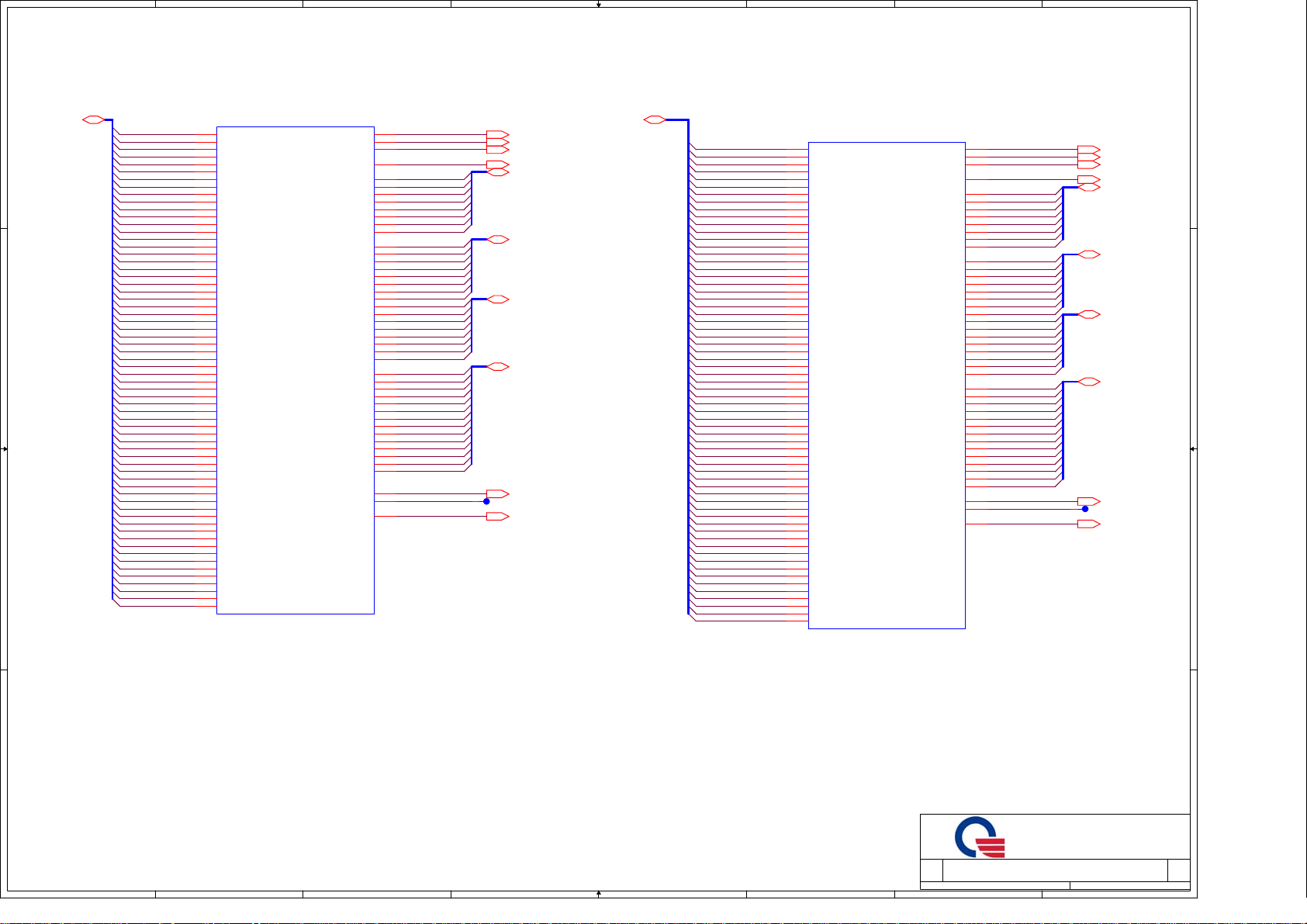

Page 3

1

H_A#[3..16][5]

A A

H_ADSTB#0[5]

H_REQ#[0..4][5]

H_A#[17..35][5]

B B

H_ADSTB#1[5]

H_A20M#[12]

H_FERR#[12]

H_IGNNE#[12]

H_STPCLK#[12]

H_INTR[12]

H_NMI[12]

H_SMI#[12]

Populate ITP700Flex for bringup

C C

+1.05V

ITP_TDI

ITP_TMS

ITP_TCK

ITP_TDO

ITP_TRST#

H_RST#

R11

D D

R10

H_A#[3..16]

H_REQ#[0..4]

H_A#[17..35]

Layout Note:

Place R4,R361,R346 & R7 close to CPU.

12

12

R9

R3

*51_4

*51/F

R8 *0_4

1 2

R1 *22.6/F_6

27.4/F

12

649/F

ITP_TCK

12

ITP_TRST#

1 2

Layout Note:

Place R8 close ITP.

12

R7

39/F

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

12

R4

150_4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

W6

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

W2

H_A#28

W5

H_A#29

H_A#30

H_A#31

H_A#32

W3

H_A#33

AA4

H_A#34

AB2

H_A#35

AA3

D22

T8

T6

T2

T7

T1

Signal Resistor Value Connect To Resistor Placement

Note: Populate R5, R8, C372 & R430 when ITP connector is populated.

1

2

U19A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

A[27]#

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Merom Ball-out Rev 1a

ADDR GROUP

0

ADDR GROUP

1

THERMAL

ICH

THERMTRIP#

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROLXDP/ITP SIGNALS

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TDO

TMS

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

H CLK

BCLK[0]

BCLK[1]

TCK

TDI

ITP debug signals

ITP_BPM#0

T12

ITP_BPM#1

T11

ITP_BPM#2

T10

ITP_BPM#3

T13T5

ITP_BPM#4

T3

ITP_BPM#5

T4

ITP disable guidelines

TDI

150 ohm +/- 5%

TMS

39 ohm +/- 1%

TRST#

500-680ohm +/- 5%

TCK

27 ohm +/- 1%

TDO

150 ohm +/- 5%

2

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

R28 56.2_4

H_IERR#

H_INIT#

H_LOCK#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

SYS_RST#

CPU_PROCHOT#CPU_PROCHOT#

H_THERMDA

H_THERMDC

PM_THRMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

FSB

BCLK

533 0 0 1133

667

166

800

200

Within 2.0" of the ITPVTT

Within 2.0" of the ITP

VTT

Within 2.0" of the ITP

GND

Within 2.0" of the ITP

GND

Within 2.0" of the ITP

VTT

3

Merom CPU Socket PN:

FOX: DGT^000021

+1.05V

TYC: DGT^000012

MLX: DGT^000004

MLX: DGT^000000

Near to CPU

Add for ESD

1 2

H_ADS# [5]

H_BNR# [5]

H_BPRI# [5]

H_DEFER# [5]

H_DRDY# [5]

H_DBSY# [5]

H_BR0# [5]

H_INIT# [12]

H_LOCK# [5]

H_RST#

H_RS#0 [5]

H_RS#1 [5]

H_RS#2 [5]

H_TRDY# [5]

H_HIT# [5]

H_HITM# [5]

遠離螺絲孔

SYS_RST# [14]

RV3

1 2

*VZ0603M260APT

H_THERMDA [4]

H_THERMDC [4]

PM_THRMTRIP# [6,12]

CLK_CPU_BCLK [2]

CLK_CPU_BCLK# [2]

BSEL2 BSEL1 BSEL0

0

1

+1.05V

3VPCU

R21

*1K/F

2

1 3

Q2

*MMBT3904

3

R2 0_4

RV1

*VZ0603M260APT

Layout Note:

Place voltage

divider within

0.5" of GTLREF

pin

0011

R19

*10K_4

THERM_CPUDIE_L#PM_THRMTRIP#

+1.05V

R32

1K/F

1 2

R33

2K/F

1 2

CPU_PROCHOT#

4

H_RESET# [5]

CPU_MCH_BSEL0[2]

CPU_MCH_BSEL1[2]

CPU_MCH_BSEL2[2]

+1.05V

12

R396

68_4

R20 *0_4

4

H_D#[0..63][5]

H_DSTBN#0[5]

H_DSTBP#0[5]

H_DINV#0[5]

H_D#[0..63][5]

H_DSTBN#1[5]

H_DSTBP#1[5]

H_DINV#1[5]

+1.05V

R394

*330_6

2

1 3

Q24

*MMBT3904

THERM_CPUDIE# [39]

THERM_CPUDIE_L# [19]

FANLESS#[39]

5

H_D#[0..63]

H_D#[0..63]

VR_TT# [42]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

V_CPU_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

+5V

R395

100K_4

Q3

DTC144EUA

2

1 3

For Throttle Function

5

U19B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

Merom Ball-out Rev 1a

R26 *1K/F

1 2

R27 *1K/F

1 2

C93 *0.1U/10V_4

R23 *0_4

1 2

Place C close to the

CPU_TEST4 pin. Make sure

CPU_TEST4 routing is

reference to GND and away

from other noisy signal.

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL[0]

BSEL[1]

BSEL[2]

12

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

MISC

PWRGOOD

CPU_TEST1

CPU_TEST2

CPU_TEST4

CPU_TEST6

CPU_PROCHOT#

3

2

1

3

2

1

6

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

Q25

2N7002E

Q4

*2N7002E

6

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

VGA_LESS# [19]

H_D#[0..63]

H_D#[0..63]

7

H_D#[0..63] [5]

H_DSTBN#2 [5]

H_DSTBP#2 [5]

H_DINV#2 [5]

H_D#[0..63] [5]

Reserved for EMI.

8

03

+1.05V

12

C651

0.1U/10V_4

+1.5V

H_DSTBN#3 [5]

H_DSTBP#3 [5]

Note:

H_DPRTSTP need to daisy chain

from ICH8 to IMVP6 to CPU.

For the purpose of testability, route these signals

through a ground referenced Z0 = 55ohm trace that

ends in a via that is near a GND via and is

accessible through an oscilloscope connection.

H_DINV#3 [5]

H_DPRSTP# [6,12,42]

H_DPSLP# [12]

H_DPWR# [5]

H_CPUSLP# [5]

PM_PSI# [42]

T15

T39

CPU_TEST3

CPU_TEST5

COMP0

COMP1

COMP2

COMP3

1 2

Comp0,2 connect with Zo=27.4ohm,Comp1,3

connect with Zo=55ohm, make those traces

length shorter than 0.5".Trace should be

at least 25 mils away from any other

toggling signal.

R5

54.9/F

RV2

1 2

R6

27.4/F

12

*VZ0603M260APT

1 2

遠離螺絲孔

H_PWRGD [12]

R31

54.9/F

1 2

R30

27.4/F

PROJECT : TW7

Size Document Number Rev

Merom (HOST BUS)

Date: Sheet of

7

Quanta Computer Inc.

354Friday, April 13, 2007

8

2B

Page 4

1

VCC_CORE

12

C20

10U/6.3V_8

A A

VCC_CORE

12

C21

10U/6.3V_8

10U/4V_8 *32

12

C41

10U/6.3V_8

12

C22

10U/6.3V_8

12

C46

10U/6.3V_8

12

C43

10U/6.3V_8

8 inside cavity, north side, secondary layer.

VCC_CORE

12

C40

10U/6.3V_8

12

C52

10U/6.3V_8

12

C53

10U/6.3V_8

VCC_CORE

B B

12

C37

10U/6.3V_8

12

C49

10U/6.3V_8

12

C42

10U/6.3V_8

8 inside cavity, south side, secondary layer.

VCC_CORE

12

C56

10U/6.3V_8

12

C28

10U/6.3V_8

12

C17

10U/6.3V_8

6 inside cavity, north side, primary layer.

VCC_CORE

12

C C

C57

10U/6.3V_8

12

C30

10U/6.3V_8

12

C44

10U/6.3V_8

6 inside cavity, south side, primary layer.

+1.05V

12

Layout out:

Place these inside socket cavity on North side secondary.

D D

12

C60

0.1U/10V_4

MBDATA[39,45] LM86_SMD [19,20]

MBCLK[39,45]

1

C18

0.1U/10V_4

12

C59

0.1U/10V_4

2N7002E

2N7002E

Q5

3

Q6

3

12

+3V

2

+3V

2

12

C39

10U/6.3V_8

12

C58

10U/6.3V_8

12

C23

10U/6.3V_8

12

C38

10U/6.3V_8

12

C51

10U/6.3V_8

12

C48

10U/6.3V_8

C19

0.1U/10V_4

1

1

2

12

C16

10U/6.3V_8

12

C47

10U/6.3V_8

12

C33

10U/6.3V_8

12

C24

10U/6.3V_8

12

12

12

C6

0.1U/10V_4

LM86_SMD

LM86_SMC

2

C34

10U/6.3V_8

C54

10U/6.3V_8

12

12

12

C7

0.1U/10V_4

C27

10U/6.3V_8

C31

10U/6.3V_8

THERM_ALERT#[14]

LM86_SMC [19,20]

3

3

R52

R38

10K_4

10K_4

LM86_SMC

LM86_SMD

THERM_ALERT#

4

VCC_CORE VCC_CORE

+3V

R37

10K_4

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

U1

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

GMT-781

ADDRESS: 98H

U19C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCCSENSE

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VSSSENSE

Merom Ball-out Rev 1a

+3V

R34

*100

25mils

LM86VCC

1

VCC

2

DXP

3

DXN

5

GND

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

5V_AL

R653

100

G3D

.

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

TP_VCCSENSE

AF7

TP_VSSSENSE

AE7

C89

0.1U/10V_4

H_THERMDA

C88

*2200pF/50V

H_THERMDC

SYS_SHDN-1#

add hardware protect

SYS_SHDN-1#[19]

4

5

ICCODE:

for Merom processors

recommended design

target is 44A

ICCP:

1before vccore stable

peak current is 4.5A

2.after vccore stable

continue current is

2.5A

+1.05V

C5

+

330U/2V/ESR9

ICCA 130mA

CPU_VID0 [42]

CPU_VID1 [42]

CPU_VID2 [42]

CPU_VID3 [42]

CPU_VID4 [42]

CPU_VID5 [42]

CPU_VID6 [42]

H_THERMDA [3]

10/10mils

E3B

H_THERMDC [3]

D3A

SYS_SHDN-1#

5

12

C655

0.01U/16V_4

6

+1.5V

Layout Note:

Place C105 near PIN

B26.

12

C656

10U/6.3V_8

VCC_CORE

R22

100/F

R18

100/F

R47 *0_4

+3V

R59

1M_4

3

2

Q9

2N7002E

1

6

TP_VCCSENSE [42]

TP_VSSSENSE [42]

2

12

C155

0.1U/10V_4

7

U19D

A4

VSS[001]

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3 A25

THERM_OVER# [39,43]

3

Q7

2N7002E

1

Size Document Number Rev

Merom Processor (P OWER )

Date: Sheet

7

VSS[082]

VSS[083]

VSS[002]

VSS[084]

VSS[003]

VSS[085]

VSS[004]

VSS[086]

VSS[005]

VSS[087]

VSS[006]

VSS[088]

VSS[007]

VSS[089]

VSS[008]

VSS[090]

VSS[009]

VSS[091]

VSS[010]

VSS[092]

VSS[011]

VSS[093]

VSS[012]

VSS[094]

VSS[013]

VSS[095]

VSS[014]

VSS[096]

VSS[015]

VSS[097]

VSS[016]

VSS[098]

VSS[017]

VSS[099]

VSS[018]

VSS[100]

VSS[019]

VSS[101]

VSS[020]

VSS[102]

VSS[021]

VSS[103]

VSS[022]

VSS[104]

VSS[023]

VSS[105]

VSS[024]

VSS[106]

VSS[025]

VSS[107]

VSS[026]

VSS[108]

VSS[027]

VSS[109]

VSS[028]

VSS[110]

VSS[029]

VSS[111]

VSS[030]

VSS[112]

VSS[031]

VSS[113]

VSS[032]

VSS[033]

VSS[114]

VSS[034]

VSS[115]

VSS[035]

VSS[116]

VSS[036]

VSS[117]

VSS[037]

VSS[118]

VSS[038]

VSS[119]

VSS[039]

VSS[120]

VSS[040]

VSS[121]

VSS[041]

VSS[122]

VSS[042]

VSS[123]

VSS[043]

VSS[124]

VSS[044]

VSS[125]

VSS[045]

VSS[126]

VSS[046]

VSS[127]

VSS[047]

VSS[128]

VSS[048]

VSS[129]

VSS[049]

VSS[130]

VSS[050]

VSS[131]

VSS[051]

VSS[132]

VSS[052]

VSS[133]

VSS[053]

VSS[134]

VSS[054]

VSS[135]

VSS[055]

VSS[136]

VSS[056]

VSS[137]

VSS[057]

VSS[138]

VSS[058]

VSS[139]

VSS[059]

VSS[140]

VSS[060]

VSS[141]

VSS[061]

VSS[142]

VSS[062]

VSS[143]

VSS[063]

VSS[144]

VSS[064]

VSS[145]

VSS[065]

VSS[146]

VSS[147]

VSS[066]

VSS[067]

VSS[148]

VSS[149]

VSS[068]

VSS[150]

VSS[069]

VSS[070]

VSS[151]

VSS[071]

VSS[152]

VSS[072]

VSS[153]

VSS[073]

VSS[154]

VSS[074]

VSS[155]

VSS[075]

VSS[156]

VSS[076]

VSS[157]

VSS[077]

VSS[158]

VSS[078]

VSS[159]

VSS[079]

VSS[160]

VSS[080]

VSS[161]

VSS[081] VSS[162]

VSS[163]

Merom Ball-out Rev 1a

PROJECT : TW7

Quanta Computer Inc.

8

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF25

.

454Friday, April 13, 2007

8

04

3D

of

Page 5

1

2

3

4

5

6

7

8

05

H_A#[3..35]

H_ADS# [3]

H_ADSTB#0 [3]

H_ADSTB#1 [3]

H_BNR# [3]

H_BPRI# [3]

H_BR0# [3]

H_DEFER# [3]

H_DBSY# [3]

CLK_MCH_BCLK [2]

CLK_MCH_BCLK# [2]

H_DPWR# [3]

H_DRDY# [3]

H_HIT# [3]

H_HITM# [3]

H_LOCK# [3]

H_TRDY# [3]

H_DINV#0 [3]

H_DINV#1 [3]

H_DINV#2 [3]

H_DINV#3 [3]

H_DSTBN#0 [3]

H_DSTBN#1 [3]

H_DSTBN#2 [3]

H_DSTBN#3 [3]

H_DSTBP#0 [3]

H_DSTBP#1 [3]

H_DSTBP#2 [3]

H_DSTBP#3 [3]

H_REQ#0 [3]

H_REQ#1 [3]

H_REQ#2 [3]

H_REQ#3 [3]

H_REQ#4 [3]

H_RS#0 [3]

H_RS#1 [3]

H_RS#2 [3]

H_A#[3..35] [3]

Short Stub < 100mils

extract from same point

M10

W10

AD12

AE3

AD9

AC9

AC7

AC14

AD11

AC11

AB2

AD7

AB1

AC6

AE2

AC5

AG3

AH8

AJ14

AE9

AE11

AH12

AH5

AE7

AE5

AH2

AH13

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

N12

N9

H5

P13

K9

M2

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

Y3

AJ9

AJ5

AJ6

AJ7

AJ2

AJ3

B3

C2

W1

W2

B6

E5

B9

A9

U24A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRESTLINE_1p0

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_CPUSLP#[3]

12

H_D#[0..63]

C185

0.1U/10V_4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPUSLP#

H_REF

C138

0.1U/10V_4

H_D#[0..63][3]

A A

+1.05V

12

R57

221/F

H_SWING

12

R56

100/F

B B

+1.05V

1 2

impedance 55 ohm

12

12

R410

R411

54.9/F

54.9/F

H_SCOMP

H_SCOMP#

12

C C

H_RESET#[3]

D D

H_RCOMP

R58

24.9_6

Layout Note:

H_RCOMP trace should be

10-mil wide with 20-mil

spacing.

R413

0_4

RV7

*VZ0603M260APT

Near NB

Add for ESD

12

+1.05V

R69

1K/F

1 2

12

R73

2K/F

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

Layout Note:

Place the 0.1 uF

decoupling capacitor

within 100 mils from

GMCH pins.

1

2

3

4

5

6

Size Document Number Rev

Crestline (HOST)

Date: Sheet

7

PROJECT : TW7

Quanta Computer Inc.

554Friday, April 13, 2007

of

8

1A

Page 6

1

A A

B B

DELAY_VR_PWRGOOD[14,42]

C C

WW22 update

--- MA14 needs

to be routed if

customers are

planning on

using 2Gb

technology and

width=8 (by 8)

DIMMs

SA_MA14[16,17]

SB_MA14[16,17]

CRESTLINE

new pin

define

Layout Note:

Location of all MCH_CFG strap

resistors needs to be close to

minmize stub.

MCH_CFG_5[11]

MCH_CFG_9[11]

MCH_CFG_12[11]

MCH_CFG_13[11]

MCH_CFG_16[11]

MCH_CFG_19[11]

MCH_CFG_20[11]

PM_BMBUSY#[14]

H_DPRSTP#[3,12,42]

PM_EXTTS#0[16]

PLT_RST-R#[13]

PM_THRMTRIP#[3,12]

PM_DPRSLPVR[14,42]

GMCH pwrok is 3.3v

tolerant

T29 PAD

T28 PAD

MCH_BSEL0[2]

MCH_BSEL1[2]

MCH_BSEL2[2]

R146 0_4

R142 0_4

R88 100_4

R91 0_4

R137 0_4

PM_BMBUSY#_R

ICH_DPRSTP#_R

PM_EXTTS#0

PM_EXTTS#1

DELAY_VR_PWRGOOD

PLTRST_MCH#

PM_THRMTRIP#_GMCH

PM_DPRSLPVR_GMCH

遠離螺絲孔

DELAY_VR_PWRGOOD

12

Near to NB

RV4

*VZ0603M260APT

D D

+3V

R141 10K_4

1 2

R130 10K_4

1 2

1

SA_MA14

SB_MA14

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

PM_EXTTS#0

PM_EXTTS#1

2

U24B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

SA-MA14

BE24

SB_MA14

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

LVDSA_DATA#_3

D47

LVDSA_DATA_3

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

C21

CFG_3

C23

CFG5

CFG9

CFG12

CFG13

CFG16

CFG19

CFG20

CFG_4

F23

CFG_5

N23

CFG_6

G23

CFG_7

J20

CFG_8

C20

CFG_9

R24

CFG_10

L23

CFG_11

J23

CFG_12

E23

CFG_13

E20

CFG_14

K23

CFG_15

M20

CFG_16

M24

CFG_17

L32

CFG_18

N33

CFG_19

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

BL2

NC_7

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2 R32

NC_16 TEST_2

CRESTLINE_1p0

SM_RCOMP_VOH

12

C309

0.01U/16V_4

SM_RCOMP_VOL

12

C283

0.01U/16V_4

2

DDR MUXINGCLKDMI

CFGRSVD

PM

GRAPHICS VIDME

NC

MISC

12

C302

2.2U/6.3V_6

12

C300

2.2U/6.3V_6

3

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

TEST_1

1.8VSUS

12

R125

1K/F

12

R123

3.01K/F

12

R113

1K/F

3

AV29

BB23

BA25

AV23

AW30

BA23

AW25

AW23

BE29

AY32

BD39

BG37

BG20

BK16

BG16

BE13

BH18

BJ15

BJ14

BE16

SMRCOMPP

BL15

SMRCOMPN

BK14

SM_RCOMP_VOH

BK31

SM_RCOMP_VOL

BL31

SMDDR_VREF_MCH

SMDDR_VREF_MCH

AR49

AW4

B42

C42

H48

H47

K44

K45

DMI_TXN0

AN47

DMI_TXN1

AJ38

DMI_TXN2

AN42

DMI_TXN3

AN46

DMI_TXP0

AM47

DMI_TXP1

AJ39

DMI_TXP2

AN41

DMI_TXP3

AN45

DMI_RXN0

AJ46

DMI_RXN1

AJ41

DMI_RXN2

AM40

DMI_RXN3

AM44

DMI_RXP0

AJ47

DMI_RXP1

AJ42

DMI_RXP2

AM39

DMI_RXP3

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

MCH_CLVREF

H35

K36

G39

G40

A37

R122

20K

1 2

4

M_A_CLK0 [16]

M_A_CLK1 [16]

M_B_CLK0 [16]

M_B_CLK1 [16]

M_A_CLK0# [16]

M_A_CLK1# [16]

M_B_CLK0# [16]

M_B_CLK1# [16]

M_A_CKE0 [16,17]

M_A_CKE1 [16,17]

M_B_CKE0 [16,17]

M_B_CKE1 [16,17]

M_A_CS#0 [16,17]

M_A_CS#1 [16,17]

M_B_CS#0 [16,17]

M_B_CS#1 [16,17]

M_A_ODT0 [16,17]

M_A_ODT1 [16,17]

M_B_ODT0 [16,17]

M_B_ODT1 [16,17]

C110 470P/50V/X7R/04

C124 0.1U/10V_4

C115 0.1U/10V_4

R44 0_4

MCH_DREFCLK [2]

MCH_DREFCLK# [2]

DREF_SSCLK [2]

DREF_SSCLK# [2]

CLK_MCH_3GPLL [2]

CLK_MCH_3GPLL# [2]

DMI_TXN[3:0] [13]

DMI_TXP[3:0] [13]

DMI_RXN[3:0] [13]

DMI_RXP[3:0] [13]

CL_CLK0 [14]

CL_DATA0 [14]

ECPWROK [14,39]

CL_RST#0 [14]

CLK_3GPLLREQ# [2]

MCH_ICH_SYNC# [14]

R485

0_4

1 2

+1.25V

12

MCH_CLVREF

12

C746

0.1U/10V_4

1 2

4

R512

1K/F

R511

392/F

1 2

LCD_BKLTCTL[19,23]

LCD_BLON_AND[19,23]

96 Mhz

100 Mhz

SMRCOMPP

SMRCOMPN

+3V

EDIDCLK[19,23]

EDIDDATA[19,23]

ENVDD[19,23]

SMDDR_VREF [16,41,44]

NB_DDCCLK[25]

NB_DDCDAT[25]

NB_HSYNC_COM[22]

NB_VSYNC_COM[22]

1.8VSUS

R78

20/F

R77

20/F

12

12

R139 0_6

R140 0_6

R136 10K_4

R484 10K_4

R480 0_6

R478 0_6

R148 0_6

R144 2.4K

NB_TV_COMP[22]

NB_TV_Y/G[22]

NB_TV_C/R[22]

+3V

5

NB_TXLCLKOUT-[22]

NB_TXLCLKOUT+[22]

NB_TXUCLKOUT-[22]

NB_TXUCLKOUT+[22]

NB_TXLOUT0-[22]

NB_TXLOUT1-[22]

NB_TXLOUT2-[22]

NB_TXLOUT0+[22]

NB_TXLOUT1+[22]

NB_TXLOUT2+[22]

NB_TXUOUT0-[22]

NB_TXUOUT1-[22]

NB_TXUOUT2-[22]

NB_TXUOUT0+[22]

NB_TXUOUT1+[22]

NB_TXUOUT2+[22]

R131 2.2K

R133 2.2K

NB_CRT_B_COM[22]

NB_CRT_G_COM[22]

NB_CRT_R_COM[22]

R128 39

R112 1.3K_6

R124 39

<check list>

HSYNC/VSYNC serial R

place close to NB

For GM -->39 ohm

PM-->NC

5

L_BKLT_EN

LVDS_IBG

NB_TV_COMP

NB_TV_Y/G

NB_TV_C/R

TV_DCONSEL_0

TV_DCONSEL_1

NB_DDCCLK

NB_DDCDAT

HSYNC11

CRTIREF

VSYNC11

<check list>

For EV@

Connect to GND

CRT R/G/B

TV A/B/C

HSYNC/VSYNC

R129 *39_4

R121 *39_4

R107 150_4

R106 150_4

R104 150_4

R110 150_4

R111 150_4

R119 150_4

6

U24C

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

B47

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LVDSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TV_DCONSEL_0

P33

TV_DCONSEL_1

H32

CRT_BLUE

G32

CRT_BLUE#

K29

CRT_GREEN

J29

CRT_GREEN#

F29

CRT_RED

E29

CRT_RED#

K33

CRT_DDC_CLK

G35

CRT_DDC_DATA

F33

CRT_HSYNC

C32

CRT_TVO_IREF

E33

CRT_VSYNC

CRESTLINE_1p0

6

<check list>

For IV@

Connect to 150ohm

CRT R/G/B

TV A/B/C

Connect to 39ohm

HSYNC/VSYNC

HSYNC11

VSYNC11

NB_TV_C/R

NB_TV_COMP

NB_CRT_B_COM

NB_CRT_G_COM

NB_CRT_R_COM

For GM

-->150 ohm

For PM --> 0 ohm

7

VCC3G_PCIE_R

N43

PEG_COMPI

M43

PEG_COMPO

PEG_RXN0

J51

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

LVDS

TV VGA

PEG_RXP[15:0][18]

PEG_RXN[15:0][18]

PEG_TXP[15:0][18]

PEG_TXN[15:0][18]

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PCI-EXPRESS GRAPHICS

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

PEG_RXN1

L51

PEG_RXN2

N47

PEG_RXN3

T45

PEG_RXN4

T50

PEG_RXN5

U40

PEG_RXN6

Y44

PEG_RXN7

Y40

PEG_RXN8

AB51

PEG_RXN9

W49

PEG_RXN10

AD44

PEG_RXN11

AD40

PEG_RXN12

AG46

PEG_RXN13

AH49

PEG_RXN14

AG45

PEG_RXN15

AG41

PEG_RXP0

J50

PEG_RXP1

L50

PEG_RXP2

M47

PEG_RXP3

U44

PEG_RXP4

T49

PEG_RXP5

T41

PEG_RXP6

W45

PEG_RXP7

W41

PEG_RXP8

AB50

PEG_RXP9

Y48

PEG_RXP10

AC45

PEG_RXP11

AC41

PEG_RXP12

AH47

PEG_RXP13

AG49

PEG_RXP14

AH45

PEG_RXP15

AG42

C_PEG_TXN0

N45

C_PEG_TXN1

U39

C_PEG_TXN2

U47

C_PEG_TXN3

N51

C_PEG_TXN4

R50

C_PEG_TXN5

T42

C_PEG_TXN6

Y43

C_PEG_TXN7

W46

C_PEG_TXN8

W38

C_PEG_TXN9

AD39

C_PEG_TXN10

AC46

C_PEG_TXN11

AC49

C_PEG_TXN12

AC42

C_PEG_TXN13

AH39

C_PEG_TXN14

AE49

C_PEG_TXN15

AH44

C_PEG_TXP0

M45

C_PEG_TXP1

T38

C_PEG_TXP2

T46

C_PEG_TXP3

N50

C_PEG_TXP4

R51

C_PEG_TXP5

U43

C_PEG_TXP6

W42

C_PEG_TXP7

Y47

C_PEG_TXP8

Y39

C_PEG_TXP9

AC38

C_PEG_TXP10

AD47

C_PEG_TXP11

AC50

C_PEG_TXP12

AD43

C_PEG_TXP13

AG39

C_PEG_TXP14

AE50

C_PEG_TXP15

AH43

IV&EV Dis/Enable setting

<check list>

SDVO/PCIE/LVDS not

implement

16 lanes NC

DREF_SSCLK

DREF_SSCLK#

<FAE>

If no use DREFCLK PU and

DREFCLK# PD

MCH_DREFCLKNB_TV_Y/G

MCH_DREFCLK#

<design guide>

If no use

DREFCLK PU and

DREFCLK# PD

R151 *80.6_4

R153 *80.6_4

R150 *80.6_4

R149 *80.6_4

PROJECT : TW7

Size Document Number Rev

Crestline (VGA,DMI)

Date: Sheet of

7

Quanta Computer Inc.

R155 24.9_6

1 2

C724 *0.1U/10V_4

C744 *0.1U/10V_4

C757 *0.1U/10V_4

C748 *0.1U/10V_4

C750 *0.1U/10V_4

C428 *0.1U/10V_4

C426 *0.1U/10V_4

C756 *0.1U/10V_4

C436 *0.1U/10V_4

C776 *0.1U/10V_4

C782 *0.1U/10V_4

C786 *0.1U/10V_4

C443 *0.1U/10V_4

C763 *0.1U/10V_4

C452 *0.1U/10V_4

C778 *0.1U/10V_4

C722 *0.1U/10V_4

C730 *0.1U/10V_4

C745 *0.1U/10V_4

C747 *0.1U/10V_4

C749 *0.1U/10V_4

C427 *0.1U/10V_4

C424 *0.1U/10V_4

C755 *0.1U/10V_4

C435 *0.1U/10V_4

C775 *0.1U/10V_4

C781 *0.1U/10V_4

C785 *0.1U/10V_4

C439 *0.1U/10V_4

C762 *0.1U/10V_4

C456 *0.1U/10V_4

C784 *0.1U/10V_4

+VCC_PEG

8

06

PEG_RXN0 [18]

PEG_RXN1 [18]

PEG_RXN2 [18]

PEG_RXN3 [18]

PEG_RXN4 [18]

PEG_RXN5 [18]

PEG_RXN6 [18]

PEG_RXN7 [18]

PEG_RXN8 [18]

PEG_RXN9 [18]

PEG_RXN10 [18]

PEG_RXN11 [18]

PEG_RXN12 [18]

PEG_RXN13 [18]

PEG_RXN14 [18]

PEG_RXN15 [18]

PEG_RXP0 [18]

PEG_RXP1 [18]

PEG_RXP2 [18]

PEG_RXP3 [18]

PEG_RXP4 [18]

PEG_RXP5 [18]

PEG_RXP6 [18]

PEG_RXP7 [18]

PEG_RXP8 [18]

PEG_RXP9 [18]

PEG_RXP10 [18]

PEG_RXP11 [18]

PEG_RXP12 [18]

PEG_RXP13 [18]

PEG_RXP14 [18]

PEG_RXP15 [18]

PEG_TXN0 [18]

PEG_TXN1 [18]

PEG_TXN2 [18]

PEG_TXN3 [18]

PEG_TXN4 [18]

PEG_TXN5 [18]

PEG_TXN6 [18]

PEG_TXN7 [18]

PEG_TXN8 [18]

PEG_TXN9 [18]

PEG_TXN10 [18]

PEG_TXN11 [18]

PEG_TXN12 [18]

PEG_TXN13 [18]

PEG_TXN14 [18]

PEG_TXN15 [18]

PEG_TXP0 [18]

PEG_TXP1 [18]

PEG_TXP2 [18]

PEG_TXP3 [18]

PEG_TXP4 [18]

PEG_TXP5 [18]

PEG_TXP6 [18]

PEG_TXP7 [18]

PEG_TXP8 [18]

PEG_TXP9 [18]

PEG_TXP10 [18]

PEG_TXP11 [18]

PEG_TXP12 [18]

PEG_TXP13 [18]

PEG_TXP14 [18]

PEG_TXP15 [18]

+1.25V

+1.25V

654Friday, April 13, 2007

8

2A

Page 7

1

2

3

4

5

6

7

8

07

M_A_DQ[63:0][16] M_B_DQ[63:0][16]

A A

B B

C C

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BG10

AW9

AM8

AN10

AM9

AN11

BD8

AY9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AT9

AN9

U24D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRESTLINE_1p0

M_A_BS#0

BB19

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

DDR SYSTEM MEMORY A

SA_WE#

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

M_A_BS#1

M_A_BS#2

M_A_CAS#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_RAS#

TP_SA_RCVEN#

M_A_WE#

M_A_BS#0 [16,17]

M_A_BS#1 [16,17]

M_A_BS#2 [16,17]

M_A_CAS# [16,17]

M_A_DM[0..7] [16]

M_A_DQS[7:0] [16]

M_A_DQS#[7:0] [16]

M_A_A[13:0] [16,17]

M_A_RAS# [16,17]

T18

M_A_WE# [16,17]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK10

BG1

BC2

BK3

BE4

BD3

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

BL9

BK5

BL5

BK9

BJ8

BJ6

BF4

BH5

BJ2

U24E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRESTLINE_1p0

M_B_BS#0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

M_B_BS#1

M_B_BS#2

M_B_CAS#

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_RAS#

TP_SB_RCVEN#

M_B_WE#

M_B_BS#0 [16,17]

M_B_BS#1 [16,17]

M_B_BS#2 [16,17]

M_B_CAS# [16,17]

M_B_DM[0..7] [16]

M_B_DQS[7:0] [16]

M_B_DQS#[7:0] [16]

M_B_A[13:0] [16,17]

M_B_RAS# [16,17]

T17 PAD

M_B_WE# [16,17]

D D

PROJECT : TW7

Size Document Number Rev

Crestline (DDR)

1

2

3

4

5

6

Date: Sheet

Quanta Computer Inc.

7

754Friday, April 13, 2007

8

1A

of

Page 8

+1.05V

5

U24G

AT35

VCC_1

AT34

VCC_2

AH28

VCC_3

AC32

VCC_5

AC31

VCC_4

AK32

VCC_6

AJ31

VCC_7

AJ28

VCC_8

AH32

VCC_9

D D

IVCCSM supply

current 1

channel

1.615A 2

channel

3.318A

C C

1.8VSUS

AH31

AH29

AF32

AU32

AU33

AU35

AV33

AW33

AW35

AY35

BA32

BA33

BA35

BB33

BC32

BC33

BC35

BD32

BD35

BE32

BE33

BE35

BF33

BF34

BG32

BG33

BG35

BH32

BH34

BH35

BJ32

BJ33

BJ34

BK32

BK33

BK34

BK35

BL33

AU30

R30

VCC_10

VCC_11

VCC_12

VCC_13

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC CORE

POWER

VCC SMVCC GFX

+1.05V

R20

VCC_AXG_1

T14

VCC_AXG_2

B B

A A

W13

W14

AA20

AA23

AA26

AA28

AB21

AB24

AB29

AC20

AC21

AC23

AC24

AC26

AC28

AC29

AD20

AD23

AD24

AD28

AF21

AF26

AA31

AH20

AH21

AH23

AH24

AH26

AD31

AJ20

AN14

Y12

VCC_AXG_3

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_7

VCC_AXG_8

VCC_AXG_9

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

VCC_AXG_27

VCC_AXG_28

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC_AXG_NCTF_55

VCC GFX NCTF

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

VCC_AXG_NCTF_61

VCC_AXG_NCTF_62

VCC_AXG_NCTF_63

VCC_AXG_NCTF_64

VCC_AXG_NCTF_65

VCC_AXG_NCTF_66

VCC_AXG_NCTF_67

VCC_AXG_NCTF_68

VCC_AXG_NCTF_69

VCC_AXG_NCTF_70

VCC_AXG_NCTF_71

VCC_AXG_NCTF_72

VCC_AXG_NCTF_73

VCC_AXG_NCTF_74

VCC_AXG_NCTF_75

VCC_AXG_NCTF_76

VCC_AXG_NCTF_77

VCC_AXG_NCTF_78

VCC_AXG_NCTF_79

VCC_AXG_NCTF_80

VCC_AXG_NCTF_81

VCC_AXG_NCTF_82

VCC_AXG_NCTF_83

VCC_SM_LF1

VCC_SM_LF2

VCC_SM_LF3

VCC_SM_LF4

VCC_SM_LF5

VCC_SM_LF6

VCC_SM_LF7

VCC SM LF

T17

T18

T19

T21

T22

T23

T25

U15

U16

U17

U19

U20

U21

U23

U26

V16

V17

V19

V20

V21

V23

V24

Y15

Y16

Y17

Y19

Y20

Y21

Y23

Y24

Y26

Y28

Y29

AA16

AA17

AB16

AB19

AC16

AC17

AC19

AD15

AD16

AD17

AF16

AF19

AH15

AH16

AH17

AH19

AJ16

AJ17

AJ19

AK16

AK19

AL16

AL17

AL19

AL20

AL21

AL23

AM15

AM16

AM19

AM20

AM21

AM23

AP15

AP16

AP17

AP19

AP20

AP21

AP23

AP24

AR20

AR21

AR23

AR24

AR26

V26

V28

V29

Y31

AW45

BC39

BE39

BD17

BD4

AW8

AT6

4

Layout Note:

370 mils from edge.

Ivcc_AXG Graphics core supply

current 7.7A

+

C109

330U/2V/ESR9

+

C95

*330U/2V/ESR9

C109 change to NC(PM)

Layout Note:

Inside GMCH cavity for VCC_AXG.

12

VCCSM_LF1

VCCSM_LF2

VCCSM_LF3

VCCSM_LF4

VCCSM_LF5

VCCSM_LF6

VCCSM_LF7

12

GMCH 1.05V

VCC Core

VCC_AXG

VCC_AXD

VTT

VCC_PEG

VCC_AXM

VCCR_RX_DMI

C276

0.1U/10V_4

12

C173

0.1U/10V_4

C222

0.1U/10V_4

current(A)

1.573

7.7

0.2

0.85

1.2

0.54

0.25

12.313SUM

12

C169

0.1U/10V_4

3

Ivcc (External GFX 1.310 A,

integrate 1.572 A)

+1.05V

+

C131

C660

330U/2V/ESR9

10U/6.3V_8

Layout Note:

370 mils from edge.

12

C318

1U/10V_4

Remark

12

C316

10U/6.3V_8

Ivcc_AXM

Controller

supply

current

540mA

+1.05V

12

C210

0.47U/10V_6

( 1.3A for

external

GFX )

for integrated

Gfx

FSB VCCP

for PCIEG

for IAMT

function

DMI

12

12

C213

0.47U/10V_6

12

C329

0.47U/10V_6

C139

0.47U/10V_6

+3V

R446 10

+VCC_GMCH_L

1 2

12

C312

10U/6.3V_8

Layout Note:

Inside GMCH cavity.

C328

10U/6.3V_8

10U/6.3V_8

12

C334

1U/10V_4

C322

0.22U/16V_6

C162

for IAMT power if not

10U/6.3V_8

support need to

connection to S0 power

12

C246

0.1U/10V_4

C201

C291

10U/6.3V_8

Layout Note:

Place close to GMCH edge.

12

C357

1U/10V_4

D9

CH501H-40PT L-F

12

C275

0.22U/16V_6

+1.05V

A test check

when use

external VGA can

remove or not..

andrew

12

C187

0.1U/10V_4

12

C247

0.22U/16V_6

1.8VSUS

2

30mA

21

12

C251

0.1U/10V_4

12

C229

0.1U/10V_4

12

C274

0.22U/16V_6

12

C311

0.1U/10V_4

Layout Note:

Place C901 where LVDS

and DDR2 taps.

AB33

AB36

AB37

AC33

AC35

AC36

AD35

AD36

AF33

AF36

AH33

AH35

AH36

AH37

AJ33

AJ35

AK33

AK35

AK36

AK37

AD33

AJ36

AM35

AL33

AL35

AA33

AA35

AA36

AP35

AP36

AR35

AR36

AL24

AL26

AL28

AM26

AM28

AM29

AM31

AM32

AM33

AP29

AP31

AP32

AP33

AL29

AL31

AL32

AR31

AR32

AR33

1

U24F

VCC_NCTF_1

VCC_NCTF_2

VCC_NCTF_3

VCC_NCTF_4

VCC_NCTF_5

VCC_NCTF_6

VCC_NCTF_7

VCC_NCTF_8

VCC_NCTF_9

VCC_NCTF_10

VCC_NCTF_11

VCC_NCTF_12

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

VCC_NCTF_32

Y32

VCC_NCTF_33

Y33

VCC_NCTF_34

Y35

VCC_NCTF_35

Y36