Page 1

Service Manual

ARCAM

CD62

Issue 1.0

DiVA CD62

Compact Disc Player (Text)

ARCAM

Page 2

Contents List

!

Contents list

!

Circuit description

!

Service guide

!

Circuit diagrams

!

Component overlays

!

Circuit board parts list

!

General assembly parts list

Page 3

CD62 (text) Circuit Description

Summary

The main Motherboard/Display PCBs for the Diva CD players

may be assembled as three different versions:

! DiVA CD62 (text) - With alternate components fitted

and the 92DAC upgrade connections omitted

(L933AY).

! DiVA CD72 (text) - With the standa rd s e t of

components fitted (L899AY).

! DiVA CD92 (text) - With analogue components and

connectors omitted, for use as a host motherboard for

the plug-in 92DAC (L934AY).

All systems are based on a Sony kit, comprising CDM14BL5BD25 CD transport / loader / laser mechanism, micro-controller

and fluorescent display.

Power Supplies

The CD62 may be fitted with any of the following transformers

dependant on supply voltage required:-

! 230VAC only - part number L849TX

! 115VAC only - part number L850TX

! 100VAC only - part number L851TX

Later models are fitted with L867TX which is a 230/115VAC

transformer.

The mains transformer has three secondary windings:

1. 13.7V – 0V – 13.7V to provide ±12V(A) supplies

(IC201 and IC205) for the audio output circuitry via

regulators IC201 and IC205.

2. 9V-0V-32V to produce the digital, motor drive and

fluorescent display grid supplies:

+11V(U) Unregulated supply for relay drive and

+5V(D) supply

+7V (IC200) Mechanism and motor driver

supply

+5V(D) (IC202) General digital logic supply

+5V(A) (IC203) Supply to DAC

-30V (IC204) Display grid voltage.

3. 0-5V to provide an AC supply for the display

filament.

Relay Mute Control

This circuit drives a relay to un-mute the analogue output ~5

seconds after the unit is powered on, and quickly mutes the

output when the unit is switched off. Th e cir cu it works

effectively as an “AND” gate.

If AC is present on the transformer secondary winding and the 5second timer composed of R222 and C221 has reached the

threshold voltage (Vbe of TR200 + Vbe of TR201 - Vce of

TR202, or ~1.0V), the relay coil is connected to +11V

(referenced to 0V_3 as required by the 9DAC’s internal circuitry)

via TR204.

When AC is removed, C231 discharges quickly through R225,

the base voltage of TR204 rises and the relay coil voltage is

removed, muting t he output.

TR203 resets the ‘timer’ by discharging C221 quickly at turn-off.

Remote Control/PIC Micro

Remote control data is received from the IREye on the display

PCB and buffered by TR300 and TR301. The Programmable

Interrupt Controller converts the RC-5 format data into the NEC

format required by the Sony micro.

Motor Driver

The status of the drawer is indicated to the micro by two micro

switches ‘INSW’ and ‘OUTSW’ on SK205. The micro controls

the drawer motor via driver IC303.

Clock Buffering

The clock and data signals LRCK, ADATA and BCLK from the

mechanism connector SK300 are double buffered by IC300

before being delivered to the DAC.

Power-On/Reset

The power-on reset signal XRST (or RESET) is generated by

R409, C410 and IC404. When the power is turned on, C410 is

initially uncharged and pin 11 of IC404 is at high voltage, and

thus the output is low. After a short time, C410 is charged via

R409; IC404 pin 11 is then low, and the output switches high

(RESET is de-asserted).

DAC & System Clock

The DAC is a Burr Brown PCM1716E, the DAC is configured

for hardware control.

Digital audio is input on pins 1, 2 & 3 in standard Red Book

Audio format, i.e . Word Clock, Bit Clock and Data.

The system clock is based around 16.9344 MHZ crystal X400

and transistor TR402. This produces a stable clock with low

jitter. IC404A & B buffer the clock as linear buffers. IC404C &

D buffer the individual mech & DAC clock lines.

Analogue Output

Left channel:

IC400A and IC400B are cascaded 69kHz 2

Bessel filters. The output devices internal to both op-amps in

IC400 are “pulled down” to the negative supply rail to force

operation in class A (one output device is conducting at all times

and crossover distortion is eliminated).

C448 AC-couples the output, the muting relay shorts the output

to ground through 120 ohm series resistors, and 3N3

Polypropylene shunt capacitors are used to swamp cable

capacitance, ensuring stability and making up the 5

filter.

The right channel is the same as the left channel. IC401A & B

are used as the buffer and filter.

nd

order low-pass

th

pole of the

Page 4

Microcontroller & Display Board

The system microcontroller IC100 serves the following functions:

! Control of the mechanism & decoder on the CDM14

mechanism

! Control of mute, attenuation and de-emphasis for the

DAC

! Direct drive of the fluorescent display

! Remote control decoding

! Keyboard scanning

The keyboard scanning works by connecting the keys to a resistor

ladder on an ADC input to the micro. Pressing a key presents a

unique voltage to this input, which the micro is pre-programmed

to interpret accordingly.

The remote control data contains a ‘Customer Code’ that

identifies this as an Arcam product. The diode network D100 to

D106 configures the micro to accept this code.

Remote Bus Carrier Filter & Demodulator

Remote control commands can be delivered over wire to SK500

for multi-room applications. Incoming signals are attenuated and

clipped by resistors and D500. L500 and C508 form a parallel

resonant circuit at approximately 37kHz. This demodulates the

incoming signal and the output is passed to IC501A where it is

‘chopped’, low pass filtered and fed to IC501B to provide the

RC5 outp ut signal.

Digital Output

The decoder on the mechanism assembly generates an SPDIF

format digital output signal. This is passed to buffer IC500A.

IC500B through E are used in parallel to provide a transformer

less 75-ohm source impedance to a single phono socket SK501.

Optical digital output via IC502 is also tapped off the digital

output signal via IC500F.

Page 5

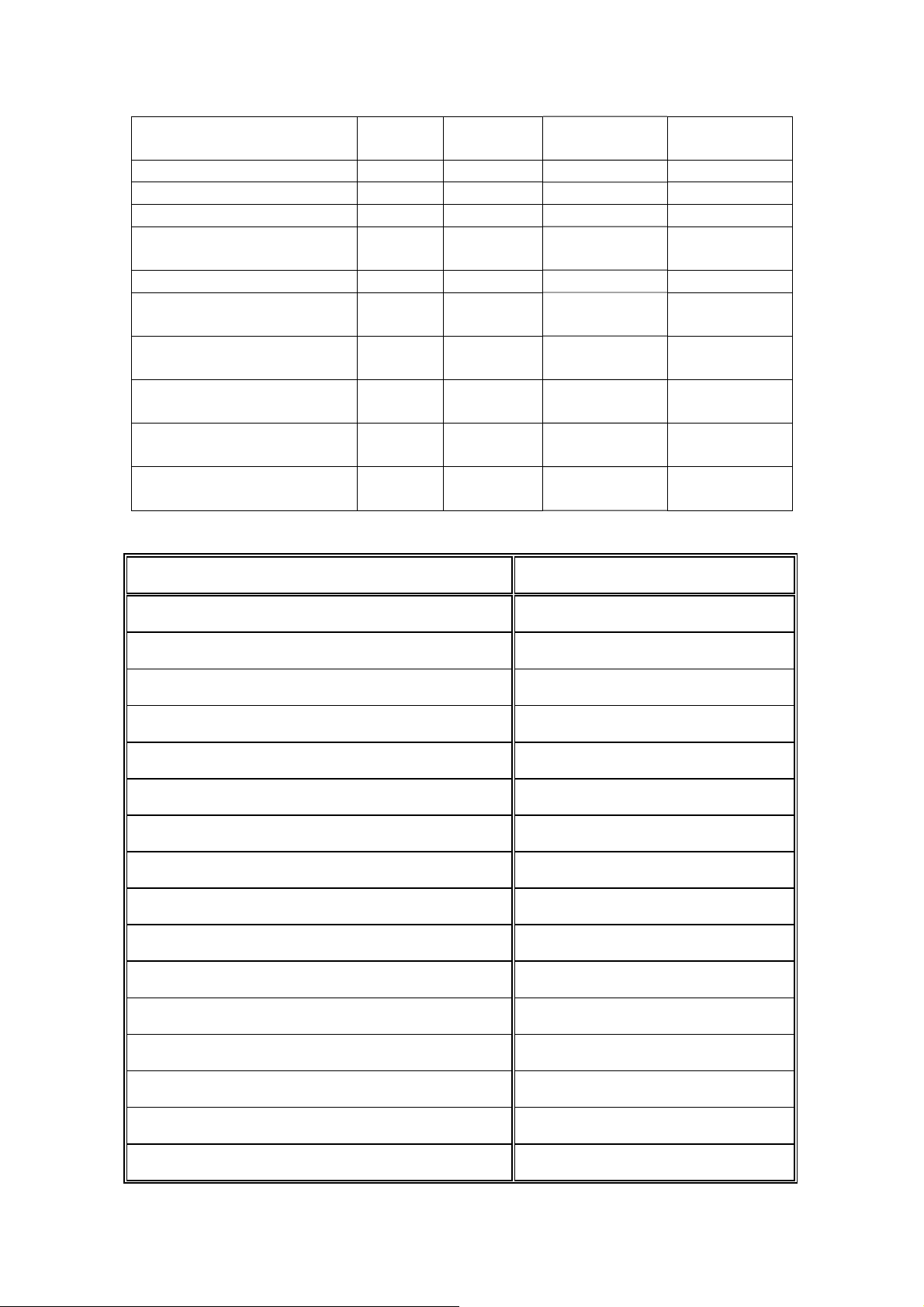

Jumper Settings / Technical Specifications

Jumper Description Jumper CD62T

Settings

Filter smoothing disable PL200 Not fitted Off On

Filter smoothing disable PL201 Not fitted Off On

IC201 Regulator bypass PL202 Not fitted Off On

IC201 Regulator output

enable

IC205 Regulator bypass PL204 Not fitted Off On

IC205 Regulator output

enable

System clock source

select

Main board clock power

enable

Main board PCM1716E

DAC enable

Main board output relay

enable

CD Mechanism

Laser pick-up

DAC conversion system

Effective resolution

Dynamic Range

Signal to Noise ratio (CCIR)

Harmonic distortion (0dBFS 1kHz)

Harmonic distortion (0dBFS 10kHz)

Frequency response (-0.7dB)

Output level (0dBFS)

Output impedance

Minimum recommended load

Coaxial digital output (75 ohm)

Power consumption (max)

Size W/D/H (mm)

Weight, net

PL203 On On Off

PL205 On On Off

PL300 Pin1 & 2 Pins 1 & 2 Pins 2 & 3

PL400 On On Off

PL401 On On Off

PL402 On On Off

CD72T

Settings

CD62T / CD72T

Sony CDM14BL-5BD25

3 beam

Multi-level Delta Sigma

16 bits (24 bit capable DAC)

100dB

>104dB

<0.005%

<0.005%

< 10Hz to 20kHz

2.3VRMS

120 ohms

Class 2

430x290x84

4.6kg (CD92T 5.6kg)

CD92T

Settings

5 kΩ

32VA

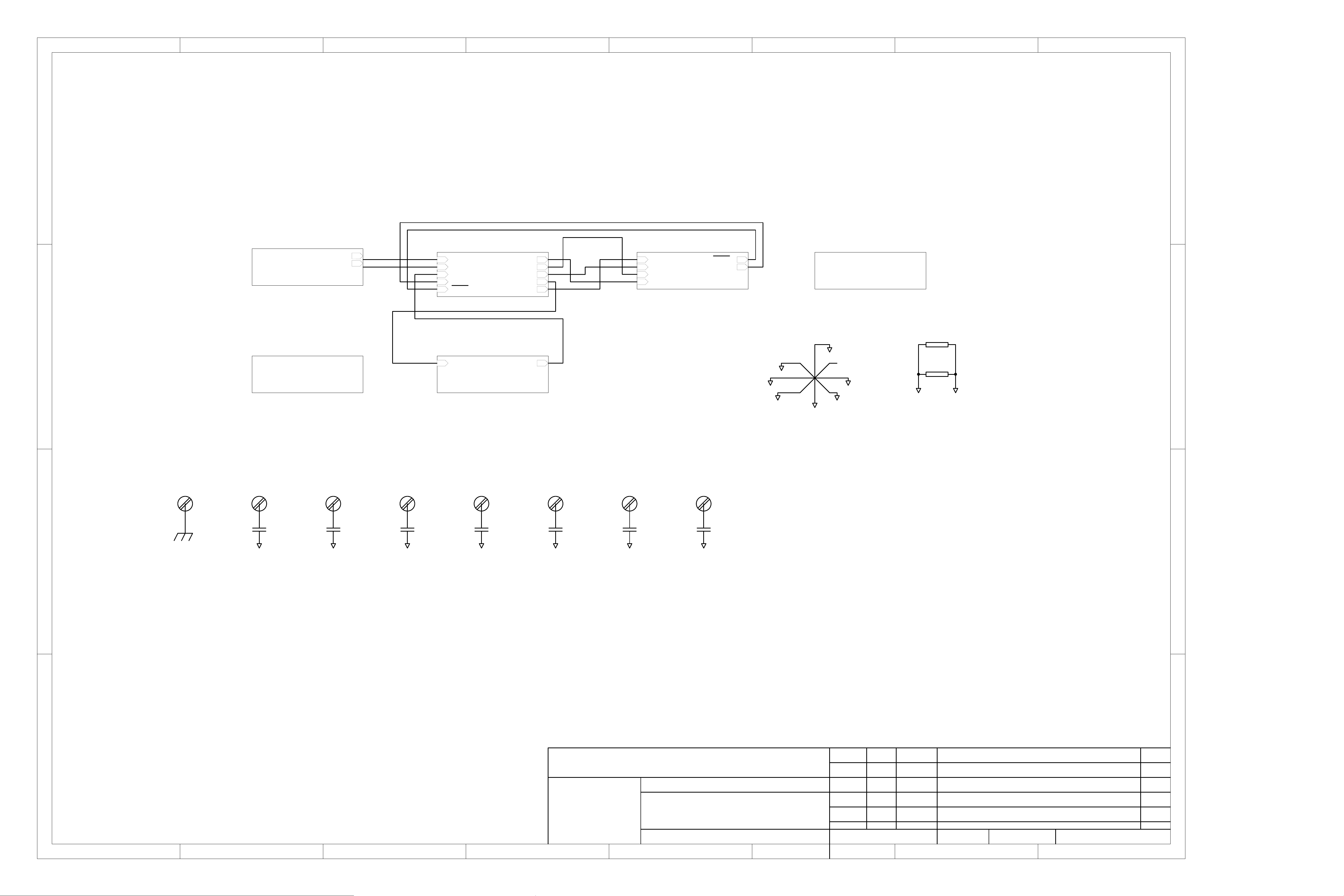

Page 6

87654321

D

POWER SUPPLIES

L933C2_1

L933C2_2.1.sch

FILA

FILB

Please refer to the CD72T (Master) schematic if changes are to be made to this schematic!

USE EXCLUDE NF WHEN CREATING BILL OF MATERIALS

MECH INTERCONNECTS DAC AND OSCILLATOR

L933C3_1

L933C3_2.1.sch

FILA

FILB

17MHZ

RESET

BCLK

ADATA

LRCKRC5 IP

DIGOP

EMPHASIS

L933C4_1

L933C4_2.1.sch

DEEM

LRCK

ADATA

BCLK

RESET

17MHZ

DISPLAY AND MICROCONTROLLER

L933C7_1

L933C7_2.1.sch

D

C

FIX152

FIXING HOLE 3.5

DISPLAY PCB

L933C1_1

L933C1_2.1.sch

FIX157

FIXING HOLE 3.2

FIX151

FIXING HOLE 3.2

RC5 INPUT AND DIG OUTPUTS

L933C5_1

L933C5_2.1.sch

FIX153

FIXING HOLE 3.5

DIGOP RC5RP

FIX154

FIXING HOLE 3.5

FIX155

FIXING HOLE 3.5

FIX156

FIXING HOLE 3.5

FIX150

FIXING HOLE 3.5

0V_DIG

0V_MOT

0V_SIG

0V_30V_9DAC

0V_2

SP100

STARPOINT

0V_1

LK600

0R0 MF

LK601

0R0 MF

0V_DIG 0V_9DAC

C

B

(EARTH BY IEC SOCKET)

C150

1N0 CD C151

NF

0V_DIG 0V_DIG 0V_DIG 0V_DIG 0V_DIG 0V_DIG 0V_DIG

1N0 CD

C152

1N0 CD

C153

1N0 CD

C154

1N0 CD

C155

1N0 CD

C156

1N0 CD

B

A

DRAWING TITLE

CD62T - TOP LEVEL SCHEMATIC

Circuit Diagram

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

Cambridge CB5 9PB

1 2 3 4 5 6 7 8

Notes:

01_1127 TGP 18 July 2001

ECO No. DESCRIPTION OF CHANGE

Filename

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933_2.1.prj

Date Printed

INITIALS

19-Jul-2001

DATE

Drawn by:

TGP

Production Release

6 7Sheet of

DRAWING NO.

A

2.1

ISSUE

L933CT

Page 7

D

SK200

IEC3

N E L

N

C200

E

C201

3N3(X1Y2)

R202

NEUTRAL LIVE

1M5 VR25

C203

220N(X2)

L200

6U8H

NEUTRAL2

CA1

L920CA

3

2

SK202

6

5

L920CA

L

3N3(X1Y2)

L201

6U8H

EL200

EARTH LEAD

EARTH LEAD

(IEC INLET TO CHASSIS)

LIVE2

BRN BRN

BLU

BLU

8M101

C202

3N3(X1Y2)

FS200

T250MA115V

115V ONLY

NEUTRAL2

SW200A

A1010

SW200B

A1010

115V

115V

10

1

2

7

6

4

5

TX200

L849TX

16

17

18

11

13

TX_16

TX_18

C206

100N CD

R200

1R0 FU

R201

1R0 FU

AC1

AC2

SK201

MOLEXPWR4

(FOR AUX TOROID)

1

3

C204

100N CD

C205

100N CD

+11V(U)

BR200

DF01M

2

4

+

NF

C210

3M3 EL

7654321

8

PL202

2WVERTJUMPER

1

+12V(A)

PL203

2WVERTJUMPER

+

C223

1M0 25V

D

BR201

DF01M

PL200

2WVERTJUMPER

NF

JP200

JUMPER

NF

1

2

R204

+

10R MF

C211

1M0 35V

Analogue op-amp supplies

D202

1N4148

LM317T

I

IC201

Vin

ADJ

A

+

C213

Vout

C216

100U EL

JP202

JUMPER

NF

O

1

2

R206

220R MF

R208

1K8 MF

NF

JP203

JUMPER

D203

1N4148

2

100N PE

D200

O

R209

1K8 MF

R207

220R MF

JP204

JUMPER

NF

1

2

D204

1N4148

JP205

JUMPER

0V_1

+

C224

1M0 25V

1

2

2WVERTJUMPER

PL205

+

C217

1N4148

IC200

LM1086-ADJ

I

Vin

Vout

ADJ

HS201

TO220HS30REG

O

R203

330R MF

D201

1N4148

+7V

Motor drive supply

R205

10R MF

1

2

JP201

+

C212

1M0 35V

JUMPER

A

+

C218

100U EL

R214

1K6 MF

+

C228

1M0 10V

PL201

2WVERTJUMPER

NFNF

I

C214

100N PE

Vin

LM337T

IC205

100U EL

A

ADJ

Vout

D207

1N4148

1

MOLEXPWR6

(FOR AUX TOROID)

NF

4

FS201

T160MA

230V

230V

9

15

AC_3

230V ONLY

19

TX_19

C

20

TX_20

NB: CABLE ASSEMBLY L920CA GOES BETWEEN

BRN BRN AND BLU BLU FROM MAINS SWITCH TO BACK OF PCB

FILA

FILB

R210

R211

10R FU

1R0 FU

R212

1R0 FU

C207

100N CD

C208

100N CD

D213

1N4003

+

C225

100U EL 100V

R227

100R MF

R228

100R MF

I

Vin

IC204

+

C226

100U EL 100V

A

ADJ

LM337T

Vout

D205

1N4148

O

R215

22K MF

R216

1K0 MF

+

-30VF

C227

100U EL 100V

Filiament supply

R217

33K MF

0V_2

D214

5V1 400MW

+11V(U)

I

C209

100N CD

IC202

Vin

D206

1N4148

LM317T

HS

A

Vout

ADJ

+

C219

100U EL

PL204

2WVERTJUMPER

NF

HS200

TO220HS08REG

O

R218

270R MF

R220

820R MF

D208

1N4148

-12V(A)

+5V(D)

+

0V_2

C

Digital +5V

C220

100U EL

B

AC1

AC2

D209

1N4148

D210

1N4148

R213

10R FU

100U EL

C230

D211

1N4148

LM317T

ADJ

A

+

C222

100U EL

Vout

O

HS202

TO220HS30REG

R219

270R MF

R221

820R MF

D212

1N4148

+5V(A)

+

0V_1

DAC supply

C229

1M0 10V

B

R222

470K MF

100U EL

C221

IC203

Relay control for AC detect

+12V(A)

SK203

23

I

Vin

22

21

20

19

18

17

16

15

14

13

12

C215

100N PE

TR200

BC549B

R226

10K MF

R229

1K5 MF

TR204

BC557B

-12V(A)

+5V(A)

D215

1N4148

+5V(D)

11

+

TR201

BC549B

R230

RLYPWR

10K MF

10

9

8

7

0V_3

+11V(U)

6

5

4

3

R224

10K MF

+

C231

+

10U EL

R223

10K MF

R225

2K2 MF

BC549B TR203

BC549B

TR202

2

1

FFC23V

Power connector for 9DAC PCB

NF

0V_9DAC

A

0V_3

0V_3

DRAWING TITLE

CD62T - POWER SUPPLIES

Circuit Diagram

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

1 2 3 4 5 6 7 8

Cambridge CB5 9PB

Notes:

ECO No. DESCRIPTION OF CHANGE

Filename

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C2_2.1.sch

Date Printed

INITIALS

19-Jul-2001

DATE

Drawn by:

TGP

Production Release01_1127

2 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001

ISSUE

L933CT

Page 8

Data connector to DAC PCB

SK301

FFC32V

NF

Flexfoil connector to Display PCB

SK302

FFC32V

7654321

8

D

+5V(D)

C300

100N CD

0V_DIG

+5V(D)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

14

R301

IC300G

74HCU04

7

C301

100N CD

BCLK

IC300A

1 2

74HCU04

IC300B

3 4

74HCU04

330R MF

R300

330R MF

NF

R302

330R MF

BCLK

ADATA

XRST

AMUTE

DEEM

RA0

RB6

RB5

RB4

RB0

HDCD

0V_9DAC

32

FILA

30

31

SCOR

0V_DIG

29

28

27

25

26

RMIN

LDOUT

24

LDIN

22

23

SENS

21

XLT

18

19

20

AMUTE

17

16

15

13

14

CLK

LDON

12

DATA

1

2

3

4

5

6

7

8

10

11

SQCK

SUBQ

9

LOADSW

XRST

-30VF

HDCD

LPH

DEEM

IREYE

FILB

R315

10K MF

0V_DIG

EMPHASIS

D

C

DIGOP

Flex connector from CDM14BL-5BD25 mech

SK300

FFC23V

23

CLK

22

XRST

21

DATA

20

LDON

19

SENS

18

XLT

+5V(D)

0V_DIG

+7V

0V_DIG

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

SUBQ

SQCK

AMUTE

BCLK

SCOR

ADATA

LRCK

LPH

PL300

3WVERTJUMPER

(Master clock select jumper)

ADATA

LRCK

1

2

JP300

3

JUMPER

IC300C

5 6

74HCU04

IC300E

74HCU04

17MHZ

(From crystal oscillator)

(From 9 DAC PCB)

IC300D

89

74HCU04

IC300F

1011

74HCU04

1213

R304

330R MF

NF

R305

330R MF

R306

330R MF

NF

LRCK

C

B

IREYE

R314

10K MF

0V_DIG

RC5 IP

R307

10K MF

R310

10K MF

R308

10K MF

TR300

BC549B

+5V(D)

R309

10K MF

TR301

BC549B

D300

1N4148

C304

100P CD

0V_DIG

+5V(D)

RA0

AMUTE

DEEM

RMIN

XRST

RESET

+5V(D)

R311

100K MF

R313

100K MF

17

18

IC302

PIC16C54XT

RA0

1

2

3

4

RA1

RA2

RA3

RTCC

MCLR

16

OSC1

X300

CST4.00

0V_DIG

OSC2

15

VSS

5

RB0

RB1

RB2

RB3

RB4

RB5

RB6

RB7

14

6

7

8

9

10

11

12

13

VDD

C302

100N CD

+5V(D)

+

RB0

RB4

RB5

RB6

C305

100U EL

Motor Drive

IC303

LB1641

O/P 'Out'

Vcc

Vcc

LoadOut

LoadIn

Bias

O/P 'In'

GND

10

9

8

7

6

LDOUT

5

LDIN

D301

4

4V7 400MW

3

2

1

C303

100N CD

0V_MOT

+7V

+

C306

100U EL

C307

10N CD

C308

100N CD

0V_MOT

+5V(D)

R303

6K8 MF

LOADSW

R312

6K8 MF

SK303

8K2005

1

2

3

4

5

LOADOUT

LOADIN

GND

INSW

OUTSW

B

A

0V_DIG

DRAWING TITLE

CD62T - MECH CONNECTS, MOTOR DRIVE AND IR MICRO

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

Cambridge CB5 9PB

Filename

1 2 3 4 5 6 7 8

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C3_2.1.sch

Notes:

Circuit Diagram

ECO No. DESCRIPTION OF CHANGE

INITIALS

DATE

Date Printed

19-Jul-2001

Drawn by:

TGP

3 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001 Production Release01_1127

ISSUE

L933CT

Page 9

D

C

C411

47N CD

LRCK

ADATA

BCLK

+5V(DAC)

+

C428

10U EL

0V_DIG

L401

7F003

+5V(A)

C429

10U EL

JP401

JUMPER

PL401

2WVERTJUMPER

1

2

(DAC enable jumper)

+5V(DAC)

C401

47N CD

C433

10U EL

C408

47N CD

0V_SIG

+

C415

47N CD

NF

0V_SIG

+5V(DAC)

DACLK

0V_DIG

+

C435

47N CD

NF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

R402

4K7 MF

LRCIN

DIN

BCKIN

CLKO

XTI

XTO

DGND

Vdd

Vcc2R

AGND2R

EXT1R

NC

VOUTR

AGND1

IC403

PCM1716#

C402

100N PE

C403

100N PE

ML/IIS

MC/DM1

MD/DM0

MUTE

MODE

CS/IWO

Vcc2L

AGND2L

VOUTL

RST

ZERO

EXTL

NC

Vcc

84

0V_SIG

IC400C

NJM2114

28

27

26

25

24

23

22

21

20

19

18

17

16

15

R412

4K7 MF

+5V(DAC)

0V_DIG

C442

47N CD

NF

C443

47N CD

NF

C409

47N CD

C404

100N PE

NF

C405

100N PE

NF

DEEM

R431

10K MF

+5V(DAC)

0V_SIG

0V_SIG

0V_SIG

C430

+

10U EL

+

C432

10U EL

+

C431

10U EL

7654321

8

+12V(A)

84

C406

IC401C

NJM2114

100N PE

C407

100N PE

0V_SIG

84

-12V(A)

IC402C

TL072

NF

R413

4K7 MF

R410

6K8 MF

C416

560P PP

0V_SIG

R415

2K7 MF

2

3

C418

220P PP

IC400A

NJM2114

R416

1

2K7 MF

R435

680R MF

C422

1N3 PP

R419

3K9 MF

R403

1K8 MF

C445

100N PE

NF

R442

2K2 MF

0V_SIG

Output filter

C420

220P PP

6

5

IC400B

NJM2114

R437

100K MF

NF

-12V(A)

R433

1K0 MF

EMC Shield

LK400

LINK10PAD

NF

C448

7

R421

C424

470N PE

NF

1M0 MF

+

10u CERA

NF

2

R405

120R MF

R423

22K MF

1

SH400

EMCPHONO

RLY400A

DPDT

0V_SIG

EMC1

D

C426

3N3 PP

0V_SIG

3

D402

1N4148

L404

7F003

+5V(DAC)

C444

47N CD

R414

4K7 MF

R411

6K8 MF

C417

560P PP

0V_SIG

R417

2K7 MF

2

3

C419

220P PP

IC401A

NJM2114

-12V(A)

1

R436

680R MF

R418

2K7 MF

C423

1N3 PP

R420

3K9 MF

R404

1K8 MF

C450

100N PE

NF

R443

2K2 MF

0V_SIG

Output filter

C421

220P PP

6

5

IC401B

NJM2114

R438

100K MF

NF

IC402A

TL072

NF

7

7

R422

C425

470N PE

NF

1M0 MF

-12V(A)

R434

1K0 MF

NF

6

0V_SIG

LK401

LINK10PAD

NF

C449

+

10u CERA

EMC1

R406

120R MF

R424

22K MF

0V_SIG

SK400

PHONO2HG

EMC

0V_SIG

C434

100N CD

0V_SIG

RLY400B

DPDT

1

C427

3N3 PP

C

0V_SIG

5

IC402B

TL072

-12V(A)

NF

0V_SIG

RLYPWR

B

JP400

JUMPER

C400

100N CD

+5V(D)

1

2

PL400

2WVERTJUMPER

(Oscillator enable jumper)

L400

7F003

JP402

JUMPER

PL402

2WVERTJUMPER

+5V(D)

1

2

14

R439

IC404G

74HCU04

C414

100N CD

7

D400

1N4148

+

R409

10K MF

0V_DIG

C410

100U EL

R432

10K MF

1M0 MF

IC404E

74HCU04

1011

IC404F

74HCU04

1213

RESET

RLY400C

DPDT

0V_3

D401

1N4148

B

L402

7F003

C413

100N CD

C436

+

10U EL

C437

10N CD

X400

16.9344MHZ

C441

33P CD

R427

33K MF

R426

33K MF

TR402

BC547B

C438

100P CD

C439

100P CD

C440

1N0 CD

R430

1K0 MF

L403

33UH AX

0V_DIG

C412

10N CD

R428

330R MF

R429

4M7 MF

1 2

IC404A

74HCU04

R400

330R MF

R425

1M0 MF

3 4

IC404B

74HCU04

R401

330R MF

IC404D

74HCU04

5 6

IC404C

74HCU04

R407

89

120R MF

R408

120R MF

C446

10P CD

0V_DIG

C447

10P CD

0V_DIG

DACLK

17MHZ

(Master clock to DAC)

(Master clock to mech)

A

0V_DIG

DRAWING TITLE

CD62T - DAC, OSCILLATOR AND ANALOGUE OUTPUTS

Circuit Diagram

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

1 2 3 4 5 6 7 8

Cambridge CB5 9PB

Notes:

ECO No. DESCRIPTION OF CHANGE

Filename

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C4_2.1.sch

Date Printed

INITIALS

19-Jul-2001

DATE

Drawn by:

TGP

4 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001 Production Release01_1127

ISSUE

L933CT

Page 10

CARRIER FILTER AND DEMODULATOR

NF

+5V(D)

7654321

8

D

SK500

JACK3.5

NF

C509

100N CD

NF

EMC1

C513

100P CD

NF

R511

470R MF

NF

R504

1K0 MF

NF

R512

100K MF

NF

D500

4V7 400MW

NF

RC5RP

R507

10K MF

NF

L500

27mH

NF

7

IC501B

LM393A

NF

C508

680P PP

NF

C510

100P CD

NF

5

6

R508

10K MF

NF

R502

1K8 MF

NF

R514

1K5 MF

NF

R503

1K8 MF

NF

2

3

IC501A

LM393A

NF

C507

100N CD

NF

R510

10K MF

NF

1

R509

10K MF

NF

R513

100K MF

NF

C503

1N0 CD

NF

D

84

IC501C

LM393A

NF

C500

100N CD

NF

C

0V_DIG

+5V(D)

R500

10R MF

C502

470N PE

0V_DIG

14

IC500G

74HCU04

7

IC500F

74HCU04

IC500E

74HCU04

C

+5V(D)

R501

10R MF

OPTICAL OUTPUT

2

1213

1011

89

R505

120R MF

R506

1K2 MF

R516

1

GP1FA550TZ

IC502

I/P

VCC

GND

3

C501

10N CD

0V_DIG

+

C506

10U EL

B

DIGOP

1 2

IC500A

74HCU04

IC500D

74HCU04

5 6

IC500C

74HCU04

3 4

IC500B

74HCU04

1K2 MF

R517

1K2 MF

R518

1K2 MF

R519

100R MF

C512

470P CD

C505

100N CD

R515

10K MF

C511

SK501

B

PHONO1

EMC

COAXIAL OUTPUT

C504

10N CD

LK500

LINK10NP

A

100N CD

0V_DIG

DRAWING TITLE

CD62T - REAR PANEL RC5 & DIGITAL OUTPUT

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

Cambridge CB5 9PB

Filename

1 2 3 4 5 6 7 8

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C5_2.1.sch

Notes:

Circuit Diagram

ECO No. DESCRIPTION OF CHANGE

INITIALS

DATE

Date Printed

19-Jul-2001

Drawn by:

TGP

5 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001 Production Release01_1127

ISSUE

L933CT

Page 11

7654321

8

D

LK701

LINK10NP

LK702

LINK10NP

LK703

LINK10NP

LK704

LINK10NP

LK705

LINK10NP

LK706

LK711

LINK10NP

LK712

LINK10NP

LK713

LINK10NP

LK714

LINK10NP

LK715

LINK10NP

LK716

LK721

LINK10NP

LK722

LINK10NP

LK723

LINK10NP

LK724

LINK10NP

LK725

LINK10NP

LK726

LK731

LINK10NP

LK732

LINK10NP

LK733

LINK10NP

LK734

LINK10NP

LK735

LINK10NP

LK736

LK741

LINK10NP

LK742

LINK10NP

LK743

LINK10NP

LK744

LINK10NP

LK745

LINK10NP

LK746

LK751

LINK10NP

LK752

LINK10NP

LK753

LINK10NP

LK754

LINK10NP

LK755

LINK10NP

LK756

LK761

LINK10NP

LK762

LINK10NP

LK763

LINK10NP

LK764

LINK10NP

LK765

LINK10NP

LK766

NF

NF NF

LK771

LINK10NP

LK772

LINK10NP

LK773

LINK10NP

LK774

LINK10NP

LK775

LINK10NP

LK776

LK781

LINK10NP

LK782

LINK10NP

LK783

LINK10NP

LK784

LINK10NP

LK785

LINK10NP

LK786

LK791

LINK10NP

LK792

LINK10NP

LK793

LINK10NP

LK794

LINK10NP

LK795

LINK10NP

LK796

NF

LK801

LINK10NP

LK802

LINK10NP

LK803

LINK10NP

LK804

LINK10NP

LK805

LINK10NP

LK806

NF

LK811

LINK10NP

LK812

LINK10NP

LK813

LINK10NP

LK814

LINK10NP

LK815

LINK10NP

LK816

NF

D

C

LINK10NP

LK707

LINK10NP

LK708

LINK10NP

LK709

LINK10NP

LK710

LINK10NP

LINK10NP

LK717

LINK10NP

LK718

LINK10NP

LK719

LINK10NP

LK720

LINK10NP

LINK10NP

LK727

LINK10NP

LK728

LINK10NP

LK729

LINK10NP

LK730

LINK10NP

NF

NF

LINK10NP

LK737

LINK10NP

LK738

LINK10NP

LK739

LINK10NP

LK740

LINK10NP

LINK10NP

LK747

LINK10NP

LK748

LINK10NP

LK749

LINK10NP

LK750

LINK10NP

LINK10NP

LK757

LINK10NP

LK758

LINK10NP

LK759

LINK10NP

LK760

LINK10NP

LINK10NP

LK767

LINK10NP

LK768

LINK10NP

LK769

LINK10NP

LK770

LINK10NP

LINK10NP

LK777

LINK10NP

LK778

LINK10NP

LK779

LINK10NP

LK780

LINK10NP

LINK10NP

LK787

LINK10NP

LK788

LINK10NP

LK789

LINK10NP

LK790

LINK10NP

LINK10NP

LK797

LINK10NP

LK798

LINK10NP

LK799

LINK10NP

LK800

LINK10NP

LINK10NP

LK807

LINK10NP

LK808

LINK10NP

LK809

LINK10NP

LK810

LINK10NP

NFNF

LINK10NP

LK817

LINK10NP

LK818

LINK10NP

LK819

LINK10NP

C

B

LK100

LINK10NP

LK101

LINK10NP

LK102

LINK10NP

LK103

LINK10NP

LK104

LINK10NP

LK105

LINK10NP

EL1

Update Box

LK106

LINK10NP

LK107

LINK10NP

LK108

LINK10NP

PB

LK109

LINK10NP

LK110

LINK10NP

LK111

LINK10NP

PCB

LK112

LINK10NP

LK113

LINK10NP

LK114

LINK10NP

IC302SW

LK115

LINK10NP

LK116

LINK10NP

LK117

LINK10NP

S/W

LK118

LINK10NP

LK119

LINK10NP

LK120

LINK10NP

LK121

LINK10NP

LK122

LINK10NP

LK123

LINK10NP

LK124

LINK10NP

LK125

LINK10NP

LK126

LINK10NP

LK127

LINK10NP

LK128

LINK10NP

LK129

LINK10NP

LK130

LINK10NP

LK131

LINK10NP

LK132

LINK10NP

LK133

LINK10NP

LK134

LINK10NP

LK135

LINK10NP

LK136

LINK10NP

B

A

UPDATE_BOX

L899PB

L825SW

DRAWING TITLE

CD62T - LINKS AND MECH PARTS

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

Cambridge CB5 9PB

Filename

1 2 3 4 5 6 7 8

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C7_2.1.sch

Notes:

Circuit Diagram

ECO No. DESCRIPTION OF CHANGE

INITIALS

DATE

Date Printed

19-Jul-2001

Drawn by:

TGP

7 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001 Production Release01_1127

ISSUE

L933CT

Page 12

(NEAR SK100)

FIX100

FIXING HOLE 3.2

CHASSIS

D

FIX102

FIXING HOLE 3.5

CHASSIS2

C100

1N0 CD

FIX101

FIXING HOLE 3.2

C101

1N0 CD

0V

FIX103

FIXING HOLE 3.5

C102

1N0 CD

+5V

100U 25V ZA EL

(NEAR SK100)

+

C103

DECOUPLING CAPACITORS FOR IC100

C104

100N CD

C105

100N CD

C106

100N CD

R100

220R MF

LED100

LED GREEN3.1MM

POWER LED

D100

1N4148

D101

REMOTE CUSTOM CODE DIODE MATRIX

D102

1N4148

D103

1N4148

D105

1N4148

7654321

DISP100

DISPLAY 14-ST-20GK

F11F1214G413G512G611G710G89G98G107G116G125G134G143G152G161G17NC18P119P220P321P422P523P624P725P826P927P1028P1129P1230P1331P1432P1533P1634P1735P1836P1937P2038P2139F241F2

8

D

42

F2F1

C

B

0V 0V

SP104

IR RX SUPPORT PAD

SP103

RX100

SBX1610-52/PIC-26043TM2

IR RX

SUPPORT PAD

Connector to main PCB

0V

3

2

IR_DISP

SK100

FFC32H

32

O/P

O/P

Case

F1

Case

31

30

SCOR_DISP

29

28

27

26

RMIN_DISP

25

LDOUT_DISP

24

LDIN_DISP

23

SENS_DISP

22

21

XLT_DISP

20

AMUTE_DISP

19

18

17

16

15

14

CLK_DISP

13

LDON_DISP

12

DATA_DISP

11

SQCK_DISP

10

SUBQ_DISP

9

LOADSW_DISP

8

XRST_DISP

7

6

5

DEEM_DISP

4

HDCD_DISP

3

LPH_DISP

2

F2

1

IR_DISP

PIN 1 TO LEFT

CABLE POINTING DOWN

-30V

+5V

GND +5V

C107

100N CD

GND

1

0V

C108

100N CD

+5V

-30V

D104

1N4148

CMO2

CMO1

+5V

0V

+

C110

10U EL

SP102

LED

SPACER

SPACER F195

HDCD LED

LED101

LED ULTRARED

NF

0V

1N4148

CMO4

D106

1N4148

CMO3

0V

C109

100N CD

0V

R101

10K MF

SW100 SW101 SW102 SW103 SW104 SW105 SW106 SW107

R103

6K8 MF

R108

3K3 MF

R109

2K2 MF

R110

1K5 MF

R111

1K0 MF

R112

680R MF

R114

R115

R116

R117

+5V

10K MF

10K MF

10K MF

10K MF

R104

6K8 MF

C129

0V

R105

6K8 MF

R106

6K8 MF

R107

6K8 MF

R102

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

+5V

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

S3

S2

1

2

3

4

5

6

7

8

9

13G

14G

NC

CMI1

SCOR

CMI2

CMI3

RMIN

CMI4

12G

VDD

S1

1G

2G

3G

4G

5G

6G

7G

8G

9G

10G

11G

S484S583S682S7

NC

NC

LDOUT

LDIN

SENS

XLT

AMUTE

PGML

NC

NC

TIMER

NC

CLK

LDON

DATA

SQCK

SUBQ

NC

AVREF

KEY0

KEY1

KEY231KEY332ADJ/AFADJ

LOADSW

33

34NC35NC36

AVSS37RST38EXTAL

39

XTAL

VSS41NC42NC43VDD44VDP45NC

40

0V

+5V

NC47LPH48NC49NC

46

-30V

81

S8

S9

S10

S11

S12

S13

S14

S15

S16

S17

S18

S19

S20

S21

NC

NC

NC

NC

NC

NC

NC

NC

EMPHASIS

CMO4

CMO3

CMO2

CMO1

NC

NC

NC

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

IC100

CXP82832

CMO4

CMO3

CMO2

CMO1

C

B

A

70mm x 12mm

DOUBLE SIDED

STICKY GASKET

70X12_DS STICKY TAPE

E1

CDTXT VFD SUPPORT

E916MC

1

2

3

4

0V

1 2 3 4 5 6 7 8

0V

R113

10R MF

NEXT PREV FF FR PAUSE STOP PLAY OPEN

DRAWING TITLE

CD62T - DISPLAY AND SYSTEM MICRO

23425

A & R Cambridge Ltd.

Pembroke Avenue

Denny Industrial Centre

Waterbeach

Cambridge CB5 9PB

Filename

J:\Change_Control\ECO_AGENDA\01_1127 CD62T RLEASE\Motherboard\l933ct_2.1.ddb - L933C1_2.1.sch

Notes:

10N CD

10K MF

Circuit Diagram

X100

CST8.00

0V

ECO No. DESCRIPTION OF CHANGE

INITIALS

DATE

Date Printed

19-Jul-2001

Drawn by:

TGP

1 7Sheet of

DRAWING NO.

A

2.1TGP 18 July 2001 Production Release01_1127

ISSUE

L933CT

Page 13

CAM Products 2000(TM): L899PB_2.GTO

Page 14

CD62 Main Board L933_2.1

Reference Description Part

number

BR200 Bridge rectifier DF01M 1A

100V

BR201 Bridge rectifier DF01M 1A

100V

C100-102 CERD 1N0 63V 20% RA 2A210

C103-109 ELST 100U 25V ZA

RUBYCON

C110 ELST 10U 50V 2N610

C129 CERD 10N 63V 20% RA 2A310

C151-156 CERD 1N0 63V 20% RA 2A210

C200-202 SUPPR CAP 3N3 250V 2K233

C203 220NF CLASS X2 CAP

275VRMS

C204-209 CERD 100N 63V 20% RA 2A410

C210 ELST 3M3 25V 2N833

C211 ELST 1M0 35V 2N810C

C212 ELST 1M0 35V 2N810C

C213-215 PEST 100N 63V 10% 2K410

C216-222 ELST 100U 25V 2N710

C223 ELST 1M0 25V 2N810

C224 ELST 1M0 25V 2N810

C225-227 ELST 100U 100V 2N710B

C228 ELST 1M0 10V 2N810

C229 ELST 1M0 10V 2N810

C230 ELST 100U 25V 2N710

C231 ELST 10U 50V 2N610

C300-303 CERD 100N 63V 20% RA 2A410

C304 CERD 100P 50V -20% +80%

RA

C305 ELST 100U 25V 2N710

C306 ELST 100U 25V 2N710

C307 CERD 10N 63V 20% RA 2A310

C308 CERD 100N 63V 20% RA 2A410

C400 CERD 100N 63V 20% RA 2A410

C401 CERD 47N 63V -20% +80% RA 2A347

C402, 403 PEST 100N 63V 10% 2K410

C406, 407 PEST 100N 63V 10% 2K410

C408 CERD 47N 63V -20% +80% RA 2A347

C409 CERD 47N 63V -20% +80% RA 2A347

C410 ELST 100U 25V 2N710

C411 CERD 47N 63V -20% +80% RA 2A347

C412 CERD 10N 63V 20% RA 2A310

C413 CERD 100N 63V 20% RA 2A410

C414 CERD 100N 63V 20% RA 2A410

C416 PPRO 560P 5% 63V RA 2D156

C417 PPRO 560P 5% 63V RA 2D156

C418-421 PPRO 220P 5% 63V RA 2D122

C419-421 PPRO 220P 5% 63V RA 2D122

C422 PPRO 1N3 63V 5% RA 2D213

C423 PPRO 1N3 63V 5% RA 2D213

C426 PPRO 3N3 5% 63V RA 2D233

C427 PPRO 3N3 5% 63V RA 2D233

C428-433 ELST 10U 50V 2N610

C434 CERD 100N 63V 20% RA 2A410

C436 ELST 10U 50V 2N610

3BDF0

1M

3BDF0

1M

2P710Z

A

2D422

A

A

2A110

N

N

Reference Description Part

number

C437 CERD 10N 63V 20% RA 2A310

C438 CERD 100P 50V -20% +80%

RA

C439 CERD 100P 50V -20% +80%

RA

C440 CERD 1N0 63V 20% RA 2A210

C441 CERD 33P 63V 20% RA 2A033

C444 CERD 47N 63V -20% +80% RA 2A347

C446 CERD 10P 63V 20% RA 2A010

C447 CERD 10P 63V 20% RA 2A010

C448 ELEC 10U 50V CERAFINE 2P610C

C449 ELEC 10U 50V CERAFINE 2P610C

C501 CERD 10N 63V 20% RA 2A310

C502 PEST 470N 63V 10% 2K447

C504 CERD 10N 63V 20% RA 2A310

C505 CERD 100N 63V 20% RA 2A410

C506 ELST 10U 50V 2N610

C511 CERD 100N 63V 20% RA 2A410

C512 CERD 470P 50V -20% +80%

RA

CA1 CD...T MAINS JUMPER

CABLE

D100-106 SSDIODE 1N4148 75V 3A4148

D200-212 SSDIODE 1N4148 75V 3A4148

D213 RECTIFIER 1N4003F 1A 200V 3B4003

D214 Diode 5V1 400mW 3C0510

D215 SSDIODE 1N4148 75V 3A4148

D300 SSDIODE 1N4148 75V 3A4148

D301 ZENER 4V7 400MW 3C0470

D400-402 SSDIODE 1N4148 75V 3A4148

DISP100 DISP CD SONY 14-ST-20GK B1 015

E1 CDTEXT VFD SUPPORT E916M

EL200 EARTH LEAD 8M101

FS200 INS COVER PCB

FUSEHOLDER

FS200 FUSEHOLDER 20mm PCB 8S004

FS201 FUSE 20mm 160mA T

S504160mA

FS201 FUSEHOLDER 20mm PCB 8S004

FS201 INS COVER PCB

FUSEHOLDER

HS200 HEATSINK CLIP TO220 13/8.6

DC/W

HS200 HEATSINK TO220 8.6

DEGC/W

HS201 HEATSINK TO220 CLIP 30 F007

HS202 HEATSINK TO220 CLIP 30 F007

IC100 IC CD CXP82832-031Q

MICRO

IC200 IC VREG LM1086CT-ADJ 5D1086

IC201-203 IC VREG POS LM317T 5D317T

IC204 IC VREG POS LM337T 5D337

IC205 IC VREG POS LM337T 5D337

IC300 IC HCMOS 74HCU04 5J7404

IC302 IC CMOS MICRO

PIC16C54XT/P

IC302 IC SOCKET 18 PIN 0.3'' 8S018

2A110

2A110

C

C

2A147

L920C

A

4

4

C

F022

C11166

F022

F006

F008

5G8283

2

A

5H16C5

4X

Page 15

Reference Description Part

number

IC302SW SOFTWARE L825S

W

IC303 IC MOTOR DRIVER LB1641 5Q1641

IC400 IC OPAMP DUAL NJM2114D 5B2114

IC401 IC OPAMP DUAL NJM2114D 5B2114

IC403 IC CD PCM1716 24 bit 96KHZ

DAC

IC404 IC HCMOS 74HCU04 5J7404

IC500 IC HCMOS 74HCU04 5J7404

IC502 SPDIF OPTICAL

TRANSMITTER

JP203 JUMPER SOCKET 0.1'' 8K004

JP205 JUMPER SOCKET 0.1'' 8K004

JP300 JUMPER SOCKET 0.1'' 8K004

JP400 JUMPER SOCKET 0.1'' 8K004

JP401 JUMPER SOCKET 0.1'' 8K004

JP402 JUMPER SOCKET 0.1'' 8K004

L200 6U8H INDUCTOR 7D968

L201 6U8H INDUCTOR 7D968

L400-402 FERRITE BEAD SINGLE

AXIAL T APED 2K BOX

L403 33UH IND 34-48330 7D033

L404 FERRITE BEAD SINGLE

AXIAL T APED 2K BOX

LED100 LED GREEN 3.1MM SLR-

37MG3F

LK600 RES MF W4 1% 0R0 1H000

LK601 RES MF W4 1% 0R0 1H000

PB PCB L899PB

PL203 2WAY MOLEX VERT MALE

CONNECTOR

PL205 2WAY MOLEX VERT MALE

CONNECTOR

PL300 3WAY MOLEX VERT MALE

CONNECTOR

PL400-402 2WAY MOLEX VERT MALE

CONNECTOR

R100 RES MF W4 1% 220R 1H122

R101 RES MF W4 1% 10K 1H310

R102 RES MF W4 1% 10K 1H310

R103 RES MF W4 1% 6K8 1H268

R104-107 RES MF W4 1% 6K8 1H268

R108 RES MF W4 1% 3K3 1H233

R109 RES MF W4 1% 2K2 1H222

R110 RES MF W4 1% 1K5 1H215

R111 RES MF W4 1% 1K0 1H210

R112 RES MF W4 1% 680R 1H168

R113 RES MF W4 1% 10R 1H010

R114-117 RES MF W4 1% 10K 1H310

R200 RES MF FU W3 1R0 5%

NFR25

R201 RES MF FU W3 1R0 5%

NFR25

R202 RES W25 5% VR25 1M5 1K515

R203 RES MF W4 1% 330R 1H133

R204 RES MF W4 1% 10R 1H010

R205 RES MF W4 1% 10R 1H010

R206 RES MF W4 1% 220R 1H122

R207 RES MF W4 1% 220R 1H122

R208 RES MF W4 1% 1K8 1H218

5G1716

5TG550

T

A

A

7F003

7F003

3D007

_2

8K6201

8K6201

8K2103

8K6201

1G810

1G810

Reference Description Part

number

R209 RES MF W4 1% 1K8 1H218

R210 RES MF FU W3 1R0 5%

NFR25

R211 RES MF FU W3 10R 5%

NFR25

R212 RES MF FU W3 1R0 5%

NFR25

R213 RES MF FU W3 10R 5%

NFR25

R214 RES MF W4 1% 1K6 1H216

R215 RES MF W4 1% 22K 1H322

R216 RES MF W4 1% 1K0 1H210

R217 RES MF W4 1% 33K 1H333

R218 RES MF W4 1% 270R 1H127

R219 RES MF W4 1% 270R 1H127

R220 RES MF W4 1% 820R 1H182

R221 RES MF W4 1% 820R 1H182

R222 RES MF W4 1% 470K 1H447

R223 RES MF W4 1% 10K 1H310

R224 RES MF W4 1% 10K 1H310

R225 RES MF W4 1% 2K2 1H222

R226 RES MF W4 1% 10K 1H310

R227 RES MF W4 1% 100R 1H110

R228 RES MF W4 1% 100R 1H110

R229 RES MF W4 1% 1K5 1H215

R230 RES MF W4 1% 10K 1H310

R301 RES MF W4 1% 330R 1H133

R302 RES MF W4 1% 330R 1H133

R303 RES MF W4 1% 6K8 1H268

R305 RES MF W4 1% 330R 1H133

R307-310 RES MF W4 1% 10K 1H310

R311 RES MF W4 1% 100K 1H410

R312 RES MF W4 1% 6K8 1H268

R313 RES MF W4 1% 100K 1H410

R314 RES MF W4 1% 10K 1H310

R315 RES MF W4 1% 10K 1H310

R400 RES MF W4 1% 330R 1H133

R401 RES MF W4 1% 330R 1H133

R402 RES MF W4 1% 4K7 1H247

R403 RES MF W4 1% 1K8 1H218

R404 RES MF W4 1% 1K8 1H218

R405-408 RES MF W4 1% 120R 1H112

R409 RES MF W4 1% 10K 1H310

R410 RES MF W4 1% 6K8 1H268

R411 RES MF W4 1% 6K8 1H268

R412-414 RES MF W4 1% 4K7 1H247

R415-418 RES MF W4 1% 2K7 1H227

R419 RES MF W4 1% 3K9 1H239

R420 RES MF W4 1% 3K9 1H239

R423 RES MF W4 1% 22K 1H322

R424 RES MF W4 1% 22K 1H322

R425 RES MF W4 1% 1M0 1H510

R426 RES MF W4 1% 33K 1H333

R427 RES MF W4 1% 33K 1H333

R428 RES MF W4 1% 330R 1H133

R429 RES MF W4 1% 4M7 1H547

R430 RES MF W4 1% 1K0 1H210

R431 RES MF W4 1% 10K 1H310

R432 RES MF W4 1% 10K 1H310

R433 RES MF W4 1% 1K0 1H210

R434 RES MF W4 1% 1K0 1H210

R435 RES MF W4 1% 680R 1H168

1G810

1G010

1G810

1G010

Page 16

Reference Description Part

number

R436 RES MF W4 1% 680R 1H168

R439 RES MF W4 1% 1M0 1H510

R442 RES MF W4 1% 2K2 1H222

R443 RES MF W4 1% 2K2 1H222

R500 RES MF W4 1% 10R 1H010

R501 RES MF W4 1% 10R 1H010

R505 RES MF W4 1% 120R 1H112

R506 RES MF W4 1% 1K2 1H212

R515 RES MF W4 1% 10K 1H310

R516-518 RES MF W4 1% 1K2 1H212

R519 RES MF W4 1% 100R 1H110

RLY400 RELAY 960 OHM 51SB12T A205

RX100 REMOTE RX PIC-26043TM2

38KHZ

SH400 PHONO EMC SHIELD E821M

SK100 32-WAY FFC CONN HORIZ 8K8132

SK200 IEC MAINS CONN PCB INS

PX

SK200 COPPER RIVET TCP/D48 BS HP007

SK200 COPPER RIVET TCP/D48 BS HP007

SK300 23-WAY FFC CONN VERT 8K8023

SK302 32-WAY FFC CONN VERT 8K8032

SK303 5-WAY AMP CT CONN 8K2005

SK400 PHONO SKT 2-WAY HOR

EMC GOLD

SK501 PHONO SKT SINGLE EMC 8D220

SP102 LED SPACER F195

SP103 DS STICKY PAD 70 X 12mm F205

SP104 IR RX SUPPORT PAD E822AP

SW100SW107

SW200 SWITCH PUSH MAINS DPST

TR200TR203

TR204 TRANS LF SS P BC557B 4A557

TR300 TRANS LF SS N BC549B 4A549

TR301 TRANS LF SS N BC549B 4A549

TR402 TRANS LF SS N BC547B 4A547

TX200 ALPHA 7CD MAINS

X100 CER RESON 8.00MHz 7W008

X300 CER RESON 4.00MHz 7W005

X400 CRYSTAL 16.9344MHz

TACT SWITCH 2-PIN LOW

PROF 9.5mm ACTUATOR

SKHVBH

TV-8

TRANS LF SS N BC549B 4A549

TRANSFORMER

PARALLEL

B2107

C

8A001

8D230

A1511

A1010

L849T

X

7X012

Page 17

CD62 General Assembly Parts List

ITEM 230V 115V 100V SILVER BLACK DESCRIPTION WHERE USED QTY

A L817RC REMOTE CONTROL 1

B L849TX L850TX L851TX TX ( L867TX = 230/115VAC multivoltage ) 1

E050AY E050AYB CD72 FRONT PANEL 1

E071AY E071AYB CD DRAWER FRONT 1

E828CP E827CP COVER PLATE 1

HA4V06S HAV406B M/C TORX M4X6 LID TO CHASSIS 4

B2012 SONY MECH 1

C11166

160mA T

C11256

250mA T

C11316

315mA T

FUSE 20MM L899AY FS201 1

E049AY REAR PANEL ASSEMBLY 1

E061AY CHASSIS & DVD / CD SUB PANEL ASSY 1

E072AY DIVA EXTENDED POWER BUTTON 1

E808MI MAINS INSULATOR 1

E879PM FOOT 4

E879SL PRODUCT CONFIGURATION CONTROL

INSIDE CHASSIS NEXT TO SL115 1

LABEL

E897PM DT81 CONFIRM BUTTON IN FRONT PANEL 8

F022 FUSE HOLDER COVER E899AY FS200 FS201 2

F164 TAPE 3509 BK 3M TESA. 5MM WIDE FRONT PANEL 400MM

F205 D/SIDED TAPE 12MM WIDE CD DRAWER FRONT 250MM

F214 WHITE 12MM DOUBLE SIDED STICKY TAPE STICK ADAPTOR TO MECH

120MM

FRONT

HA3V10A M3 x 6mm MACHINE SCREW PCB TO CHASSIS 8

HA3V06A MC TORX P/H M3X6 STZP SCREW DISP PCB TO SUB PANEL 4

HA4A12B M/C PAN SUPA M4X12 STBK (500) EARTH LEAD TO CHASSIS 1

HA4V06S M/C TORX M4X6 ST STAINLESS STEEL MECH TO BUSHES ON NEW CHS 3

HE6V06B SFTP TORX SCREW NO.6x6mm BK FRONT PANEL TO CHASSIS, PCB

4

TO CHASSIS EARTH

HF4V09B SCREW AND STAR WASHER NO.4 X 3/8" REAR PANEL, LID TO REAR

13

PANEL

HJ4A00A NUT M4 FULL STZP (1000) EARTH LEAD TO CHASSIS 1

HL4SA WASHER M4 IN LOCK STZP EARTH LEAD TO CHASSIS 1

K5408 LIGHT PIPE SLEEVING (6mm) 1

L806CA CABLE ASS MOTORDRVE L806CA ISS2 CD MECH. LEAD 1

L811CA3 23-WAY FLEX-FOIL CD MECH. LEAD 1

Page 18

CD62 General Assembly Parts List

ITEM 230V 115V 100V SILVER BLACK DESCRIPTION WHERE USED QTY

L860CA CD 72/92 DISPLAY TO MAIN FCC CABLE DISPLAY LEAD 1

L933AY MOTHER/DISP. PCB BUILD STD 1

SL017 BLANKING LABEL REAR PANEL 1

SL025 LASER WARNING (CLASS 1 LASER

PRODUCT)

SL115 LASER LABEL (DANGER RADIATION) INSIDE CHASSIS 1

REAR PANEL 1

Loading...

Loading...