PLUS MAKE YOUR PRODUCTION A-PLUS

A

ASM4106C

DATA SHEET

PLUS INTEGRATED CIRCUITS INC.

A

Address:

3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei,

Taiwan 115, R.O.C.

(115)台北市南港區成功路㆒段 32 號 3 樓之 10.

TEL: 886-2-2782-9266

FAX: 886-2-2782-9255

WEBSITE : http: //www.aplusinc.com.tw

Sales E-mail: Mr. Jason

sales@aplusinc.com.tw

Technology E-mail: Mr. George

service@aplusinc.com.tw

ASM4106C Data Sheet

Aplus

ASM4106C – VERY LOW-COST VOICE SYNTHESIZER WITH 4-BIT MICROPROCESSOR

1.0 General Description

The ASM4106C is very low cost voice synthesizer with 4-bit microprocessor. It has various features

including 4-bit ALU, ROM, RAM, I/O ports, timers, clock generator, watchdog timer(WDT), voice

synthesizer, etc. It consists of 22 instructions in the device. With CMOS technology and halt function

can minimize power dissipation. Its architecture is similar to RISC, with two stages of instruction

pipeline. It allows all instructions to be executed in a single cycle, except for program branches and

data table read instructions (which need two instruction cycles).

1.1 Feature

Single power supply can operate from 2.4V through 5V

Internal Program ROM: 4K x 10-bit

1 sets of 17-bit DPR can access up to 128K x 10 bits data memory space

Data Registers:

• 64 x 4-bit data RAM (00-1Fh plus 40h-5Fh)

• Unbanked special function registers (SFR) range: 20h-3Fh

I/O Ports:

• PRA: 4-bit I/O Port A (2Bh)

• PRB: 2-bit Output Port B (2Dh)

On-chip clock generator: Resistive Clock Drive(RM)

Timer: 1

• Timer0: a 9-bit auto-reload timer/counter

Stack: 2-level subroutine nesting

HALT and Release from HALT function to reduce power consumption

Watch Dog Timer (WDT)

Instruction: 1-cycle instruction except for table read and program branches which are 2-cycles

Number of instruction: 22

The Voice function can be implemented by microprocessor instruction

1

Rev 1.0

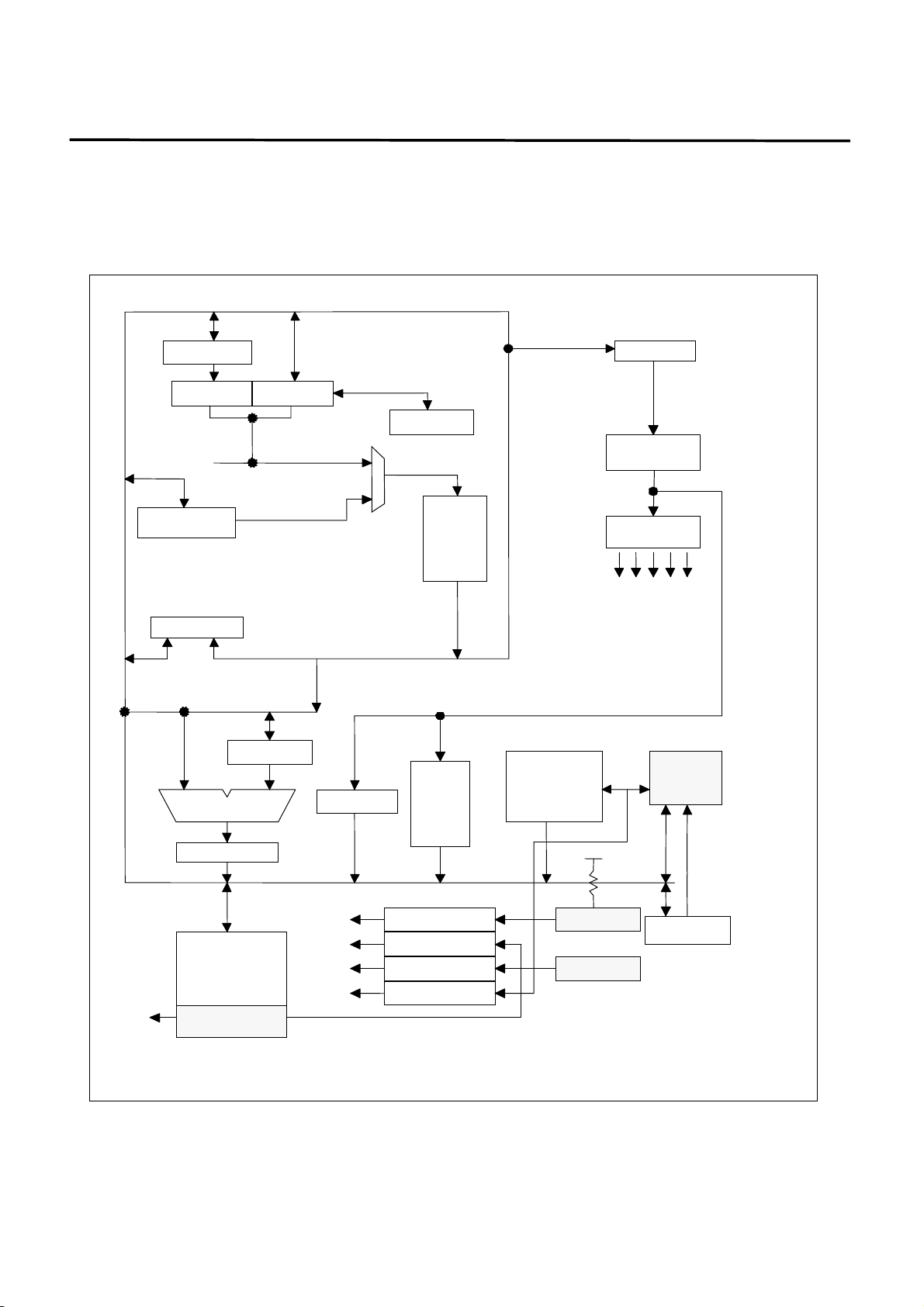

FIGURE 1.1 : Block Diagram of ASM4106C

(12)

]

(4)

)

Aplus

Data Bus[3:0]

ASM4106C Data Sheet

(ADDR[16:12])

=00000b

COUT

PCLATCH(8)

PCH(8) PCL(4)

DPR3,2,1

DLATCH(10)

Data Bus[3:0

Accumlator

ALU(4)

Register(4)

One-Channel

( Voice synthesizer )

COUT

PC[11:0]

ADDR[16:0]

DPR[16:0]

P1,P2,P3,P4

enter test mode

Reset Chip

Reset Chip

ROM_Data[9:0]

Immediate(4

Stack

(2-Level)

ROM_ADDR[16:0]

Program

(Data)

ROM

SRAM

(64 x 4)

00h-1Fh

40h-5Fh

Clock Generator

Tes t s el ect

Power on Reset

RESET pin

Instruction Bus [9:0]

Instruction Bus [9:0]

Timer0(9)

OSC

VDD/GND

PRA0

ROM Latch

Instruction

Latch

Instruction

Decoder

Control Signal

Instruction Bus [9:0]

PRA(4)

PRB(2)

weak or strong

pull-low for PRA,

PRB, PRC

PRASL(4)

2

Rev 1.0

Loading...

Loading...