APLUS APR6008 Datasheet

INTEGRATED CIRCUITS INC.

APR6008

Voice Recording & Playback Device

8 Minute Duration

Features

•Multi-level analog storage

-High quality audio recording and playback

•Dual mode storage of analog and/or digital data

-Eliminates the need for separate digital memory

•Advanced, non-volatile Flash memory technology

-No battery backup required

•SPI interface

-Allows any commercial microcontroller to control

the device

•Programmable Sampling Clock

-Allows user to choose quality and duration levels

•Single 3V power supply

•Low power consumption

-Playback operating current: 15 mA typical

-Standby current: 1 uA maximum

-Automatic power-down

•Multiple package options available

-CSP, SOP, PDIP, Bare Die

•On-board clock prescaler

-Eliminates the need for external clock dividers

•Automatic squelch circuit

Reduces background noise during quiet passages

-

General Description

Figure 1 APR6008 Pinout Diagrams

The APR6008 offers non-volatile storage of voice and/or data

in advanced Multi-Level Flash memory. Up to 8 minutes of

audio recordin

imum of 30K bits of di

devices can be cascaded for lon

greater digital storage. Device control is accomplished

throu

gh an industry standard SPI interface that allows a

microcontroller to mana

This flexible arran

messa

ging options. The APR6008 is ideal for use in cellular

and cordless phones, telephone answerin

di

gital assistants, personal voice recorders, and voice pag-

ers.

APLUS Integrated

lity

by usin

i mplemented in an advanced non-volatile Flash memory

logy

process. Each memory cell can typically store 256 volta

levels. This allows the

si

gnals in their natural form, eliminating the need for en

ding

and compression which can introduce distortion.

2002/5/10 Page 1

g and playback can be accommodated. A max-

gital data can be stored.

APR6008

ger duration recording or

ge message recording and playback.

gement allows for the widest variety of

g devices, personal

achieves this high level of storage capabi-

g a proprietary analog multi-level storage te

APR6008 voice

to

reproduce audio

chno

co-

ge

28 pin DIP

/CS

1

DI

2

DO

NC

NC

NC

NC

3

4

5

6

7

8

9

10

11

12

13

14

VSSD

ANAOUT-

ANAOUT+

/RESET

l -

VSSA

AUDOUT

SQLCAP

28

27

26

25

24

23

22

21

20

19

18

17

16

15

SCLK

VCCD

EXTCLK

/INT

SAC

VSSA

NC

/BUSY

NC

NC

VCCA

ANAIN+

ANAIN/SQLOUT

APR6008

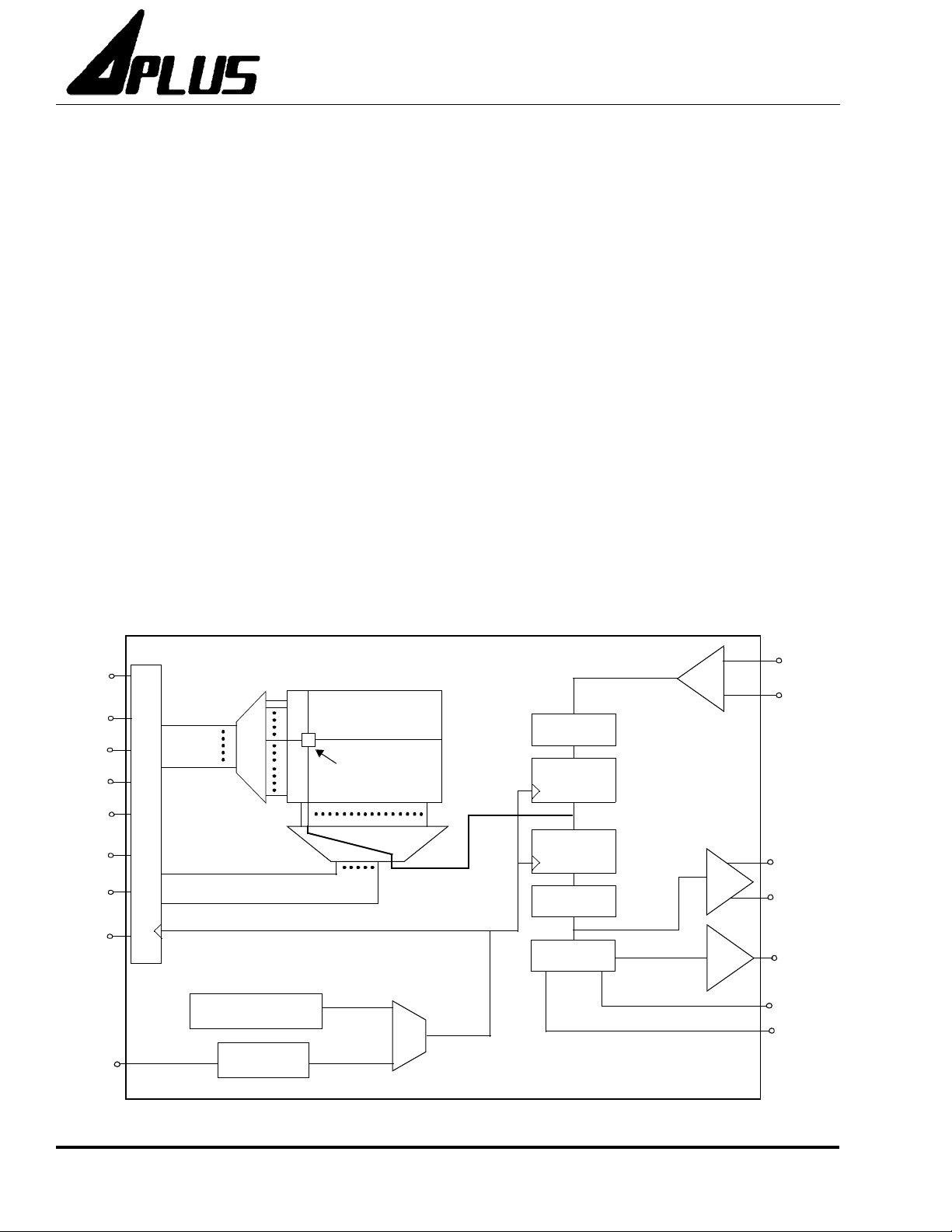

Functional Description

The EXTCLK pin allows the use of an external sampling

clock. This input can accept a wide range of frequencies

dependin

that follows the clock. Alternativel

nal oscillator can be used to suppl

Mux followin

si

gnal if a clock is present, otherwise the internal oscillator

source is chosen. Detailed information on how to pro

divider and internal oscillator can be found in the explanation

of the

Command Description

the appropriate sample clock fre

Sampling Rate & Voice Quality

The audio si

should be fed into the differential inputs ANAIN-, and

ANAIN+. After pre-amplification the si

anti-aliasin

its response based on the sample rate bein

nal anti-aliasin

After passin

the sample and hold circuit which works in con

the Analo

flash memor

g on the divider ratio programmed into the divider

y, the programmable inter-

y the sampling clock. The

g both signals automatically selects the EXTCLK

gram the

PWRUP

command, which appears in the

section. Guidance on how to choose

quency can be found in the

section.

gnal containing the content you wish to record

gnal is routed into the

g filter. The anti-aliasing filter automatically adapts

g used. No exter-

g filter is therefore required.

g through the anti-alias filter, the signal is fed into

g Write Circuit to store each analog sample in a

y cell.

OpCode

junction with

When a read operation is desired the Analog Read Circuit

extracts the analo

the si

gnal to the Internal Low Pass Filter. The low pass filter

converts the individual samples into a continuous output. The

output si

fferential output driver. The differential output driver feeds the

ANAOUT+ and ANAOUT- pins. Both differential output pins

swin

The s

si

control si

reducin

mation, refer to the

After passin

goes to the output amplifier. The output amplifier drives a single ended output on the AUDOUT pin. The single ended output swin

All SPI control and hand shakin

Master Control Circuit. This circuit decodes all the SPI si

and

the status re

the APR6008 .

gnal then goes to the squelch control circuit and di-

g around a 1.23V potential.

quelch control circuit automatically reduces the output

gnal by 6 dB during quiet passages. A copy of the squelch

gnal is present on the SQLOUT pin to facilitate

g gain in the external amplifier as well. For more infor-

gs around a 1.23V potential.

generates all the internal control signals. It also contains

g data from the memory array and feeds

Squelch

g through the squelch circuit the output signal

gister used for examining the current status of

section.

g signals are routed to the

gnals

Figure 2 APR6008 Block Diagram

/RESET

/BUSY

SAC

/INT

DO

DI

/CS

SCLK

EXTCLK

Row

Address

Row Decoder

Master Control Circuit

Column Address

Programmable Internal

Oscillator

Programmable

Divider

1.92 Mcell Memory Array

Single Analog

Memory Cell

Column Decoder

Analog input/output

to Memory array

Mux

Low Pass

Write Circuit

Read Circuit

Low Pass

Squelch

Pre-

Amp

Amp

Amp

ANAIN+

ANAIN-

ANAOUT+

ANAOUT-

AUDOUT

SQLCAP

/SQLOUT

Page 2 Voice Recording & Playback Device

Revision 2.1

APR6008

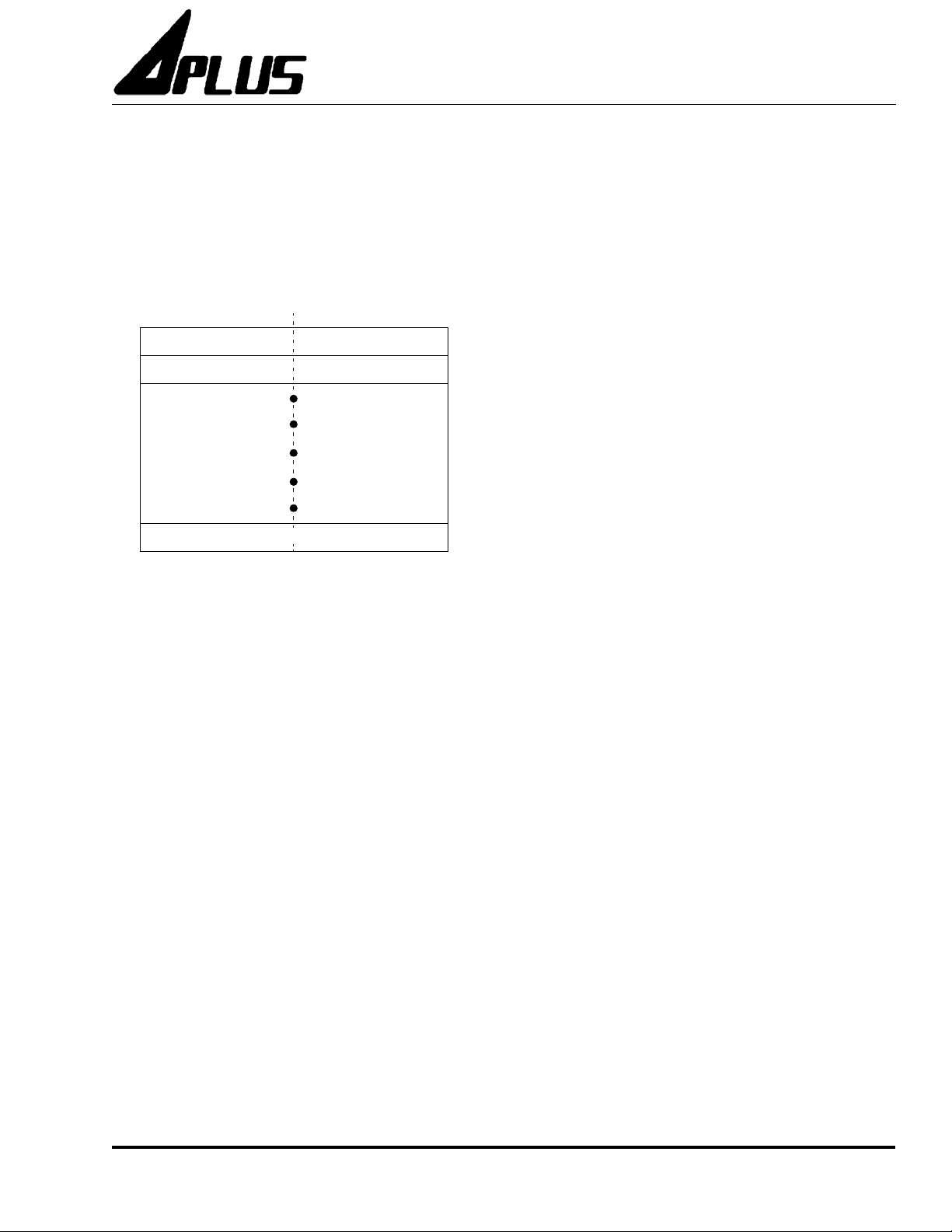

Memory Organization

The APR6008 memory array is organized to allow the greatest flexibilit

The smallest addressable memor

The APR6008 contains 640 sectors.

y in message management and digital storage.

y unit is called a “sector”.

Figure 3 Memory Map.

SAC Trigger Point

Sector 0

Sector 1

Sector 639

Sectors 0 through 639 can be used for analog storage. Du ring

audio recording one memory cell is used per sample

clock c

ycle. When recording is stopped an end of data (EOD)

bit is programed into the memory. This prevents playback of

silence when partial sectors are used. Unused memor

exists between the EOD bit and the end of the sector can not

be used.

Sectors 0 throu

stora

ge. Other sectors, with the exception of sector 639, can

store data but have not been tested, and are thus not

teed to provide 100%

error correction or forward check-before-store methods.

Once a write c

chosen sector is lost.

Mixin

g audio signals and digital data within the same sector is

not possible.

Note: There are a total of 15bits reserved for addressing. The

APR6008 only

for larger devices within the APR6008 family.

Can Not be Used for Digital Data

y that

gh 9 are tested and guaranteed for digital

guaran-

good bits. This can be managed with

ycle is initiated all previously written data in the

requires 10 bits. The additional 5 bits are used

SPI Interface

All memory management is handled by an external host processor. The host processor communicates with the APR6008

throu

gh a simple Serial Peripheral Interface (SPI) Port. The

SPI port can run on as little as three wires or as man

seven dependin

section will describe how to mana

APR6008 SPI Port and associated OpCode commands.

This topic is broken down into the followin

•Sendin

•OpCode Command Description

•Receivin

•Current Device Status

•Reading the Silicon Identification (SID)

•Writin

•Readin

•Recordin

•Pla

•Handshakin

Sending Commands to the Device

This section describes the process of sendin

the APR6008 All Opcodes are sent in the same wa

exception of the

The

in the

that follow. The minimum SPI confi

commands uses the DI, /CS, and SCLK pins. The device will

accept inputs on the DI pin whenever the /CS pin is low.

OpCode commands are clocked in on the risin

SPI clock. Fi

OpCode commands into the device. Figure 5 is a description

of the OpCode stream.

You must wait for a command to finish executin

in

BUSY pin. You can substitute monitorin

inserting a fixed delay between commands. The required

dela

shows the timin

mands. Table 1 describes which

g Digital Data

ying Back Audio Data

DIG_WRITE and DIG_READ

Writing Digital Data

g a new command. This is accomplished by monitoring the /

y is specified as

g on the amount of control necessary. This

ge memory using the

g sections:

g Commands to the Device

g Device Information

(CDS)

g Digital Data

g Audio Data

g Signals

g OpCodes to

DIG_WRITE

and

gure 4 shows the timing diagram for shifting

T

g diagram for sending consecutive com-

next1,Tnext2,Tnext3

DIG_READ

and

commands

are

Reading Digital Data

guration needed to send

g edge of the

g before send-

g of the busy pin by

or T

next4

specification to use.

T

next

y as

y with the

commands

described

sections

. Figure 6

.

Voice Recording & Playback Device Page 3

Revision 2.1

APR6008

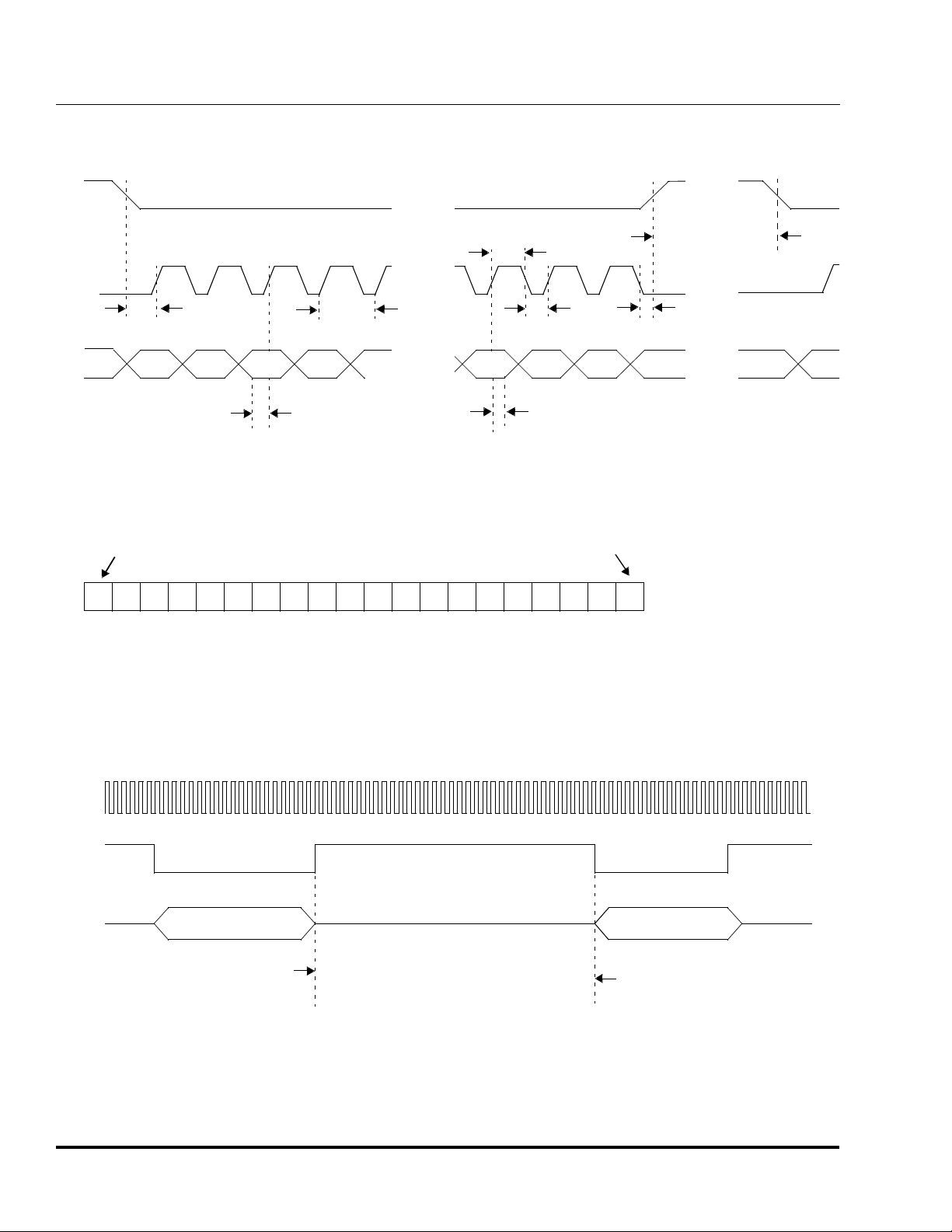

Figure 4Sending SPI Commands

/CS

SCLK

~

~

T

hiSCLK

~

~

T

next1

, T

~

~

next2

~

~

, T

next3

, T

next4

T

fCS

DI

Figure 5OpCode Format

Op4Op3 Op1Op0A14A13A12A11A10 A9 A8 A7 A6Op2

Op4

First bit shifted in

Op3

Op2 Op1

T

suDI

T

pSCLK

{

OpCode Command OpCode Parameter

Figure 6Opcode Stream Timing

A0

A0

T

rCS

~

~

T

loSCLK

~

~

T

A5 A4 A3 A2 A1

A1A2

hDI

Last bit shifted in

{

SCLK

/CS

DI

Page 4 Voice Recording & Playback Device

Current Command Next Command

T

next1,Tnext2,Tnext3,Tnext4

Revision 2.1

APR6008

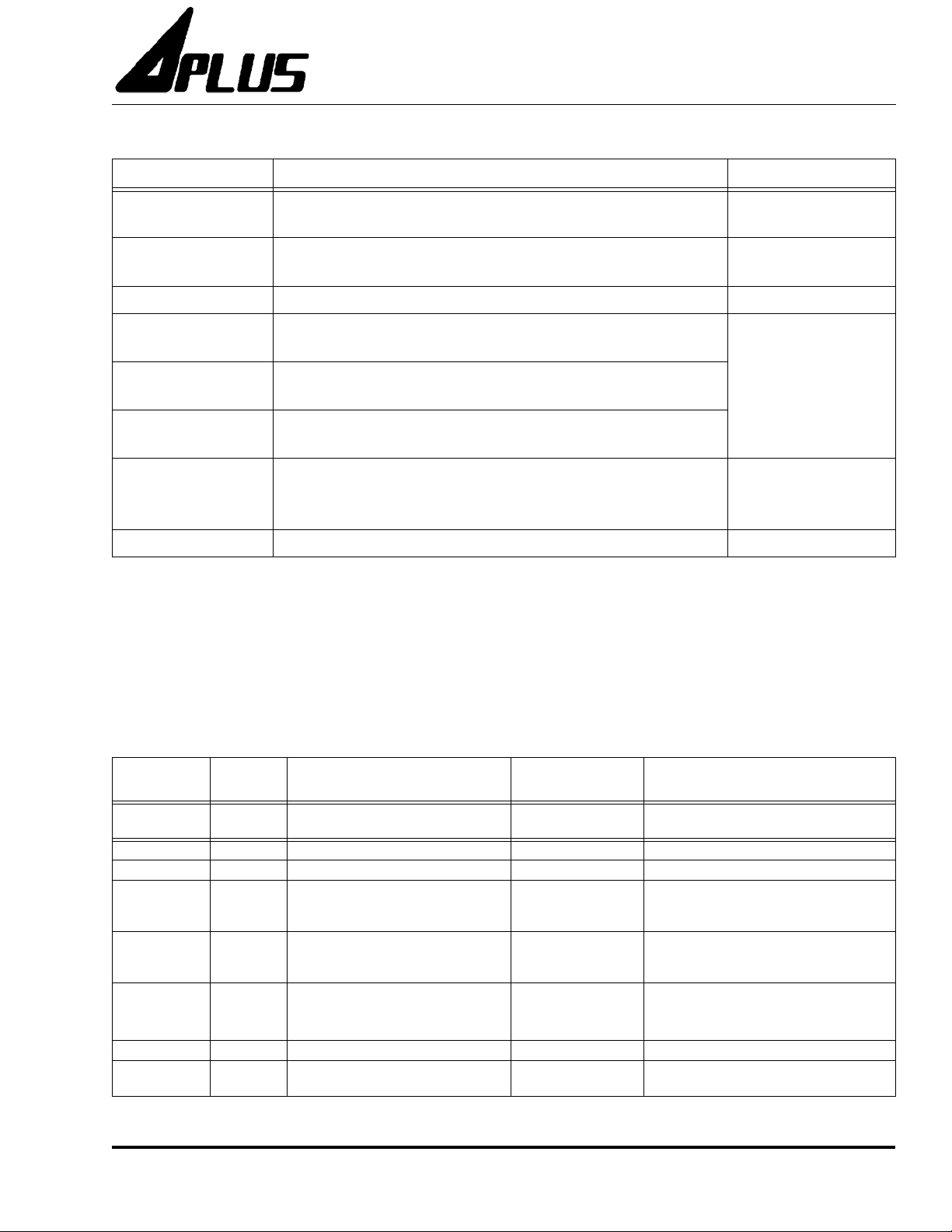

Table 1 Sequential Command Timing

Current Command Next command Timing Symbol

NOP

Any Command T

SID

PWRUP

Any Command T

STOP_PWDN PWRUP

SET_REC

STOP, STOP_PWDN, SET_REC, REC,NOP

REC

SET_PLAY

STOP, STOP_PWDN, SET_FWD, FWD, SET_PLAY,PLAY, NOP

PLAY

SET_FWD

SET_FWD, FWD, STOP, STOP_PWDN

FWD

DIG_WRITE

DIG_READ

DIG_ERASE

STOP

Any Digital Command,

Note: For partial DIG_READ T

rise of /CS, not from the rise of /CS

Any Command T

STOP, STOP_PWDN

is measured from the extra clock low that follows the 8K sampling rate: 376m SEC

next2

OpCode Command Description

Designers have access to a total of 14 OpCodes. These

OpCodes are listed in Table 2. The name of the Opcode

appears in the left hand column. The followin

represent the actual binar

y information contained in the 20 bit

data stream. Some commands have limits on which com-

g two columns

next1 5u SEC

next2 5m SEC

T

next2 5m SEC

Within SAC Low Time

T

next3

4K sampling rate: 752 m SEC

next4 470m SEC

mand can follow them. These limits are shown in the “

able Follow on Commands

” column. The last column

Allow-

summarizes each command.

Combinations of OpCodes can be used to accommodate

almost an

y memory management scheme.

Table 2

Instruction

Name

NOP

SID

SET_FWD

FWD

PWRUP

STOP

STOP_PWDN

Voice Recording & Playback Device Page 5

Revision 2.1

Operational Codes

APR6008

OpCode

(5 bits) Opcode Parameters (15bits)

[Op4 - Op0]

[00000] [Don’t Care] All Commands No Operation

[00001] [Don’t care] All Commands Causes the silicon ID to be read.

[00010] Sector Address

[00011] [Don’t care] SET_FWD,

[00100] [A14-A10]: all zeros

[00110] [Don’t care] All Commands Stops the current operation.

[00111] [Don’t care] PWRUP Stops the current operation. Causes the

[Address MSB - Address LSB]

[Address 14 - Address 0]

[A14 - A0]

[A9-A2]: EXTCLK divider ratio

[A1-A0]: Sample Rate Frequency

Allowable Follow

on Commands Summary

SET_FWD,

FWD, STOP,

STOP_PWDN

FWD, STOP,

STOP_PWDN

All Commands Resets the device to initial conditions.

Starts a fast forward operation from the

sector address specified.

Starts a fast forward operation from the

current sector address.

Sets the sample frequency and divider

ratios.

device to enter power down mode.

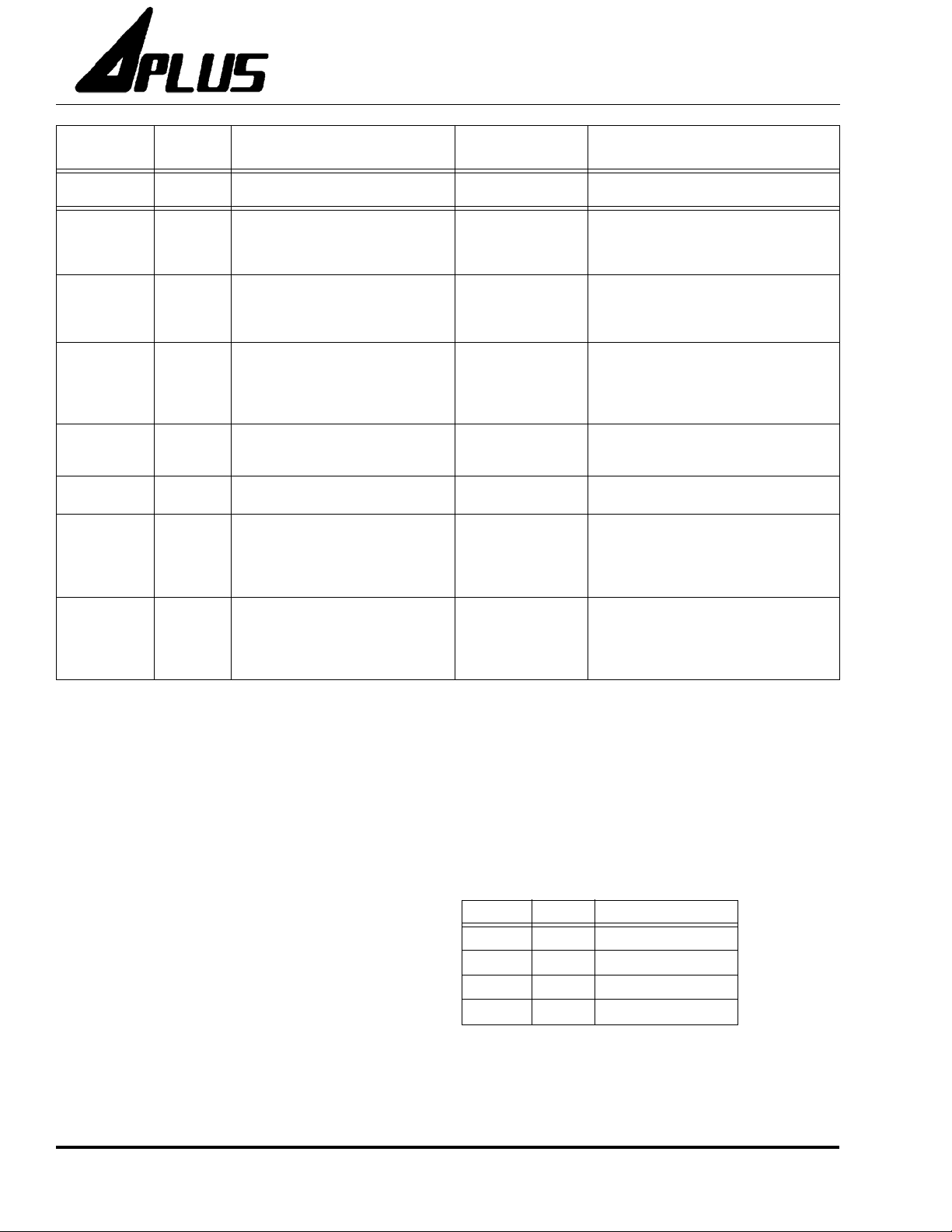

APR6008

Instruction

Name

SET_REC

REC

DIG_ERASE

DIG_WRITE

DIG_READ

SET_PLAY

PLAY

OpCode

(5 bits) Opcode Parameters (15bits)

[Op4 - Op0]

[01000] Sector Address

[01001] [Don’t care] STOP,

[01010] Sector Address

[01011] [A14 - A0][XXXX][D0 - D3004][XXXX] All Commands This command writes data bits D0 - D3003

[01111] Sector A d dress

[01100] Sector Address

[01101] [Don’t care] STOP,

[Address MSB - Address LSB]

[Address 14 - Address 0]

[A14 - A0]

[A14 - A0]

[A14 - A0]

[A14 - A0]

Allowable Follow

on Commands Summary

STOP,

STOP_PWDN,

SET_REC,

REC,NOP

STOP_PWDN,

SET_REC,

REC,NOP

All Commands Erases all data contained in specified sec-

All Commands This command reads data bits D0 - D3003

STOP,

STOP_PWDN,

SET_FWD, FWD,

SET_PLAY,PLAY,

NOP

STOP_PWDN,

SET_FWD, FWD,

SET_PLAY,PLAY,

NOP

Starts a record operation from the sector

address specified.

Starts a record operation from the current

sector address.

tor. You must not erase a sector before

recording voice signals into it. You must

erase a sector before storing digital data in

it.

starting at the specified address. All 3004

bits must be written.

starting at the specified address.

Starts a play operation from the sector

address specified.

Starts a play operation from the current

sector address.

NOP

The

command performs no operation in the device. It is

most often used when readin

more information on readin

Device Status

SID

THE

of its silicon ID re

ing the SID

SET_FWD

The

from the be

section.

operation instructs the device to return the contents

gister. For more information see the

section.

command instructs the device to fast forward

ginning of the sector specified in the OpCode

g the current device status. For

g device status see the

Current

Read-

The device will continue to fast forward in this manner until

either an EOD is reached, a new command is sent, or the end

of the memor

the device will stop and

The output amplifiers are muted durin

PWRUP

The

mode and set the internal clock fre

divider ratio. To select an Internal oscillator fre

[A1 - A0] bits accordin

y array is reached. When an EOD is reached

generate an interrupt on the /INT pin.

g this operation.

command causes the device to enter power up

quency and EXTCLK

quency set the

g to the following binary values:

parameter field. The device will fast forward until either an

EOD bit, or the end of the sector is reached. If no EOD bit or

forthcomin

the sector is reached, the device will loop back to the be

nin

an EOD bit is found the device will stop and

g command has been received when the end of

gin-

g of the same sector and begin the same process again. If

generate an

interrupt on the /INT pin. The output amplifiers are muted durin

g this operation.

FWD

The

command instructs the device to fast forward from

the start of the current sector to the next EOD marker. If no

EOD marker is found within the current sector the device will

increment to the next se

Page 6 Voice Recording & Playback Device

quential sector and continue looking.

A1 A0 Sample rate

0 0 6.4 kHz

0 1 4.0 kHz

1 0 8.0 kHz

1 1 5.3 kHz

If

you are using an external sample clock signal you must

also set the EXTCLK divider ratio. This divider ratio is e

to N:1 where N is an inte

The N value should be selected to satisf

ger between 1 and 256, excluding 2.

y the following equa-

Revision 2.1

qual

APR6008

tion as closely as possible:

EXTCLK fre

Example:

Suppose that 8.0 KHz samplin

the fre

N

Roundin

The Op Code Parameter bit stream, composed of bits

[A9 - A2][A1 - A0], therefore becomes binar

[00001000][10].

STOP

The

operation.

STOP_PWDN

The

current command and enter power down mode. Durin

down the device consumes si

PWRUP command must be used to force the device into

power up mode before an

SET_REC

The

recordin

continue to record until the end of the current sector is

reached. If no forthcomin

when the end of the sector is reached the device will loop

back to the be

previousl

SET_REC

mand immediatel

that no audio information is lost. For more information see the

section entitled

REC

The

the current sector. If no new command is received before the

device reaches the end of the sector the device will automaticall

y increment to the next sequential sector and continue

recordin

until the memor

command is received. For more information see the section

entitled

DIG_ERASE

The

sector specified. Erase should not be done before recordin

voice signals into a sector. Erase must be done before storing

digital data in a sector.

DIG_WRITE

The

the specified sector. All 3K bits must be written, no partial

usa

ge of the sector is possible. The memory acts as a FIFO,

the first data bit shifted in will be the first data bit shifted out. A

sector must be erased usin

BEFORE

tion on storin

Digital Data

DIG_READ

The

q = (N) * (128) * (selected sampling frequency)

g is desired. Assume that

quency of the signal present on EXTCLK = 8MHz.

8000000

-------------------------1288000()

g up, N = 8

Command causes the device to stop the current

g at the sector address specified. The device will

y recorded material. If the next command is another

REC

or

command instructs the device to begin recording in

g. The device will continue to record in this manner

Recording Audio Data

data can be written to the sector. For more informa-

g digital data, see the section entitled

.

7.8125==

command causes the device to stop the

g power

gnificantly less power. The

y commands can be executed.

command instructs the device to begin

g command has been received

ginning of the same sector and overwrite the

command the device will execute the com-

y following the end of the current sector so

Recording Audio Data

y is exhausted or a

.

command erases all data contained in the

command stores 3K bits of digital data in

g the

.

STOP

STOP_PWDN

or

DIG_ERASE

command

Writing

command instructs the device to retrieve

di

gital data that was previously written to the specified sector.

The first bit shifted out is the first bit that was written. The last

bit shifted out is the last bit that was written. For more information on readin

g digital data see the section entitled

ing Digital Data.

SET_PLAY

The

back at the specified sector. If no forthcomin

received, or EOD bit encountered, before the end of the sector is reached the device will loop back to the be

same sector and continue pla

the audio output. If the next command is another

PLAY

or

immediatel

y

gap in playback is present. For more information see the section entitled

PLAY

The

the current sector. If no forthcomin

EOD bit encountered, before the device reaches the end of

the sector the device will automaticall

se

quential sector and continue playing. The device will con-

tinue to pla

STOP

a

information see the section entitled

g

or

command instructs the device to begin play-

g command is

ginning of the

yback with no noticeable gap in

command the device will execute the command

y following the end of the current sector so that no

Playing Back Audio Data.

command instructs the device to begin playback at

y in this manner until the memory is exhausted or

STOP_PWDN

command is received. For more

g command is received, or

y increment to the next

Playing Back Audio Data.

Read-

SET_PLAY

Voice Recording & Playback Device Page 7

Revision 2.1

Loading...

Loading...