Apex Microtechnology Corporation EB02 Datasheet

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

1

• COMPATIBLE WITH PWM FREQUENCIES UP TO 50KHZ

• 10V TO 100 V MOTOR SUPPLY

• 10A CONTINUOUS OUTPUT CURRENT

• HCMOS COMPATIBLE SCHMITT TRIGGER LOGIC INPUTS

• SEPARATE SOURCE OUTPUTS FOR NEGATIVE RAIL

CURRENT SENSE

• SLEEP MODE

• WIDE RANGE FOR GATE DRIVE AND LOGIC SUPPLIES

APPLICATIONS

HIGH POWER CIRCUITS FOR DIGITAL CONTROL OF:

• THREE AXIS MOTION USING BRUSH TYPE

MOTORS

• THREE PHASE BRUSHLESS DC MOTOR DRIVE

• THREE PHASE AC MOTOR DRIVE

• THREE PHASE STEP MOTOR DRIVE

DESCRIPTION

The EB02 consists of three independent FET half

bridges with drivers. The drivers may be interfaced

with CMOS or HCMOS level logic.

FEATURES

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

MICROTECHNOLOGY

TRIPLE INDEPENDENT LOGIC INTERFACED HALF BRIDGES

EBO2

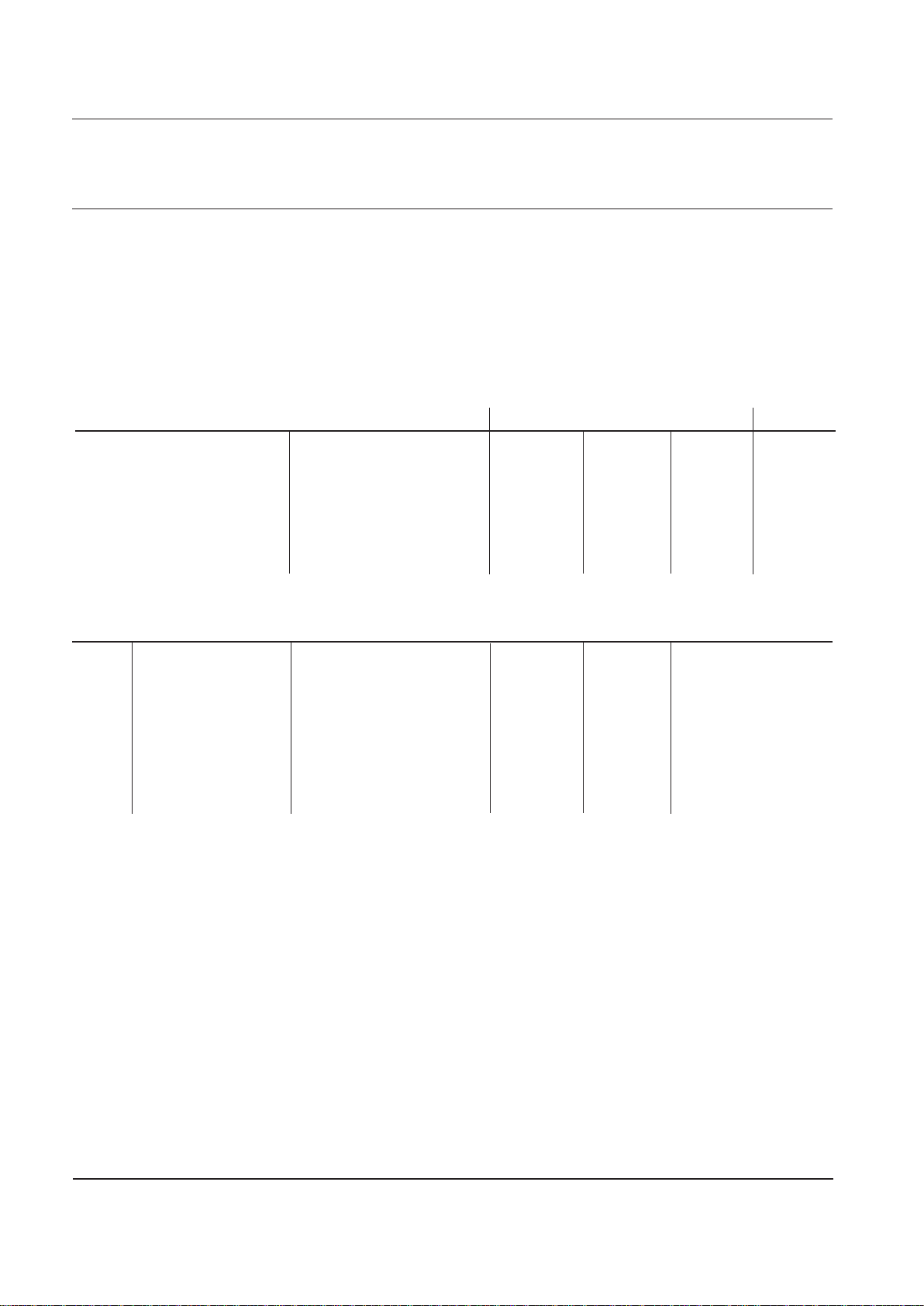

FIGURE 1. BLOCK DIAGRAM

Half

Bridge

Driver

Half

Bridge

Driver

Half

Bridge

Driver

FET

Half

Bridge

Output

FET

Half

Bridge

Output

FET

Half

Bridge

Output

12

11

1

2

3

4

5

6

7

8

9

10

14

15

16

17

18

19

20

21

22

23

24

Hin 1

13

HV1

OUT1

SD

S1

Lin 1

HVRTN1

Hin 2

HV2

OUT2

S2

HVRTN2

Lin2

HV3

OUT3

S3

HVRTN3

Hin3

Lin 3

V 1

cc

V 2

cc

V 3

cc

V

dd

,Logic Supply

V

ss

,Logic Ground

APEX MICROTECHNOLOGY CORPORATION • 5980 NORTH SHANNON ROAD • TUCSON, ARIZONA 85741 • USA • APPLICATIONS HOTLINE: 1 (800) 546-2739

2

ABSOLUTE MAXIMUM RATINGS

SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

MOTOR VOLTAGE SUPPLY, HV 100V

OUTPUT CURRENT, peak 20A

OUTPUT CURRENT, continuous1 10A

GATE SUPPLY VOLTAGE, Vcc 20V

LOGIC SUPPLY VOLTAGE, Vdd 20V

POWER DISSIPATION, internal1 51 Watts

LOGIC INPUT VOLTAGE -0.3V to Vdd + 0.3V

THERMAL RESISTANCE TO CASE3 2.1°C/Watt

TEMPERATURE, pin solder, 10s 300°C

TEMPERATURE, junction2 150°C

TEMPERATURE RANGE, storage –55 to +150°C

OPERATING TEMPERATURE, case –25 to +85°C

EB02

SPECIFICATIONS

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

POSITIVE OUTPUT VOLTAGE I

OUT

=10A; Vcc=10.8V , Vdd=5V; 99.2 101.5 Volts

HV=100V, Fpwm=50kHz, L=100 µH

NEGATIVE OUTPUT VOLTAGE " -1.5 .8 Volts

POSITIVE EDGE DELAY " 260 n-second

RISETIME " 50 n-second

NEGATIVE EDGE DELAY " 310 n-second

FALLTIME " 5 0 n-second

PWM FREQUENCY Set by external circuitry 50 kHz

INPUT IMPEDANCE Set by internal resistors 50 k-ohm

INPUT

A logic level input independently controls each FET in

the half bridge. A logic level high turns on the FET and

low turns it off. A common shut down input turns off all

FETs when high.

All inputs are Schmitt triggers with the upper threshold at

2/3 V

dd

and the lower threshold at 1/3 Vdd. This comfortably

interfaces with CMOS or HCMOS provided that the Vdd for

the logic family and the EB02 are the same.

TTL families may be used if a pull-up to Vcc is added to

the TTL gates driving the EB02, and Vdd for the EB02 is the

same supply as V

cc

for the TTL family.

An open signal connector pulls the shut down input high and

all other inputs low, insuring that all outputs are off.

However, input impedance is 50k on all inputs; therefore, if

one input is open circuited a high radiated noise level could

spuriously turn on a FET.

OUTPUT

Each output section consists of a switching mode FET half

bridge. Separate HV supply, emitter, and HV return lines are

provided for each section.

The FETs are conservatively rated to carry 10A. At 10A

the saturation voltage is 1.5 V maximum, over the full

environmental range.

Each FET has an intrinsic diode connected in anti-parallel.

When switching an inductive load this diode will conduct,

and the drop at 10A will be 1.5V maximum, over the full

environmental range.

INPUT AND OUTPUT SIGNALS

NOTES: 1. Over full operating temperature range.

2. Long term operation at the maximum junction temperature will result in reduced product life. Lower internal temperature by

reducing internal dissipation or using better heatsinking to achieve high MTTF.

3. Each FET.

PIN SYMBOL FUNCTION PIN SYMBOL FUNCTION

1 V

cc

3 Gate supply 3 13 HV1 High Voltage supply 1

2 Lin3 Low drive logic in 3 14 OUT1 Section 1 output

3 Hin3 High drive logic in 3 15 S1 Section 1 source

4 V

dd

Logic supply 16 HVRTN1 Section 1 return

5 V

cc

2 Gate supply 2 17 HV2 High voltage supply 2

6 Lin2 Low drive logic in 2 18 OUT 2 Section 2 output

7 V

ss

Signal ground 19 S2 Section 2 source

8 Hin2 High drive logic in 2 20 HVRTN2 Section 2 return

9 V

cc

1 Gate supply 1 21 HV3 High voltage supply 3

10 Lin1 Low drive logic in 1 22 OUT 3 Section 3 output

11 SD Shut down logic in 23 S3 Section 3 source

12 Hin1 High drive logic in 1 24 HVRTN 3 Section 3 return

Loading...

Loading...