HIGH VOLTAGE POWER OPERATIONAL AMPLIFIERS

PA41/PA42 • PA41A/PA42A

MICROTECHNOLOGY

FEATURES

• MONOLITHIC MOS TECHNOLOGY

• LOW COST

• HIGH VOLTAGE OPERATION—350V

• LOW QUIESCENT CURRENT—2mA

• NO SECOND BREAKDOWN

• HIGH OUTPUT CURRENT—120 mA PEAK

• AVAILABLE IN DIE FORM—PA41DIE

APPLICATIONS

• PIEZO ELECTRIC POSITIONING

• ELECTROSTATIC TRANSDUCER & DEFLECTION

• DEFORMABLE MIRROR FOCUSING

• BIOCHEMISTRY STIMULATORS

• COMPUTER TO VACUUM TUBE INTERFACE

DESCRIPTION

The PA41/42 are high voltage monolithic MOSFET operational amplifiers achieving performance features previously

found only in hybrid designs while increasing reliability. Inputs

are protected from excessive common mode and differential

mode voltages. The safe operating area (SOA) has no second

breakdown limitations and can be observed with all type loads

by choosing an appropriate current limiting resistor. External

compensation provides the user flexibility in choosing

optimum gain and bandwidth for the application.

The PA41 is packaged in a hermetically sealed TO-3 and all

circuitry is isolated from the case by an aluminum nitride (AlN)

substrate.

The PA42 is packaged in APEX’s hermetic ceramic SIP10

package.

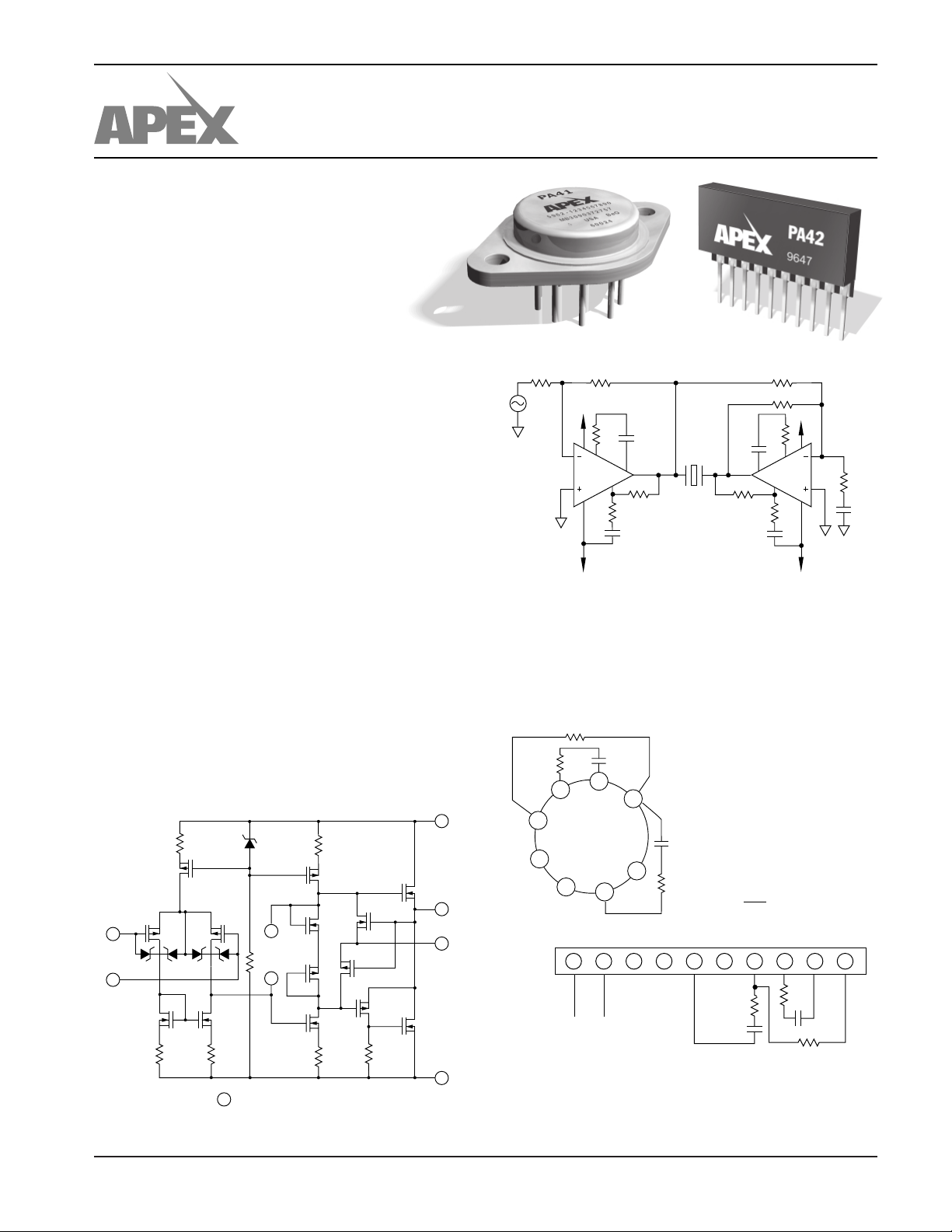

EQUIVALENT SCHEMATIC

Q1

Q5Q4

(1)

(2)

5

–IN

6

+IN

D2 D3 D4 D5

Q11

(8)

COMP

COMP

(9)

Q12

5

PA41 PIN NUMBER

(1)

PA42 PIN NUMBER

HTTP://WWW.APEXMICROTECH.COM (800) 546-APEX (800) 546-2739

8

+V

I

LIM

1

4

OUT

–V

7

(5)

S

S

D1

Q2

2

Q6

Q8

3

Q13

Q3

Q7

Q9

Q10

Q14

(6)

(7)

(10)

TYPICAL APPLICATION

R

V

IN

20R

+175

A1

PA41/42

2.2K

10pF

R

180

100Ω

330pF

CL

PIEZO

TRANSDUCER

LOW COST 660V p-p

–175

PIEZO DRIVE

Two PA41/42 amplifiers operated as a bridge driver for a

piezo transducer provides a low cost 660 volt total drive capability. The RN CN network serves to raise the apparent gain of A2

at high frequencies. If R

is set equal to R the amplifiers can be

N

compensated identically and will have matching bandwidths.

10pF

R

CL

180

100Ω

330pF

20R

20R

2.2K

PA41/42

+175

A2

Rn

Cn

–175

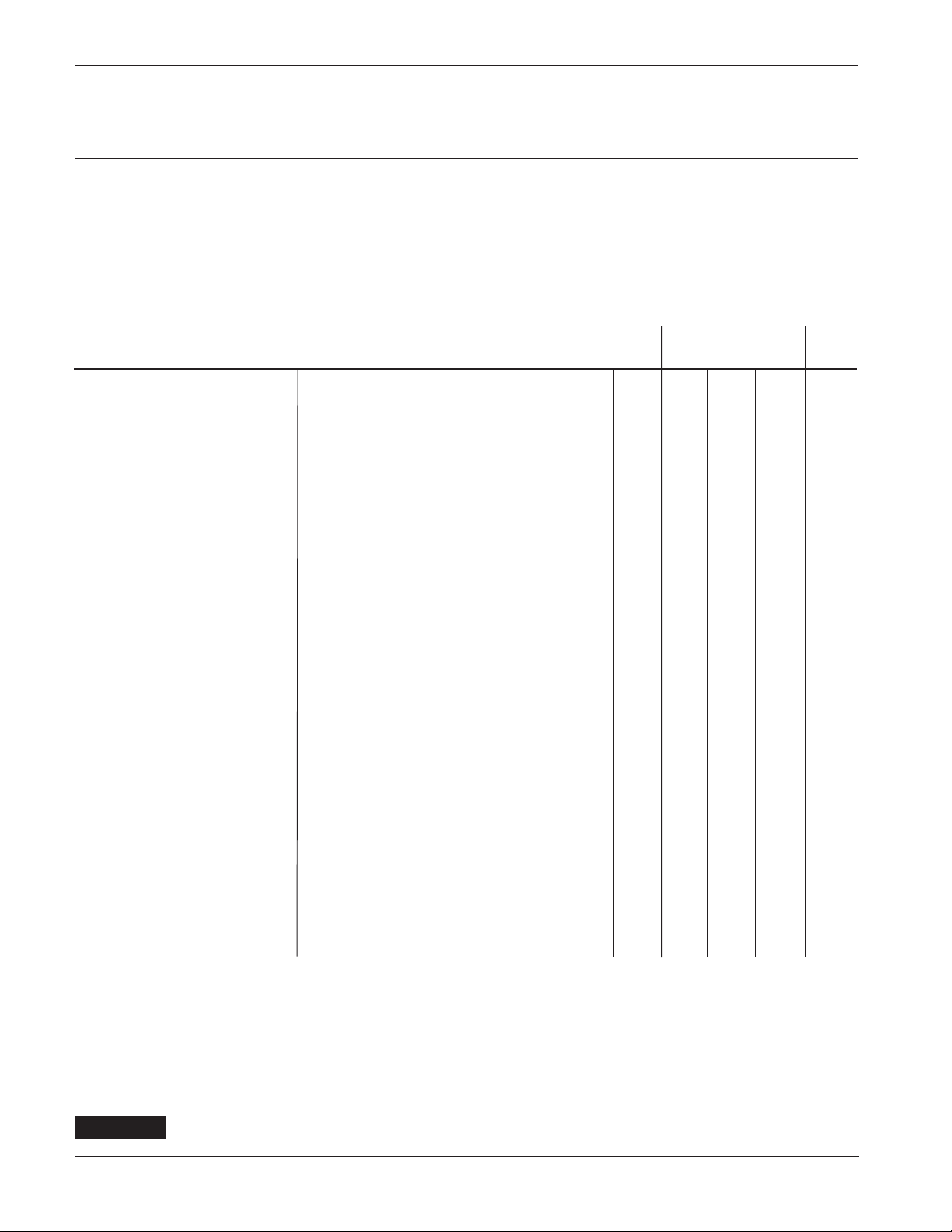

EXTERNAL CONNECTIONS

R

CL

C

C

COMP

2

7

–V

S

12345678910

I

LIM

1

C

330pF

8

R

+V

100Ω

S

NC –V

S

C , C ARE NPO RATED

S

FOR FULL SUPPLY VOLTAGE.

R

TOP VIEW

S

COMP

OUT

PA41

PA42

–IN

R

4

5

C

3

TOP VIEW

6

+IN

–IN +IN

NOTE: PA41 Recommended mounting torque is 4-7 in•lbs

(.45 -.79 N•m)

CAUTION: The use of compressible, thermally conductive

insulators may void warranty.

PHASE

COMPENSATION

Gain C

1 18pF 2.2KΩ

≥10 10pF 2.2KΩ

≥30 3.3pF 2.2KΩ

S

=

CL

I

+V

LIM

S

R

S

100Ω

C

S

330pf

C

C

3

I

LIM

C

C

C

C

R

C

C

C

R

CL

R

C

OUTNC

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

ABSOLUTE MAXIMUM RATINGS

PA41/PA42 • PA41A/PA42A

PA41/PA41A PA42/PA42A

ABSOLUTE MAXIMUM RATINGS

SUPPLY VOLTAGE, +VS to –V

OUTPUT CURRENT, continuous within SOA 60 mA 60 mA

S

OUTPUT CURRENT, peak 120 mA 120 mA

POWER DISSIPATION, continuous @ T

INPUT VOLTAGE, differential ±16 V ±16 V

= 25°C 12W 9W

C

INPUT VOLTAGE, common mode ±V

TEMPERATURE, pin solder – 10 sec 300°C 220°C

TEMPERATURE, junction

2

TEMPERATURE, storage –65 to +150°C –65 to +150°C

TEMPERATURE RANGE, powered (case) –40 to +125°C –40 to +125°C

SPECIFICATIONS

PARAMETER TEST CONDITIONS

1

PA41/PA42 PA41A/PA42A

MIN TYP MAX MIN TYP MAX UNITS

INPUT

OFFSET VOLTAGE, initial 25 40 15 30 mV

OFFSET VOLTAGE, vs. temperature

4, 7

Full temperature range 70 130 40/* 65/* µV/°C

OFFSET VOLTAGE, vs supply 20 32 * * µV/V

OFFSET VOLTAGE, vs time 75 * µV √kh

BIAS CURRENT, initial

BIAS CURRENT, vs supply .2/.5 .5/50 * * pA/V

OFFSET CURRENT, initial

INPUT IMPEDANCE, DC 10

7

7

5/100

50/2000

2.5/100 50/400 * * pA

11

INPUT CAPACITANCE 5 * pF

COMMON MODE, voltage range ±VS–12 * V

COMMON MODE REJECTION, DC VCM = ±90V DC 84 94 * * dB

NOISE, broad band 10kHz BW, RS = 1KΩ 50 * µV RMS

NOISE, low frequency 1-10 Hz 110 * µV p-p

GAIN

OPEN LOOP at 15Hz RL = 5KΩ 94 106 * * dB

BANDWIDTH, open loop 1.6 * MHz

POWER BANDWIDTH CC = 10pf, 280V p-p 26 * kHz

PHASE MARGIN Full temperature range 60 * °

OUTPUT

VOLTAGE SWING IO = 40mA ±VS–12 ±VS–10 ±VS–10

CURRENT, peak

5

120 * mA

CURRENT, continuous 60 * mA

SETTLING TIME to .1% CC = 10pF, 10V step, AV = –10 12 * µs

SLEW RATE CC = OPEN 40 * V/µs

CAPACITIVE LOAD AV = +1 10 * nF

RESISTANCE6, no load RCL = 0 150 * Ω

RESISTANCE6, 20mA load RCL = 0 25 * Ω

POWER SUPPLY

VOLTAGE

3

See Note 3 ±50 ±150 ±175 * * * V

CURRENT, quiescent 1.6 2.0 .9 1.4 1.8 mA

THERMAL

PA41

RESISTANCE, AC junction to case

PA42

RESISTANCE, AC junction to case

PA41

RESISTANCE, DC junction to case

PA42

RESISTANCE, DC junction to case

F > 60Hz 5.4 6.5 * * °C/W

F > 60Hz 7 10 * * °C/W

F < 60Hz 9 10.4 * * °C/W

F < 60Hz 12 14 * * °C/W

PA41 RESISTANCE, junction to air Full temperature range 30 * °C/W

PA42 RESISTANCE, junction to air Full temperature range 55 * °C/W

TEMPERATURE RANGE, case Meets full range specifications –25 +85 * * °C

350V 350V

S

150°C 150°C

SPECIFICATIONS

±V

S

**pA

* Ω

±VS–8.5

V

NOTES: * The specification for PA41A/PA42A is identical to the specification for PA41/PA42 in applicable column to the left.

1. Unless otherwise noted TC = 25°C, CC = 18pF, RC = 2.2KΩ. DC input specifications are ± value given. Power supply voltage is

typical rating.

2. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation

to achieve high MTTF. For guidance, refer to heatsink data sheet.

3. Derate maximum supply voltage .5 V/°C below case temperature of 25°C. No derating is needed above TC = 25°C.

4. Sample tested by wafer to 95%.

5. Guaranteed but not tested.

6. The selected value of RCL must be added to the values given for total output resistance.

7. Specifications separated by / indicate values for the PA41 and PA42 respectively.

CAUTION

APEX MICROTECHNOLOGY CORPORATION • 5980 NORTH SHANNON ROAD • TUCSON, ARIZONA 85741 • USA • APPLICATIONS HOTLINE: 1 (800) 546-2739

The PA41/PA42 is constructed from MOSFET transistors. ESD handling procedures must be observed.

TYPICAL PERFORMANCE

GRAPHS

PA41/PA42 • PA41A/PA42A

15

12

POWER DERATING

T = T

C

T = T

C

9

6

T = T

A

PA41

PA42

3

T = T

A

0

0 25 50 75 100 125

INTERNAL POWER DISSIPATION, P(W)

120

TEMPERATURE, T (°C)

SMALL SIGNAL RESPONSE

100

80

60

CC = 3.3pF

CC = 10pF

40

20

OPEN LOOP GAIN, A(dB)

0

–20

1 100 10M

CC = 18pF

10 1K 10K .1M 1M

FREQUENCY, F (Hz)

140

CURRENT LIMIT

130

120

110

+I

LIM

–I

LIM

100

90

80

NORMALIZED CURRENT LIMIT, (%)

–50 0 100

–25 25 50 75

CASE TEMPERATURE, T (°C)

PHASE RESPONSE

0

–30

–60

CC = 3.3pF

CC = 10pF

CC = 18pF

–90

CC = 18pF

–120

PHASE, (°)ϕ

–150

CC = 3.3pF

–180

–210

10 10K 1M

1 100 .1M 10M

CC = 10pF

1K

FREQUENCY, F (Hz)

60

40

CURRENT LIMIT

+I

LIM

20

0

–20

-I

LIM

–40

CURRENT LIMIT RANGE, I (mA)

125

C

–60

100 200

0 300 400

CURRENT LIMIT RESISTOR, RCL ( )Ω

500

POWER RESPONSE

400

PP

200

O

100

80

60

40

OUTPUT VOLTAGE, V (V )

CC = 18pF

20

10K 20K .2M.1M

30K

50K .3M .5M 1M

FREQUENCY, F (Hz)

RL = 10KΩ

CC = 10pF

CC = 3.3pF

HARMONIC DISTORTION

1.0

AV = 20

.6

= 3.3pf

C

.4

C

= 2K Ω

R

L

.2

.1

VO = 30V

.06

.04

.02

DISTORTION, (%)

.01

.006

.004

.002

100 10K

PP

VO = 180V

VO = 60V

PP

3K 100K

30K200 1K 0

PP

FREQUENCY, F (Hz)

COMMON MODE REJECTION

120

100

80

60

40

20

0

10 10K .1M

1 100 1K 1M

COMMON MODE REJECTION, CMR (dB)

FREQUENCY, F (Hz)

60

50

SLEW RATE

QUIESCENT CURRENT

150

130

40

110

30

20

SLEW RATE, V/µs

10

0

COMPENSATION CAPACITANCE, C

42081612

(pf)

C

POWER SUPPLY REJECTION

120

100

+V

80

60

–V

40

20

0

10 100 1K 10K .1M

11M

POWER SUPPLY REJECTION, PSR (dB)

FREQUENCY, F (Hz)

S

S

90

70

50

100 150 300 350

NORMALIZED QUIESCENT CURRENT, (%)

TOTAL SUPPLY VOLTAGE, V

(V)

OUTPUT VOLTAGE SWING

O

18

– V

S

16

14

12

10

8

6

4

2

25°C +OUT

0

20 120

04060

OUTPUT CURRENT, I

VOLTAGE DROP FROM SUPPLY, V

= 85°C

C

T

= 25°C

C

T

= -25

T

C

200

85°C –OUT

25°C –OUT

–25°C –OUT

–25°C +OUT

250

85

°C

°C +O

80

O

UT

100

(mA)

S

(V)

APEX MICROTECHNOLOGY CORPORATION • TELEPHONE (520) 690-8600 • FAX (520) 888-3329 • ORDERS (520) 690-8601 • EMAIL prodlit@apexmicrotech.com

PA41/PA42 • PA41A/PA42A

OPERATING

CONSIDERATIONS

GENERAL

Please read Application Note 1 "General Operating Considerations" which covers stability, supplies, heat sinking, mounting, current limit, SOA interpretation, and specification interpretation. Visit www.apexmicrotech.com for design tools that

help automate tasks such as calculations for stability, internal

power dissipation, current limit; heat sink selection; Apex’s

complete Application Notes library; Technical Seminar Workbook; and Evaluation Kits.

CURRENT LIMIT

For proper operation the current limit resistor, RCL, must be

connected as shown in the external connection diagram. The

minimum value is 18 ohms, however for optimum reliability the

resistor value should be set as high as possible. The value can

be estimated as follows with the maximum practical value of

500 ohms.

R

3

=

CL

I

LIM

The PA41/42 is externally compensated and performance

can be tailored to the application. Use the graphs of small

signal gain and phase response as well as the graphs for slew

rate and power response as a guide. The compensation

capacitor C

compensation capacitor and associated resistor R

must be rated at 350V working voltage. The

C

must be

C

mounted closely to the amplifier pins to avoid spurious oscillation. An NPO capacitor is recommended for compensation.

SAFE OPERATING AREA (SOA)

The MOSFET output stage of this power operational amplifier has two distinct limitations:

1. The current handling capability of the die metallization.

2. The temperature of the output MOSFETs.

NOTE: The output stage is protected against transient

flyback. However, for protection against sustained, high energy flyback, external fast-recovery diodes should be used.

Use the typical performance graphs as a guide for expected

variations in current limit value with a given RCL and variations

over temperature. The selected value of R

the specified typical value of output resistance to calculate the

total output resistance. Since the load current passes through

R

the value selected also affects the output voltage swing

CL

according to:

VR = IO R

*

where VR is the voltage swing reduction.

When the amplifier is current limiting, there may be small

signal spurious oscillation present during the current limited

portion of the negative half cycle. The frequency of the oscillation is not predictable and depends on the compensation,

gain of the amplifier, and load. The oscillation will cease as the

must be added to

CL

CL

200

120

100

, (mA)

S

50

OR –V

S

40

30

20

10

PA41 SOA

300mS

DC, T

DC, T

C

C

= 125

200mS

DC

= 85

°C

°C

amplifier comes out of current limit.

5

INPUT PROTECTION

The PA41/42 inputs are protected against common mode

voltages up the supply rails and differential voltages up to ±16

volts as well as static discharge. Differential voltages exceeding 16 volts will be clipped by the protection circuitry. However,

if more than a few milliamps of current is available from the

overload source, the protection circuitry could be destroyed.

The protection circuitry includes 300 ohm current limiting

resistors at each input, but this may be insufficient for severe

overloads. It may be necessary to add external resistors to the

application circuit where severe overload conditions are expected. Limiting input current to 1mA will prevent damage.

STABILITY

The PA41/42 has sufficient phase margin when compensated for unity gain to be stable with capacitive loads of at least

10 nF. However, the low pass circuit created by the sumpoint

4

3

OUTPUT CURRENT FROM +V

PULSE CURVES @ 10% DUTY CYCLE MAX

2

10 20 30 50 100 200 300 500

SUPPLY TO OUTPUT DIFFERENTIAL, VS -VO (V)

200

120

100

, (mA)

S

50

OR –V

S

40

30

20

10

PA42 SOA

300mS

DC, T

DC, T

C

= 125

C

= 85

°C

100mS

200mS

DC

°C

(–in) capacitance and the feedback network may add phase

shift and cause instabilities. As a general rule, the sumpoint

load resistance (input and feedback resistors in parallel)

should be 5K ohm or less at low gain settings (up to 10).

Alternatively, use a bypass capacitor across the feedback

resistor. The time constant of the feedback resistor and

bypass capacitor combination should match the time constant

of the sumpoint resistance and sumpoint capacitance.

This data sheet has been carefully checked and is believed to be reliable, however, no responsibility is assumed for possible inaccuracies or omissions. All specifications are subject to change without notice.

PA41/42U REV. G JANUARY 1999 © 1999 Apex Microtechnology Corp.

5

4

OUTPUT CURRENT FROM +V

3

PULSE CURVES @ 10% DUTY CYCLE MAX

2

10 20 30 50 100 200 300 500

SUPPLY TO OUTPUT DIFFERENTIAL, VS -VO (V)

Loading...

Loading...