ANPEC APU0066-002YE-TY, APU0066-002QE-TY, APU0066-001YE-TY, APU0066-001QE-TY Datasheet

16 COM / 40 SEG Driver & Controller for Dot Matrix LCD

Copyright ANPEC Electronics Corp.

Rev. A.07 - FEB., 2002

APU0066

www.anpec.com.tw1

PRELIMINARY

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise

customers to obtain the latest version of relevant information to verify before placing orders.

FEATURES

GENERAL DESCRIPTIONAPPLICATIONS

ORDERING INFORMATION

••

••

• Internal Memory

- Character Generator ROM : 8320 bits

- Character Generator RAM : 512 bit

- Display Data RAM : 80 × 8 bits for 80 digits

••

••

• Power Supply Voltage : 3V/5V ± 10%

••

••

• Supply Voltage for Display : 0 ~ -5V (V

5

)

••

••

• CMOS Process

••

••

• 1/8 duty, 1/11 duty or 1/16 duty : Selectable

- 1/8 duty : 5 × 7dots format 1 line

- 1/1 1 duty: 5 × 10 dots format 1 line

- 1/16 duty : 5 × 7dots format 2 line

••

••

• 80 QFP or Bare Chip Available

••

••

• Display Character Pattern :

- 5 × 7dots format : 192 kinds

- 5 × 10 dots format : 32 kinds

(The special character pattern can be

programmable by Character Generator RAM

directly.)

••

••

• A Customer Character Pattern Can be

Programmable by Mask Option

••

••

• Automatic Power on Reset Function

••

••

• It is Possible to Read Both Character Generator

and Display Data RAM from MPU

••

••

• Character Type Dot Matrix LCD Driver & Con

-troller

••

••

• Internal Driver :16 Common and 40 Segment

Signal Output

••

••

• Display Character Format : 5× 7 dots + Cursor,

5 × 10 dots + Cursor

••

••

• Easy Interface with a 4-bit or 8-bit MPU

The APU0066 is a dot matrix LCD driver & controller

LSI that is fabricated by low power CMOS

technology.

APU0066

ROM Code

Package Type

Handling Code

RO M Code

001 : Standard

002 : Customer

Package Type

Q : QFP

Y : Chip

Handling Code

TY : Tray

E

Copyright ANPEC Electronics Corp.

Rev. A.07 - FEB., 2002

APU0066

www.anpec.com.tw2

PRELIMINARY

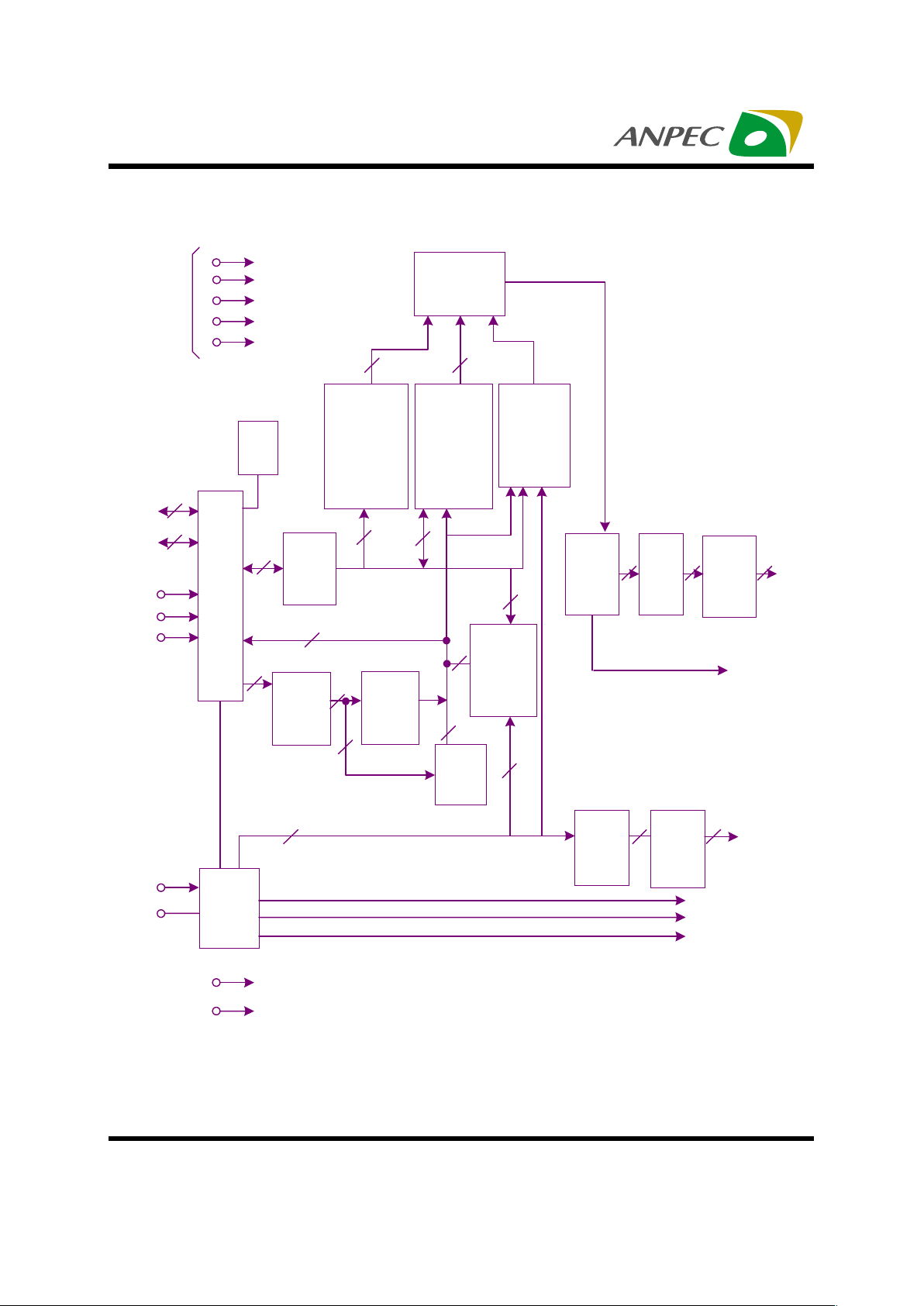

BLOCK DIAGRAM

Paralle / Serial

Data Conversion

Circuit

Cursor

Blink Control

Circuit

Character

Generaotr

RAM

(CG RAM)

512 bits

Character

Generaotr

ROM

(CG ROM)

8320 bits

Data

Register

(DR)

Input

Output

Buffer

Busy

Flag

Instruction

Register

(IR)

Instruction

Decoder

(ID)

Address

Counter

(AC)

Display Data

RAM

(DD RAM)

80 x 8 bits

Timing

Generation

Circuit

16-bit

Shift

Rregister

Common

Signal

Driver

5

4

4

8

8

8

8

7

7

7

8

7

8

7

7

16

16

D

Common

Signal

(C

1

~ C16)

CLK

1

M

V

DD

GND

D

B0 ~ DB

3

D

B4 ~ DB

7

R / W

RS

E

V

1

V

2

V

3

V

4

V

5

Power

Supply

for

LCD

Drive

40-bit

Shift

Rregister

40-bit

Latch

Circuit

Segment

Signal

Driver

Segment

Signal

(S

1

~ S40)

40 40

40

5

CLK

2

OSC

1

OSC

2

Copyright ANPEC Electronics Corp.

Rev. A.07 - FEB., 2002

APU0066

www.anpec.com.tw3

PRELIMINARY

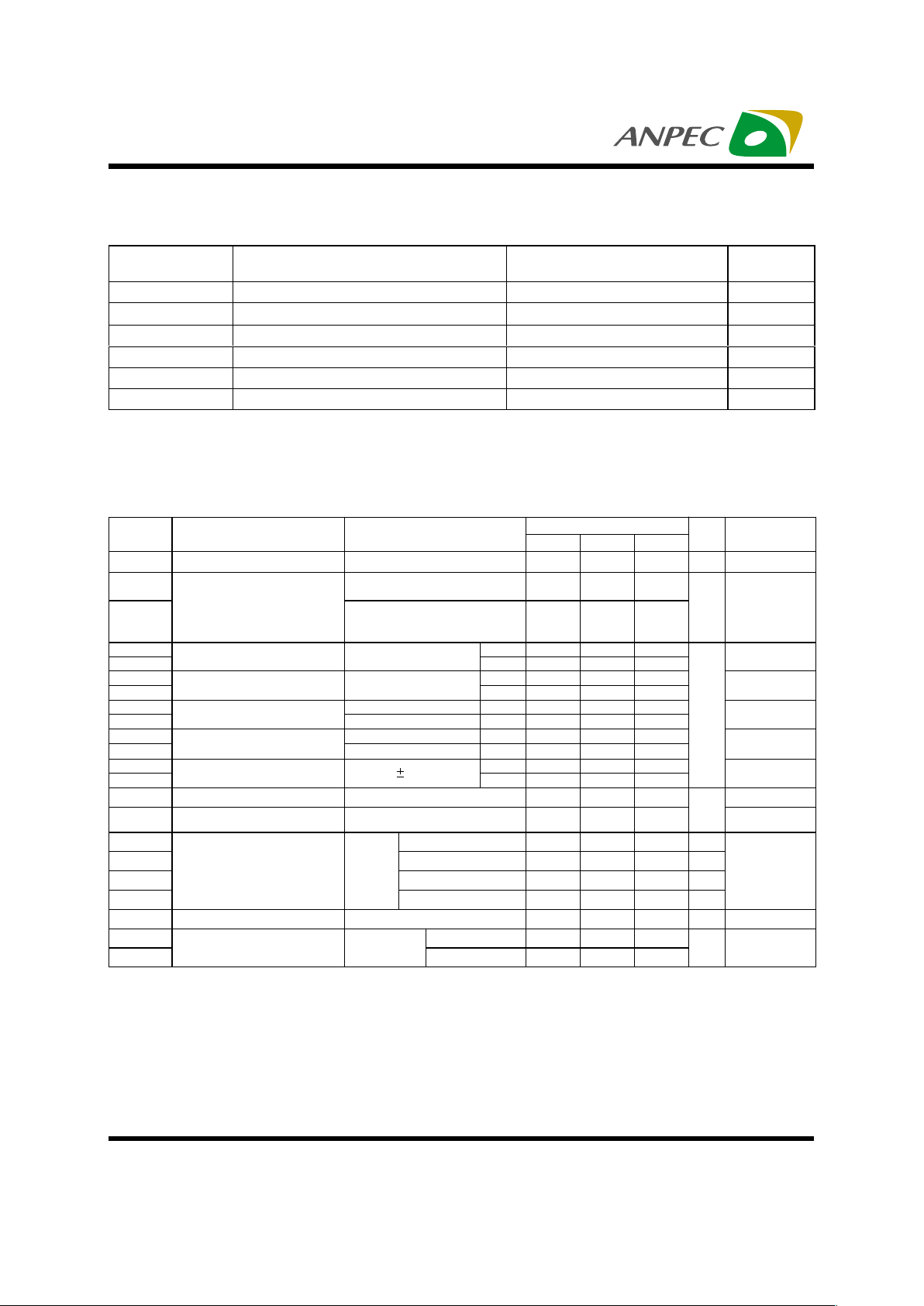

ABSOLUTE MAXIMUM RATINGST

A

= 25

°°

°°

°C

∗ Voltage greater than above may damage to the circuit (VDD ≥ V1 ≥ V2 ≥ V3 ≥ V4 ≥ V5 )

Symbol Parameter Rating Unit

V

DD

Operating Voltage -0.3 ~ +7 V

V

LCD

D riv er Su p p ly Vo lt a g e

V

DD

- 13 .5 ~ V

DD

+ 0.3 V

V

IN

Input Voltage -0.3 ~ V

DD

+ 0.3 V

P

D

Power Dissipation 500 mW

T

OPR

Operating Tem perature -20 to +75 °C

T

STG

Storage Temp eratu re Range -30 to +85 °C

ELECTRICAL CHARACTERISTICS

APU0066

Symbol Parameter Test Conditions

Min. Typ. Max.

Unit

Applicable

Pin

V

DD

Operating Voltage

2.7

3

3.3 V

I

DD1

Ceramic Resonator

F

OSC

= 250KHz

0.3 0.5

I

DD2

Operating Current (∗1) Res is to r O scillatio n

External Clock Operation

F

OSC

= 270KHz

0.17 0.3

mA

V

IH1

High 1.9

V

DD

V

IL1

Input Voltage 1

Low -0.3

0.4

E, DB0 - DB

7

R/W, RS

V

IH2

High 0.7V

DD

V

DD

V

IL2

Input Voltage 2

Low

0.2V

DD

OSC

1

V

OH1

I

OH

= -0.1 mA High 2.0

V

LH1

Output Voltage 1

I

OL

= 0.1mA Low

0.4

DB

0

- DB

7

V

OH2

IO = -40µA

High 0.8V

DD

V

LH2

Output Voltage 2

I

O

= 40µA

Low

0.2V

DD

CLK1, CLK 2.

M, D

VD

COM

COM

1

VD

SEG

Voltage Drop (∗2)

I

O

= 0.05mA

SEG

1.5

V

C

1

~ C

16

S1 ~ S

40

I

LKG

Input Leakage Current V

IN

= 0 or V

DD

-1

1

E

I

IL

Input Low Current V

DD

= 3V (test pull up R) -10 -50 -120

µA

RS, R/W,

DB

0

- DB

7

F

EC

Frequency(∗3)

125 250 350

KHz

Duty

Duty 45 50 55

%

T

R

Rise Time

0.2

µs

T

F

External Clock

Fall Time

0.2

µs

OSC

1

F

OSC

Internal C lock Frequency (∗3) Rf = 75K Ω ± 2%

190 270 350

KHz OSC

1

, OSC

2

V

LCD1

1/5 bias 3

10

V

LCD2

LCD Driving Voltage (∗4)

V

DD

– V

5

1/4 bias 3

10

V

V1 – V

5

Note: ∗1 : The supply current value from V

DD

when the power condition is as follows

V

DD

= 5V, V

SS

= 0V, V5 = -2V (when V

DD

= 5V)

V

DD

= 3V, V

SS

= 0V, V5 = -2V (when V

DD

= 3V)

∗2 : The voltage drop from LCD bias terminals VDD, V1, V4 and V5 to each common terminal (C1 ~ C16). And

also the voltage drop from LCD bias terminals VDD, V2, V3 and V5 to each segment terminal (S1 ~ S80).

∗3 and ∗4 : Refer to oscillator circuit and input the voltage listed in the table below to V1 ~ V5.

DC Characteristics (VDD = 3V ± 10%, V

SS

= 0V, TA = -30 ~ 85°C)

Copyright ANPEC Electronics Corp.

Rev. A.07 - FEB., 2002

APU0066

www.anpec.com.tw4

PRELIMINARY

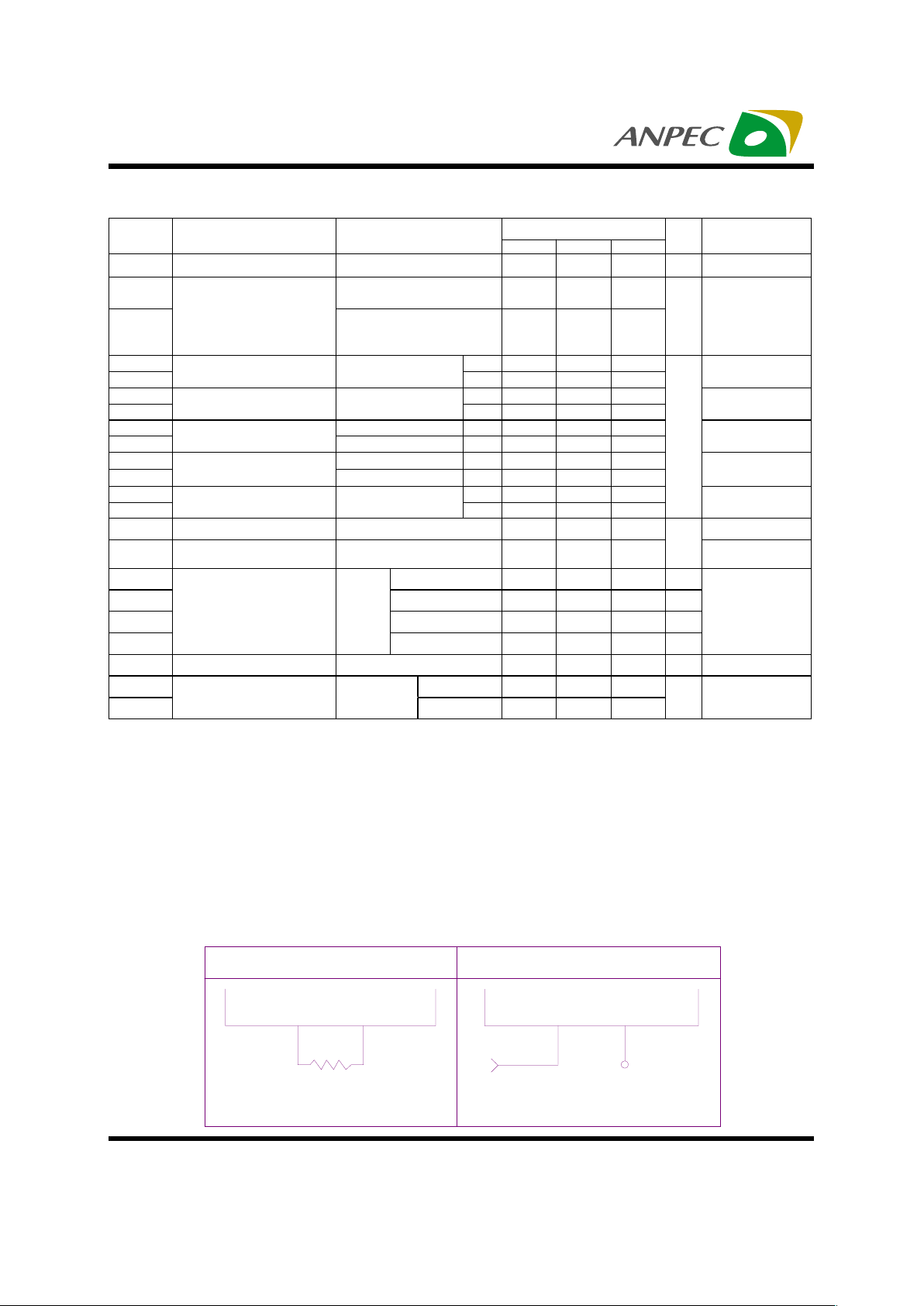

DC Characteristics (VDD = 5V ± 10%, VSS = 0V, TA = -20 ~ 75°C)

APU0066

Symbol Parameter Test Conditions

Min. Typ. Max.

Unit

Applicable Pin

V

DD

Operating Voltage

4.5

5.5 V

I

DD1

Ceramic Resonator

F

OSC

= 250KHz

0.55 0.8

I

DD2

Operating Current (∗1) Resistor Oscillation

External Clock Operati on

F

OSC

= 270KHz

0.35 0.6

mA

V

IH1

High 2.2

V

DD

V

IL1

Input Voltage 1

Low -0.3

0.6

E, DB

0

- DB

7

R/W, RS

V

IH2

High V

DD

- 1

V

DD

V

IL2

Input Voltage 2

Low

-0.2

1

OSC

1

V

OH1

I

OH

= -0.205mA High 2.4

V

LH1

Output Voltage 1

I

OL

= 1.2mA Low

0.4

DB

0

- DB

7

V

OH2

IO = -40µA

High 0.9V

DD

V

LH2

Output Voltage 2

I

O

= 40µA

Low

0.1V

DD

CLK1, CLK2.

M, D

VD

COM

COM

1

VD

SEG

Voltage Drop (∗2) IO = ± 0.1mA

SEG

1

V

C

1

~ C

16

S1 ~ S

40

I

LKG

Input Leakage Current V

IN

= 0 or V

DD

-1

1

E

I

IL

Input Low Current V

DD

= 5V (test pull up R) -50 -125 -250

µ

A

RS, R/W,

DB

0

- DB

7

F

EC

Frequency (∗3)

125 250 350

KHz

Duty

Duty 45 50 55

%

T

R

Rise Time

0.2

µ

s

T

F

External Clock

Fall Time

0.2

µ

s

OSC

1

F

OSC1

Internal Clock Frequenc y (∗3) Rf = 91K

Ω ±

2%

190 270 350

KHz OSC

1

, OSC

2

V

LCD1

1/5 bias 4.6

10

V

LCD2

LCD Driving Voltage (∗4)

V

DD

- V

5

1/4 bias 3

10

V

V

1

– V

5

Note : ∗1 : Applies to the current value flown in terminal VDD when power is input as follows;

V

DD

= 5V, GND = 0V, V1 = 3.4V, V2 =1.8V, V3 = 0.2V, V4 = 1.4V and V5 = -3V.

∗2 : Applied to the voltage drop occurring from terminals VDD , V1, V4 and V5 to each common terminal

(C1 - C16) when 0.1mA is flown in or out to and from all COM and SEG terminals, and also to

voltage drop occurring from terminals VDD ,V2, V3 and V5 to each SEG terminal (S1 ~ S40). When

the output level is at VDD , V1, V2 level , 0.1mA is flown out, while 0.1mA flow in when the output

level is at V3, V4 or V5 level. This occurs when 5V or -5V is input to VDD, V1 and V3 or to V2, V4, and

V5 respectively.

∗3 : Oscillator Circuit

OpenFrequency Input

Resistor Circuit External Clock Circuit

Rf : 91KΩ 2%

OSC

1

R

f

OSC

2

OSC

1

OSC

2

±

Copyright ANPEC Electronics Corp.

Rev. A.07 - FEB., 2002

APU0066

www.anpec.com.tw5

PRELIMINARY

∗4 : Input the voltage listed in the table below to V1 - V

5

∗ V

LCD

is the LCD driving voltage, refer to the initial set of the instruction code.

Duty 1/8, 1/11

1/16

Bias 1/4 1/5

Power Supply

V

1

V

DD

- V

LCD

/ 4 V

DD

- V

LCD

/ 5

V

2

V

DD

- V

LCD

/ 2 V

DD

- 2V

LCD

/ 5

V

3

V

DD

- V

LCD

/ 2 V

DD

- 3V

LCD

/ 5

V

4

V

DD

- 3V

LCD

/ 4 V

DD

- 4V

LCD

/ 5

V

5

V

DD

- V

LCD

V

DD

- V

LCD

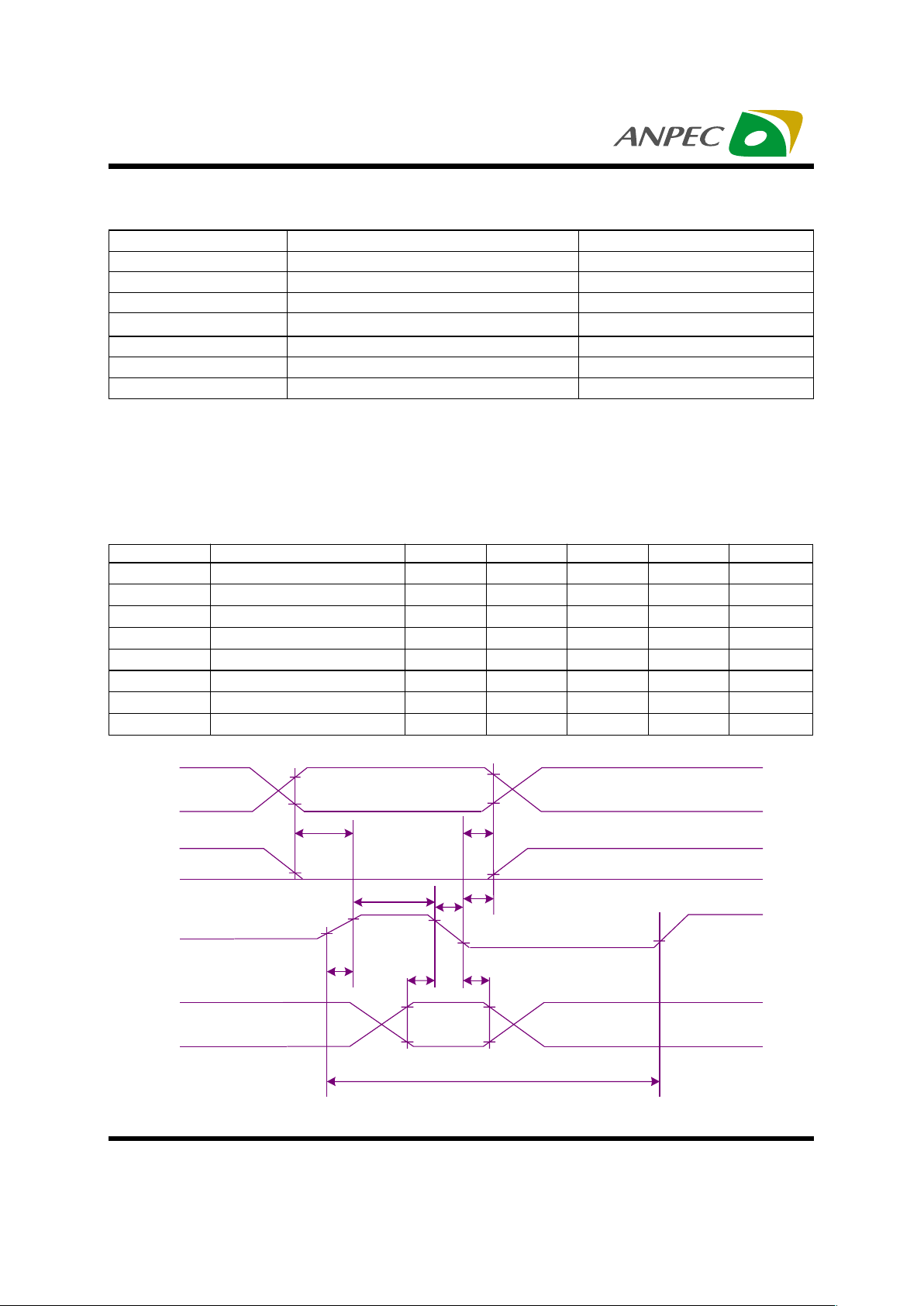

AC Characteristics (VDD = 5V ± 10%, VSS= 0V, TA = -20 ~ +75°C)

1. Write mode

RS

R/W

E

V

IH1

V

IL1

T

SU1

V

IL1

V

IH1

V

IL1

T

H1

T

W

V

IL1

T

H1

T

F

V

IH1

V

IL1

V

IH1

V

IL1

T

R

T

SU2

T

H2

V

IL1

V

IH1

V

IL1

T

C

Vaild Data

V

IH1

V

IL1

DB0 ~ DB

7

Symbol Characteristic Min. Typ. Max. Unit Test Pin

T

C

E Cycle Time 500 - - ns E

T

R

E Rise Time - - 25 ns E

T

F

E Fall Time - - 25 ns E

T

W

E Pulse Width (High, L ow) 220 - - ns E

T

SU1

R/W and RS Set-up Time 40 - - ns R/W, RS

T

H1

R/W and RS Hold Time 10 - - ns R/W,RS

T

SU2

Data Set-up Time 60 - - ns DB0 ~ DB

7

T

H2

Data Hold Time 10 - - ns DB0 ~ DB

7

Loading...

Loading...