Page 1

APL3533

Ultra-Low On-Resistance, 6A Dual Load Switch with Soft Start

Features

• 16mΩ(Typical) On-resistance per Channel

• 6A Continuous Current

• Soft Start Time Programmable by External

Capacitor

• Wide Input Voltage Range (VIN): 0.8V to 5.5V

• Supply Voltage Range (VBIAS): 3V to 5.5V

• Output Discharge when Switch Disabled

• Reverse Current Blocking when Switch Disabled

• Over-Temperature Protection

• Enable Input

• Lead Free and Green Devices Available (RoHS

Compliant)

Applications

• Notebook

• AIO PC

General Description

The APL3533 is an ultra-low on-resistance, dual powerdistribution switch with external soft start control. It integrates two N-channel MOSFETs that can deliver 6A continuous load current each.

The device integrates over-temperature protection. The

over temperature protection function shuts down the Nchannel MOSFET power switch when the junction temperature rises beyond 160oC and will automatically turns

on the power switch when the temperature drops by 40oC.

The device is available in lead free TDFN2x3-14A

packages.

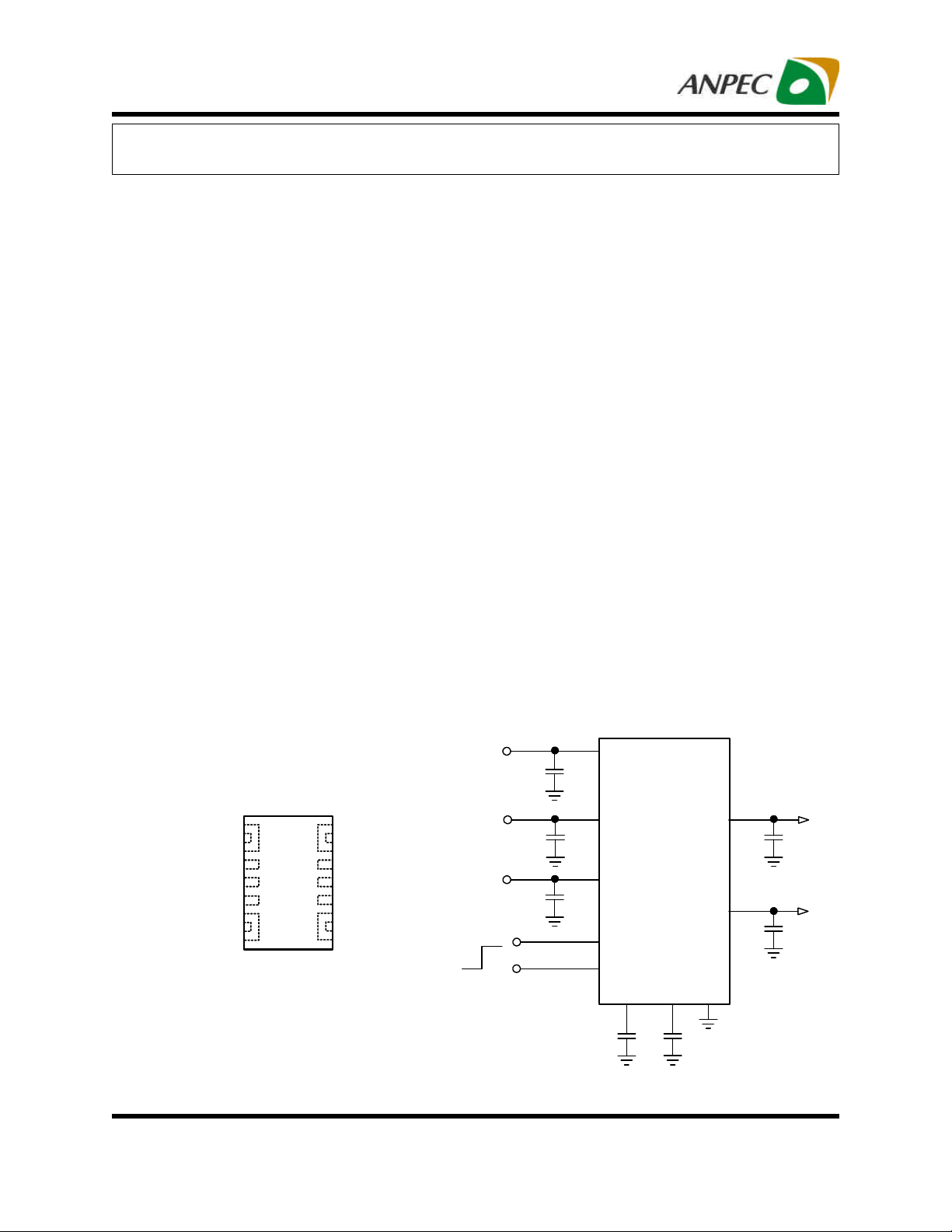

Simplified Application Circuit

V

Off

On

V

V

BIAS

BIAS

IN1

IN2

VIN1 VOUT1

APL3533

VIN2

VOUT2

EN1

EN2

SS1

SS2

GND

www.anpec.com.tw1

V

OUT1

V

OUT2

Pin Configurations

14 VOUT1VIN1 1

VIN1 2

EN1 3

BIAS 4

EN2 5

VIN2 6

VIN2 7

TDFN2x3-14A

(Top View)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and

advise customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

13 VOUT1

12 SS1

11 GND

10 SS2

9 VOUT2

8 VOUT2

Page 2

APL3533

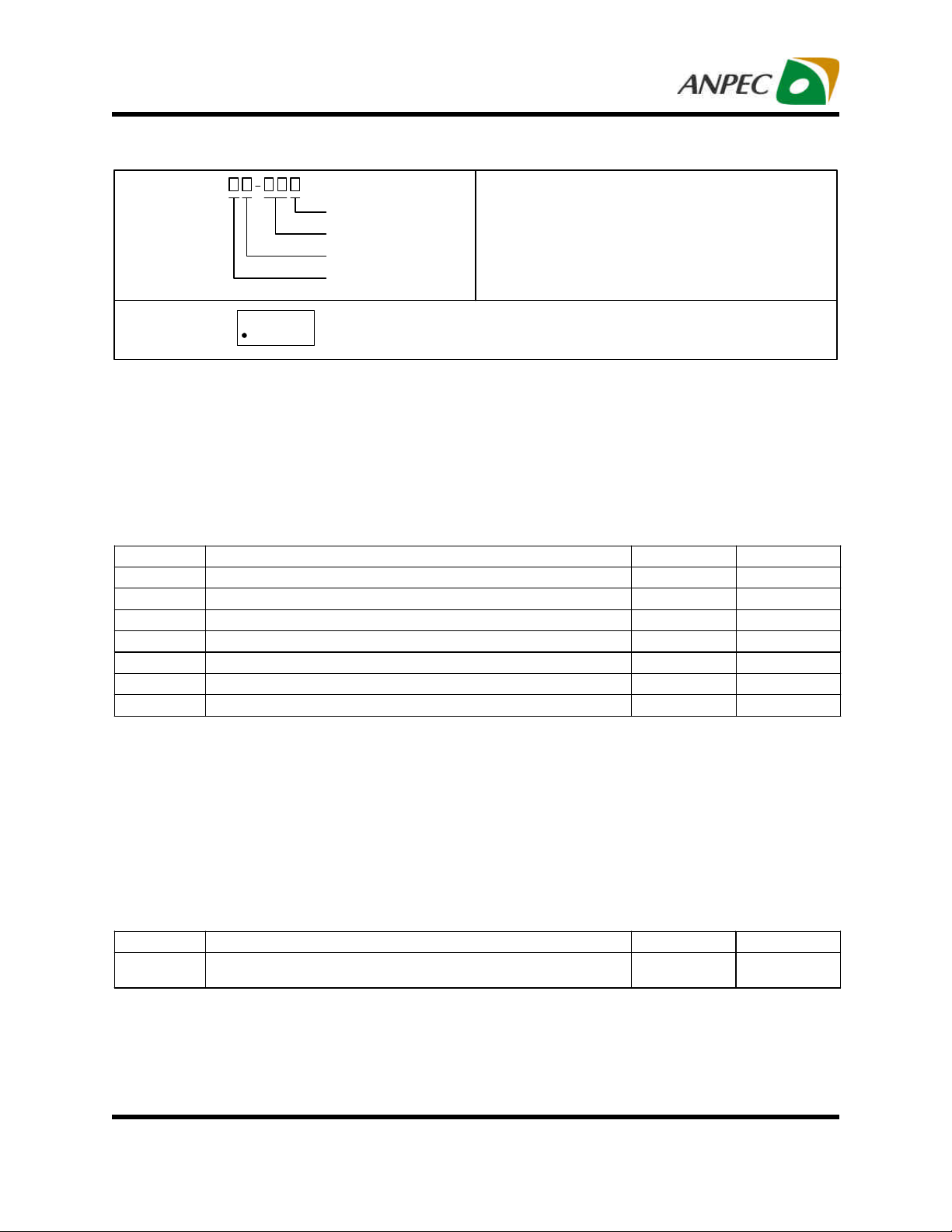

Ordering and Marking Information

APL3533

APL3533

QB:

L3533

XXXXX

Assembly Material

Handling Code

TemperatureRange

Package Code

XXXXX-Date Code

Package Code

QB : TDFN2x3-14A

Operating Ambient Temperature Range

I : -40 to 85oC

Handling Code

TR : Tape & Reel

Assembly Material

G : Halogen and Lead Free Device

Note : ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant)and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

Absolute Maximum Ratings

(Note 1)

Symbol Parameter Rating Unit

V

BAIS to GND Voltage -0.3 ~ 6 V

BIAS

V

, V

VIN1, VIN2 to GND Voltage -0.3 ~ 6 V

IN1

IN2

V

, V

OUT1

V

, V

EN1

TJ Maximum Junction Temperature -40 ~ 150

T

STG

T

SDR

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are

VOUT1, VOUT2 to GND Voltage -0.3 ~ 6 V

OUT2

EN1, EN2 to GND Voltage -0.3 ~ 6 V

EN2

Storage Temperature -65 ~ 150

Maximum Lead Soldering Temperature (10 Seconds) 260

o

C

o

C

o

C

stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

Thermal Characteristics

Symbol Parameter Typical Value

θJA

Note 2: θJA is measured with the component mounted on a high effective thermal conductivity test board in free air.

Junction-to-Ambient Resistance in Free Air

Copyright ANPEC Electronics Corp.

(Note 2)

80

www.anpec.com.tw2

Rev. A.2 - Mar., 2013

Unit

o

C/W

Page 3

APL3533

Recommended Operating Conditions

Symbol

V

BIAS Input Voltage 3.0 ~ 5.5 V

BIAS

V

, V

IN1

VIN1, VIN2 Input Voltage 0.8 ~ 5.5 V

IN2

I

VOUT1 or VOUT2 Output Current (single channel) 0 ~ 6 A

OUT

PD Maximum Power Dissipation, TA=50oC

Parameter Range Unit

(Note4)

0.94 W

(Note 3)

VIH EN1, EN2 Logic High Input Voltage 1.2 ~ 5.5 V

VIL EN1, EN2 Logic Low Input Voltage 0 ~ 0.4 V

TA Ambient Temperature -40 ~ 85

TJ Junction Temperature -40 ~ 125

Note 3 : Refer to the typical application circuit.

Note 4 : Refer to the thermal consideration on page 15.

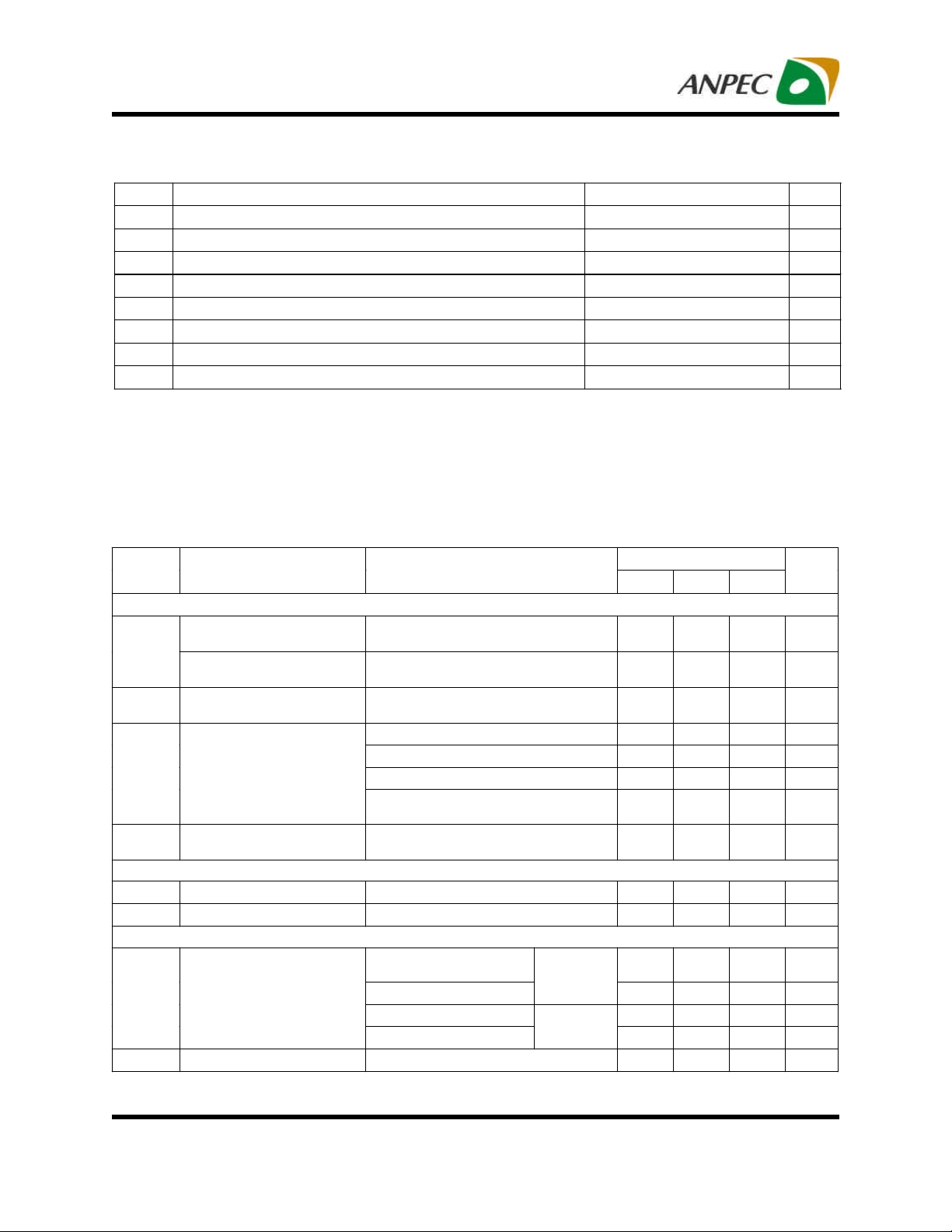

Electrical Characteristics

Unless otherwise specified, these specifications apply over V

Typical values are at TA=25oC.

Symbol

Parameter Test Conditions

SUPPLY CURRENT

I

BIAS

ISD

BIAS Supply Current (both

channels)

BIAS Supply Current (single

channel)

BIAS Supply Current at

Shutdown

No load, V

No load, V

No load, V

No load, V

VIN Off-State Supply Current

I

OFF

(per channel)

No load, V

No load, V

No load, V

Reverse Leakage Current (per

channel)

V

EN1,2

=0V, V

UNDER-VOLTAGE LOCKOUT (UVLO)

Rising BIAS UVLO Threshold V

BIAS UVLO Hysteresis - 0.1 - V

rising 1.9 2.4 2.9 V

BIAS

POWER SWITCH

= V

IN1

IN2

= 0.8V~5.5V, V

EN1

= V

EN2=VBIAS

=5V and TA= -40~85oC.

APL3533

Min. Typ. Max.

=5V =V

BIAS

=5V, V

BIAS

=5V, V

BIAS

=5V, V

BIAS

=5V, V

BIAS

=5V, V

BIAS

=5V, V

BIAS

=0V - 0.1 16

IN1,2

=5V

EN1,2

EN1

EN1,2

EN1,2

EN1,2

EN1,2

EN1,2

=5V, V

=0V

EN2

=0V - - 2

=0V, V

=0V, V

=0V, V

=0V, V

=5V - 0.1 8

IN1,2

=3.3V - 0.1 3

IN1,2

=1.8V - 0.1 2

IN1,2

=0.8V - 0.1 1

IN1,2

-

-

60 90

50 -

o

C

o

C

Unit

µA

µA

µA

µA

µA

µA

µA

µA

I

=200mA, TJ= 25oC

R

DS(ON)

Power Switch On Resistance

VOUT Discharge Resistance V

OUT

I

=200mA, TJ= -40~125oC

OUT

I

=200mA, TJ= 25oC

OUT

I

=200mA, TJ= -40~125oC

OUT

=0V, VOUT1 or VOUT2 force 1V - 150 180

EN1,2

Channel 1

Channel 2

- 16 18

-

- 24

- 16 18

-

- 24

mΩ

mΩ

mΩ

mΩ

Ω

Copyright ANPEC Electronics Corp.

www.anpec.com.tw3

Rev. A.2 - Mar., 2013

Page 4

APL3533

, EN2=low, measured at

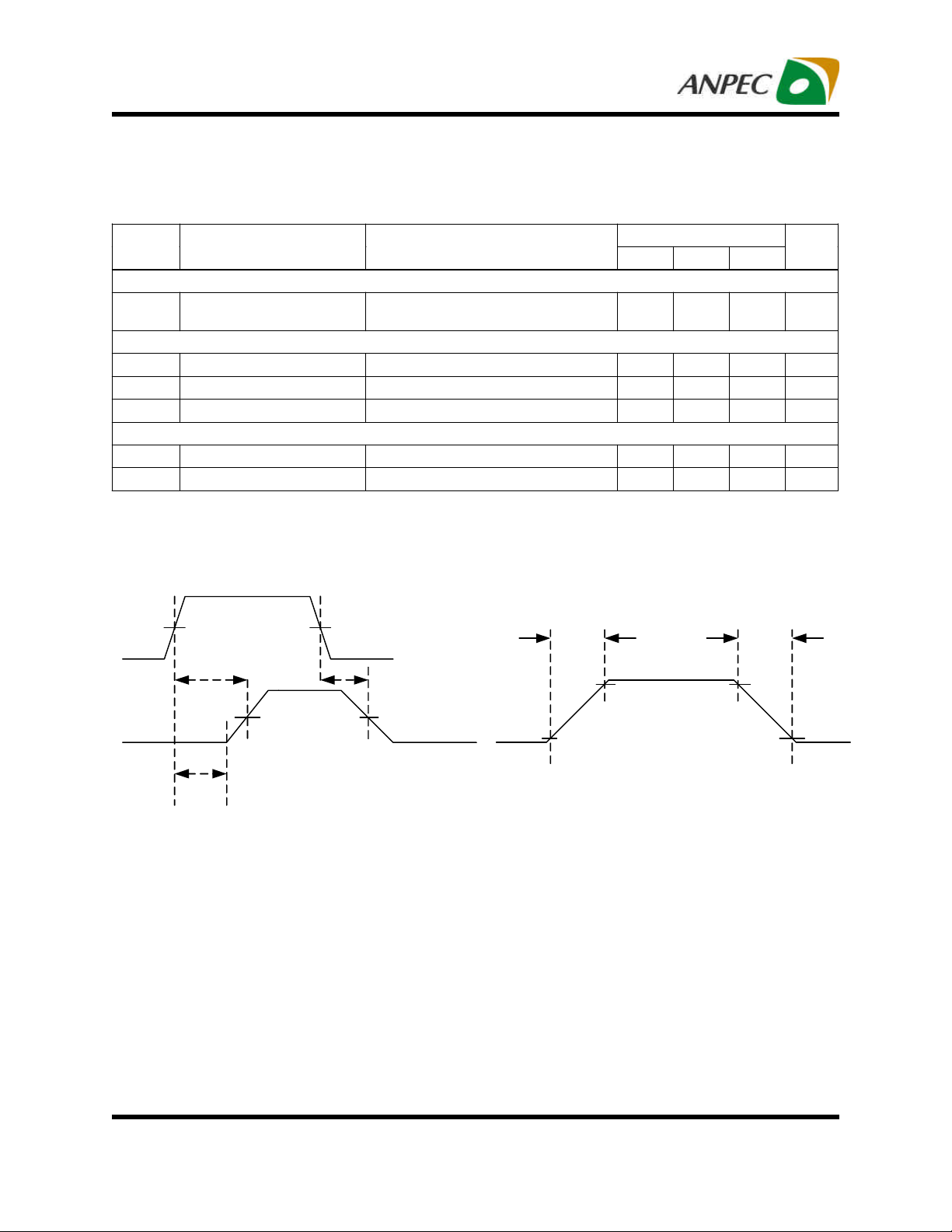

Electrical Characteristics

Unless otherwise specified, these specifications apply over V

Typical values are at TA=25oC.

= V

IN1

IN2

= 0.8V~5.5V, V

EN1

= V

EN2=VBIAS

=5V and TA= -40~85oC.

Symbol

Parameter Test Conditions

SOFT-START CONTROL PIN

SS Discharge Current

EN INPUT PIN

Input Logic High

Input Logic Low

Input Current

OVERT-TEMPERATURE PROTECTION (OTP)

Over-Temperature Threshold

Over-Temperature Hysteresis

Timing Chart

50%50%

V

EN

t

ON

t

OFF

V

=6V, V

SS1,2

SS1 or SS2

TJ rising

EN1,2

=0V

t

R

90% 90%

APL3533

Min. Typ. Max.

- 560 -

1.2 - - V

- - 0.4 V

-

-

1

- 160 -

- 40 -

t

F

Unit

µA

µA

°C

°C

50% 50%

V

OUT

t

D

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

Figure 1. tON/t

V

OUT

, tR/tF Waveforms

OFF

10% 10%

www.anpec.com.tw4

Page 5

APL3533

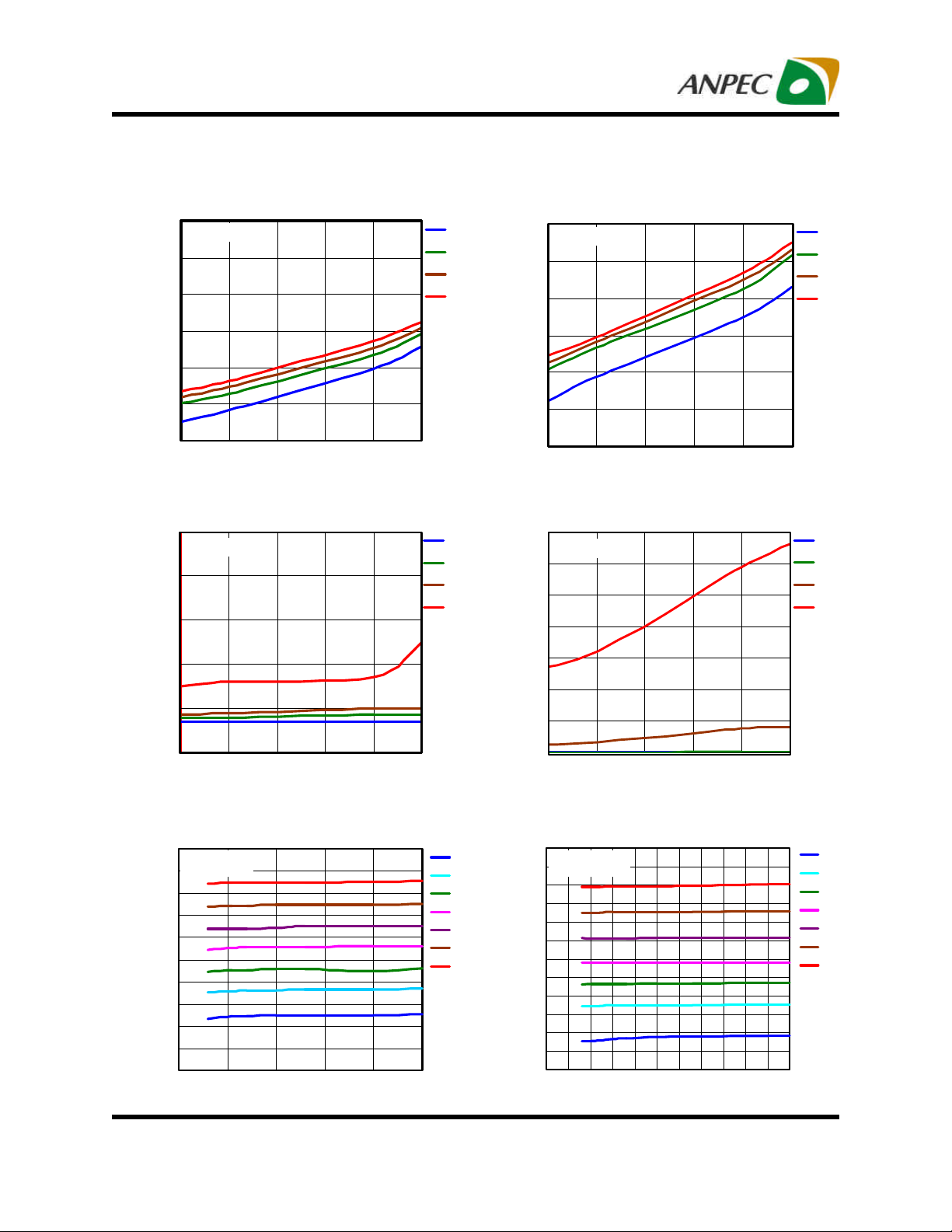

Typical Operating Characteristics

Quiescent Current vs. BIAS

Supply Voltage (Both Channels)

100

V

= V

BIAS

IN

90

(µA)

80

BIAS

70

60

50

Quiescent Current, I

40

3 3.5 4 4.5 5 5.5

BIAS Supply Voltage, V

Shutdown Current vs. BIAS

Supply Voltage (Both Channels)

0.5

V

= V

BIAS

IN

0.4

(µA)

SD

0.3

BIAS

(V)

-40

25

85

125

-40

25

85

125

Quiescent Current vs. BIAS Supply

Voltage (Single Channel)

60

V

= V

BIAS

IN

55

(µA)

BIAS

50

45

40

35

Quiescent Current, I

30

3 3.5 4 4.5 5 5.5

BIAS Supply Voltage, V

Off-Stage Supply Current vs. VIN

Supply Voltage (SINGLE CHANNEL)

14

V

= 5.5V

BIAS

(µA)

12

OFF

10

8

BIAS

-40

25

85

125

(V)

-40

25

85

125

0.2

0.1

Quiescent Current, I

0

3 3.5 4 4.5 5 5.5

BIAS Supply Voltage, V

Switch On Resistance vs. VIN

Supply Voltage

32

V

= 3 V

BIAS

30

(mΩ)

28

26

DS(ON)

24

22

20

18

16

14

Switch On Resistance, R

12

0.5 1 1.5 2 2.5 3

VIN Supply Voltage, VIN (V)

BIAS

(V)

-40

0

25

50

75

100

125

6

4

2

Off-Stage Supply Current,I

0

3 3.5 4 4.5 5 5.5

VIN Supply Voltage, VIN (V)

Switch On Resistance vs. VIN

Supply Voltage

24

V

= 5.5V

BIAS

23

22

(mΩ)

21

DS(ON)

20

19

18

17

16

15

14

13

Switch On Resistance, R

12

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5

VIN Supply Voltage, VIN (V)

-40

0

25

50

75

100

125

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw5

Page 6

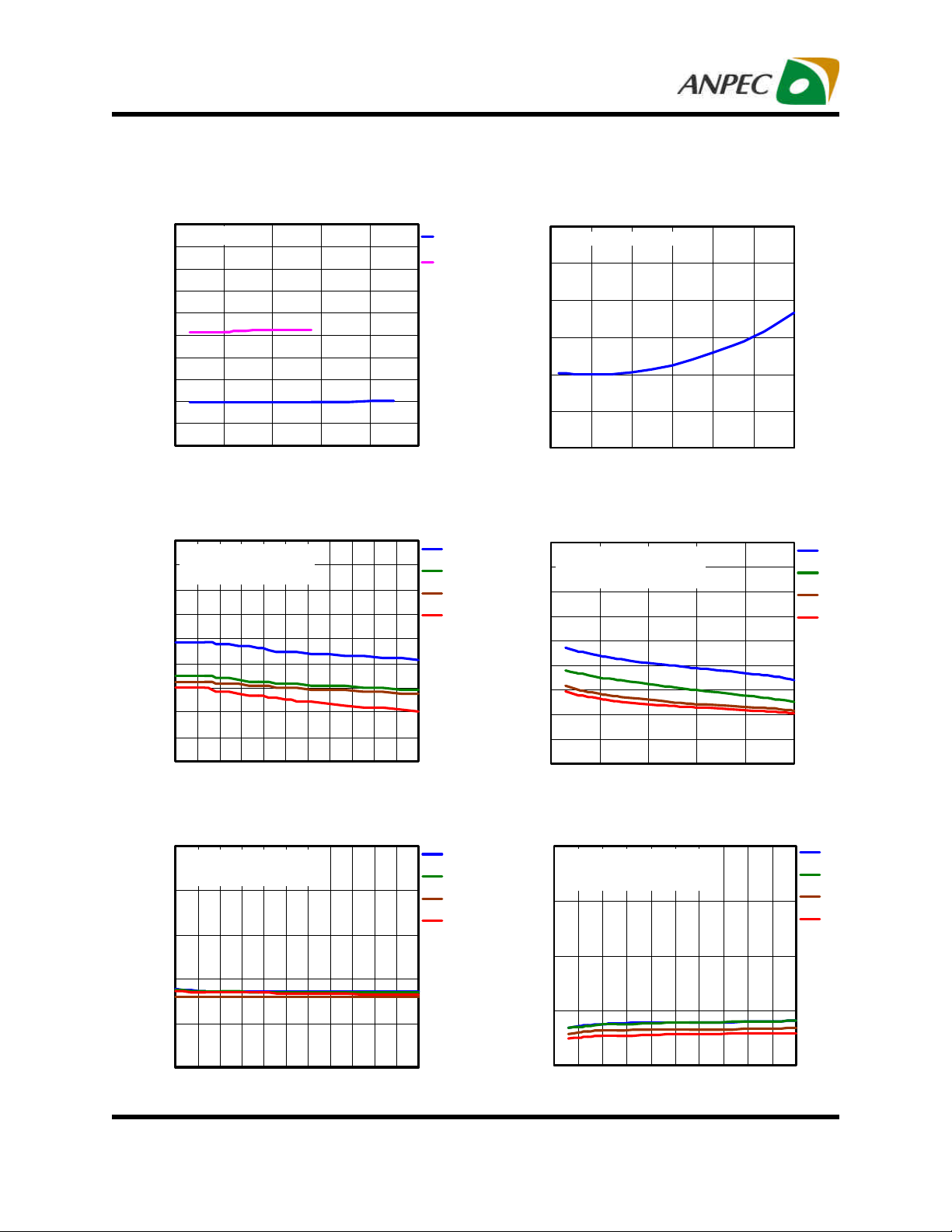

APL3533

Typical Operating Characteristics

Switch On Resistance vs. VIN

Supply Voltage

24

TJ=25°C

23

(mΩ)

22

21

DS(ON)

20

19

18

17

16

15

Switch On Resistance, R

14

0.5 1.5 2.5 3.5 4.5 5.5

VIN Supply Voltage, VIN (V)

Turn On Delay Time vs. VIN

Supply Voltage

500

V

= 3V, RL = 10 Ω

BIAS

450

CSS= 1nF, C

400

(µs)

D

350

300

250

200

150

Turn On Delay Time, t

100

50

0.8 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0

= 0.1µF

OUT

VIN Supply Voltage, VIN (V)

Switch On Resistance vs. Output

Current

V

=5V

BIAS

V

=3.3V

BIAS

20

V

= 5V, VIN= 5V, TJ = 25°C

BIAS

19

(mΩ)

DS(ON)

18

17

16

15

Switch On Resistance, R

14

0 1 2 3 4

Output Current, I

OUT

(A)

6

5

Turn On Delay Time vs. VIN Supply

Voltage

-40

25

85

125

500

V

= 5.5V, CSS= 1nF,

BIAS

450

R

= 10Ω, C

OUT

400

(µs)

D

350

300

250

200

150

Turn On Delay Time, t

100

50

0.5 1.5 2.5 3.5 4.5 5.5

OUT

= 0.1µF

VIN Supply Voltage, VIN (V)

-40

25

85

125

Falling Time vs. VIN Supply Voltage

5

V

= 3V, RL = 10 Ω

BIAS

CSS= 1nF, C

4

(µs)

F

3

2

Falling Time, t

1

0

0.8 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

= 0.1µF

OUT

VIN Supply Voltage, VIN (V)

-40

25

85

125

Falling Time vs. VIN Supply Voltage

5

V

= 5.5V, Css = 1nF,

BIAS

R

= 10Ω, C

OUT

4

(µs)

F

3

Falling Time, t

2

1

0.5 1 1.5 2 2 .5 3 3.5 4 4.5 5 5.5

VIN Supply Voltage, VIN (V)

OUT

= 0.1 µF

-40

25

85

125

www.anpec.com.tw6

Page 7

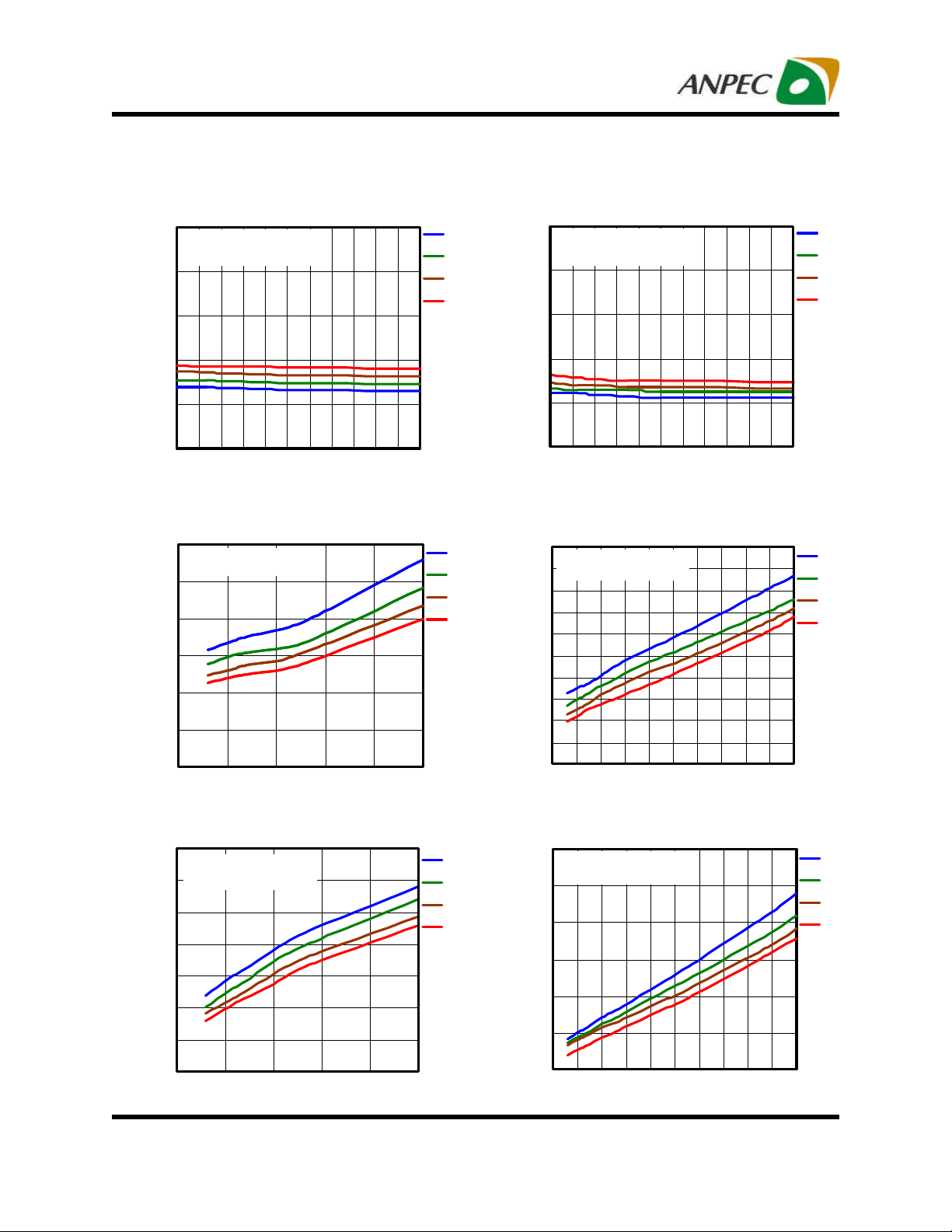

APL3533

Typical Operating Characteristics

Turn Off Time vs. VIN Supply

Voltage

5

V

= 3V, RL = 10Ω

BIAS

CSS= 1 nF, C

4

OUT

= 0.1µF

(µs)

OFF

3

2

Turn Off Time, t

1

0

0.8 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0

VIN Supply Voltage, VIN (V)

Turn On Time vs. VIN Supply

Voltage

1200

V

= 3V, RL = 10Ω

BIAS

CSS= 1nF, C

1000

(µs)

800

ON

600

400

Turn On Time, t

200

0

0.5 1.0 1.5 2.0 2.5 3.0

= 0.1µF

OUT

VIN Supply Voltage, VIN (V)

-40

25

85

125

-40

25

85

125

Turn Off Time vs. VIN Supply

Voltage

5

V

= 5.5V, RL = 10Ω

BIAS

CSS= 1nF, C

4

OUT

= 0.1µF

(µs)

OFF

3

2

Turn Off Time, t

1

0

0.8 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 2.8 3.0

VIN Supply Voltage, VIN (V)

Turn On Time vs. VIN Supply

Voltage

2000

V

= 5.5V, RL = 10Ω

1800

1600

(µs)

1400

ON

1200

1000

Turn On Time, t

BIAS

CSS= 1nF, C

800

600

400

200

0

0.5 1 .0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

OUT

= 0.1µF

VIN Supply Voltage, VIN (V)

-40

25

85

125

-40

25

85

125

Rising Time vs. VIN Supply Voltage

1400

1200

1000

(µs)

R

Rising Time, t

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

V

= 3V, RL = 10Ω

BIAS

CSS= 1 nF, C

800

600

400

200

0

0.5 1.0 1.5 2.0 2.5 3.0

OUT

= 0.1µF

VIN Supply Voltage, VIN (V)

-40

25

85

125

Rising Time vs. VIN Supply Voltage

3000

V

= 5.5V, RL = 10Ω

BIAS

CSS= 1nF, C

2500

2000

(µs)

R

1500

1000

OUT

= 0.1µF

Rising Time, t

500

0

0.5

1.0 1.5 2.0 2.5

3.0 3.5 4.0

4.5 5.0 5.5

VIN Supply Voltage, VIN (V)

www.anpec.com.tw7

-40

25

85

125

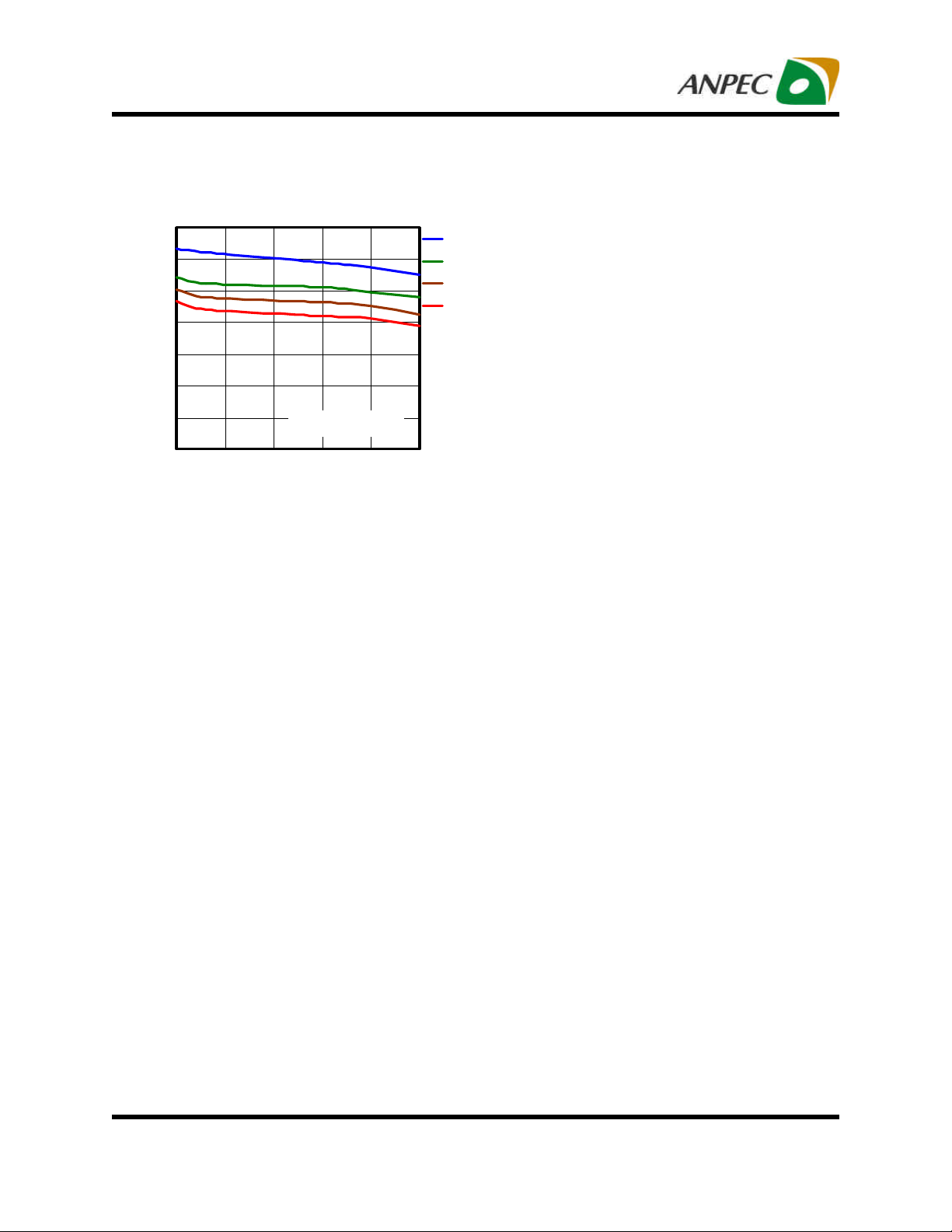

Page 8

APL3533

Typical Operating Characteristics

Rising Time vs. BIAS Supply

Voltage

1600

1400

1200

(µs)

R

1000

800

600

Rising Time, t

-40

25

85

125

400

200

3 3.5

BIAS Supply Voltage, V

VIN = 3V, RL = 10Ω

CSS = 1nF, COUT = 0.1µF

4 4.5 5 5.5

BIAS

(V)

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw8

Page 9

APL3533

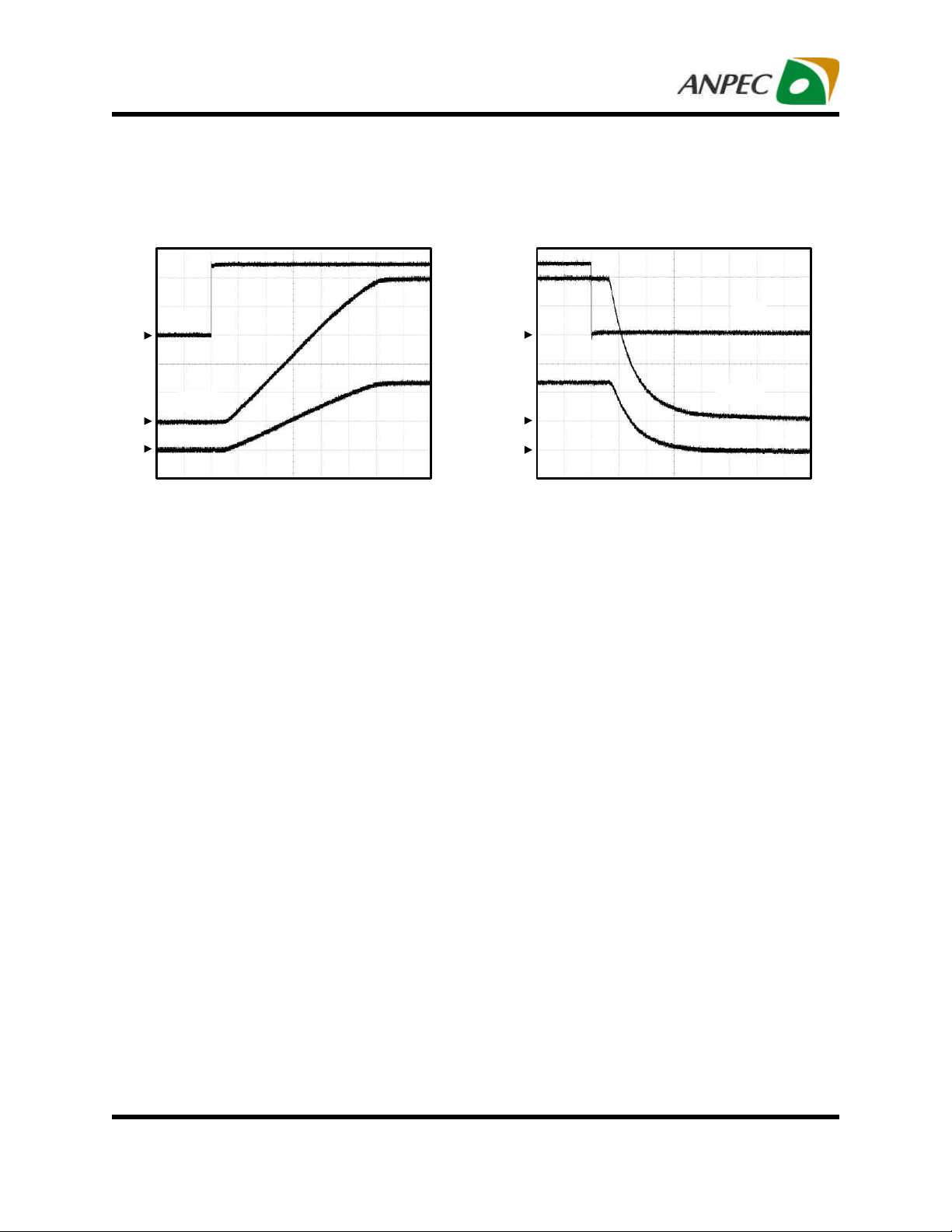

Operating Waveforms

Refer to the typical application circuit. TA= 25oC unless otherwise specified.

V

EN

1

2

V

OUT

I

OUT

3

V

=3V, VIN=0.8V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

CH3: I

, 200mV/Div, DC

OUT

, 50 mA/Div, DC

OUT

TIME: 200µs/Div

Enable

Enable

1

2

3

V

=3V, VIN=0.8V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

CH3: I

, 200mV/Div, DC

OUT

, 50mA/Div, DC

OUT

TIME: 1µs/Div

Shutdown

Shutdown

V

EN

V

OUT

I

OUT

V

EN

1

V

OUT

2

I

OUT

3

V

=3V, VIN=0.8V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

CH3: I

, 200mV/Div, DC

OUT

, 50mA/Div, DC

OUT

TIME: 200µs/Div

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

1

2

3

V

=3V, VIN=0.8V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

CH3: I

, 200mV/Div, DC

OUT

, 50mA/Div, DC

OUT

TIME: 1µs /Div

V

EN

V

OUT

I

OUT

www.anpec.com.tw9

Page 10

APL3533

Operating Waveforms

Refer to the typical application circuit. TA= 25oC unless otherwise specified.

V

1

2

3

EN

V

OUT

I

OUT

V

=5V, VIN=5V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

OUT

CH3: I

, 200mA/Div, DC

OUT

TIME: 500µs/Div

Enable

, 1V/Div, DC

1

2

3

V

=5V, VIN=5V

BIAS

C

=0.1µF, CSS=1nF, RL=10Ω

OUT

CH1: VEN, 2V/Div, DC

CH2: V

OUT

CH3: I

, 200mA/Div, DC

OUT

Shutdown

, 1V/Div, DC

IOUT

V

EN

V

OUT

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw10

Page 11

APL3533

Pin Description

PIN

NO. NAME

1 VIN1

2 VIN1

3 EN1 Enable input of switch 1. Logic high turns on switch 1. The EN1 pin cannot be left floating.

4 BIAS Bias voltage input pin for internal control circuitry.

5 EN2 Enable input of switch 2. Logic high turns on switch 2. The EN2 pin cannot be left floating.

6 VIN2

7 VIN2

8 VOUT2

9 VOUT2

10 SS2

11 GND Ground pin of the circuitry. All voltage levels are measured with respect to this pin.

12 SS1

13 VOUT1

14 VOUT1

Power supply Input of switch 1. Connect this pin to an external DC supply.

Power supply Input of switch 2. Connect this pin to an external DC supply.

Switch 2 output.

Soft start control of switch 2. A capacitor from this pin to ground sets the VOUT2’s rise slew

rate.

Soft start control of switch 1. A capacitor from this pin to ground sets the VOUT1’s rise slew

rate.

Switch 1 output.

FUNCTION

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw11

Page 12

APL3533

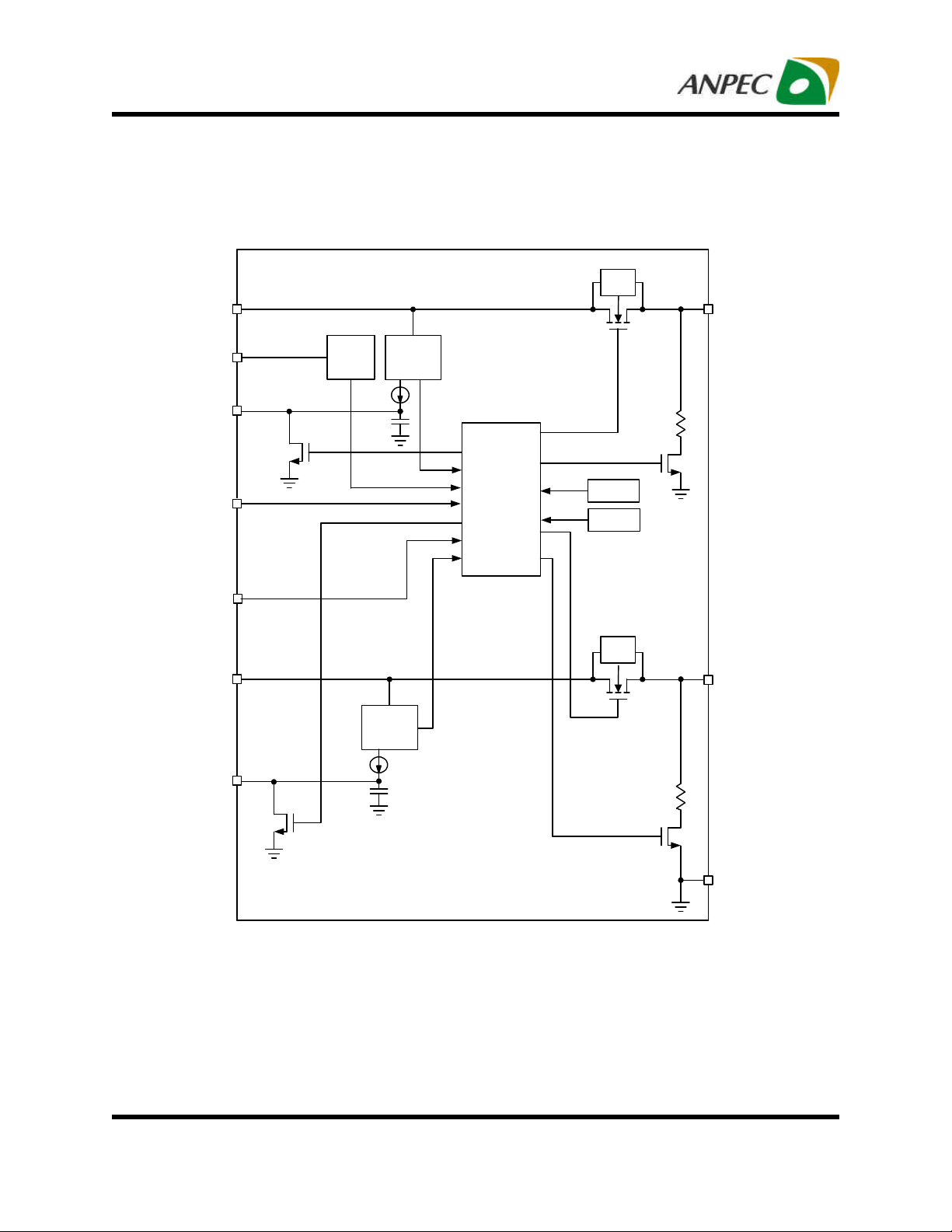

Block Diagram

VIN1

Bulk

Select

VOUT1

BIAS

SS1

EN1

EN2

VIN2

SS2

UVLO

Charge

Pump

Charge

Pump

Control

Logic

OTP1

OTP2

Bulk

Select

VOUT2

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

GND

www.anpec.com.tw12

Page 13

APL3533

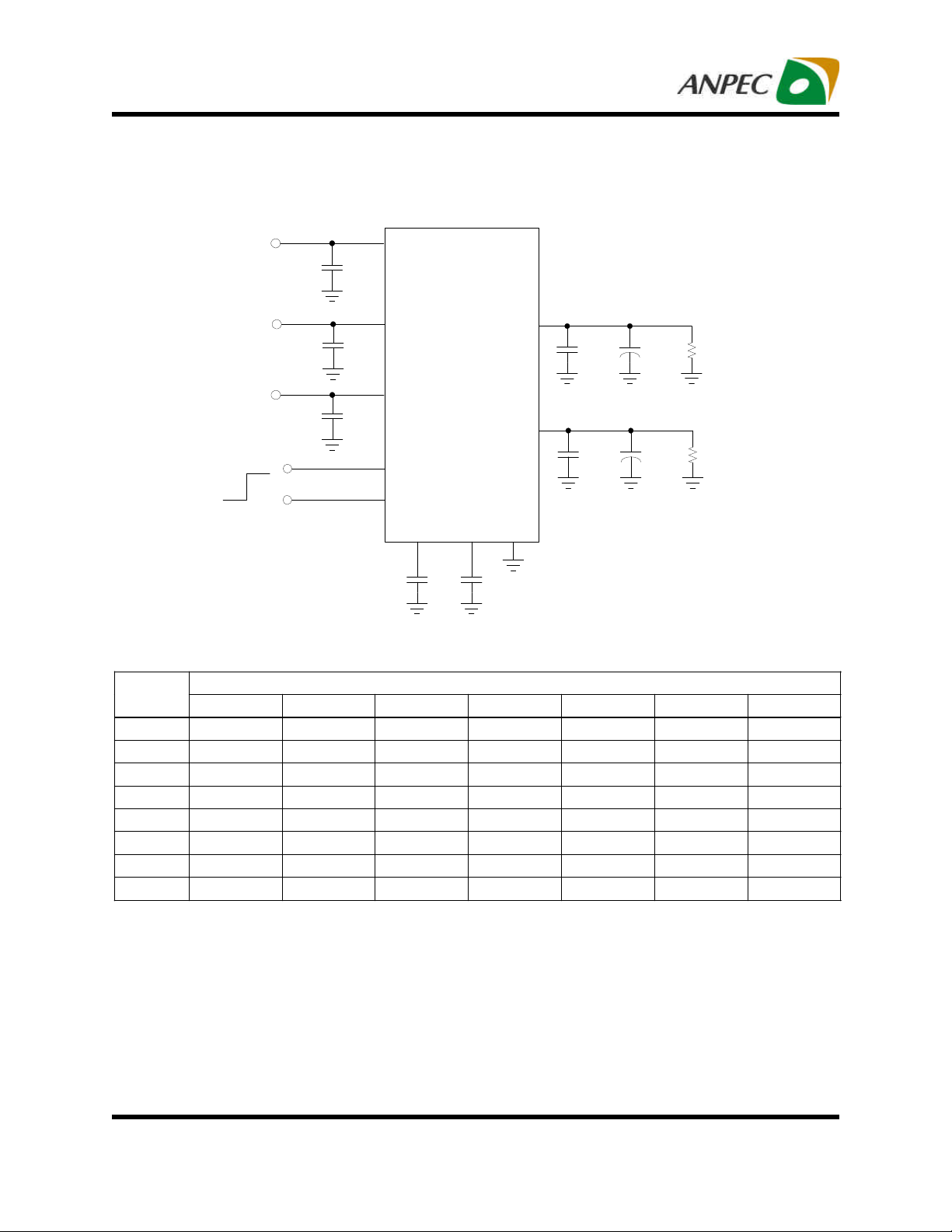

Typical Application Circuit

V

Off

On

V

BIAS

V

C

BIAS

0.1µF

IN1

C

IN1

1µF

IN2

C

IN2

1µF

4

1, 2

VIN1 VOUT1

6, 7

VIN2

3

EN1

5

EN2

BIAS

APL3533

VOUT2

13, 14

8 , 9

C

OUT1

0.1µF

C

OUT2

0.1µF

C

L1

150µF

C

L2

150

µF

R

R

LOAD1

LOAD2

SS2

GND

12

C

BIAS

10

SS1

=5V, CL=0.1µF, CIN=1µF, RL=10Ω, Typical values are at TA=25°C

11

C

SS2

CSS(pF)

Soft-Start Time (µs) 10% to 90%, V

VIN=5V VIN=3.3V

SS1

VIN=1.8V VIN=1.5V VIN=1.2V VIN=1.05V VIN=0.8V

0 112 73 53 49 45 42 38

220 492 322 197 170 146 132 128

330 685 450 270 230 198 180 145

470 911 598 355 307 263 233 188

1000 2030 1280 749 635 538 470 388

2200 4360 2740 1574 1336 1118 1014 797

4700 8780 5540 3218 2696 2289 2037 1624

10000 19060 12011 6862 5700 4806 4301 3410

Note: The table Contains soft-start time values measured on a typical device. The soft-start times shown are only valid for the powerup sequence where VIN and V

are already in steady state condition, and EN pin is asserted high.

BIAS

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw13

Page 14

APL3533

Function Description

VIN Under-voltage Lockout (UVLO)

A under-voltage lockout (UVLO) circuit monitors the VBIAS

pins voltage to prevent wrong logic controls. The UVLO

function initiates a soft-start process after the BIAS supply voltages exceed rising UVLO voltage threshold during powering on.

Power Switch

The power switch is an N-channel MOSFET with a ultralow R

MOSFET prevents a reverse current flowing from the VOUT

back to VIN. When IC is in UVLO state, the internal parasitic diodes connected from VOUT to VIN will be forward

biased.

Soft-start

The APL3533 Provides an adjustable soft-start circuitry

to control rise rate of the output voltage and limit the current surge during start-up. The soft-start time is set with a

capacitor from the SS pin to the ground.

. When IC is in shutdown state (V

DS(ON)

EN1,2

=0V), the

Enable Control

The APL3533 has a dedicated enable pin (EN). A logic

low signal applied to this pin shuts down the output. Following a shutdown, a logic high signal re-enables the

output through initiation of a new soft-start cycle.

Over-Temperature Protection (OTP)

When the junction temperature exceeds 160oC, the internal thermal sense circuit turns off the power FET and

allows the device to cool down. When the device’s junction temperature cools by 40oC, the internal thermal

sense circuit will enable the device, resulting in a pulsed

output during continuous thermal protection. Thermal

protection is designed to protect the IC in the event of

over temperature conditions. For normal operation, the

junction temperature cannot exceed TJ=+125oC.

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw14

Page 15

APL3533

Application Information

Power Sequencing

V

BIAS

V

, V

IN1

IN2

V

, V

EN1

EN2

V

, V

OUT1

OUT2

V

, V

EN1

EN2

V

, V

OUT1

OUT2

V

, V

IN1

IN2

V

BIAS

Figure 2. APL3533 Power Sequencing Diagram

The APL3533 has a built-in reverse current blocking circuit to prevent a reverse current flowing through the body

diode of power switch from the VOUT back VIN pin when

power switch disabled. The reverse current blocking circuit is not active before V

is ready. When IC is in UVLO

BIAS

state, the internal parasitic diodes of power switch connected from VOUT to VIN will be forward biased.

Otherwise, VOUT should not be higher than VBIAS, and

VBIAS must be higher than the voltage of any other input

pin, the reason is that the internal parasitic diodes connected from VOUT to VBIAS will be forward biased.

Capacitor Selection

The APL3533 requires proper input capacitors to supply

current surge during stepping load transients to prevent

the input voltage rail from dropping. Because the parasitic inductor from the voltage sources or other bulk capacitors to the VIN pin limit the slew rate of the surge

currents, more parasitic inductance needs more input

capacitance.

For normal applications (except OTP or output short circuit has occurred), the recommended input capacitance

of VIN is 1µF and output capacitance of VOUT is 0.1µF at

least. Please place the capacitors near the APL3533 as

close as possible.

A bulk output capacitor, placed close to the load, is recommended to support load transient current.

Soft-Start Capacitor

The soft-start capacitor on SS pin can reduce the inrush

current and overshoot of output voltage. The capacitor is

charge to VSS with a constant current source. This results

in a linear charge of the soft-start capacitor and thus the

output voltage.

Thermal Consideration

The APL3533 maximum power dissipation depends on

the differences of the thermal res istance and temperature between junc tion and ambient air. The power dissipation PD across the device is:

PD = (TJ - TA) / θ

JA

where (TJ-TA) is the temperature difference between the

junction and ambient air. θJA is the thermal resistance

between junction and ambient air. Assuming the TA=25°C

and maximum TJ=160°C (typical thermal limit threshold),

the maximum power dissipation is calc ulated as:

P

=(160-25)/80

D(max)

= 1.68(W)

For normal operation, do not exceed the maximum operating junction temperature of TJ = 125°C. The calc ulated

power dissipation should be less than:

PD =(125-25)/80

= 1.25(W)....................................................TA=25oC

PD =(125-85)/80

= 0.5(W)......................................................TA=85oC

The power dissipation depends on operating ambient

temperature for fixed TJ=125oC and thermal resistance

θJA. For APL3533 packages, the Figure 3 of derating

curves allows the designer to see the effect of rising

ambient temperature on the maximum power allowed.

1.3

1.2

1.1

1.0

0.9

0.8

0.7

Power Dissipation (W)

0.6

0.5

-40 -30 -20 -10 0 10 20 30 40 50 60 70 80 90

Ambient Temperature (oC)

Figure 3. Derating Curves for APL3533 Package

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw15

Page 16

APL3533

Application Information

Layout Consideration

The PCB layout should be carefully performed to maximize thermal dissipation and to minimize voltage drop,

droop and EMI. The following guidelines must be

considered:

1. Please place the input capacitors near the VIN pin as

close as possible.

2. Output decoupling capacitors for load must be placed

near the load as close as possible for decoupling high

frequency ripples.

3. Locate APL3533 and output capacitors near the load to

reduce parasitic resistance and inductance for excellent

load transient performance.

4. The negative pins of the input and output capacitors

and the GND pin must be connected to the ground plane

of the load.

5. Keep VIN and VOUT traces as wide and short as

possible.

Recommended Minimum Footprint

0.48 (0.0192)

0.25 (0.01)

0.4 (0.016)

1.3 (0.051)

TDFN2x3-14A

Unit: mm, (Inch)

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw16

Page 17

APL3533

Pack age Information

TDFN2x3-14A

D

Pin 1

D2

A

E

Pin 1 Cornar

e

b

A1

A3

NX

aaa c

SEATING PLANE

S

Y

M

B

O

L

A

A1

A3

b

D

E

e

L

aaa

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

MIN. MAX.

0.70

0.00

0.15 0.25

1.90 2.10

2.90 3.10

0.30

L

TDFN2x3-14A

MILLIMETERS

0.80

0.05

0.11 REF

0.40 BSC 0.016 BSC

0.40

0.08 0.003

INCHES

MIN. MAX.

0.028

0.000

0.004 REF

0.006 0.010

0.075 0.083

0.114 0.122

0.012

0.031

0.002

0.016

www.anpec.com.tw17

Page 18

APL3533

Carrier Tape & R eel Dimensions

OD0

B0

P0

P2

P1

A

E1

F

W

Application

TDFN2x3-14A

K0

SECTION A-A

B

A

H

A0

SECTION B-B

OD1

B

T

A

d

T1

A H T1 C d D W E1 F

178.0±2.00 50 MIN.

8.4+2.00

-0.00

13.0+0.50

-0.20

1.5 MIN. 20.2 MIN. 8.0±0.20 1.75±0.10 3.50±0.05

P0 P1 P2 D0 D1 T A0 B0 K0

4.0±0.10 4.0±0.10 2.0±0.05

1.5+0.10

-0.00

1.5 MIN.

0.25±0.05

2.30±0.20 3.30±0.20 1.00±0.20

Devices Per Unit

Package Type Unit Quantity

TDFN2x3-14A

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

(mm)

Tape & Reel 3000

www.anpec.com.tw18

Page 19

APL3533

Taping Direction Information

TDFN2x3-14A

USER DIRECTION OF FEED

Classification Profile

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw19

Page 20

APL3533

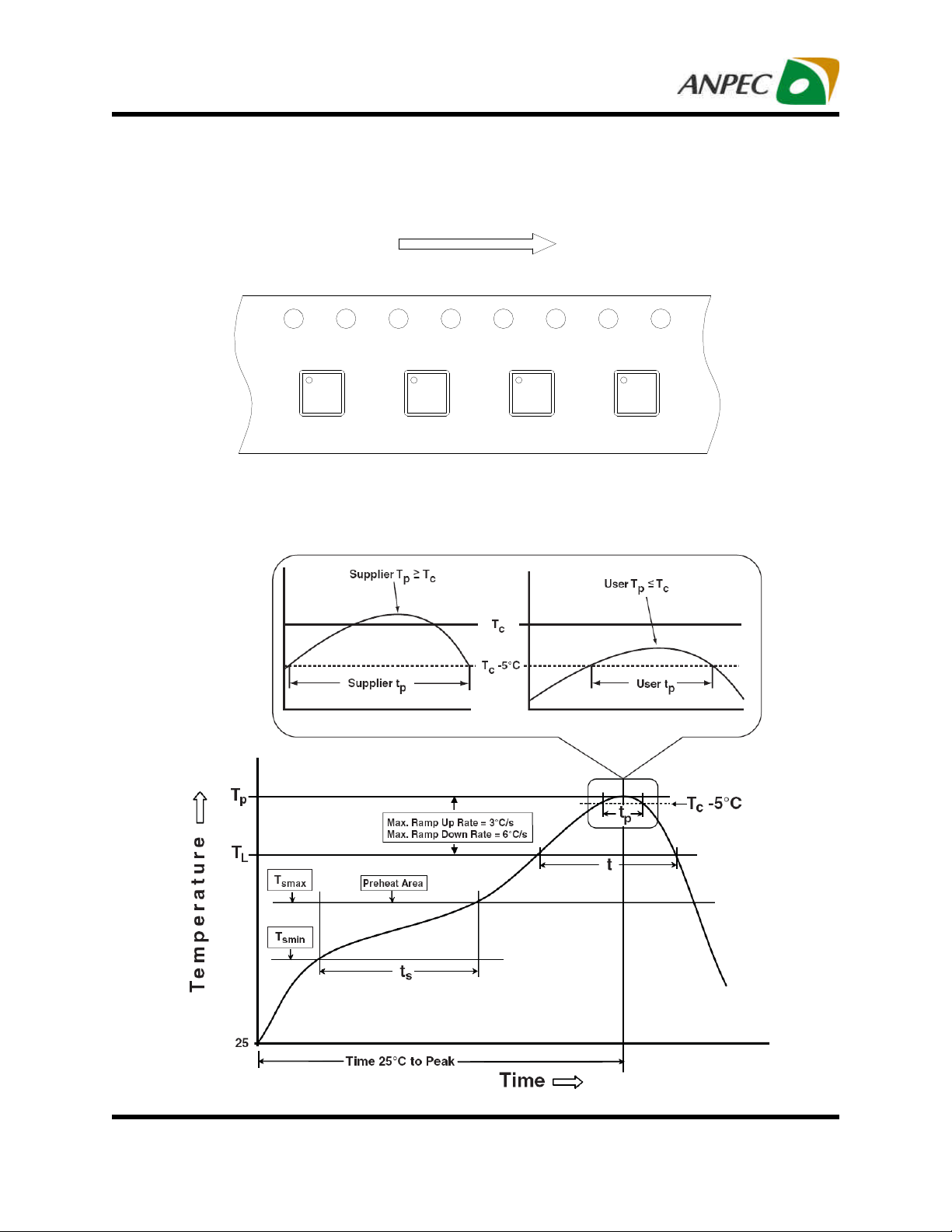

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Preheat & Soak

Temperature min (T

Temperature max (T

Time (T

smin

to T

smax

smin

smax

) (ts)

)

)

Average ramp-up rate

(T

to TP)

smax

Liquidous temperature (TL)

Time at liquidous (tL)

Peak package body Temperature

(Tp)*

Time (tP)** within 5°C of the specified

classification temperature (Tc)

Average ramp-down rate (Tp to T

smax

Time 25°C to peak temperature

See Classification Temp in table 1 See Classification Temp in table 2

)

100 °C

150 °C

60-120 seconds

150 °C

200 °C

60-120 seconds

3 °C/second max. 3°C/second max.

183 °C

60-150 seconds

217 °C

60-150 seconds

20** seconds 30** seconds

6 °C/second max. 6 °C/second max.

6 minutes max. 8 minutes max.

* Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

** Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

Package

Thickness

<2.5 mm

Volume mm

3

Volume mm

<350

235 °C 220 °C

≥350

3

≥2.5 mm 220 °C 220 °C

Table 2. Pb-free Process – Classification Temperatures (Tc)

Package

Thickness

<1.6 mm

1.6 mm – 2.5 mm

Volume mm3

<350

Volume mm3

350-2000

Volume mm3

260 °C 260 °C 260 °C

260 °C 250 °C 245 °C

>2000

≥2.5 mm 250 °C 245 °C 245 °C

Reliability Test Program

Test item Method Description

SOLDERABILITY JESD-22, B102

HOLT JESD-22, A108

PCT JESD-22, A102

TCT JESD-22, A104

HBM MIL-STD-883-3015.7

MM JESD-22, A1 15

Latch-Up JESD 78

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

5 Sec, 245°C

1000 Hrs, Bias @ Tj=125°C

168 Hrs, 100%RH, 2atm, 121°C

500 Cycles, -65°C~150°C

VHBM≧2KV

VMM≧200V

10ms, 1tr≧100mA

www.anpec.com.tw20

Page 21

APL3533

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

Copyright ANPEC Electronics Corp.

Rev. A.2 - Mar., 2013

www.anpec.com.tw21

Page 22

Loading...

Loading...