Evaluation Board User Guide

One Technology Way • P. O . Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel : 781.329.4700 • Fax : 781.461.3113 • www.analog.com

UG-370

Evaluation Board for the ADE7816 Six Current Channels, One Voltage Channel

Energy Metering IC

FEATURES

Evaluation board to implement a fully functional 6-channel

energy meter

Accompanying PC-based LabVIEW software

Easy connection of external transducers via screw terminals

Optically isolated metering components

USB-based PC connection

External voltage reference option available for on-chip

reference evaluation

ADE7816 INTERFACE AND EVALUATION BOARD

GENERAL DESCRIPTION

The ADE7816 evaluation kit includes an evaluation board that

allows the performance of the ADE7816 6-channel energy

measurement IC to be evaluated. The ADE7816 evaluation kit

includes evaluation software, written in LabVIEW®, that provides

access to the registers of the ADE7816 using a PC interface. This

document provides information to assist the user in evaluating

the ADE7816.

Complete specifications for the ADE7816 are available in the

ADE7816 data sheet available from Analog Devices, Inc., and

should be consulted in conjunction with this user guide when

using the evaluation board.

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

10489-001

Figure 1.

Rev. 0 | Page 1 of 16

UG-370 Evaluation Board User Guide

TABLE OF CONTENTS

Features.............................................................................................. 1

General Description ......................................................................... 1

ADE7816 Interface and Evaluation Board .................................... 1

Revision History ............................................................................... 2

Evaluation Board Hardware............................................................ 3

Overview........................................................................................ 3

Powering the ADE7816 Evaluation Board................................ 3

Typical Input Configurations...................................................... 3

Jumper Configuration.................................................................. 3

Installing the Evaluation Board Software...................................... 7

Installing the Drivers ................................................................... 7

Launching the Evaluation Board Software................................... 7

Running the Evaluation Software............................................... 8

Troubleshooting the Launch....................................................... 8

Evaluation Software Functions ........................................................9

Communication ............................................................................9

Main Menu.....................................................................................9

Reset the ADE7816........................................................................9

Active Energy.................................................................................9

Reactive Energy .......................................................................... 10

RMS.............................................................................................. 10

Waveform Sampling................................................................... 10

ADE7816 Interrupts................................................................... 11

Read and Write Registers .......................................................... 11

All Registers Access.................................................................... 11

Troubleshooting.......................................................................... 12

Evaluation Board Schematics........................................................ 13

REVISION HISTORY

3/12—Revision 0: Initial Version

Rev. 0 | Page 2 of 16

Evaluation Board User Guide UG-370

A

A

EVALUATION BOARD HARDWARE

OVERVIEW

The ADE7816 evaluation kit includes an evaluation board that

is used to evaluate the silicon. The board includes the ADE7816

energy measurement IC, associated filtering, and isolation to

allow high voltage inputs to be applied. It also includes an NXP

Semiconductors LPC2368FBD100 microcontroller that handles

all communication from the PC to the ADE7816. Connect P14

of the ADE7816 evaluation board to the USB port of the PC,

using the cable provided in the evaluation board kit.

A schematic of the ADE7816 evaluation board is shown in

Figure 20, Figure 21, and Figure 22

POWERING THE ADE7816 EVALUATION BOARD

An external 3.3 V dc supply is required to power up the ADE7816

evaluation board. P9 provides the 3.3 V supply. This provides

power for the ADE7816 and the nonisolated side of the circuit,

including the ADE7816 IC. Power for the isolated side of the

circuit, which includes the microcontroller, is provided, by

default, by the USB connection. If an external power source

is preferred, apply this power source on P12. When using an

external power supply, Jumper JP24 must be changed to the

1, 2 position (see Tabl e 1).

TYPICAL INPUT CONFIGURATIONS

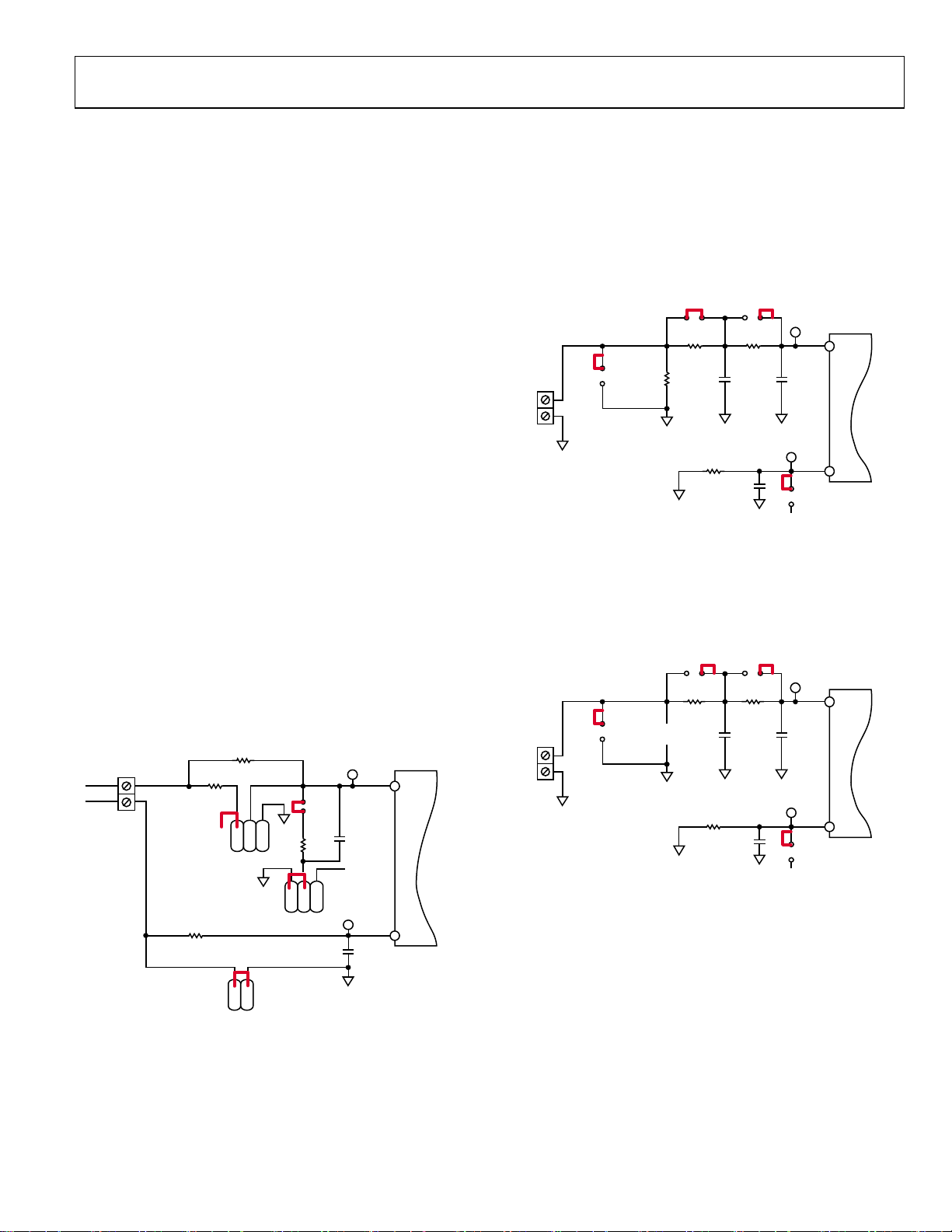

Voltage Channel

The voltage channel input is applied to P6. The ADE7816

evaluation board is designed to interface directly with a line

voltage source. A resistor divider is therefore included to step

down the input voltage. Figure 2 shows the default configuration

of the voltage channel input.

R28

VP

VN

1MΩ

R25

1kΩ

JP9A

JP7N

R31

1kΩ

123

JP8C

1

2

123

P6

JP9C

R34

1kΩ

VP

VN

Figure 2. Typical Voltage Channel Configuration

The maximum signal level that can be applied to the VP pin of

the ADE7816 is 0.5 V peak with respect to VN. Any input level

can be accommodated by modifying the resistor divider network,

R28 and R34.

C26

22nF

VN

C25

22nF

ADE7816

VP

VN

10489-002

Current Channels

The ADE7816 includes six, single-ended current channels that can

be interfaced with either a current transformer (CT) or Rogowski

coil. Apply the sensor output for Current Channel A to P1. Similar

to the voltage channel, all current inputs have a maximum input of

0.5 V peak. Figure 3 shows a typical configuration for Current

Channel A when a CT is being used.

JP3

R9

100Ω

BURDEN

RESISTOR

R1

IAP

IAN

JP1A

P1

Figure 3. Typical Current Channel A Configuration with a CT

22nF

C9

R94

1kΩ

C17

22nF

JP5A

R17

1kΩ

22nF

C17

IAN

IN

IAP

1kΩ

IAP

IAN

ADE7816

If a Rogowski coil is used, no burden resistor is required. A second

stage antialiasing filter is recommended and is enabled through

JP3A. Because the differential nature of the Rogowski coil output

counterbalances a single-pole filter, a second stage is required to

achieve a suitable level of attenuation at the Nyquist frequency.

JP3

R9

100Ω

DO NOT

INSTALL

R1

IAP

IAN

JP1A

P1

Figure 4. Typical Current Channel A Configuration with a Rogowski Coil

22nF

C9

R94

1kΩ

C17

22nF

JP5A

R17

1kΩ

22nF

C17

IAN

IN

IAP

1kΩ

IAP

IAN

ADE7816

Current Channel B through Current Channel F are configured

in a similar manner. Note, however, that Current Channel D,

Current Channel E, and Current Channel F share a common

neutral line and, therefore, only a single antialiasing filter is

present on the neutral line for all three channels.

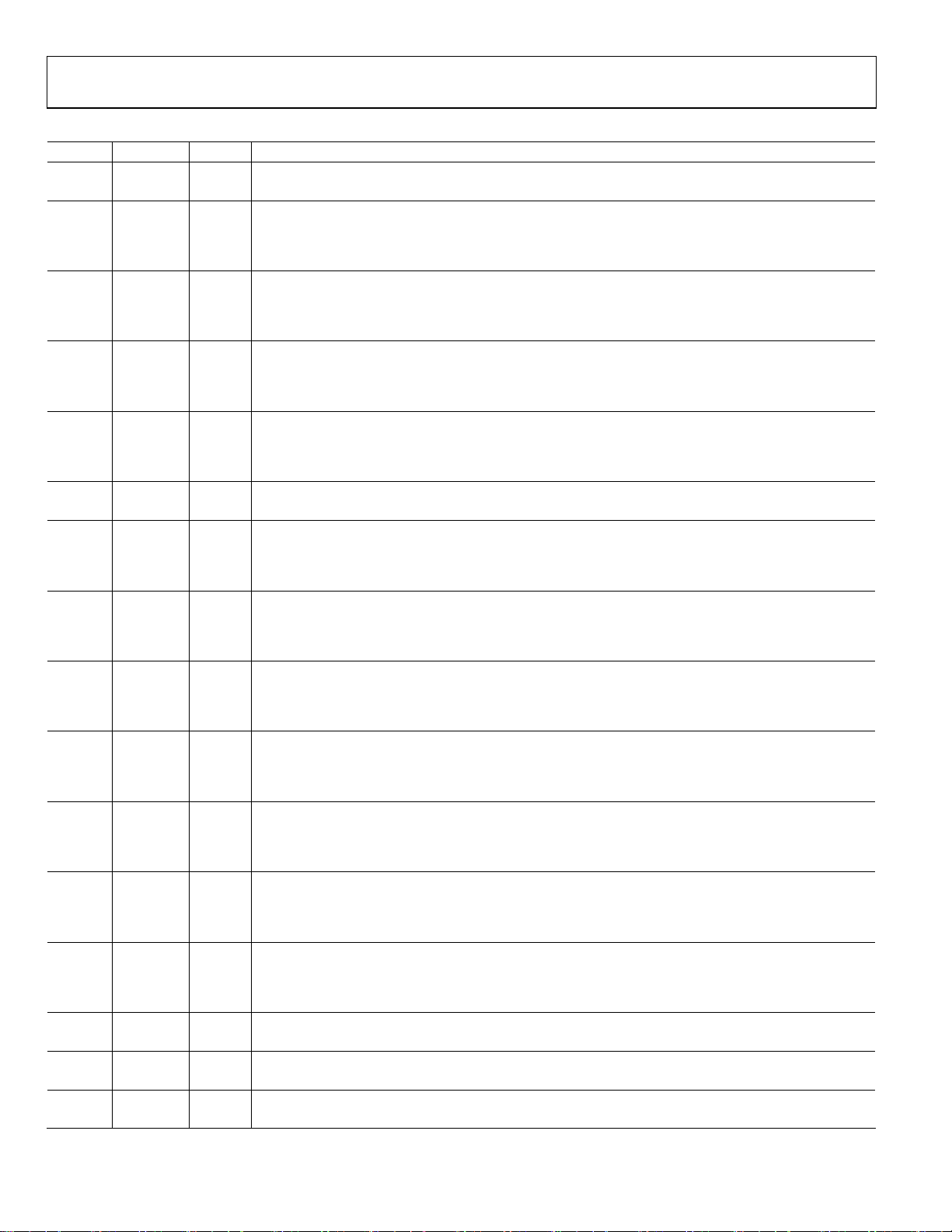

JUMPER CONFIGURATION

Tabl e 1 describes the jumpers included on the ADE7816 evaluation

board and the required settings for different configurations.

Before connecting any high voltage signal, review the jumper

configuration and verify that it is correct for its specific setup.

10489-003

10489-004

Rev. 0 | Page 3 of 16

UG-370 Evaluation Board User Guide

Table 1. Jumper Configurations

Jumper Default Option Description

JP1 Closed Pin 2 (PULL_HIGH) is controlled externally by the microcontroller.

X Open Pin 2 (PULL_HIGH) is connected to VDD via the pull-up resistor, R86.

JP1A Closed

X Open

JP1B Closed

X Open

JP1C Closed

X Open

JP1N Closed

X Open

JP2 Closed Pin 3 (PULL_LOW) is controlled externally by the microcontroller.

X Open Pin 3 (PULL_LOW) is connected to GND via the pull-down resistor, R87.

JP3 Closed

X Open

JP3A X Closed

Open

JP3B X Closed

Open

JP3C X Closed

Open

JP3N X Closed

Open

JP4 Closed

X Open

JP5 X Closed

Open

JP5A Closed This disables the antialiasing filter comprised of R17 and C17 in the IAP signal path.

X Open This enables the antialiasing filter comprised of R17 and C17 in the IAP signal path.

JP5B Closed This disables the antialiasing filter comprised of R19 and C19 in the IBP signal path.

X Open This enables the antialiasing filter comprised of R19 and C19 in the IBP signal path.

JP5C Closed This disables the antialiasing filter comprised of R21 and C21 in the ICP signal path.

X Open This enables the antialiasing filter comprised of R21 and C21 in the ICP signal path.

This connects Pin 1 of the Channel IA pin connector (P1) to AGND. Use this configuration in conjunction

with JP3A and JP5A closed to short the IAP pin of the ADE7816 to AGND.

Pin 1 of the Channel IA pin connector (P1) is left floating. Use this configuration in normal operation to

drive the IAP pin with an analog signal.

This connects Pin 1 of the Channel IB pin connector (P2) to AGND. Use this configuration in conjunction

with JP3B and JP5B closed to short the IBP pin of the ADE7816 to AGND.

Pin 1 of the Channel IB pin connector (P2) is left floating. Use this configuration in normal operation to

drive the IBP pin with an analog signal.

This connects Pin 1 of the Channel IC pin connector (P3) to AGND. Use this configuration in conjunction

with JP3C and JP5C closed to short the ICP pin of the ADE7816 to AGND.

Pin 1 of the Channel IC pin connector (P3) is left floating. Use this configuration in normal operation to

drive the ICP pin with an analog signal.

This connects Pin 1 of the Channel IF pin connector (P4) to AGND. Use this configuration in conjunction

with JP3N and JP5N closed to short the IFP pin of the ADE7816 to AGND.

This connects Pin 1 of the Channel IC pin connector (P4) to AGND. Use this configuration in conjunction

with JP3N and JP5N closed to short the IFP pin of the ADE7816 to AGND.

This connects Pin 1 of the Channel ID pin connector (P38) to AGND. Use this configuration in conjunction

with JP5 and JP7 closed to short the IDP pin of the ADE7816 to AGND.

Pin 1 of the Channel ID pin connector (P38) is left floating. Use this configuration in normal operation to

drive the IDP pin with an analog signal.

This disables the antialiasing filter comprised of R9 and C9 in the IAP signal path. This filter is required

only when using a di/dt sensor.

This enables the antialiasing filter comprised of R9 and C9 in the IAP signal path. This filter is required

only when using a di/dt sensor.

This disables the antialiasing filter comprised of R11 and C11 in the IBP signal path. This filter is required

only when using a di/dt sensor.

This enables the antialiasing filter comprised of R11 and C11 in the IBP signal path. This filter is required

only when using a di/dt sensor.

This disables the antialiasing filter comprised of R13 and C13 in the ICP signal path. This filter is required

only when using a di/dt sensor.

This enables the antialiasing filter comprised of R13 and C13 in the ICP signal path. This filter is required

only when using a di/dt sensor.

This disables the antialiasing filter comprised of R15 and C15 in the IFP signal path. This filter is required

only when using a di/dt sensor.

This enables the antialiasing filter comprised of R15 and C15 in the IFP signal path. This filter is required

only when using a di/dt sensor.

This connects Pin 1 of the Channel IE pin connector (P39) to AGND. Use this configuration in conjunction

with JP6 and JP8 closed to short the IEP pin of the ADE7816 to AGND.

Pin 1 of the Channel IE pin connector (P39) is left floating. Use this configuration in normal operation to

drive the IEP pin with an analog signal.

This disables the antialiasing filter comprised of R90 and C69 in the IDP signal path. This filter is required

only when using a di/dt sensor.

This enables the antialiasing filter comprised of R90 and C69 in the IDP signal path. This filter is required

only when using a di/dt sensor.

Rev. 0 | Page 4 of 16

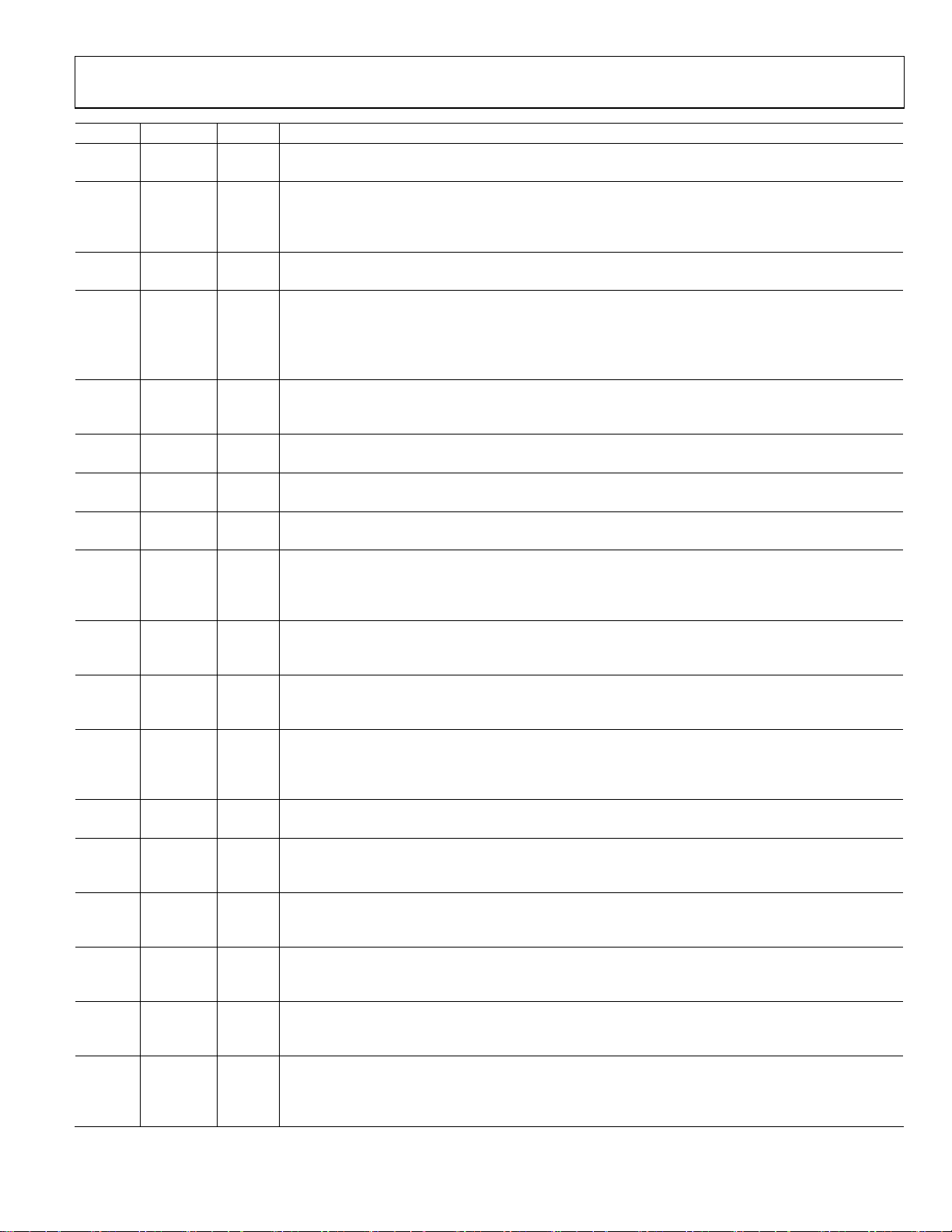

Evaluation Board User Guide UG-370

Jumper Default Option Description

JP5N Closed This disables the antialiasing filter comprised of R23 and C23 in the IFP signal path.

X Open This enables the antialiasing filter comprised of R23 and C23 in the IFP signal path.

JP6 X Closed

Open

JP7 Closed This disables the antialiasing filter comprised of R92 and C71 in the IDP signal path.

X Open This enables the antialiasing filter comprised of R92 and C71 in the IDP signal path.

JP7C 1, 2

2, 3 This connects the VP input to AGND.

X Open

JP7N X Closed

Open This enables the antialiasing filter comprised of R25 and C25 in the VN signal path.

JP8 Closed This disables the antialiasing filter comprised of R93 and C72 in the IEP signal path.

X Open This enables the antialiasing filter comprised of R93 and C72 in the IEP signal path.

JP8C X 1, 2 This connects R34 and C26 to AGND.

2, 3 This connects R34 and C26 to VN. This configuration is not typically used in normal operation.

JP9 Closed Pin 34 (NC) is connected to the microcontroller. This configuration is not required for normal operation.

X Open Pin 34 (NC) is left floating.

JP9C X Closed

Open

JP10 X 1, 2 This connects the 16.38 MHz, on-board crystal (Y1) to the CLKIN and CLKOUT pins of the ADE7816.

2, 3

JP11 X 1, 2 This connects the supply of second side of the isocouplers (VDD2) to VDD, the supply of the ADE7816.

2, 3

JP12 Closed

X Open

JP13 Closed Pin 33 (NC) is connected to the microcontroller. This configuration is not required for normal operation.

X Open Pin 33 (NC) is left floating.

JP14 Closed

X Open The antialiasing filter for the IAN pin is provided by R94 and C73.

JP15 Closed

X Open The antialiasing filter for the ICN pin is provided by R95 and C74.

JP17 Closed

X Open The antialiasing filter for the IBN pin is provided by R96 and C75.

JP18 Closed

X Open The antialiasing filter for the IN pin is provided by R97 and C76.

JP21 Closed

X Open

This disables the antialiasing filter comprised of R91 and C70 in the IEP signal path. This filter is only

required when using a di/dt sensor.

This enables the antialiasing filter comprised of R91 and C70 in the IEP signal path. This filter is only

required when using a di/dt sensor.

This bypasses the voltage divider. Use this configuration in conjunction with JP9C (open). Use this

configuration when applying low voltage signals.

This enables the voltage divider consisting of R28 and R34. Use in conjunction with JP9C (closed). Use

this configuration when applying high voltage signals.

This enables the antialiasing filter comprised of R25 and C25 in the VN signal path. Connects VN to

ground. Use this configuration when using high voltage signals.

This enables the voltage divider consisting of R28 and R34. Use in conjunction with JP7C (open). Use this

configuration when applying high voltage signals.

This bypasses the voltage divider. Use this configuration in conjunction with JP7C (1, 2). Use this

configuration when applying low voltage signals.

This allows an external clock to be connected to the EXT_CLKIN connector. This configuration

disconnects the on-board crystal (Y1).

This connects the supply of second side of the isocouplers (VDD2) to a 3.3 V supply provided at the P10

connector.

This connects the ADR280 voltage reference to the REF pin of the ADE7816. Use this configuration when

the ADE7816 is configured for external reference use.

This disconnects the ADR280 voltage reference from the REF pin of the ADE7816. Use this configuration

in normal operation when the ADE7816 internal reference is used.

This connects the IAN pin to the IBN, ICN, and IN pins. This allows a single antialiasing filter to be used for

all neutral inputs.

This connects the ICN pin to the IAN, IBN, and IN pins. This allows a single antialiasing filter to be used for

all neutral inputs.

This connects the IBN pin to the IAN, ICN, and IN pins. This allows a single antialiasing filter to be used for

all neutral inputs.

This connects the IN pin to the IAN, IBN, and ICN pins. This allows a single antialiasing filter to be used for

all neutral inputs.

This signals the microcontroller, NXP LPC2368, to declare all I/O pins as outputs. Use this configuration

when another microcontroller manages the ADE7816 through the P17 socket.

Disables the option to use another microcontroller to manage the ADE7816 through the P17 socket. Use

this in normal operation to allow the microcontroller, NXP LPC2368 (U8), to manage the ADE7816.

Rev. 0 | Page 5 of 16

UG-370 Evaluation Board User Guide

Jumper Default Option Description

JP24 1, 2

X 2, 3

JP31,

JP32,

JP33,

JP34

1, 2

X 2, 3

This selects an external 3.3 V power supply, provided at the P12 connector, to power the domain that

includes the NXP LPC2368 and one side of the isocouplers. Use this configuration if USB provided power

supply is not desired.

This selects the USB provided power supply to power the domain that includes the NXP LPC2368 and

one side of the isocouplers. Use this in normal operation to provide the power to the NXP LPC2368 and

one side of the isocouplers from the PC.

Use this configuration to select I2C communication between the ADE7816 and the NXP LPC2368

microcontroller. In this configuration, the HSDC port is enabled.

Use this configuration to select SPI communication between the ADE7816 and the NXP LPC2368

microcontroller. In this configuration, HSDC communication is not available.

Rev. 0 | Page 6 of 16

Evaluation Board User Guide UG-370

INSTALLING THE EVALUATION BOARD SOFTWARE

INSTALLING THE DRIVERS

When using the ADE7816 evaluation tools for the first time, a

driver must be installed to allow successful communication. The

driver can be found on the accompanying CD in the Drivers

folder.

There are two folders within the Drivers folder.

• The Windows XP and VISTA folder contains the driver

suitable for 32-bit operating systems, such as Windows® XP

and the 32-bit version of Windows Vista®.

• The Windows 7 (64 bit) folder contains the driver suitable

for 64-bit operating systems, such as Windows 7.

Select the appropriate driver based on the operating system

used. To install the driver, follow this procedure. Note that the

format of the screens may vary depending on the operating

system being used.

1. Connect the USB cable to the PC and the interface board.

The Found New Hardware Wizard window appears,

indicating that the PC has detected the new hardware.

3. In the Found New Hardware Wizard window, select the

Install from a list or specific location (Advanced) option

and click Next >.

The following window opens (see Figure 6).

Figure 6. Search for Driver Window

4. Select Include this location in the search: and click the

Browse button to locate the Windows XP and VISTA or

Windows 7 (64 bit) folder in the Drivers folder on the

evaluation kit CD.

5. Click Next >.

The Hardware Installation window appears, stating that

the hardware did not pass the Windows Logo test.

6. Click Continue until the installation is complete.

7. Click Finish to close the window.

10489-006

Figure 5. Found New Hardware Wizard Screen

2. If you are installing the driver on a system running

Windows 7, the Found New Hardware Wizard may not

appear. To manually select the driver, follow these steps.

a. Choose Control Panel > Hardware and Sound >

Device Manager and locate the new hardware under

the Ports heading.

b. Right-click the port and select Update Driver

Software.

c. Select Browse my Computer for Driver Software.

A window similar to that shown in Figure 6 appears.

d. Go to Step 4.

LAUNCHING THE EVALUATION BOARD SOFTWARE

The evaluation software is available on the accompanying CD in

the Evaluation Software folder. An executable version of the

10489-005

Rev. 0 | Page 7 of 16

software is available in the EXE folder. The executable can be

run even if a licensed copy of LabVIEW is not available. If

LabVIEW 2010 is being used on the PC for the first time, an

installer must be run before opening any of the LabVIEW files.

This installer is available in the Installer folder. If a copy of

LabVIEW 2010 is available on the PC, a full version of the

evaluation code is also provided in the Full Code folder.

To run the installer, double-click on the setup.exe file in the

Installer folder. Follow the prompts to install the LabVIEW

2010 run-time engine. When the installation is complete, the

ADE7816 evaluation software opens automatically. It is also

available in the Start menu. This shortcut can be found by

selecting Programs > ADE7816_Eval_Rev5.

UG-370 Evaluation Board User Guide

RUNNING THE EVALUATION SOFTWARE

When the evaluation software is running, it automatically detects

the COM port that the ADE7816 evaluation board is connected to.

If the port detection is successful, the COM port number appears

in the Port Control field, as shown in Figure 7 (COM4 in this

example).

Figure 7. ADE7816 Evaluation Software Main Window

Note that an external power supply to the evaluation board is

not required for COM port detection, assuming that JP24 is set

to the default position of 2, 3 (connecting Pin 2 and Pin 3 of

JP24 together).

10489-007

TROUBLESHOOTING THE LAUNCH

If the software does not detect the COM port, the message shown

in Figure 8 displays.

10489-008

Figure 8. COMM Port Not Found Message

If this message appears, take the following steps:

1. Click Ye s to return to the ADE7816 Evaluation Software

main window (see Figure 7).

2. Verify that the interface board is connected to the PC using

the USB cable.

3. Ensure that the required drivers are installed as described in

the Installing the Drivers section.

4. Using the Device Manager tool, ensure that the port is

operating correctly.

5. Click the Port Control tab in the main window and manually

select the correct COM port.

If the COM port is still not visible, close LabVIEW and reset the

COM port manually. To do this, take the following steps:

1. Disconnect the USB cable connected to P14.

2. Press the S2 push-button on the ADE7816 evaluation board.

3. Connect the USB cable to P14 again prior to relaunching

LabVIEW.

Rev. 0 | Page 8 of 16

Evaluation Board User Guide UG-370

EVALUATION SOFTWARE FUNCTIONS

COMMUNICATION

The ADE7816 evaluation software allows access to all registers and

features of the ADE7816 using SPI, I

By default, the evaluation board is configured to be used with

SPI. To change the mode of communication to I

JP31, JP32, JP33, and JP34 jumpers to Position 1, Position 2. Then,

change the communication switch in the main window of the

evaluation board software to I

option is selected, the communication mode locks. To change

the communication after this time, the ADE7816 must be

powered down by removing the power on P9.

2

C, and HSDC communication.

2

C, change the

2

C (see Figure 7). Once a menu

MAIN MENU

The menu options available in the ADE7816 Evaluation

Software main window include the following:

Note that only one option under MENU can be open at a time;

click Exit to return to the front panel before choosing another

option under MENU.

RESET THE ADE7816

In the ADE7816 Evaluation Software main window, click Reset

ADE7816 and the Software Reset window appears, as shown in

Figure 9.

• Reset ADE7816

• Active Power

• Reactive Power

• RMS

• Wave for m Sa mp lin g

• Interrupts

• Read and Write registers

• All Registers Access

• Exit (stops LabVIEW)

These options provide access to all internal registers and allow

the evaluation of the performance of the ADE7816 (see Figure 7).

To access these functions, click the desired option in the MENU

panel. Click on an option under MENU to display a window

where the specific function can be accessed.

10489-009

Figure 9. Reset Window

Click RESET to perform a software reset on the ADE7816. All

register data is lost with the exception of the CONFIG2 register.

ACTIVE ENERGY

In the ADE7816 Evaluation Software main window, click Active

Power and the Active Energy window appears, as shown in

Figure 10. This window allows access to all registers associated

with the active energy measurement.

The drop-down list at the top left of the window allows the

channel to be selected and registers associated with Channel A

through Channel F to be accessed. Click Read to read a register.

Register modifications can be made directly on the signal path

diagram; click Wr it e to write these modifications to the part.

10489-010

Figure 10. Active Energy Window

Rev. 0 | Page 9 of 16

UG-370 Evaluation Board User Guide

Within the Active Energy window, click Line Cycle

Accumulation to access the window shown in Figure 11.

10489-011

Figure 11. Line Cycle Accumulation Window

The line cycle mode allows energy to be accumulated over

an integral number of half line cycles. To activate line cycle

accumulation, an ac signal must be present on the voltage

channel.

Click EXIT in the Line Cycle Accumulation window to return

to the Active Energy window.

REACTIVE ENERGY

In the ADE7816 Evaluation Software main window, click

Reactive Power and the Reactive Energy window appears.

This window is similar to the Active Energy window shown

in Figure 10; however, it allows access to registers that are

associated with the reactive energy measurements. The dropdown list at the top left of the window allows the channel to be

changed to access registers associated with Channel A through

Channel F. The Line Cycle Accumulation window (see Figure 11)

is also accessible from the Reactive Energy window.

WAVEFORM SAMPLING

The Wave for m Sa mp ling window is shown in Figure 13. To use

the Wave for m Sa mplin g window, I

communication interface (see Figure 7) in the ADE7816

Evaluation Software main window. The I

in conjunction with the HSDC interface (see the ADE7816

data sheet).

Figure 12. RMS Window

2

C must be selected as the

2

C interface is used

10489-012

RMS

In the ADE7816 Evaluation Software main window, click RMS

to display the window shown in Figure 12. From this window,

registers associated with the IRMS and VRMS measured are

accessed. Click Read Setup and Wri te Set up to allow the

configuration to be read and modified, respectively. Under

the Reading Time/Channel slide bar, click Read RMS

Continuously to read continuously over a specified time.

Rev. 0 | Page 10 of 16

Figure 13. Waveform Sampling Window

This window allows raw waveform data to be captured and

displayed on a graph. To save the data to a file, click Wr i te

waveforms to file? and enter a destination in the File Path box.

10489-013

Evaluation Board User Guide UG-370

ADE7816 INTERRUPTS

The ADE7816 Interrupts window is shown in Figure 14.

Figure 14. ADE7816 Interrupts Window

This window allows access to the status and enable registers

associated with the

IRQ0

allow the individual interrupt enable bits to be selected. After

these selections are configured, click Write Mas k0 Reg is ter and

Writ e Mask 1 R egis ter to write to the part. The lights represent

the corresponding interrupt status registers. Click Read Status0

Register and Read Status1 Register to read these registers. Click

Clear Status0 Register and Clear Status1 Register, respectively, to

clear the

IRQ0

and

IRQ1

IRQ1

and

interrupt.

pins. The switch buttons

10489-014

ALL REGISTERS ACCESS

The All Registers Access window allows all the registers in the

ADE7816 to be accessed at once (see Figure 16).

READ AND WRITE REGISTERS

The ADE7816 Read and Write Registers window is shown in

Figure 15.

Figure 15. Read and Write Registers Window

Select the register name from the drop-down list to access an

individual register from this window. Alternatively, click Register

Name to access registers by number; clicking this button displays

fields for entering a register name and register size. To access the

register directly, type in the number and size of the register into

the appropriate fields.

10489-016

Figure 16. All Registers Access Window

Click Read All Regs or Writ e Al l R egs to read or modify the

entire ADE7816 register bank. Choose a destination file at the

top of the window and click Save All Regs into a file to save the

current configuration to a comma-separated variable (.csv) file.

To load the desired configuration from a file, click Load All Regs

from a file; the contents of the specified .csv file are written to

the ADE7816.

10489-015

Rev. 0 | Page 11 of 16

UG-370 Evaluation Board User Guide

TROUBLESHOOTING

Communication Failure

If communication to the ADE7816 is not successful, the warning

message shown in Figure 17 displays.

10489-017

Figure 17. Communication Unsuccessful Message

This message indicates that the ADE7816 did not respond and

the communication timed out. Reset the communication port

on the PC to restore communication to the ADE7816. Click OK

and the ClearPort.vi window appears (see Figure 18).

Before continuing with the evaluation of the ADE7816, investigate

the reason for the communication failure. After the COM port is

cleared, the window shown in Figure 19 displays some possible

reasons for the failed communication. Click OK.

10489-019

Figure 19. Error Debug Window

Now, go to the ADE7816 Evaluation Software main window

and click Exit from the menu drop-down list (see Figure 7).

Verify that the correct COM port is selected and ensure that the

currently configured communication mode is selected in the pulldown list. Refer to Tab le 1 to verify that the correct jumpers are

installed for the selected communication interface.

If the previous procedure does not correct the issue, take the

following steps:

1. Close the evaluation software.

2. Manually reset the COM port; disconnect the USB cable

connected to P14 and press the S2 push-button on the

ADE7816 evaluation board.

3. Connect the USB cable to P14 again, prior to relaunching

LabVIEW.

Figure 18. ClearPort.vi Window

When the ClearPort.vi window appears, press the S2 push-button

located below the PC connection on the ADE7816 interface port to

reset the PC COM port (see Figure 1). After completing this

action, click DONE in the ClearPort.vi window.

Incorrect Register Readings

If the data read back from the ADE7816 registers is always

0xFFFF, a possible cause is that the ADE7816 is not correctly

powered. Ensure that a 3.3 V supply has been supplied to the

ADE7816, as described in the Powering the ADE7816

10489-018

Evaluation Board section.

Another possible cause is that the incorrect communication port is

selected. Ensure that the correct jumpers are installed and that

the communication mode is selected in the ADE7816 Evaluation

Software main window of the evaluation board, as described in

the Communication section.

Rev. 0 | Page 12 of 16

Evaluation Board User Guide UG-370

EVALUATION BOARD SCHEMATICS

10489-020

Figure 20. ADE7816 Evaluation Board Schematic (Page 1)

Rev. 0 | Page 13 of 16

UG-370 Evaluation Board User Guide

10489-021

Figure 21. ADE7816 Evaluation Board Schematic (Page 2)

Rev. 0 | Page 14 of 16

Evaluation Board User Guide UG-370

10489-022

Figure 22. ADE7816 Evaluation Board Schematic (Page 3)

Rev. 0 | Page 15 of 16

UG-370 Evaluation Board User Guide

NOTES

ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection

circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions

set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you

have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc.

(“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal,

temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided

for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional

limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term

“Third Party” includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including

ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may

not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to

promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any

occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board.

Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice

to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO

WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED

TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL

PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER’S POSSESSION OR USE OF

THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE

AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable

United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of

Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby

submits to the pers onal jurisdiction and venu e of such courts. The United Nations Conventi on on Contracts for the Internation al Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2012 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

UG10489-0-3/12(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...