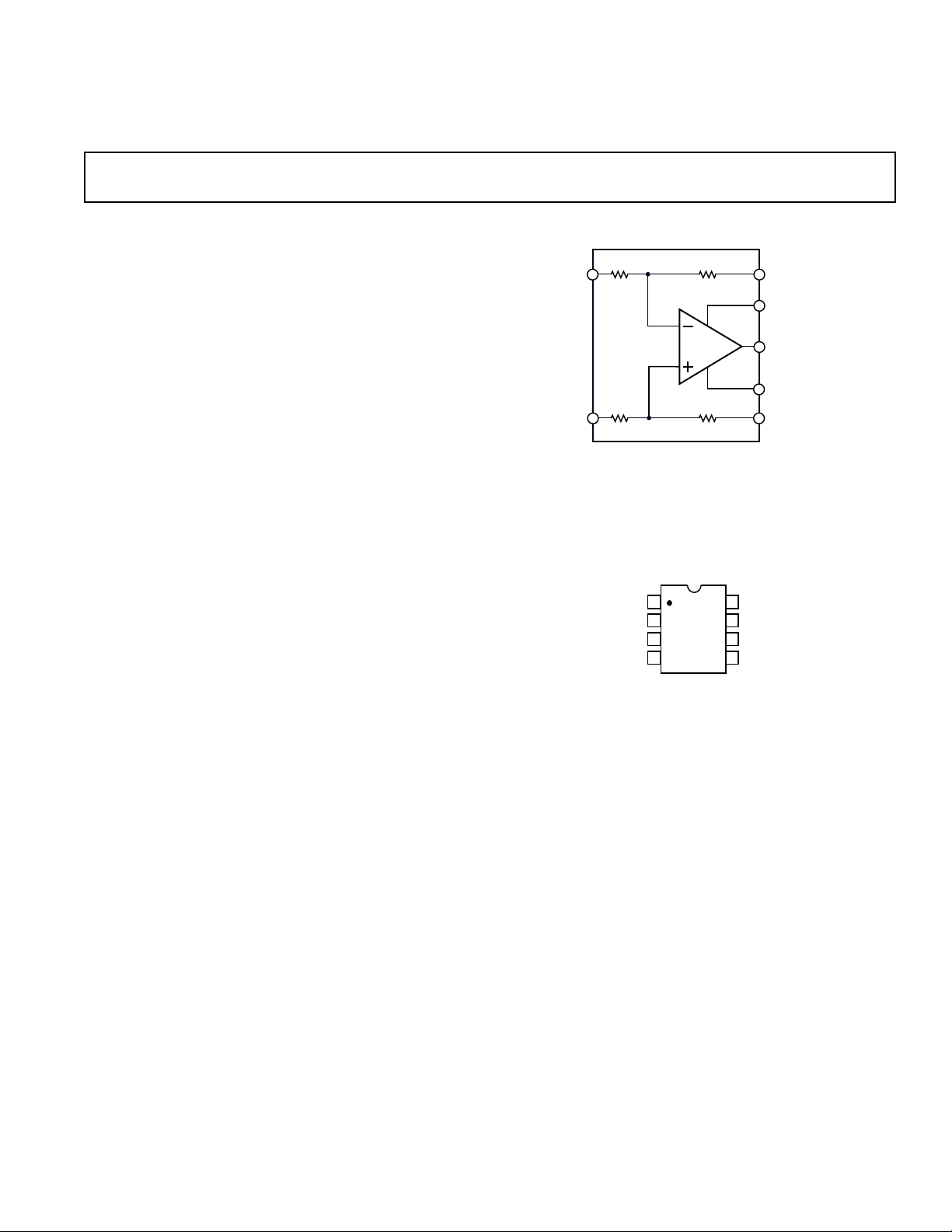

SSM2141

–IN

+IN

SENSE

+V

CC

OUTPUT

–V

EE

REFERENCE

25kΩ 25kΩ

25kΩ25kΩ

1

3

2

5

7

6

4

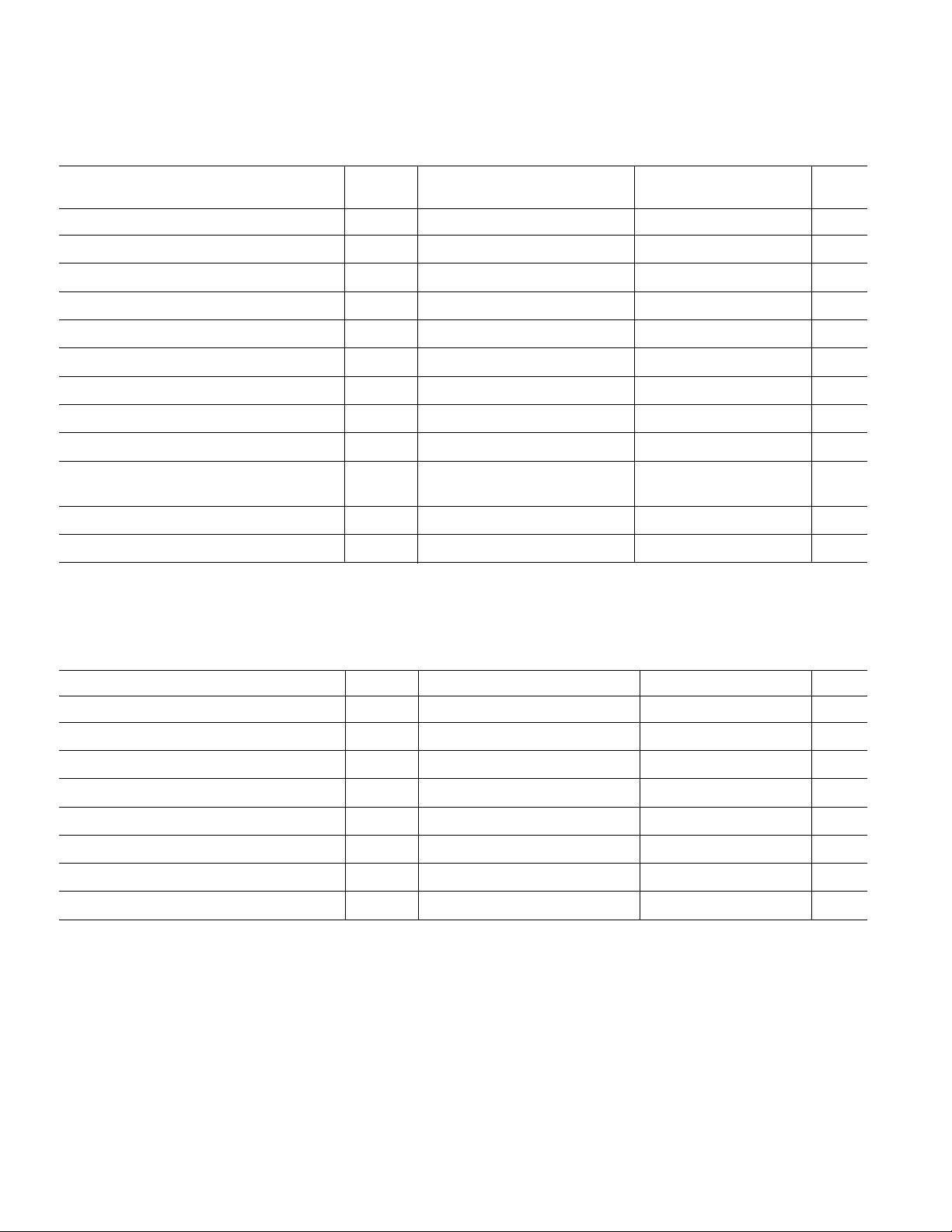

1

2

3

4

8

7

6

5

TOP VIEW

(Not to Scale)

NC = NO CONNECT

SSM2141

REFERENCE

SENSE

OUTPUT

V+

NC

–IN

+IN

V–

High Common-Mode Rejection

a

FEATURES

High Common-Mode Rejection

DC: 100 dB typ

60 Hz: 100 dB typ

20 kHz: 70 dB typ

40 kHz: 62 dB typ

Low Distortion: 0.001% typ

Fast Slew Rate: 9.5 V/ms typ

Wide Bandwidth: 3 MHz typ

Low Cost

Complements SSM2142 Differential Line Driver

APPLICATIONS

Line Receivers

Summing Amplifiers

Buffer Amplifiers–Drives 600 V Load

GENERAL DESCRIPTION

The SSM2141 is an integrated differential amplifier intended to

receive balanced line inputs in audio applications requiring a

high level of noise immunity and optimum common-mode

rejection. The SSM2141 typically achieves 100 dB of commonmode rejection (CMR), whereas implementing an op amp with

four off-the-shelf precision resistors will typically achieve only

40 dB of CMR—inadequate for high-performance audio.

The SSM2141 achieves low distortion performance by

maintaining a large slew rate of 9.5 V/µs and high open-loop

gain. Distortion is less than 0.002% over the full audio

bandwidth. The SSM2141 complements the SSM2142

balanced line driver. Together, these devices comprise a fully

integrated solution for equivalent transformer balancing of

audio signals without the problems of distortion, EMI fields,

and high cost.

Additional applications for the SSM2141 include summing

signals, differential preamplifiers, and 600 Ω low distortion

buffer amplifiers. For similar performance with G = 1/2, see

SSM2143.

Differential Line Receiver

SSM2141

FUNCTIONAL BLOCK DIAGRAM

PIN CONNECTIONS

8-Pin Plastic Mini-DIP

(P Suffix)

Narrow Body SO

(S Suffix)

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

SSM2141–SPECIFICA TIONS

ELECTRICAL CHARACTERISTICS

(@ VS = 618 V, TA = +258C, unless otherwise noted)

SSM2141

Parameter Symbol Conditions Min Typ Max Units

OFFSET VOLTAGE V

OS

VCM = 0 V –1000 25 1000 µV

GAIN ERROR No Load, VIN = ±10 V, RS = 0 Ω 0.001 0.01 %

INPUT VOLTAGE RANGE IVR (Note 1) ±10 V

COMMON-MODE REJECTION CMR VCM = ±10 V 80 100 dB

POWER SUPPLY REJECTION RATIO PSRR VS = ±6 V to ±18 V 0.7 15 µV/V

OUTPUT SWING V

SHORT-CIRCUIT CURRENT LIMIT I

O

SC

RL = 2 kΩ±13 ±14.7 V

Output Shorted to Ground +45/–15 mA

SMALL-SIGNAL BANDWIDTH (–3 dB) BW RL = 2 kΩ 3 MHz

SLEW RATE SR RL = 2 kΩ 6 9.5 V/µs

TOTAL HARMONIC DISTORTION R

= 100 kΩ 0.001 %

L

THD RL = 600 Ω 0.01

CAPACITIVE LOAD DRIVE CAPABILITY C

SUPPLY CURRENT I

NOTES

1

Input Voltage Range Guaranteed by CMR test.

Specifications subject to change without notice

L

SY

No Oscillation 300 pF

No Load 2.5 3.5 mA

ELECTRICAL CHARACTERISTICS

(@ VS = 618 V, –408C ≤ TA ≤ +858C)

Parameter Symbol Conditions Min Typ Max Units

OFFSET VOLTAGE V

OS

VCM = 0 V –2500 200 2500 µV

GAIN ERROR No Load, VIN = ±10 V, RS = 0 Ω 0.002 0.02 %

INPUT VOLTAGE RANGE IVR (Note 1) ±10 V

COMMON-MODE REJECTION CMR VCM = ±10 V 75 90 dB

POWER SUPPLY REJECTION RATIO PSRR VS = ±6 V to ±18 V 1.0 20 µV/V

OUTPUT SWING V

O

RL = 2 kΩ±13 ±14.7 V

SLEW RATE SR RL = 2 kΩ 9.5 V/µs

SUPPLY CURRENT I

NOTES

1

Input Voltage Range Guaranteed by CMR test.

Specifications subject to change without notice

SY

No Load 2.6 4.0 mA

–2–

REV. B

SSM2141

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V

Input Voltage

1

. . . . . . . . . . . . . . . . . . . . . . . . Supply Voltage

1

Output Short-Circuit Duration . . . . . . . . . . . . . . Continuous

Storage Temperature Range

P Package . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 60 sec) . . . . . . . . . . . . +300°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Operating Temperature Range . . . . . . . . . . . . –40°C to +85°C

ORDERING GUIDE

Operating Temperature Package Package

Model Range Description Option

SSM2141P XIND (–40°C ≤ T

≤ +85°C) 8-Pin Plastic DIP N-8

A

SSM2141S XIND (–40° C ≤ TA ≤ +85°C) 8-Pin Narrow Body SO SO-8

Typical Performance Characteristics

Package Type u

2

JA

u

JC

Units

8-Pin Plastic DIP (P) 103 43 °C/W

NOTES

1

For supply voltages less than ±18 V, the absolute maximum input voltage is equal

to the supply voltage.

2

θJA is specified for worst case mounting conditions, i.e., θJA is specified for device

in socket for P-DIP package.

Small Signal Transient Response

Common-Mode Rejection vs. Frequency

Large Signal Transient Response

Power Supply Rejection vs. Frequency

REV. B

Total Harmonic Distortion vs. Frequency

Dynamic Intermodulation Distortion vs. Frequency

–3–

SSM2141–

Typical Performance Characteristics

Input Offset Voltage vs. Temperature

Gain Error vs. Temperature

Closed-Loop Gain vs. Frequency

Slew Rate vs. Temperature

Closed-Loop Output Impedance

vs. Frequency

Supply Current vs. Temperature

Supply Current vs. Supply Voltage

Maximum Output Voltage vs.

Output Current (Source)

Maximum Output Voltage vs.

Output Current (Sink)

REV. B–4–

SSM2141

5mV

1S

+1µV

0V

–1µV

0.1 TO 10Hz PEAK-TO-PEAK NOISE

10mV

2mS

+10µV

0V

–10µV

NOTE: EXTERNAL AMPLIFIER GAIN = 1000;

THEREFORE, VERTICAL SCALE = 10µV/DIV.

TA = +25°C

V

S

= ±15V

Voltage Noise Density vs. Frequency

10mV

TA = +25°C

V

= ±15V

S

NOTE: EXTERNAL AMPLIFIER GAIN = 1000;

THEREFORE, VERTICAL SCALE = 10µV/DIV.

1mS

+10µV

0V

–10µV

Voltage Noise from 0 kHz to 1 kHz

APPLICATIONS INFORMATION

The SSM2141 represents a versatile analog building block. In

order to capitalize on fast settling time, high slew rate, and high

CMR, proper decoupling and grounding techniques must be

employed. For decoupling, place 0.1 µF capacitor located within

close proximity from each supply pin to ground.

Low Frequency Voltage Noise

Voltage Noise from 0 kHz to 10 kHz

REV. B

Slew Rate Test Circuit

–5–

SSM2141

MAINTAINING COMMON-MODE REJECTION

In order to achieve the full common-mode rejection capability

of the SSM2141, the source impedance must be carefully

controlled. Slight imbalances of the source resistance will result

in a degradation of DC CMR—even a 5 Ω imbalance will

degrade CMR by 20 dB. Also, the matching of the reactive

source impedance must be matched in order to preserve the

CMRR over frequency.

Figure 1. Precision Difference Amplifier. Rejects

[E

+

E2]

Common-Mode Signal =

1

2

by 100 dB

Figure 5. Suitable Instrumentation Amplifier

Requirements can be Addressed by Using an

Input Stage Consisting of A1, A2, R1 and R

2

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

8-Pin

Epoxy Mini-DIP

P-Suffix (N-8)

C1532–2.5–5/91

Figure 2. Precision Unity Gain Inverting Amplifier

Figure 3. Precision Summing Amplifier

0.210 (5.33)

MAX

0.160 (4.06)

0.115 (2.93)

0.022 (0.558)

0.014 (0.356)

0.1574 (4.00)

0.1497 (3.80)

0.0098 (0.25)

0.0040 (0.10)

SEATING

0.430 (10.92)

0.348 (8.84)

8

14

PIN 1

0.100

(2.54)

BSC

8-Pin Narrow Body SO

0.1968 (5.00)

0.1890 (4.80)

8

PIN 1

0.0500

(1.27)

PLANE

BSC

5

0.280 (7.11)

0.240 (6.10)

0.060 (1.52)

0.015 (0.38)

0.130

(3.30)

MIN

0.070 (1.77)

0.045 (1.15)

SEATING

PLANE

S-Suffix (SO-8)

5

0.2440 (6.20)

41

0.2284 (5.80)

0.0688 (1.75)

0.0532 (1.35)

0.0192 (0.49)

0.0138 (0.35)

0.0098 (0.25)

0.0075 (0.19)

0.325 (8.25)

0.300 (7.62)

0.015 (0.381)

0.008 (0.204)

0.0196 (0.50)

0.0099 (0.25)

8°

0°

0.195 (4.95)

0.115 (2.93)

x 45°

PRINTED IN U.S.A.

0.0500 (1.27)

0.0160 (0.41)

Figure 4. Precision Summing Amplifier with Gain

–6–

REV. B

Loading...

Loading...