Page 1

FEATURES

■

Guaranteed

■

8-Pin SO Plastic Package

■

2.0mA Maximum Supply Current

■

4.62V/4.37V Precision Voltage Monitor

■

Power OK/Reset Time Delay: 600ms

■

Minimum External Component Count

■

Superior Upgrade for DS1232

Reset Assertion at VCC = 1V

LTC1232

Microprocessor

Supervisory Circuits

U

DESCRIPTIO

The LTC®1232 provides power supply monitoring,

watchdog timing and external reset for microprocessor

systems. A precise internal voltage reference and

comparator circuit monitor the power supply line. When

an out-of-tolerance condition occurs, the reset outputs

are forced to active states. The RST output is guaranteed

to remain logic low even with V

as low as 1V.

CC

U

APPLICATIO S

■

Critical µP Power Monitoring

■

Intelligent Instruments

■

Computers and Controllers

■

Automotive Systems

TYPICAL APPLICATIO

5V DC

PB RST

TD

TOL

LTC1232

V

RST

CC

ST

U

5V DC

100k

(e.g. 6805)

I/O LINE

RESET

MPU

The LTC1232 has an internal watchdog timer which forces

the reset outputs to active states when the Strobe input is

not forced low prior to a preset time-out period. The

watchdog timing can be set to operate on time-out periods

of typically 150ms, 600ms or 1.2 seconds.

The LTC1232 performs push-button reset control.

The LTC1232 debounces the push-button input

and guarantees an active reset pulse width of 250ms

minimum.

, LTC and LT are registered trademarks of Linear Technology Corporation.

RST Output Voltage vs

Supply Voltage

5

4

3

2

GND

RST

LTC1232 • TA01

RST OUTPUT VOLTAGE (V)

1

0

1

0

SUPPLY VOLTAGE (V)

3

4

2

5

LTC1232 • TA02

sn1232 1232fas

1

Page 2

LTC1232

WWWU

ABSOLUTE AXI U RATI GS

(Note 1, 2 and 3)

Terminal Voltage

V

.......................................................–0.3V to 7.0V

CC

ST and RST .......................................... – 0.3V to 7.0V

All Other Inputs and Outputs ...... – 0.3V to V

Power Dissipation.............................................. 500mW

Operating Temperature Range

LTC1232C ............................................... 0°C to 70°C

LTC1232I ........................................... –40°C to 85°C

Storage Temperature Range ................. –65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

+0.3V

CC

UU

W

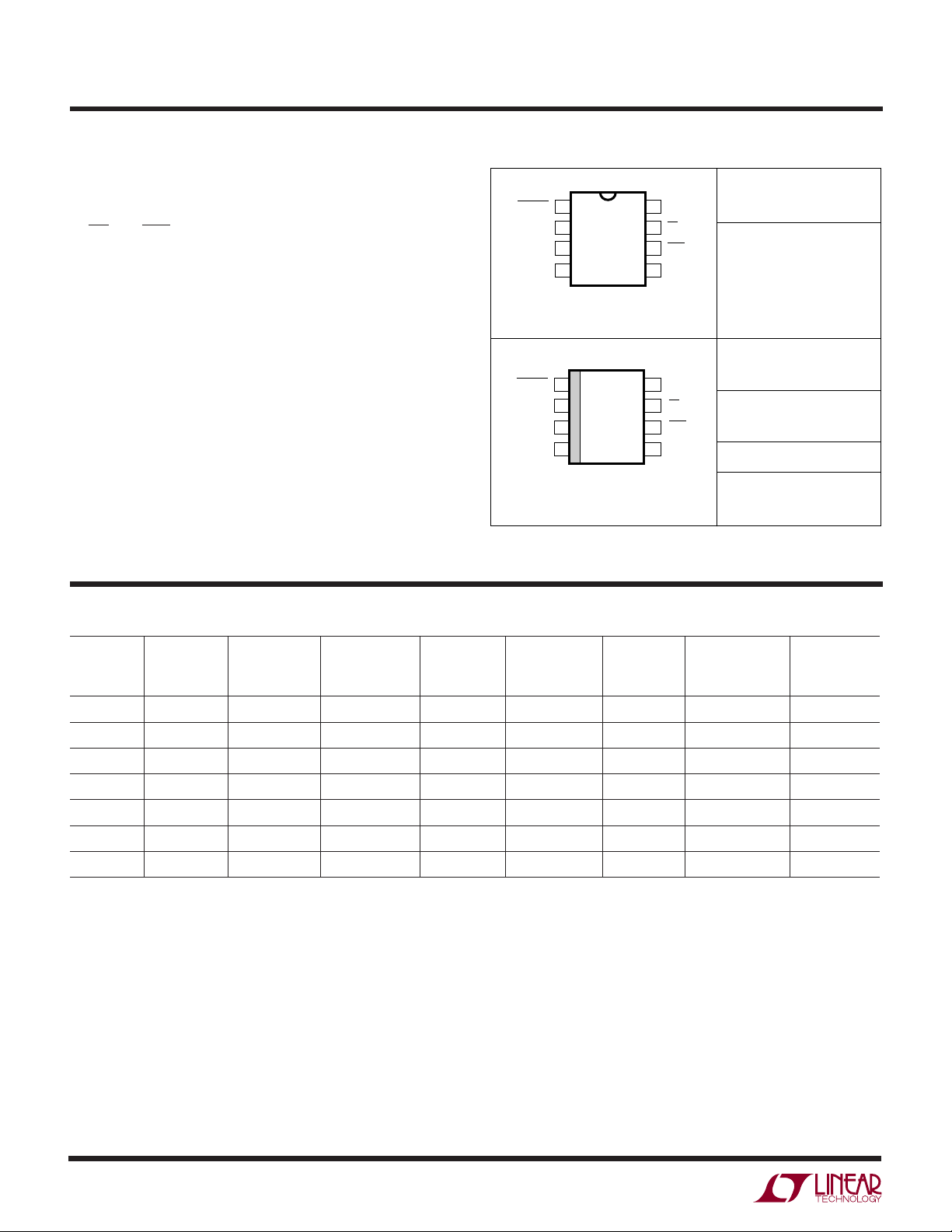

PACKAGE/ORDER I FOR ATIO

TOP VIEW

PB RST

1

TD

2

TOL

3

GND

4

N8 PACKAGE

8-LEAD PDIP

= 100°C, θJA = 130°C/W

T

JMAX

TOP VIEW

PB RST

1

TD

2

TOL

3

GND

4

S8 PACKAGE

8-LEAD PLASTIC SO

T

= 100°C, θJA = 180°C/W

JMAX

Consult LTC Marketing for parts specified with wider operating temperature ranges.

V

8

CC

ST

7

RST

6

RST

5

V

8

CC

ST

7

RST

6

RST

5

ORDER

PART NUMBER

LTC1232CN8

ORDER

PART NUMBER

LTC1232CS8

LTC1232IS8

S8 PART MARKING

1232

1232I

U

PRODUCT SELECTIO GUIDE

POWER RAM CONDITIONAL

WATCHDOG BATTERY FAIL WRITE PUSH-BUTTON BATTERY

PINS RESET TIMER BACKUP WARNING PROTECT RESET BACKUP

LTC1232 8 X X X

LTC690 8 X X X X

LTC691 16 X XXXX

LTC694 8 X X X X

LTC695 16 X XXXX

LTC699 8 X X

LTC1235 16 X XXXXX X

2

sn1232 1232fas

Page 3

LTC1232

WW

RECO E DED OPERATI G CO DITIO S

over the full operating temperature. V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

CC

V

IH

V

IL

Supply Voltage ● 4.5 5 5.5 V

ST and PB RST Input High Level ● 2V

ST and PB RST Input Low Level ● – 0.3 0.8 V

DC ELECTRICAL CHARACTERISTICS

temperature. V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

IL

I

OH

I

OL

I

CC

V

CCTP

V

CCTP

V

HYS

V

RST

= full operating range.

CC

Input Leakage (Note 3) ● –1 1 µA

Output Current at 2.4V (Note 5) ● –1 –13 mA

Output Current at 0.4V (Note 5) ● 26 mA

Supply Current (Note 4) ● 0.5 2 mA

VCC Trip Point TOL = GND ● 4.5 4.62 4.74 V

VCC Trip Point TOL = V

VCC Trip Point Hysteresis 40 mV

RST Output Voltage at VCC = 1V I

= full operating range.

CC

= 10µA 4 200 mV

SINK

The ● denotes the specifications which apply over the full operating

CC

UU UU

The ● denotes the specifications which apply

+0.3 V

CC

● 4.25 4.37 4.49 V

AC CHARACTERISTICS

The ● denotes the specifications which apply over the full operating temperature.

VCC = full operating range.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

t

PB

t

RST

t

ST

t

RPD

t

f

t

RPU

t

R

t

TD

C

IN

C

OUT

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All voltage values are with respect to GND.

Note 3: The PB RST pin is internally pulled up to VCC with an internal

impedance of 10k typical. The TD pin has internal bias current.

PB RST = V

RESET Active Time ● 250 610 1000 ms

ST Pulse Width ● 20 ns

VCC Detect to RST and RST ● 100 ns

VCC Slew Rate 4.75V–4.25V ● 300 µs

VCC Detect to RST and RST tR = 5µs ● 250 610 1000 ms

(Reset Active Time)

VCC Slew Rate 4.25V–4.75V ● 0ns

ST Pin Detect to RST and RST TD = GND ● 60 150 250 ms

(Watchdog Time-Out Period) TD = Floating

Input Capacitance 5pF

Output Capacitance 5 pF

IL

TD = V

CC

Note 4: Measured with outputs open.

Note 5: The RST pin is an open drain output.

● 40 ms

● 250 610 1000 ms

● 500 1200 2000 ms

sn1232 1232fas

3

Page 4

LTC1232

UWW

TI I G DIAGRA S

Push-Button Reset Power Down

PB RST

RST

RST

t

ST

V

IL

t

PB

V

V

Strobe Input Power Up

t

TD

t

4.50V

4.75V

4.25V

F

t

RPD

V

OH

V

OL

LTC1232 • TD03

t

R

t

RPU

V

OH

V

OL

LTC1232 • TD04

V

IH

V

RST

RST

V

RST

RST

CC

CC

t

RST

IH

IL

LTC1232 • TD01

LTC1232 • TD02

4.75V

4.25V

4.50V

BLOCK DIAGRA

8

V

CC

TOL

3

5%, 10%

SWITCH

OSC

PB RST

1

7

ST

LEVEL SENSE

AND

DEBOUNCE

LEVEL SENSE

W

1.3V

6

RST

+

C1

–

WATCHDOG

TIMER

RESET PULSE

GENERATOR

5

RST

4

2

TD

TIME-OUT

SELECTION

LTC1232 • BD01

sn1232 1232fas

Page 5

UW

LTC1232 • TPC03

TEMPERATURE (˚C)

–50

RESET ACTIVE TIME (ms)

648

672

696

25 75

624

600

–25 0

50 100 125

576

552

VCC = 5V

TYPICAL PERFOR A CE CHARACTERISTICS

LTC1232

VCC Trip Point vs Temperature

4.63

TOL = GND

4.62

4.61

4.60

TRIP POINT (V)

CC

4.59

V

4.58

4.57

–50

–25 0

25 75

TEMPERATURE (˚C)

Time-Out Period vs Temperature

696

VCC = 5V

TD = NO CONNECTION

672

648

624

600

576

WATCHDOG TIME-OUT PERIOD (ms)

552

–50

–25 0

50 100 125

LTC1232 • TPC01

50 100 125

25 75

TEMPERATURE (˚C)

TRIP POINT (V)

CC

V

LTC1232 • TPC04

VCC Trip Point vs Temperature

4.38

TOL = V

CC

4.37

4.36

4.35

4.34

4.33

4.32

–50

–25 0

TEMPERATURE (˚C)

50 100 125

25 75

Reset Active Time vs Temperature

LTC1232 • TPC02

RST Output Voltage vs Supply Voltage

5

TA = 25°C

EXTERNAL PULL-UP = 10µA

4

3

2

RST OUTPUT VOLTAGE (V)

1

0

1

0

SUPPLY VOLTAGE (V)

3

2

4

LTC1232 • TPC05

5

U

PI FU CTIO S

VCC: 5V Supply Input. The V

with a 0.1µF capacitor.

GND: Ground Pin.

PB RST: Logic Input to be Directly Connected to a Push-

Button. The PB RST input requires an active low signal

which is debounced and timed for a minimum of 40ms.

When this condition is satisfied, the reset pulse generator

forces the reset outputs to active states. The reset outputs

remain in active states for a minimum of 250ms after

PB RST is released from logic low level.

UU

pin should be bypassed

CC

TOL: Input to Select 5% or 10% Variation on VCC. When

TOL is connected to GND, the reset pulse generator forces

the reset outputs to active states as VCC falls below 4.75V

(4.62V typical). When TOL is connected to VCC, the reset

pulse generator forces the reset outputs to active states as

V

falls below 4.5V (4.37V typical).

CC

TD: Time-Out Delay. TD is a three-level input to select three

different time-out periods. The time-out period is set by

the TD input to be 150ms with TD connected to GND,

600ms with TD left floating, and 1.2 seconds with TD

connected to VCC.

sn1232 1232fas

5

Page 6

LTC1232

U

UU

PI FU CTIO S

RST: Open Drain Logic Output for µP Reset Control.

The LTC1232 provides three ways to generate µP reset.

First, when VCC falls below VCC trip point (4.75V with

TOL = GND and 4.5V with TOL = V

), RST goes active low.

CC

After VCC returns to 5V, the reset pulse generator forces

RST to remain active low for a minimum of 250ms.

Second, when the watchdog timer is not serviced prior to

a selected time-out period, the reset pulse generator also

forces RST to active low for a minimum of 250ms and

repeats for every time-out period. Third and the last, when

the PB RST pin stays active low for a minimum of 40ms,

RST becomes active low. The RST output will remain

WUUU

APPLICATIO S I FOR ATIO

Power Monitoring

The LTC1232 uses a bandgap voltage reference and a

precision voltage comparator, C1, to monitor the 5V

supply input on VCC (see Block Diagram). When VCC falls

below the VCC trip point (4.62V typical with

TOL = GND and 4.37V typical with TOL VCC), the reset

outputs are forced to active states. The VCC trip point

accounts for a 5% or 10% variation on VCC, so the reset

outputs become active when V

point. On power-up, the reset signals are held in active

states for a minimum of 250ms after the VCC trip point is

reached to allow the power supply and microprocessor

to stabilize. On power-down, the RST signal remains

active low even with VCC as low as 1V. This capability helps

hold the microprocessor in stable shutdown condition.

Figure 1 shows the timing diagram of the RST signal.

falls below the VCC trip

CC

active low for a minimum of 250ms from the moment the

push-button reset input is released from logic low level.

RST: RST is an Active High Logic Output. It is the inverse

of RST.

ST: Logic Input to Reset the Watchdog Timer. Driving ST

either high or low longer than the time-out period set by

the TD input, forces the reset outputs to active states for

a minimum of 250ms. The timer resets itself and begins to

time-out again with each high to low transition on the ST

input (see Figure 2).

The precision voltage comparator, C1, typically has 40mV

of hysteresis which ensures that glitches at VCC pin do not

activate the reset outputs. Response time is typically 10µs.

To help prevent mitriggering due to transient loads, V

CC

pin should be bypassed with a 0.1µF capacitor with the

leads trimmed as short as possible.

Push-Button Reset

The LTC1232 provides a logic input pin, PB RST, for direct

connection to a push-button. This push-button reset input

requires an active low signal. Internally, this input signal is

debounced and timed for a minimum of 40ms. When this

6

V2 V2

V

CC

t

1

RST

Figure 1. Reset Active Time

V1 V1

t

1

V1 = VCC TRIP POINT

V2 = VCC TRIP POINT + V

t1 = RESET ACTIVE TIME

LTC1232 • TA03

HYS

sn1232 1232fas

Page 7

WUUU

APPLICATIO S I FOR ATIO

condition is satisfied, the reset pulse generator forces the

reset outputs to active states. The reset signals will remain

active for a minimum of 250ms from the moment the

push-button reset input is released from logic low level

(see Timing Diagram).

Watchdog Timer

The LTC1232 provides a watchdog timer function to

monitor the activity of the microprocessor. If the microprocessor does not stimulate the strobe input, ST, within

a selected time-out period, the reset outputs are forced to

active states for a minimum of 250ms. The time-out period

is selected by the Time-Out Delay input, TD, to be 150ms

with TD connected to GND, 600ms with TD left floating,

and 1.2 seconds with TD connected to VCC. The 1.2 second

time-out period is adequate for many systems to serve the

watchdog timer immediately after a reset. Figure 2 shows

the timing diagram of watchdog time-out period and reset

active time. The watchdog time-out period is restarted as

LTC1232

= 5V

V

CC

ST

t

2

1

RST

t

1

t

t1 = RESET ACTIVE TIME

t2 = WATCHDOG TIME-OUT PERIOD

Figure 2. Watchdog Time-Out Period and Reset Active Time

soon as the reset outputs are inactive. When a high-to-low

transition occurs at the ST pin prior to time-out, the

watchdog time is reset and begins to time-out again. To

ensure the watchdog time does not time-out, a high-to low

transition on the ST pin must occur at or less than the

minimum time-out period. If the input to the ST pin

remains either high or low, reset pulses will be issued for

every time-out period selected by the TD pin. The watchdog timer is disabled when VCC falls below the VCC trip

point.

t

2

t

1

LTC1232 • TA04

PACKAGE DESCRIPTIO

.300 – .325

(7.620 – 8.255)

.009 – .015

(0.229 – 0.381)

+.035

.325

–.015

+0.889

8.255

()

–0.381

NOTE:

1. DIMENSIONS ARE

*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

U

INCHES

MILLIMETERS

N8 Package

8-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

.400*

(10.160)

MAX

87 6

.255 ± .015*

(6.477 ± 0.381)

12

.045 – .065

(1.143 – 1.651)

.065

(1.651)

TYP

.100

(2.54)

BSC

3

5

4

.130 ± .005

(3.302 ± 0.127)

.125

(3.175)

MIN

.018 ± .003

(0.457 ± 0.076)

.020

(0.508)

MIN

N8 0502

sn1232 1232fas

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

7

Page 8

LTC1232

PACKAGE DESCRIPTIO

.050 BSC

N

.245

MIN

1 2 3 N/2

.030 ±.005

TYP

RECOMMENDED SOLDER PAD LAYOUT

U

S8 Package

8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

.189 – .197

.045 ±.005

.160

±.005

.228 – .244

(5.791 – 6.197)

(4.801 – 5.004)

8

N

1

NOTE 3

7

2

6

3

5

N/2

4

.150 – .157

(3.810 – 3.988)

NOTE 3

.010 – .020

(0.254 – 0.508)

.008 – .010

(0.203 – 0.254)

NOTE:

1. DIMENSIONS IN

2. DRAWING NOT TO SCALE

3. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

× 45°

.016 – .050

(0.406 – 1.270)

INCHES

(MILLIMETERS)

0°– 8° TYP

.053 – .069

(1.346 – 1.752)

.014 – .019

(0.355 – 0.483)

TYP

.004 – .010

(0.101 – 0.254)

.050

(1.270)

BSC

SO8 0502

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LTC690 5V Supply Monitor, Watchdog Timer and Battery Backup 4.65V Threshold

LTC694-3.3 3.3V Supply Monitor, Watchdog Timer and Battery Backup 2.9V Threshold

LTC699 5V Supply Monitor and Watchdog Timer 4.65V Threshold

LTC1326 Micropower Precision Triple Supply Monitor for 5V, 3.3V and ADJ 4.725V, 3.118V, 1V Thresholds (±0.75%)

LTC1326-2.5 Micropower Precision Triple Supply Monitor for 2.5V, 3.3V and ADJ 2.363V, 3.118V, 1V Thresholds (±0.75%)

LTC1536 Precision Triple Supply Monitor for PCI Applications Meets PCI t

LTC1726-2.5 Micropower Triple Supply Monitor for 2.5V, 3.3V and ADJ Adjustable RESET and Watchdog Time-Outs

LTC1726-5 Micropower Triple Supply Monitor for 5V, 3.3V and ADJ Adjustable RESET and Watchdog Time-Outs

LTC1727-2.5/LTC1727-5 Micropower Triple Supply Monitor with Open-Drain Reset Individual Monitor Outputs in MSOP

LTC1728-1.8/TC1728-3.3 Micropower Triple Supply Monitor with Open-Drain Reset 5-Lead SOT-23 Package

LTC1728-2.5/LTC1728-5 Micropower Triple Supply Monitor with Open-Drain Reset 5-Lead SOT-23 Package

LTC1985-1.8 Micropower Triple Supply Monitor with Push-Pull Reset Output 5-Lead SOT-23 Package

Timing Specifications

FAIL

8

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

sn1232 1232fas

LW/TP 1002 1K REV A • PRINTED IN USA

© LINEAR TECHNOLOGY CORPORATION 1992

Loading...

Loading...