Page 1

Engineer To Engineer Note EE-189

a

Technical Notes on using Analog Devices' DSP components and development tools

Contact our technical support by phone: (800) ANALOG-D or e-mail: dsp.support@analog.com

Or vi sit ou r on-l ine re sourc es htt p:// www.analog.com/dsp and http://www.analog.com/dsp/EZAnswers

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs

Contributed by R. Murphy October 27, 2003

Introduction

Some members of the SHARC® DSP family

have Link Ports that enable point-to-point

communication between DSPs. This EE-note is

intended to supplement the existing

documentation and facilitate debugging Link

Port systems. In this EE-note we will briefly

cover the basics of using link ports, provide

some tips on link port operation across the

SHARC DSP family, and discuss the anomalies

associated with some of the Link Port

functionality.

• Suitable for long distance transfers

Sending the data along with the LACK (Link

Acknowledge) signal as well as the ability for

LACK to hold off further words lends itself to

long trace-length usage.

• Link Port Booting

The ability to boot the DSP via the link port

can further free up the external bus and allows

for complex booting schemes in which many

DSPs can be booted in sequence via link

ports, even with unique application code for

each DSP.

Why Use Link Ports?

The Basics

• Point-to-Point Inter-processor Communication

Use the Link Ports to transfer data amongst

the DSPs in the cluster, freeing up the external

port for other accesses.

• Flexible, efficient data control

Link Ports can use the core or the zerooverhead DMA controller to transfer data to /

from the DSP for efficient data I/O.

• Bi-directional communication on a single link

The Link Ports are bi-directional, so a routine

can easily switch the direction of the transfer.

• Multiple simultaneous transfers

The Link Ports allow the DSP to

communicate with other DSPs simultaneously

saving time and board layout.

Copyright 2003, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of

customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property

of their respective holders. Information furnished by Analog Devices Applications and Development Tools Engineers is believed to be accurate and reliable, however

no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices’ Engineer-to-Engineer Notes.

Link Ports Availability by DSP

ADSP-21060 & ADSP-21062:

6 Link ports, 4 bits wide, 1x or 2x core clock

ADSP-21160:

6 Link ports, 8 bits wide, up to 95* MHz

ADSP-21161:

2 Link ports, 8 bits wide, up to 100 MHz

*ADSP-21160M = 80MHZ, ADSP-21160N = 95MHz

The ADSP-2106x and ADSP-2116x Link Ports

!

are logically but not electrically compatible.

Please see EE-160 on www.analog.com/sharc

for more information on using these peripherals

together.

Page 2

A

Link Port Buffers:

These are Memory Mapped two location deep

FIFOs with support for either 32 or 48 bit words.

The user has the flexibility to assign any link

Transmitter Receiver

LDATx

Each

Link

Port

LCLKx LCLKx

LACKx LACKx

SHARC

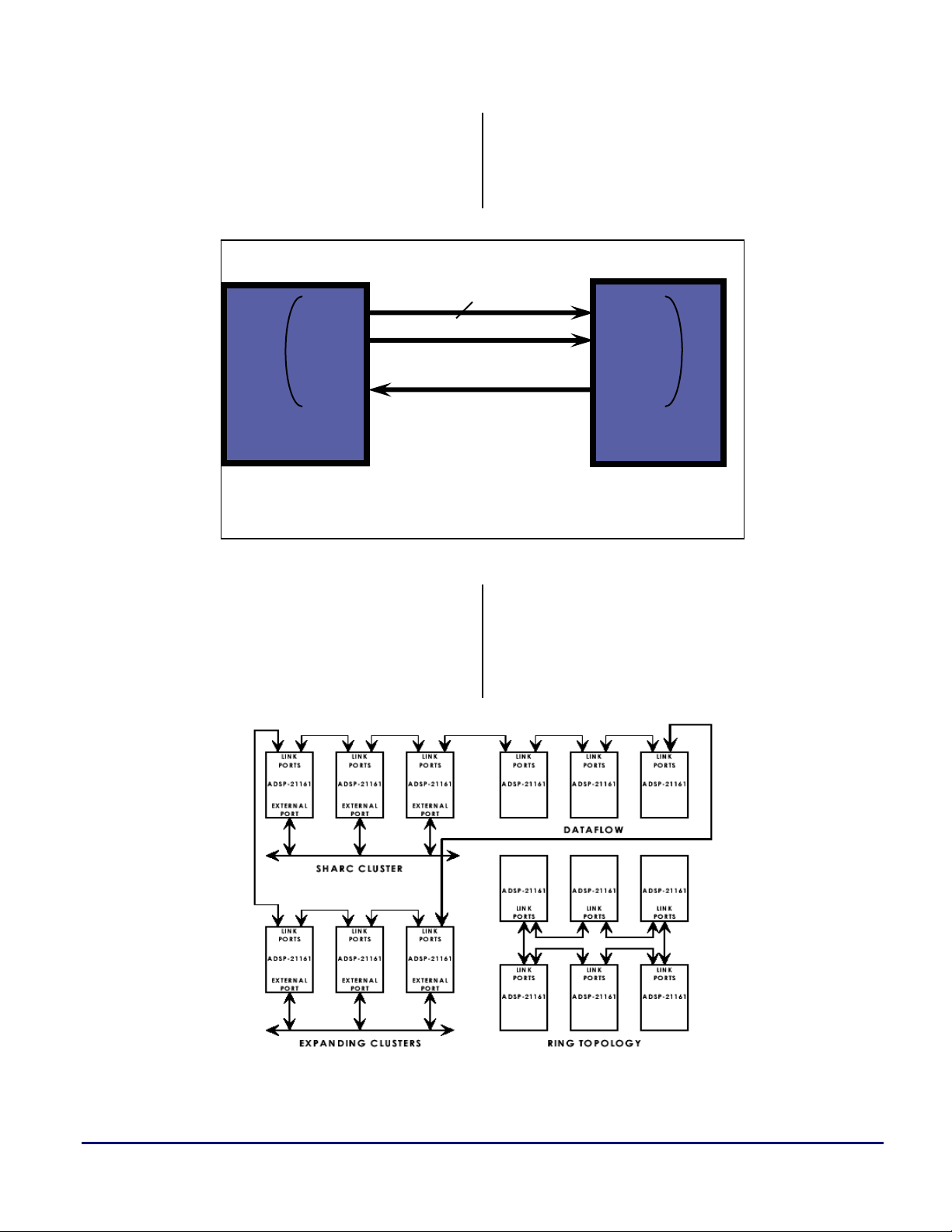

Figure 1 .Link Port Connections 21xxx DSPs

4/8

port to any link buffer, and each link buffer has a

dedicated DMA channel. In order to prevent lost

data, a read of an empty buffer or a write to a full

buffer results in core hang.

LDATx

Each

Link

Port

SHARC

Figure 1 displays the connection of the link port

signals. The data path is 4 bits wide on the

ADSP-2106x DSPs, and configurable for either 4

or 8 bits wide on the ADSP-2116x DSPs. The

LDATx and LCKx signals are driven by the

transmitter. LACKx is driven by the receiver.

Data is driven on the rising edge of LCLKx and

sampled on the falling edge. The receiver will

deassert the LACKx signal to hold off the

transfer if it’s link buffer is full.

Figure 2.Link Port Communication Examples

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs (EE-189) Page 2 of 6

Page 3

A

Figure two displays possible link port

communication schemes. It also highlights the

ability of the link ports to work in conjunction

with the External Port, to connect SHARC DSPs

within a cluster, as well as to tie clusters

together. Up to six SHARC DSPs can be used

together in a multiprocessing cluster, sharing

external memory via the external port, and

multiple clusters can be tied together using the

link ports.

Link Port Interrupts

There are three types of interrupts associated

with the Link Ports. They are DMA, Non-DMA,

and LSRQ:

DMA: An interrupts is generated at the

completion of the DMA, i.e. when the DMA

count has decremented to zero.

Non-DMA: When DMA is not enabled, a Link

Port Interrupt will be generated when the Rx

buffer is not empty or when the Tx buffer is not

full. These interrupts use the same interrupt

vector as in the DMA instance above.

LSRQ: Link Port Service Requests allows an

external device to initiate a Link Port transfer,

even though the Link Ports & Buffers are not

initialized. When the external device asserts

LxCLK or LxACK, an LSRQ interrupt is

generated. The ISR should poll the LSRQ

register to determine which Link Port to initialize

and the direction of transfer.

Link Port Registers and Settings

While most of the Link Port functionality is

shared across the SHARC family, the register

names and settings are not. Table 1 lists the

names of registers in each family. Among the

key differences to note are that the ADSP-2106x

family Link Ports supported speeds of 1x or 2x

the Core Clock rate, and the newer ADSP-2116x

DSPs support 1x, 1/2x, 1/3x, 1/4x. Also note that

the data-word width is selectable in the 2116x

family for either 4 or 8-bits.

Link Buffer Status

Port to Buffer Assignment

Word size 32/48

Transmit/Receive

DMA, Chaining

4 or 8 bit data path

LCLK rate

ADSP-2106x

LCOM, LCTL, LAR

LCOM LCOM LxSTAT bits in LCTL

LAR LAR LABx bits in LCTL

LxEXT bit in LCTL LxEXT in LCTLx LxEXT bit in LCTL

LxTRAN bit in

LCTL

LxDEN, LxCHEN

bits in LCTL

4 bits always LxDPWID in LCTLx LxDPWID bit in LCTL

1x or 2x core clock

LCLKX2x in LCOM

Table 1: Link Port Register Names

ADSP-21160

LCOM, LCTLx, LAR

LxTRAN bit in

LCTLx

LxDEN, LxCHEN

bits in LCTLx

LxCLKD bits in

LCTLx (1:1, 1:2, 1:3,

1:4)

ADSP-21161

LCTL

LxTRAN bit in LCTL

LxDEN, LxCHEN bits in LCTL

LxCLKD bits in LCTL

(1:1, 1:2, 1:3, 1:4)

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs (EE-189) Page 3 of 6

Page 4

A

Silicon Anomalies

Anomaly list for each part for further

information. This table is provided as a summary

Table 2 summarizes some of the Link-Portspecific anomalies that can cause problems if not

only. SHARC Silicon Anomaly Lists are

maintained online at www.analog.com/sharc

accommodated. Please see the respective

Anomaly Exists in Specifics Workaround

Transfers fail at 2x 21060 & 21062 (3.3

volt & 5 volt)

Throughput limited

for 32 bit transfers in

1:1 ratio

Core driven transfers

may fail if you

overrun the buffer

Change in direction

Tx --> Rx corrupts

first word

21160M, 21160N,

21161N all revisions

21160M 0.x Can’t rely on the core to hang on a

21160M 0.x 1st byte of 1st word corrupted, other

-Manifests as corrupted first nibble

of transfer

-Exacerbated by high operating

temp and asynchronous CLKINs

No data loss, just 2 cycle stall for

every other word transmitted

read/write of a empty/full buffer

data ok

-Use 1x speed

-Use 1:2, 1:3, 1:4 ratio

-Use 48 bit transfers

-Use DMA

-poll link buffer status bits

-Send a dummy word after

changing from Tx to Rx

Link to Link transfer

are not reliable at all

frequencies

Data corruption may

occur in a particular

alignment of LCLK

& CLKIN

Buffers & status bits

flaky out of /RESET

21160M all revisions Receiver sample / hold issue -See throughput table in ADSP-

21160 Datasheet

-Use ½ core clk rate

21160M all revisions,

21161N 0.3

21160M all revisions,

21161N 0.3, 1.0, 1.1,

fixed in 1.2

Table 2: Link Port-specific silicon anomalies

Typically only seen in boards where

each DSP has it’s own CLKIN

source

Affects Link ports setup as Tx only,

not Rx

-Use 1/2x, 1/3x, 1/4x ratio

-Synchronize CLKIN sources

-Setup a dummy transfer

-Write the LBUF manually with

the 1st two words to overwrite

the buffer junk

Booting

remainder of the application code one 48-bit

word at a time, using multiple transfers and

For a DSP configured to boot in Link Port mode,

Link Port 0 (Link Port 4 in ADSP-21160) is

initialized to receive via DMA channel 8 the 256

unpacking the data into instructions, and finally

it uses a DMA to overwrite itself with the

beginning of the application code.

word kernel. The boot mode is selected at reset

by the boot configuration pins. The link boot

kernel is then executed and copies in the

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs (EE-189) Page 4 of 6

The ‘master’ DSP is either booted via a Link

Port from an upstream SHARC or from an

Page 5

A

EPROM or Host. The ‘master’ can simply

includes the loader file (application code) or it

can copy it from the host or EPROM and set up a

DMA to send it out to the other DSPs Link port.

The link ports can be used in this manner to

setup to boot a large number of DSPs, each with

unique source code. The booted DSPs can in turn

boot the other DSPs in their respective clusters

via link ports or another peripheral. For more

information on booting please refer to EE-77,

SHARC Link Port Booting.

Things to watch out for

Stalls:

• -There is a 1-cycle stall incurred following 2

successive link buffer reads.

• -An N cycle stall (core hang) is incurred on a

read from an empty buffer or a write to a full

buffer.

When using DMA:

• -When the DMA completes, there are still 2

words in the Link Buffer. A write to LCTL to

• disable the link port directly following the

DMA completion will cause that data to be

lost. Instead poll the buffer status bits and

write LCTL when the buffer reports being

empty.

Misc.:

• -When using 48-bit word length at 100 MHz,

the LACK signal is de-asserted after every 48bit word transmission. (key when interfacing

to transceivers)

• -Link port cables for EZ-kits: Analog Devices

third-party Transtech-DSP (www.transtechdsp.com) sells link port cables that are

compatible with the connectors on the 2116x

ez-kits, however these cables are intended for

the ADSP-TS101S ez-kit, and will not work

with the 2116x ez-kits. Look in the resources

section at the end of this document for a link

to EE-106, a standard for cabling materials

and design that will work reliably at the

100Mhz operating frequency.

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs (EE-189) Page 5 of 6

Page 6

A

References

[1] ADSP-2106x SHARC® User’s Manual, Second Edition

[2] ADSP-21161 SHARC® DSP Hardware Reference Manual, Third Edition

Resources: (available at http://www.analog.com/SHARC)

[3] Using Token Passing to Control SHARC Link Port Bi-directional Communication (EE-16)

[4] SHARC Link Port Timing Notes (EE-41)

[5] ADSP-2106x Link Ports - Maximum Throughput (EE-47)

[6] SHARC Link Port Booting (EE-77)

[7] Link Port Open Systems Interconnect Cable Standard (EE-106)

[8] Examining ADSP-21160 Link Port Backward Compatibility to the ADSP-2106x Link Ports (EE-160)

Document History

Version Description

October 27, 2003 by R. Murphy. Revision of Anomaly Information

March 20, 2003 by R. Murphy. Initial Draft Release

Link port tips & tricks for ADSP-2106x & ADSP-2116x SHARC® DSPs (EE-189) Page 6 of 6

Loading...

Loading...