Page 1

AN-842

APPLICATION NOTE

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

AD9929: HD/CLI Timing Relationship in Slave Mode

by Scott Milne

INTRODUCTION

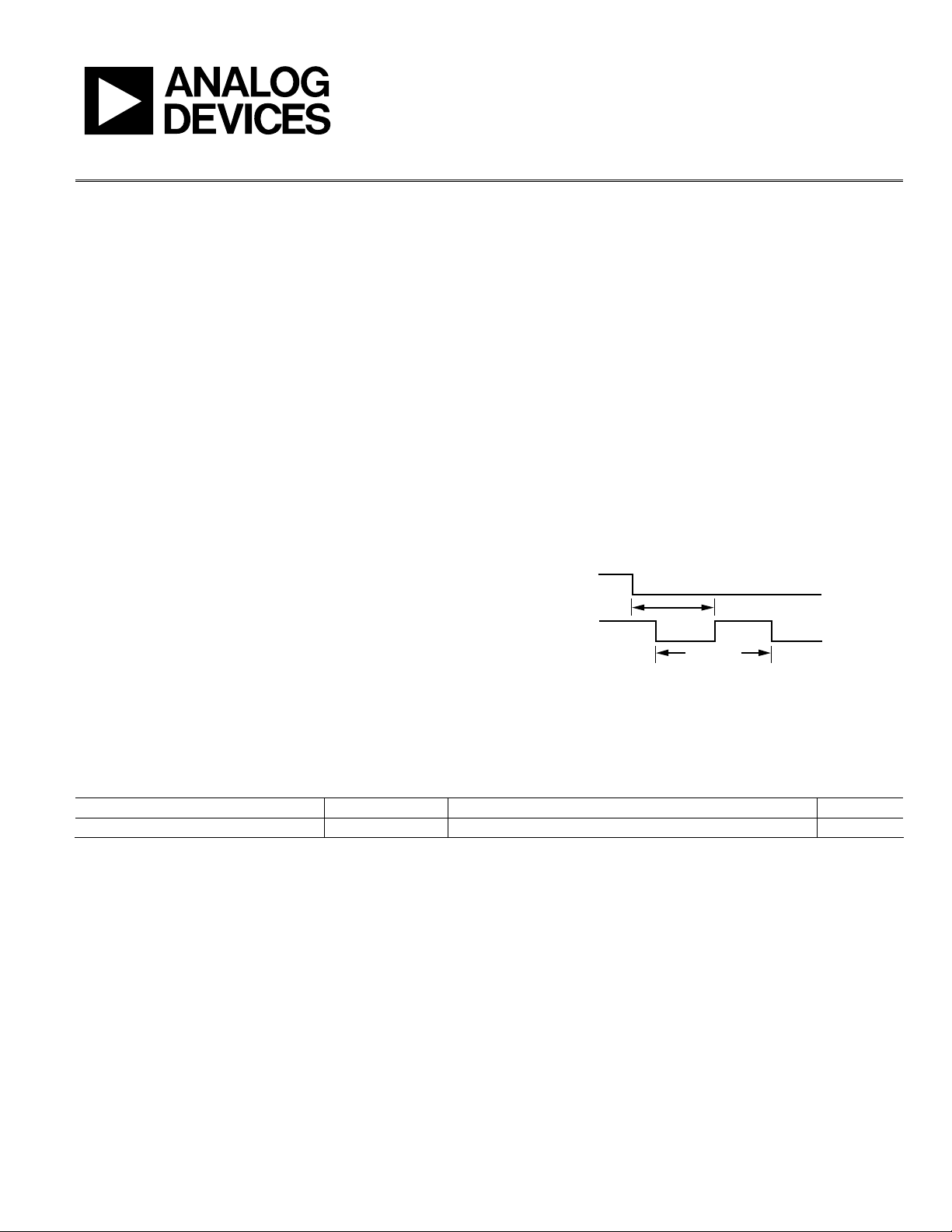

When operating the AD9929 in slave mode, the relationship

between HD and CLI is critical to insure proper resetting of the

internal counters. The HD signal is used to reset several internal

counters. Under certain timing conditions, it is possible for the

counter reset location to vary by ±1 pixel at hot or cold

temperatures.

HD AND CLI PHASE RELATIONSHIP

The external HD signal is latched by an internal clock that is

generated by a combination of the master clock, CLI, and the

value programmed to the SHDLOC register (Register 0x02,

Bits[21:16]). As shown in

from the falling edge of HD to the rising edge of CLI. This

definition is used when describing the invalid HD to CLI

relationship for a given SHDLOC value.

Figure 1, t

is defined as the time

HDCLI

For operation at 36 MHz and SHDLOC = 0x0, the invalid

values for t

are from 18.8 ns to 24.8 ns. The invalid region

HDCLI

shifts with SHDLOC and is governed by the following equations:

Minimum t

Maximum t

where 27.8 ns is the period of CLI (t

= 18.8 ns − (27.8 ns/48) × SHDLOC(decimal)

HDCLI

= 24.8 ns − (27.8 ns/48) × SHDLOC(decimal)

HDCLI

) at 36 MHz. For

CONV

example, for 36 MHz operation and SHDLOC = tap 4, the

inhibit region for t

Minimum t

Maximum t

HDCLI

HDCLI

HD

CLI

would be derived in the following way:

HDCLI

= 18.8 ns − (27.8 ns/48) × 4 = 16.5 ns

= 24.8 ns − (27.8 ns/48) × 4 = 22.5 ns

t

HDCLI

t

CONV

Figure 1. HD-to-CLI Phase Relationship

05996-001

HD-TO-CLI TIMING SPECIFICATIONS

AVDD = TCVDD = DVDD = 2.7 V to 3.6 V, −25°C to +85°C, H1BLKRETIME = 1, SHDLOC = 0.

Table 1.

Parameter Symbol Min Typ Max Unit

Invalid HD-to-CLI Timing Relationship t

HDCLI

18.8 21.8 24.8 ns

Rev. 0 | Page 1 of 2

Page 2

AN-842

NOTES

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

AN05996-0-4/06(0)

T

Rev. 0 | Page 2 of 2

TTT

Loading...

Loading...