AN-748

APPLICATION NOTE

One Technology Way

9106

www.analog.com

–0.7 ns. The negative set- up time is due to the keep out

Figure 2. DAC Timing Violating

Set-Up Time by 0.1 ns

Figure 3. DAC Timing Violating

Set-Up Time by 0.5 ns

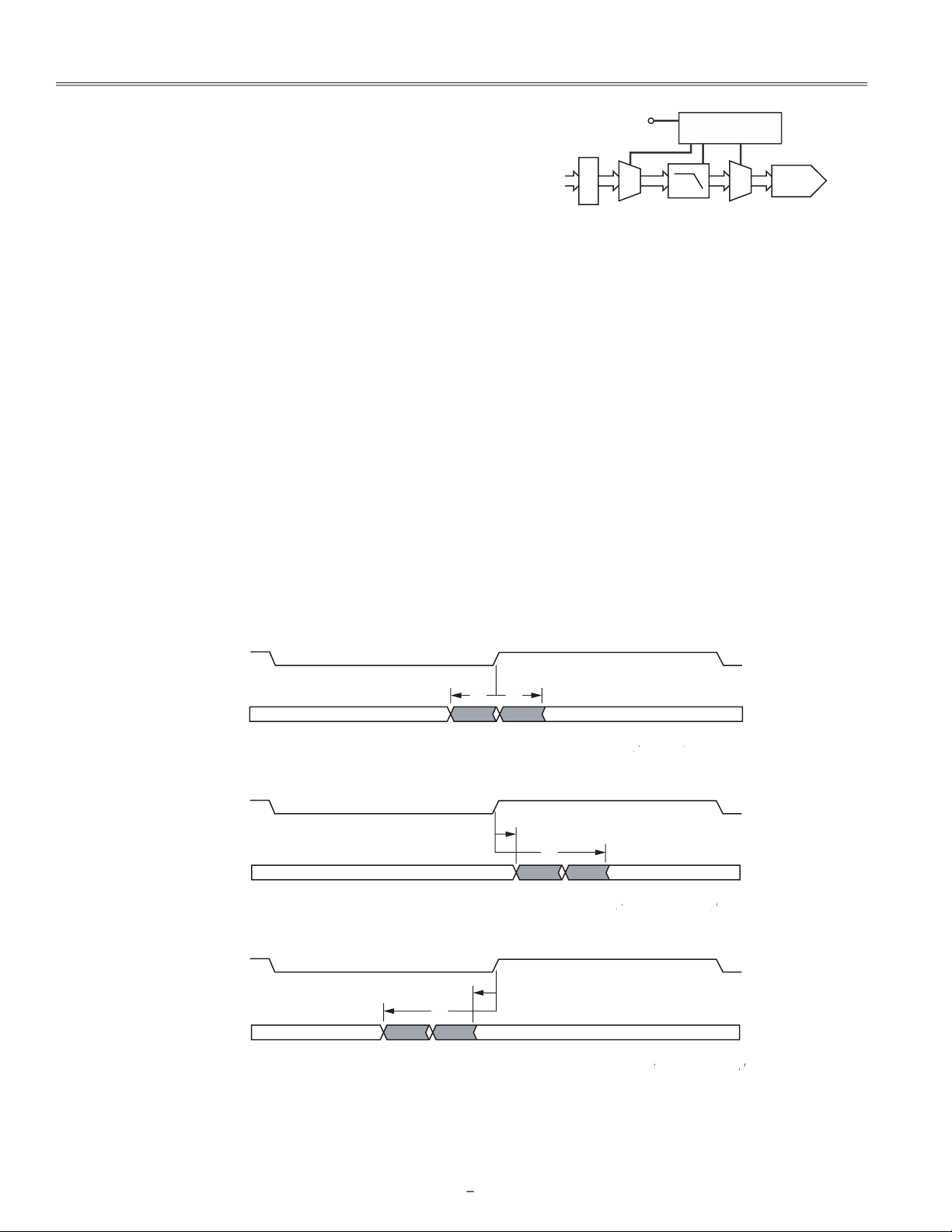

t

S

t

H

INPUT DATA

and t

and t

are both positive)

are both positive)

t

S

t

H

INPUT DATA

is negative, t

is negative, t

is positive)

is positive)

t

H

t

S

INPUT DATA

is negative)

is negative)

DAC

DATA

INPUT

DATA

TREE

INPUT

DATA

LATCH

INTERPOLATION

FILTERS

DAC

LATCH

CLOCK TREE

CLOCK INPUT

START 100kHz STOP 50MHz4.99MHz/

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

100

REF LVL

0dBm

RBW

VBW

SWT

5kHz

5kHz

5s

RF ATT

UNIT

30dB

dBm

Figure 6. DAC Timing Meeting Set-Up

and Hold Requirements

START 100kHz STOP 50MHz4.99MHz/

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–

100

REF LVL

0dBm

RBW

VBW

SWT

5kHz

5kHz

5s

RF ATT

UNIT

30dB

dBm

Figure 7. DAC Timing Violating Set-Up

and Hold Requirements by 0.1 ns

START 100kHz STOP 50MHz4.99MHz/

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–

100

REF LVL

0dBm

RBW

VBW

SWT

5kHz

5kHz

5s

RF ATT

UNIT

30dB

dBm

Figure 8. DAC Timing Violating Set-Up

and Hold Requirements by 0.5 ns

Loading...

Loading...