Page 1

AN-720

APPLICATION NOTE

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • Tel: 781/329-4700 • Fax: 781/326-8703 • www.analog.com

AD8099 Evaluation Boards

by John Ardizzoni

INTRODUCTION

The AD8099 evaluation boards are designed to help

customers quickly implement and evaluate new low

noise, low distortion op amp designs. Any of the circuit

confi gurations shown in the AD8099 data sheet can be

fabricated using the AD8099 evaluation boards. The

AD8099 evaluation boards have been designed for optimal performance and minimal layout parasitics.

There are two basic AD8099 evaluation board configurations: inverting and noninverting. These two

configurations are offered for both package types,

LFCSP and SOIC. Part numbers for the evaluation boards

can be found in Table 7 of the AD8099 data sheet, or in

Table 1 of this document.

The evaluation board features edge mounted SMA connectors at the input and output for effi cient connection

to other circuit boards or test equipment. The board is

a 2-layer PCB, with ground plane on both sides of the

board. The ground plane under the input pins has been

removed. Removing the ground plane from under the

input pins minimizes the stray capacitance at the input

of the op amp, which improves stability and reduces

peaking. The evaluation board components are SMTs

and range from 0603 to 1206 case size; the electrolytic

bypass capacitors, C1–C4, are 3528 case size.

Supply bypassing for the AD8099 is a key consideration

for optimal circuit performance, especially when distortion is of concern. The AD8099 uses a combination of

common-mode bypassing (a capacitor between the two

power supplies) and shunt bypassing (from the power

supply pins of the amplifi er to ground). The evaluation

board schematics show the bypassing schemes in detail,

in Figures 1, 4, 7, and 10.

Since the AD8099 is ex ternally compensated and has

a large gain bandwidth product, the component values

and placement are critical. The AD8099 data sheet features a detailed section on the compensation networks

and component values. In low gain confi gurations (G =

+2), the compensation network consists of three components, a series-parallel combination of resistor and

capacitors to the negative supply. To min imize stray

capacitance, the evaluation board provides only one set

of mounting pads for the parallel components. Therefore,

the parallel combination of resistor and capacitor (R7 and

C

for the SOIC boards and RC, CP for the LFCSP boards)

P

must be soldered one on top of the other. Figure 13 illustrates the proper mounting confi guration. The previously

mentioned reference designators correspond to R

C1, found in the AD8099 data sheet.

The AD8099 output does not drive signifi cant values of

load capacitance (>5 pF); therefore the output connections should be kept short, direct, and terminated when

appropriate. Larger values of capacitance may be driven

by placing a series resistor (25 ⍀ to 50 ⍀ ) into the R5

position. This will help isolate the capacitive loading effects at the output of the AD8099. Minimizing the output

capacitance will help ensure stability while minimizing

peaking and ringing.

and

C

REV. A

Page 2

AN-720

R3

IN

R1

*

AGND

*USER DEFINED VALUE

**0508 CASE SIZE

+V

S

C2**

0.1F

C1

10F

AGND

R4

*

1

2

10F

3

4

C4

AGND

*

R2

*

FEEDBACK

–IN

+IN

–V

S

C3

*

–V

U1

DEV

S

DISABLE

+V

V

OUT

C

P

R7

*

C5**

0.1F

8

7

S

6

5

C

C

C6

10F

AGND

R5

*

DIS

AGND

R6

*

GND1

OUT

GND3GND2

AGND

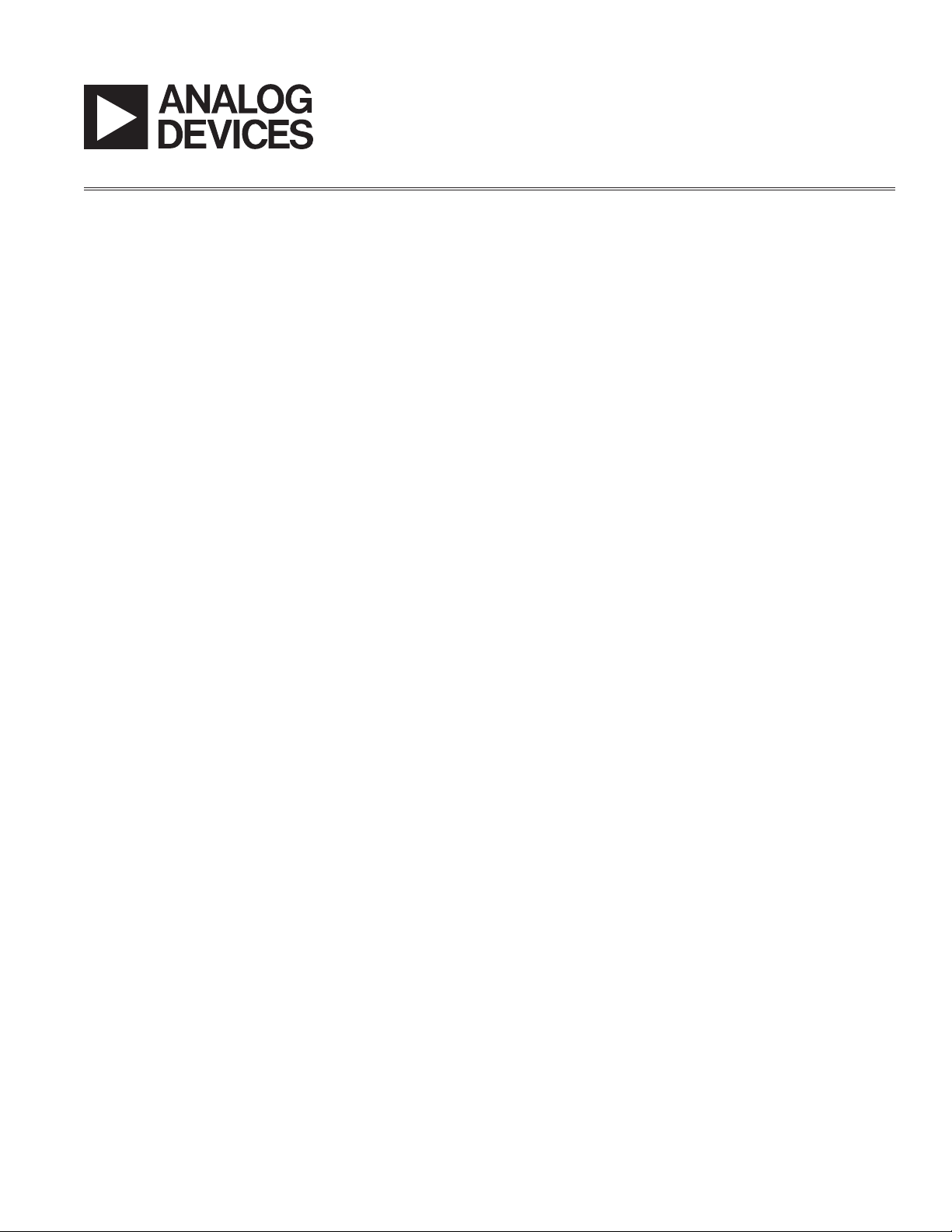

Figure 1. Noninverting Schematic (SOIC)

C6

COMPONENT SIDE CIRCUIT SIDE

Figure 2. Board Assembly Drawings (SOIC)

Figure 3. Board Layout Patterns (SOIC)

–2–

REV. A

Page 3

AN-720

IN

R3

R1

*

AGND AGND

*USER DEFINED VALUE

**0508 CASE SIZE

+V

S

C2**

0.1F

C1

10F

AGND

R4

*

1

2

10F

3

4

C4

AGND

*

R2

*

FEEDBACK

–IN

+IN

–V

S

C3

*

–V

U1

DEV

S

DISABLE

+V

V

OUT

C

P

R7

*

C5**

0.1F

8

7

S

6

5

C

C

C6

10F

AGND

R5

*

DIS

AGND

GND1

OUT

R6

*

GND3GND2

AGND

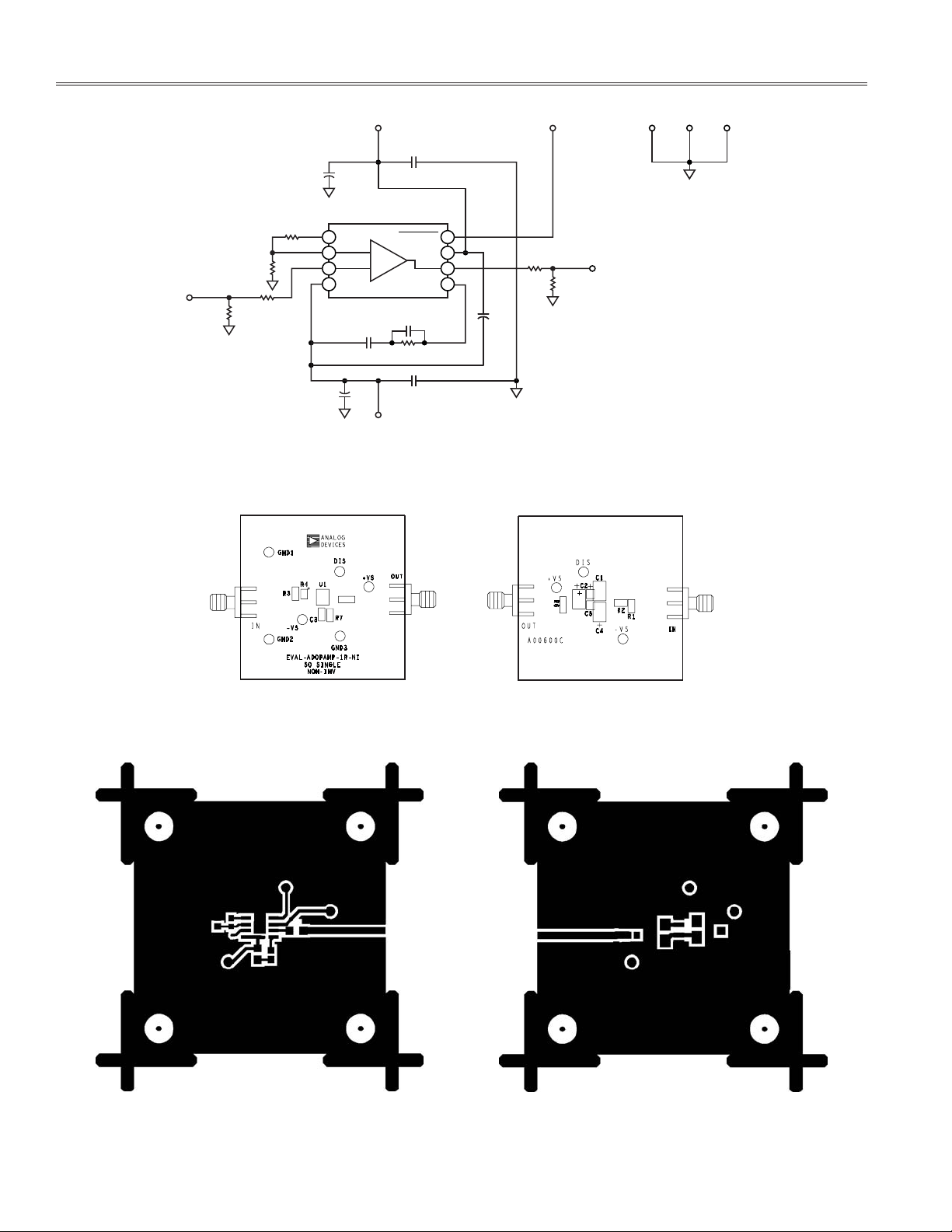

Figure 4. Inverting Schematic (SOIC)

C6

COMPONENT SIDE CIRCUIT SIDE

Figure 5. Board Assembly Drawings (SOIC)

REV. A

Figure 6. Board Layout Patterns (SOIC)

–3–

Page 4

AN-720

IN

R1P

R2

*

*

AGND

AGND

*USER DEFINED VALUE

**0508 CASE SIZE

+V

S

C2**

0.1F

C1

10F

DIS

R3

*

1

R1

*

R4

*

DISABLE

2

FEEDBACK

–IN

3

+IN

4

AGND

U1

8

+V

S

V

OUT

7

6

C

C

5

–V

S

–V

S

10F

C4

AGND

AGND

R5

C3

AGND

*

AGND

R6

*

C

P

*

R

C

*

10F

C

C

*

C5**

0.1F

GND1 GND4GND2

OUT

GND3

AGND

Figure 7. Noninverting Schematic (CSP)

COMPONENT SIDE CIRCUIT SIDE

Figure 8. Board Assembly Drawing (CSP)

Figure 9. Board Layout Patterns (CSP)

–4–

REV. A

Page 5

AN-720

+V

S

C2**

0.1F

C1

10F

DIS

R3

*

1

R1

*

IN

R1P

R2

*

*

AGND

AGND

*USER DEFINED VALUE

**0508 CASE SIZE

R4

*

DISABLE

2

FEEDBACK

–IN

3

+IN

4

AGND

U1

8

+V

S

V

OUT

7

6

C

C

5

–V

S

C4

10F

AGND

AGND

R5

C3

AGND

*

AGND

R6

*

C

P

*

R

C

*

10F

C

C

*

C5**

0.1F

–V

S

GND1 GND4GND2

OUT

Figure 10. Inverting Schematic (CSP)

GND3

AGND

COMPONENT SIDE CIRCUIT SIDE

Figure 11. Board Assembly Drawing (CSP)

Figure 12. Board Layout Patterns (CSP)

REV. A

–5–

Page 6

AN-720

RC(R7)

MOUNTING PADS

PCB

C

C

Figure 13. Soldering of Two Parallel Components

Table 1. Evaluation Board Selection Guide

Package Type

Board Confi guration CSP SOIC

Inverting EVAL-ADOPAMP-1CP-I EVAL-ADOPAMP-1R-IN

Noninverting EVAL-ADOPAMP-1CP-N EVAL-ADOPAMP-1R-NI

SOLDER TERMINATOR

SOLDER

SOLDER TERMINATOR

–6–

REV. A

Page 7

–7–

Page 8

AN04805–0–7/04(A)

© 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

–8–

Loading...

Loading...