Multiformat HDTV Encoder with

a

FEATURES

INPUT FORMATS

YCrCb in 2 10-Bit (4:2:2) or 3 10-Bit (4:4:4) Format

Compliant to SMPTE274M (1080i), SMPTE296M

(720p) and Any Other High-Definition Standard Using

Async Timing Mode

RGB in 3 10-Bit 4:4:4 Format

OUTPUT FORMATS

YPrPb HDTV (EIA-770.3)

RGB Levels Compliant to RS-170 and RS-343A

11-Bit + Sync (DAC A)

11-Bit DACs (DAC B, C)

PROGRAMMABLE FEATURES

Internal Test Pattern Generator with Color Control

Y/C Delay ()

Individual DAC On/Off Control

VBI Open Control

2

C Filter

I

2-Wire Serial MPU Interface

Single Supply 5 V/3.3 V Operation

52-Lead MQFP Package

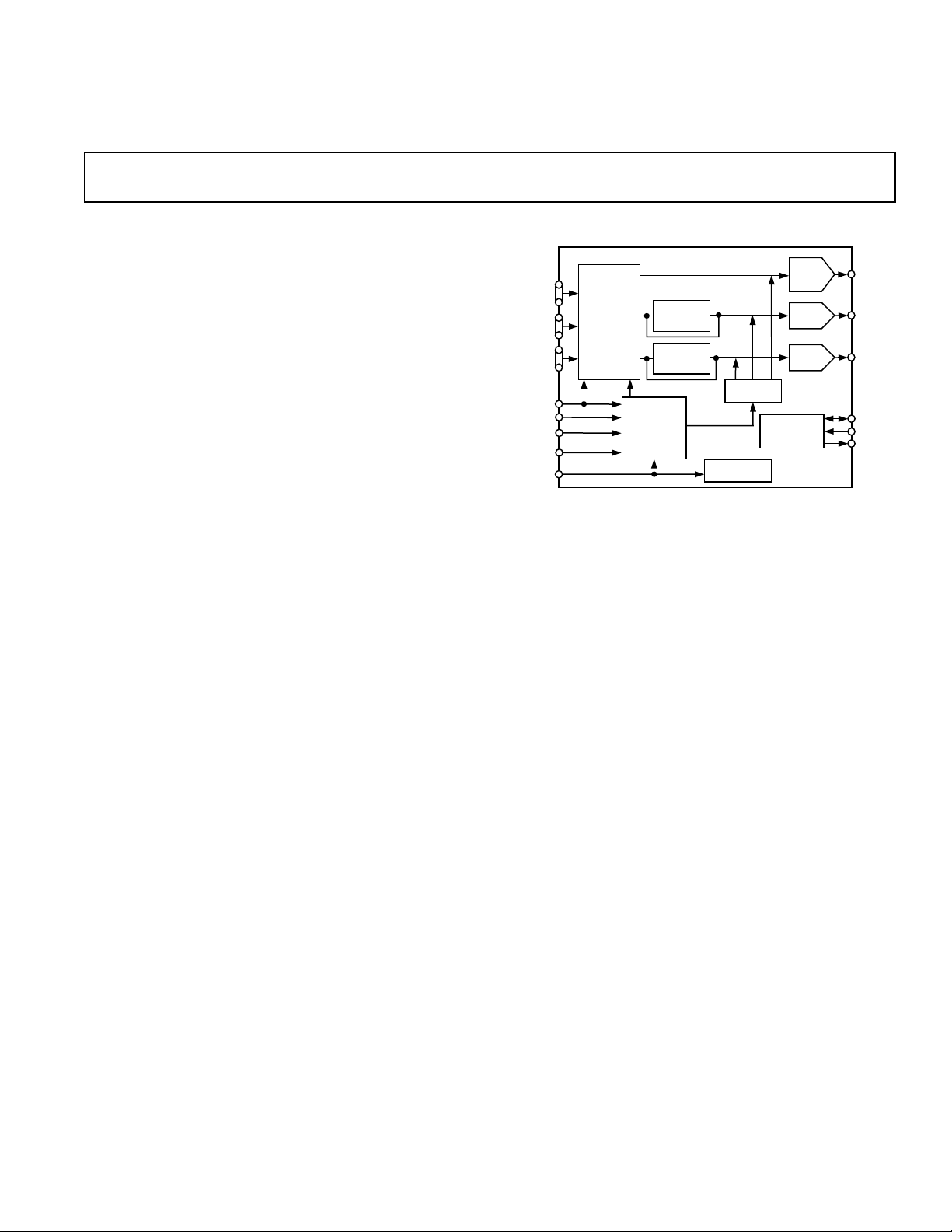

Y0–Y9

Cr0–Cr9

Cb0–Cb9

CLKIN

HORIZONTAL

SYNC

VERTICAL

SYNC

BLANKING

RESET

Three 11-Bit DACs

ADV7197

FUNCTIONAL BLOCK DIAGRAM

11-BIT

+ SYNC

DAC

TEST

PATTERN

GENERATOR

AND

DELAY

CHROMA

4:2:2 TO 4:4:4

CHROMA

4:2:2 TO 4:4:4

TIMING

GENERATOR

(SSAF)

(SSAF)

SYNC

GENERATOR

I2C MPU

PORT

11-BIT

DAC

11-BIT

DAC

DAC CONTROL

BLOCK

ADV7197

DAC A ( Y)

DAC B

DAC C

V

REF

R

SET

COMP

APPLICATIONS

HDTV Display Devices

HDTV Projection Systems

Digital Video Systems

High Resolution Color Graphics

Image Processing/Instrumentation

Digital Radio Modulation/Video Signal Reconstruction

GENERAL DESCRIPTION

The ADV7197 is a triple, high-speed, digital-to-analog encoder

on a single monolithic chip. It consists of three high-speed video

D/A converters with TTL-compatible inputs.

The ADV7197 has three separate 10-bit-wide input ports that

accept data in 4:4:4 10-bit YCrCb or RGB, or 4:2:2 10-bit

YCrCb. This data is accepted in HDTV format at 74.25 MHz

or 74.1758 MHz. For any other high definition standard but

SMPTE274M or SMPTE296M, the Async Timing Mode can

be used to input data to the ADV7197. For all standards,

*ADV is a registered trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

external horizontal, vertical, and blanking signals or EAV/SAV

codes control the insertion of appropriate synchronization signals

into the digital data stream and therefore the output signals.

The ADV7197 outputs analog YPrPb HDTV complying to

EIA-770.3, or RGB complying to RS-170/RS-343A.

The ADV7197 requires a single 5 V/3.3 V power supply, an

optional external 1.235 V reference, and a 74.25 MHz (or

74.1758 MHz) clock.

The ADV7197 is packaged in a 52-lead MQFP package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

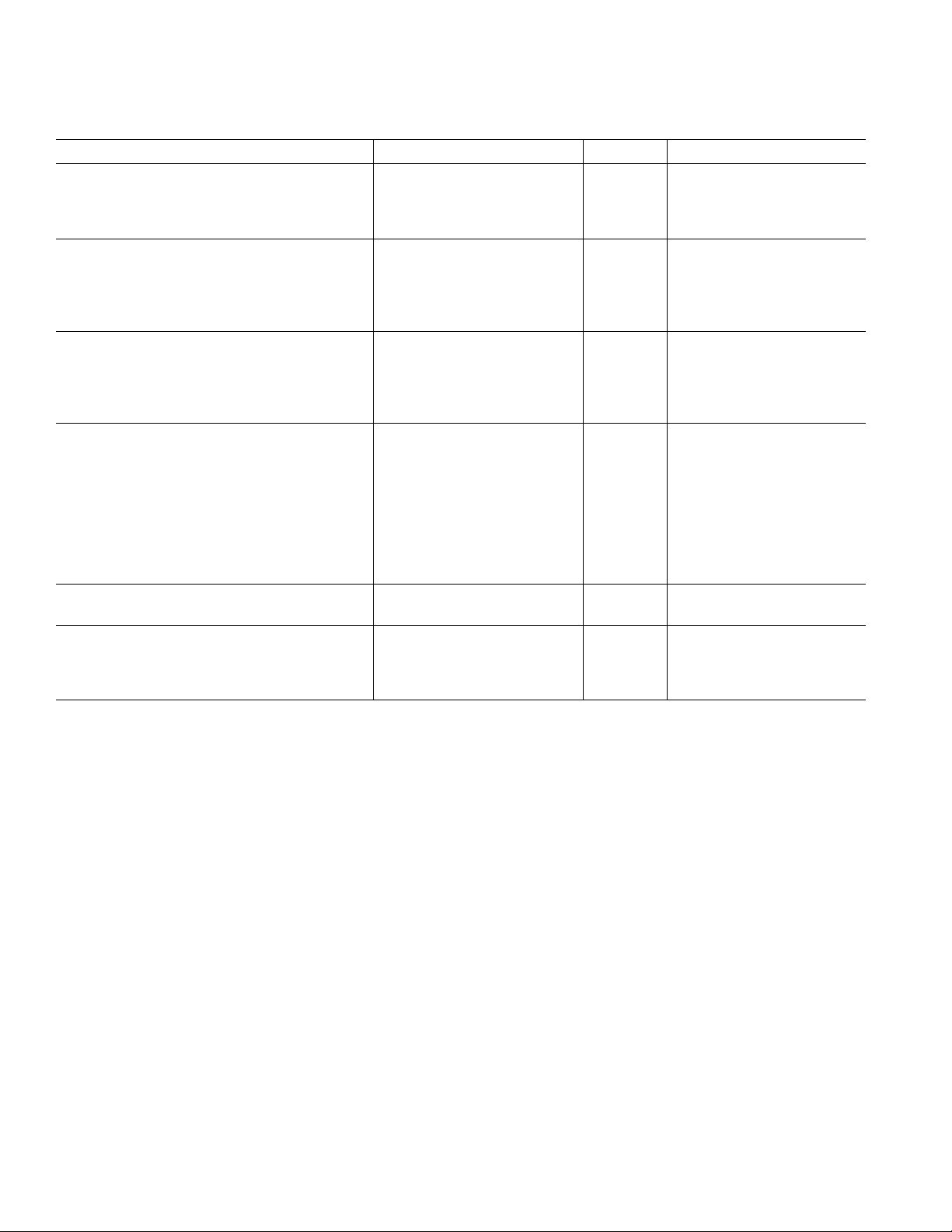

ADV7197–SPECIFICATIONS

(VAA = 4.75 V to 5.25 V, V

1

5 V SPECIFICATIONS

70C] unless otherwise noted.)

Parameter Min Typ Max Unit Test Conditions

STATIC PERFORMANCE

Resolution 11 Bits

Integral Nonlinearity 1.5 LSB

Differential Nonlinearity 0.9 2.0 LSB Guaranteed Monotonic

DIGITAL OUTPUTS

Output High Voltage, V

Output Low Voltage, V

OH

OL

Three-State Leakage Current 10 µAV

Three-State Output Capacitance 4 pF

DIGITAL AND CONTROL INPUTS

Input High Voltage, V

Input Low Voltage, V

IH

IL

Input Leakage Current 0 1 µAV

Input Capacitance, C

IN

ANALOG OUTPUTS

Full-Scale Output Current 3.92 4.25 4.56 mA DAC A

Output Current Range 3.92 4.25 4.56 mA DAC A

DAC-to-DAC Matching 1.4 % DAC A, B, C

Output Compliance Range, V

Output Impedance, R

OUT

Output Capacitance, C

OC

OUT

VOLTAGE REFERENCE (External and Internal)

Reference Range, V

POWER REQUIREMENTS

2

I

DD

3, 4

I

AA

REF

Power Supply Rejection Ratio 0.01 %/%

NOTES

1

Guaranteed by characterization.

2

IDD or the circuit current is the continuous current required to drive the digital core.

3

IAA is the total current required to supply all DACs including V

4

All DACs on.

Specifications subject to change without notice.

REF

= 1.235 V, R

REF

2.4 V I

= 2470 , R

SET

LOAD

0.4 V I

= 300 . All specifications T

= 400 µA

SOURCE

= 3.2 mA

SINK

= 0.4 V

IN

2.0 V

0.8 V

= 0.4 V or 2.4 V

IN

4pF

2.54 2.83 3.11 mA DAC B, C

2.39 2.66 2.93 mA DAC B, C

1.4 V

100 kΩ

7pF

1.112 1.235 1.359 V

96 102 mA With f

CLK

11 15 mA

circuitry.

to T

MIN

= 74.25 MHz

MAX

[0C to

–2–

REV. 0

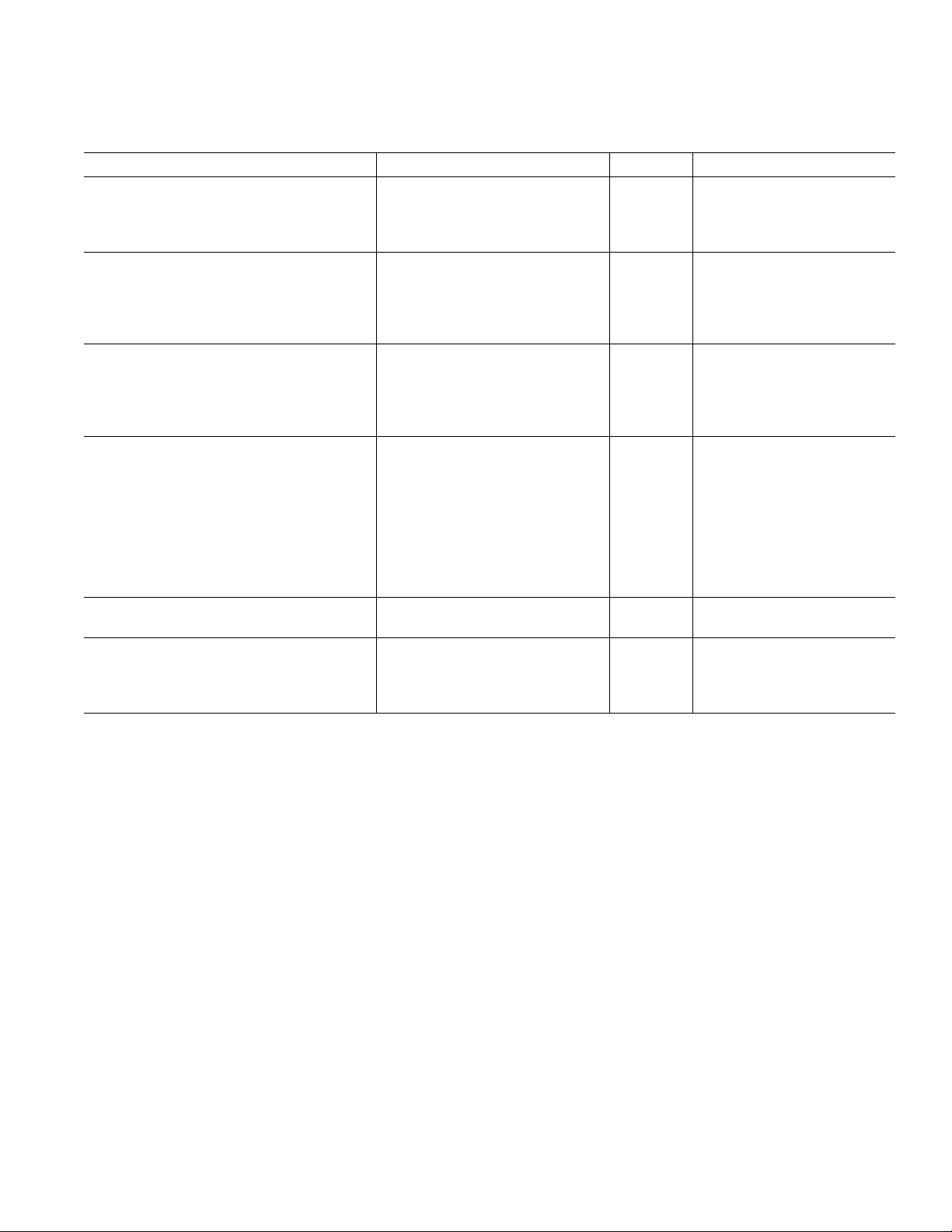

ADV7197

3.3 V SPECIFICATIONS

(VAA = 3.15 V to 3.45 V, V

1

to 70C] unless otherwise noted.)

= 1.235 V, R

REF

= 2470 , R

SET

= 300 . All specifications T

LOAD

Parameter Min Typ Max Unit Test Conditions

STATIC PERFORMANCE

Resolution 11 Bits

Integral Nonlinearity 1.5 LSB

Differential Nonlinearity 0.9 2.0 LSB

DIGITAL OUTPUTS

Output High Voltage, V

Output Low Voltage, V

OH

OL

Three-State Leakage Current 10 µAV

2.4 V I

0.4 V I

SOURCE

= 3.2 mA

SINK

= 0.4 V

IN

= 400 µA

Three-State Output Capacitance 4 pF

DIGITAL AND CONTROL INPUTS

Input High Voltage, V

Input Low Voltage, V

IH

IL

Input Leakage Current 0 1 µAV

Input Capacitance, C

IN

2V

0.8 0.65 V

= 0.4 V or = 2.4 V

IN

4pF

ANALOG OUTPUTS

Full-Scale Output Current 3.92 4.25 4.56 mA DAC A

2.54 2.83 3.11 mA DAC B, C

Output Current Range 3.92 4.25 4.56 mA DAC A

2.39 2.66 2.93 mA DAC B, C

DAC-to-DAC Matching 1.4 % DAC A, B, C

Output Compliance Range, V

Output Impedance, R

OUT

Output Capacitance, C

OC

OUT

0 1.4 V

100 kΩ

7pF

VOLTAGE REFERENCE (External)

Reference Range, V

POWER REQUIREMENTS

2

I

DD

3, 4

I

AA

REF

1.112 1.235 1.359 V

46 mA With f

11 15 mA

= 74.25 MHz

CLK

Power Supply Rejection Ratio 0.01 %/%

NOTES

1

Guaranteed by characterization.

2

IDD or the circuit current is the continuous current required to drive the digital core.

3

IAA is the total current required to supply all DACs including V

4

All DACs on.

Specifications subject to change without notice.

circuitry.

REF

MIN

to T

MAX

[0C

REV. 0

–3–

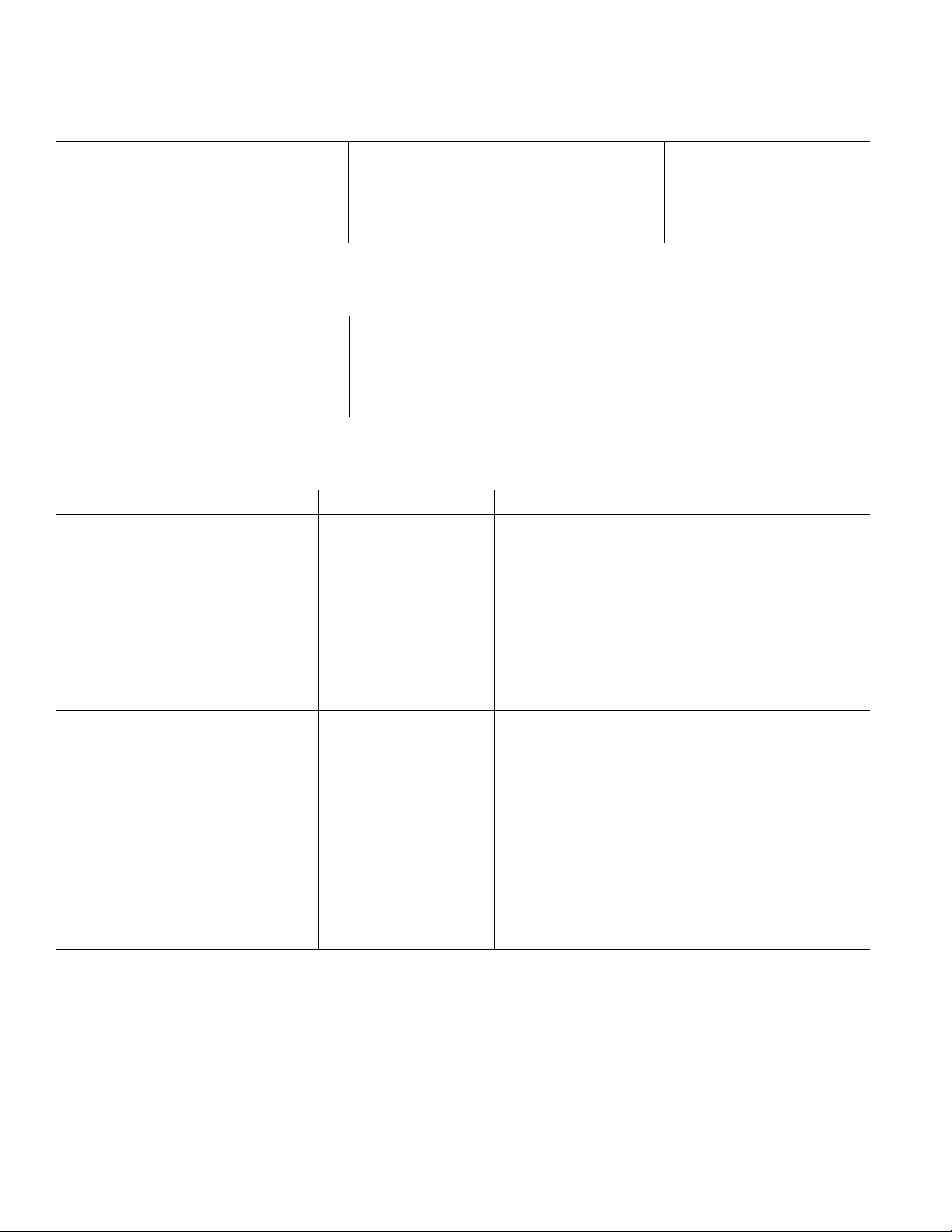

ADV7197–SPECIFICATIONS

(VAA = 4.75 V to 5.25 V, V

to T

5 V DYNAMIC–SPECIFICATIONS

[0C to 70C] unless otherwise noted.)

MAX

Parameter Min Typ Max Unit

Luma Bandwidth 13.5 MHz

Chroma Bandwidth 6.75 MHz

Signal-to-Noise Ratio 64 dB Luma Ramp Unweighted

Chroma/Luma Delay Inequality 0 ns

Specifications subject to change without notice.

= 1.235 V, R

REF

= 2470 , R

SET

= 300 . All specifications T

LOAD

MIN

3.3 V DYNAMIC–SPECIFICATIONS

(VAA = 3.15 V to 3.45 V, V

T

to T

MIN

[0C to 70C] unless otherwise noted.)

MAX

= 1.235 V, R

REF

= 2470 , R

SET

= 300 . All specifications

LOAD

Parameter Min Typ Max Unit

Luma Bandwidth 13.5 MHz

Chroma Bandwidth 6.75 MHz

Signal-to-Noise Ratio 64 dB Luma Ramp Unweighted

Chroma/Luma Delay Inequality 0 ns

Specifications subject to change without notice.

(VAA = 4.75 V to 5.25 V, V

5 V TIMING–SPECIFICATIONS

P

arameter Min Typ Max Unit Conditions

MPU PORT

1

to T

[0C to 70C] unless otherwise noted.)

MAX

= 1.235 V, R

REF

= 2470 , R

SET

= 300 . All specifications T

LOAD

MIN

SCLOCK Frequency 10 400 kHz

SCLOCK High Pulsewidth, t

SCLOCK Low Pulsewidth, t

Hold Time (Start Condition), t

Setup Time (Start Condition), t

Data Setup Time, t

5

SDATA, SCLOCK Rise Time, t

SDATA, SCLOCK Fall Time, t

Setup Time (Stop Condition), t

1

2

3

4

6

7

8

0.6 µs

1.3 µs

0.6 µs After This Period the 1st Clock Is Generated

0.6 µs Relevant for Repeated Start Condition

100 ns

300 ns

300 ns

0.6 µs

RESET Low Time 100 ns

ANALOG OUTPUTS

Analog Output Delay

2

10 ns

Analog Output Skew 0.5 ns

CLOCK CONTROL AND PIXEL PORT

f

CLK

t

CLK

Clock High Time, t

Clock Low Time, t

Data Setup Time, t

Data Hold Time, t

Control Setup Time, t

Control Hold Time, t

9

10

11

12

11

12

3

74.25 MHz HDTV Mode

81 MHz Async Timing Mode

5 1.5 ns

5 2.0 ns

2.0 ns

4.5 ns

7ns

4.0 ns

Pipeline Delay 16 Clock Cycles For 4:4:4 Pixel Input Format

NOTES

1

Guaranteed by characterization.

2

Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of DAC output full-scale transition.

3

Data: Cb/Cr (9:0), Cr (9:0), Y (9:0); Control: HSYNC/SYNC, VSYNC/TSYNC; DV

Specifications subject to change without notice.

–4–

REV. 0

ADV7197

(VAA = 3.15 V to 3.45 V, V

T

to T

3.3 V TIMING–SPECIFICATIONS

P

arameter Min Typ Max Unit Conditions

MPU PORT

1

MIN

[0C to 70C] unless otherwise noted.)

MAX

= 1.235 V, R

REF

= 2470 , R

SET

= 300 . All specifications

LOAD

SCLOCK Frequency 10 400 kHz

SCLOCK High Pulsewidth, t

SCLOCK Low Pulsewidth, t

Hold Time (Start Condition), t

Setup Time (Start Condition), t

Data Setup Time, t

5

SDATA, SCLOCK Rise Time, t

SDATA, SCLOCK Fall Time, t

Setup Time (Stop Condition), t

1

2

3

4

6

7

8

0.6 µs

1.3 µs

0.6 µs After This Period the 1st Clock Is Generated

0.6 µs Relevant for Repeated Start Condition

100 ns

300 ns

300 ns

0.6 µs

RESET Low Time 100 ns

ANALOG OUTPUTS

2

Analog Output Delay 10 ns

Analog Output Skew 0.5 ns

CLOCK CONTROL AND PIXEL PORT

f

CLK

t

CLK

Clock High Time, t

Clock Low Time, t

Data Setup Time, t

Data Hold Time, t

Control Setup Time, t

Control Hold Time, t

9

10

11

12

11

12

3

74.25 MHz HDTV Mode

81 MHz Async Timing Mode

51.5 ns

52.0 ns

2.0 ns

4.5 ns

7ns

4.0 ns

Pipeline Delay 16 Clock Cycles For 4:4:4 Pixel Input Format

NOTES

1

Guaranteed by characterization.

2

Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of DAC output full-scale transition.

3

Data: Cb/Cr (9:0), Cr (9:0), Y (9:0); Control: HSYNC/SYNC, VSYNC/TSYNC; DV

Specifications subject to change without notice.

REV. 0

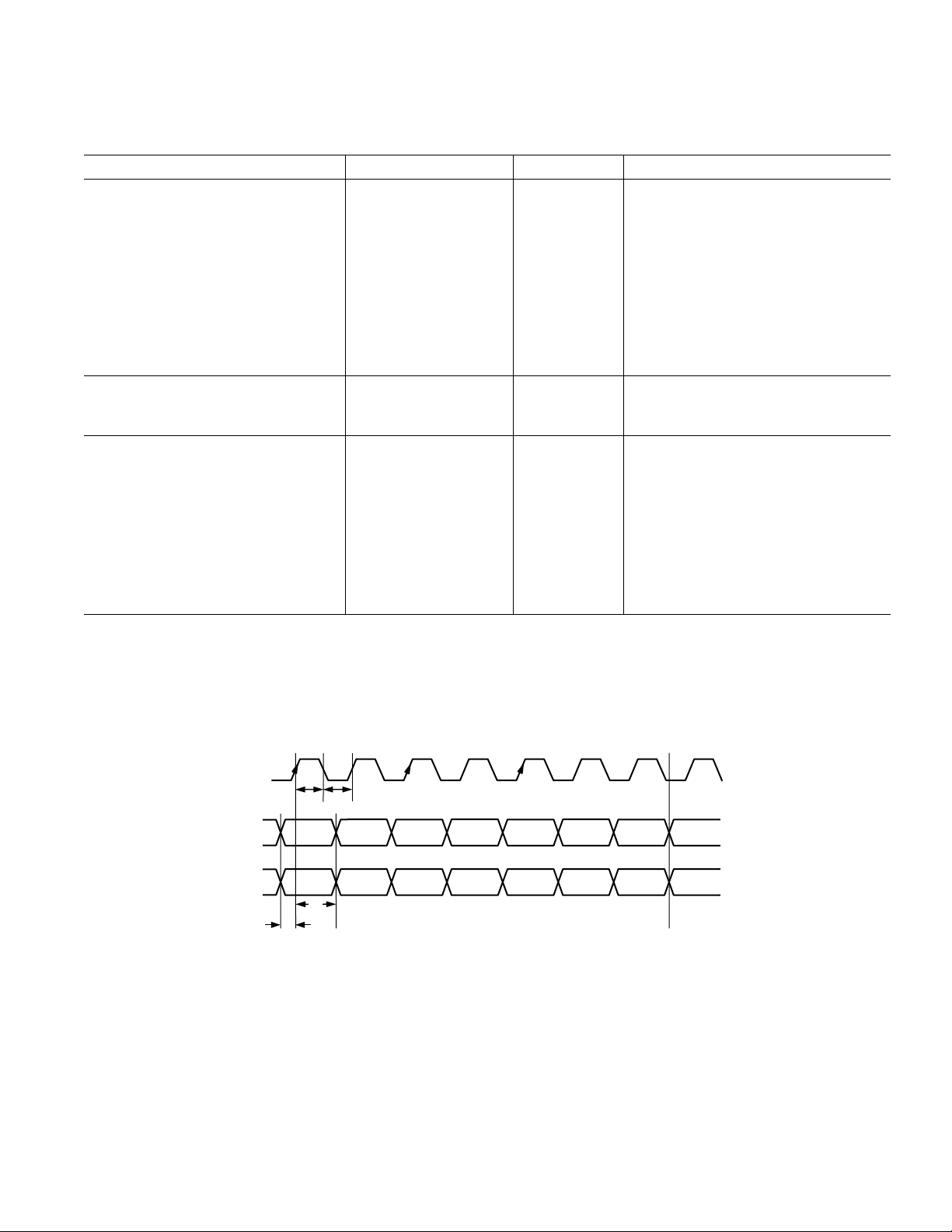

CLOCK

PIXEL INPUT

DATA

t

t

9

10

Y0

Cb0

t

t

11

Y1

Cr0

12

Y2

Cb1 Cr1

...

...

...

Figure 1. 4:2:2 Input Data Format Timing Diagram

–5–

Yxxx

Cbxxx

Yxxx

Crxxx

– CLOCK HIGH TIME

t

9

– CLOCK LOW TIME

t

10

– DATA SETUP TIME

t

11

– DATA HOLD TIME

t

12

ADV7197

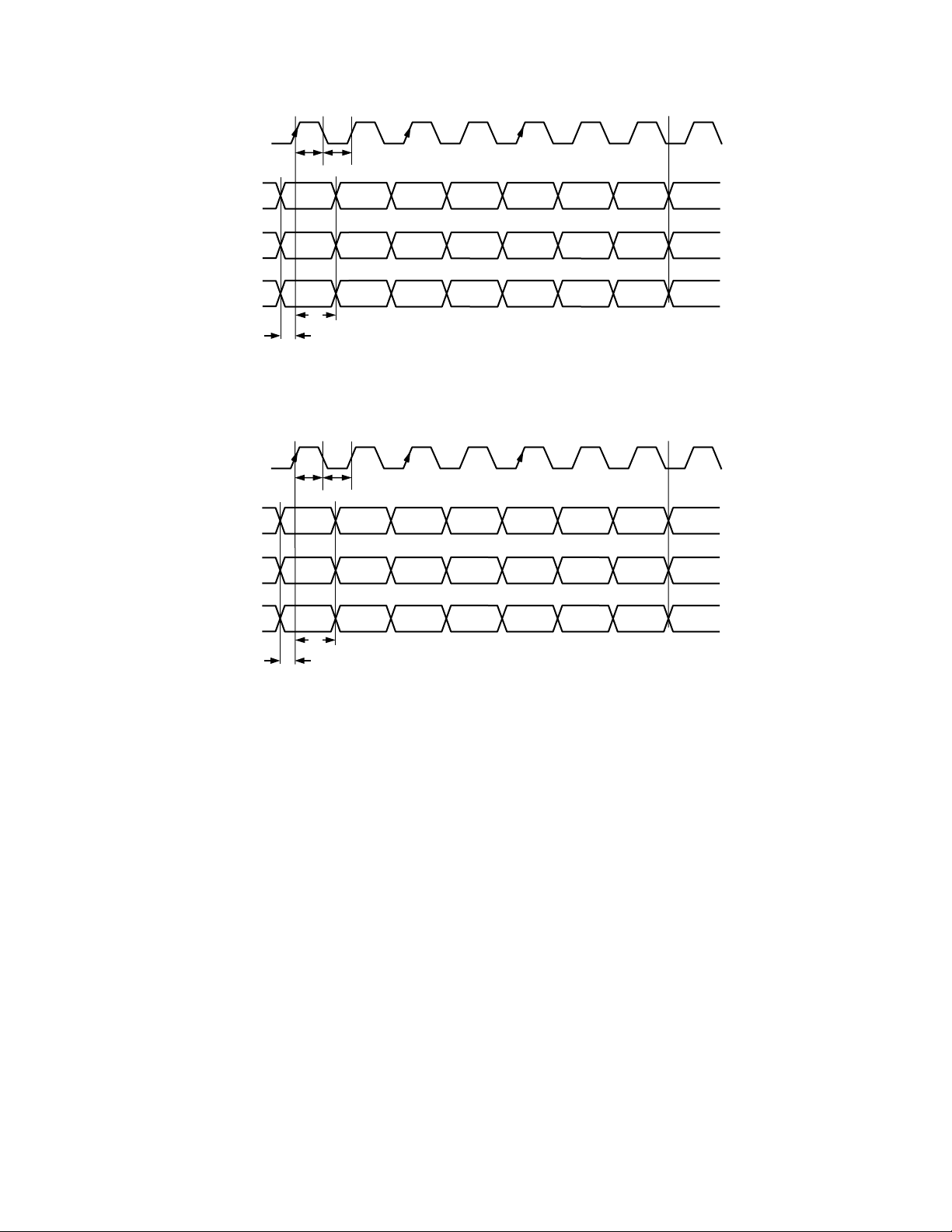

CLOCK

t

t

9

10

PIXEL INPUT

DATA

CLOCK

PIXEL INPUT

DATA

Y0

Cb0

Cr0 Cr1 Cr2 Cr3 ... Crxxx

t

t

11

Y1

Cb1

12

Y2

Cb2 Cb3

... ...

Yxxx

...

Cbxxx

Yxxx

Cbxxx

Crxxx

t

– CLOCK HIGH TIME

9

t

– CLOCK LOW TIME

10

t

– DATA SETUP TIME

11

t

– DATA HOLD TIME

12

Figure 2. 4:4:4 YCrCb Input Data Format Timing Diagram

t

t

9

10

R0

G0

B0 B1 B2 B3 ... Bxxx

t

t

11

R1

G1

12

R2

G2 G3

... ...

Rxxx

...

Gxxx

Rxxx

Gxxx

Bxxx

t

– CLOCK HIGH TIME

9

t

– CLOCK LOW TIME

10

t

– DATA SETUP TIME

11

t

– DATA HOLD TIME

12

Figure 3. 4:4:4 RGB Input Data Format Timing Diagram

–6–

REV. 0

Loading...

Loading...