192-Bit, 360 MHz True-Color

a

FEATURES

192-Bit Pixel Port Allows 2048 3 2048 3 24 Screen

Resolution

360 MHz, 24-Bit True-Color Operation

Triple 8-Bit D/A Converters

8:1 Multiplexing

Onboard PLL

RS-343A/RS-170 Compatible Analog Outputs

TTL Compatible Digital Inputs

Internal Voltage Reference

Standard 8-Bit MPU I/O Interface

DAC-DAC Matching: Typ 2%, Adjustable to 0.02%

+5 V CMOS Monolithic Construction

304-Pin PQFP Package

APPLICATIONS

Ultrahigh Resolution Color Graphics

Image Processing

Drives 24-Bit Color 2K 3 2K Monitors

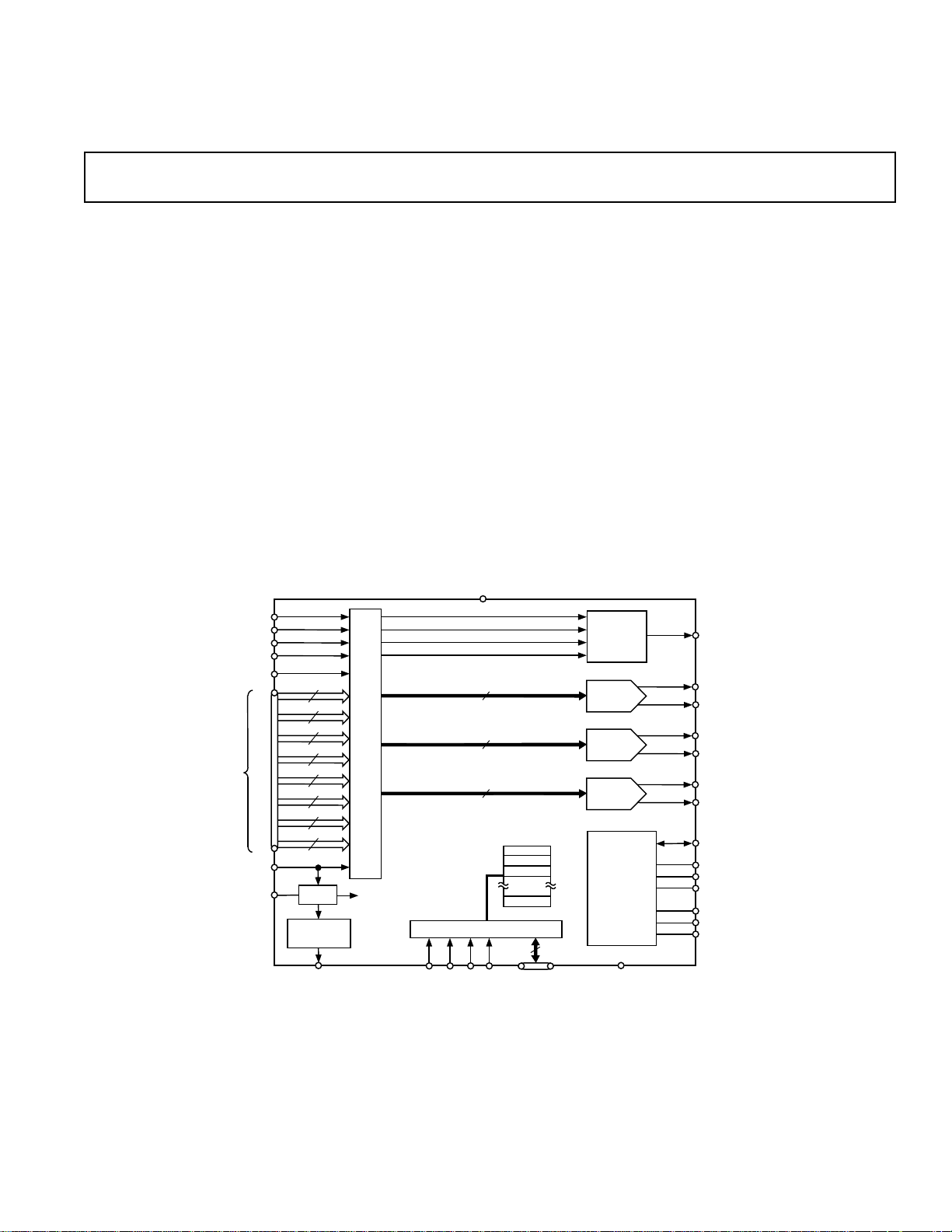

FUNCTIONAL BLOCK DIAGRAM

Video DAC with Onboard PLL

ADV7129

GENERAL DESCRIPTION

The ADV7129 is a complete analog output, video DAC on a single

CMOS (ADV®) monolithic chip. The part is specifically designed

for use in the highest resolution graphics and imaging systems.

The ultimate level of integration, comprised of 360 MHz triple

8-bit DACs, a programmable pixel port, an internal voltage reference and an onboard PLL, makes the ADV7129 the only choice

for the very highest level of performance and functionality.

The device consists of three high speed, 8-bit, video D/A converters (RGB). An onboard phase locked loop clock generator

is provided to provide high speed operation without requiring

high speed external crystal or clock circuitry.

The part is fully controlled through the MPU port by the onboard command registers. This MPU port may be updated at

any time without causing sparkle effects on the screen.

ADV is a registered trademark of Analog Devices, Inc.

(continued on page 10)

V

AA

VSYNC

HSYNC

CSYNC

BLANK

ODD/EVEN

PIXEL

DATA

(RED,

GREEN,

BLUE)

LOADIN

LPF

ADV is a registered trademark of Analog Devices, Inc..

24

A

24

B

24

C

24

D

24

E

24

F

24

G

24

H

CLOCK

CONTROL

LOADOUT

MUX

PLL

8:1

INT PIXEL

CLOCK

ADV7129

CONTROL

REGISTERS

8

8

8

MPU PORT

BLANK

AND SYNC

LOGIC

RED

DAC

GREEN

DAC

BLUE

DAC

VOLTAGE

REFERENCE

8

D7–D0CE R/W C0 C1

GND

SENSE/SYNCOUT

IOR

IOR

IOG

IOG

IOB

IOB

V

REF

R

RSET

R

GSET

R

BSET

RCOMP

GCOMP

BCOMP

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

1

(V

ADV7129–SPECIFICATIONS

All specifications T

All Versions Conditions

STATIC PERFORMANCE

3

= +5 V, V

AA

1

= +1.235 V, R

REF

to T

MIN

, R

RSET

GSET, RBSET

unless otherwise noted.)

MAX

2

= 280 V, RL = 25 V, CL = 10 pF.

Min Typ Max Units

Resolution (Each DAC) 8 Bits

Accuracy (Each DAC)

Integral Nonlinearity ± 1 LSB

Differential Nonlinearity Guaranteed Monotonic ± 1 LSB

Gray Scale Error ±5 % Gray Scale

Binary Coding

DIGITAL INPUTS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

Input Capacitance, C

INL

IN

IN

INH

V

= 0.4 V or 2.4 V ±10 µA

IN

2.0 VAA + 0.5 V

GND – 0.5 0.8 V

10 pF

DIGITAL OUTPUTS

Output High Voltage, V

Output Low Voltage, V

OL

OH

I

= –400 µA 2.4 V

OH

IOL = 3.2 mA 0.4 V

Floating-State Leakage Current ±10 µA

Floating-State Output Capacitance 10 pF

ANALOG OUTPUTS

Gray Scale Current Range 10 60 mA

Output Current

White Level Relative to Black 50.16 52.80 55.44 mA

Black Level Relative to Blank 4.1 4.32 4.54 mA

Blank Level, Sync Disabled 0 5 50 µA

LSB Size 223 µA

DAC to DAC Matching 2 5 %

Output Compliance, V

Output Impedance, R

OC

OUT

Output Capacitance, C

OUT

0 1.4 V

10 kΩ

20 pF

VOLTAGE REFERENCE

Voltage Reference Range, V

Input Current, I

VREF

REF

V

= 1.234 V for Specified 1.14 1.235 1.30 V

REF

Performance 5 µA

POWER REQUIREMENTS

V

AA

4

I

AA

4

I

AA

Analog Current 160 200 mA

Digital Current @ 360 MHz 360 400 mA

5V

Power Supply Rejection Ratio 0.12 %/%

DYNAMIC PERFORMANCE

Clock and Data Feedthrough

Glitch Impulse 50 pV secs

DAC to DAC Crosstalk

NOTES

1

±5%

for all versions.

2

Temperature range (T

3

Static performance is measured with the Gain Error Registers set to 00H (disabled).

4

IAA is measured with a typical dynamic pattern, satisfying the absolute maximum current spec for the DACs.

5

Clock and Data Feedthrough is a function of the amount of overshoot and undershoot on the digital inputs. Glitch impulse includes clock and data

feedthrough. TTL input values are 0 V to 3 V, with input rise/fall times ≥3 ns, measured at the 10% and 90% points. Timing reference points are at 50% for

inputs and outputs.

6

DAC to DAC crosstalk is measured by holding one DAC high while the other two DACs are making low to high and high to low transitions.

Specifications subject to change without notice.

MIN

to T

5

6

), 0°C to +70°C, TJ (Silicon Junction Temperature) ≤100oC.

MAX

–2–

–30 dB

–23 dB

REV. 0

ADV7129

2

(V

= +5 V, V

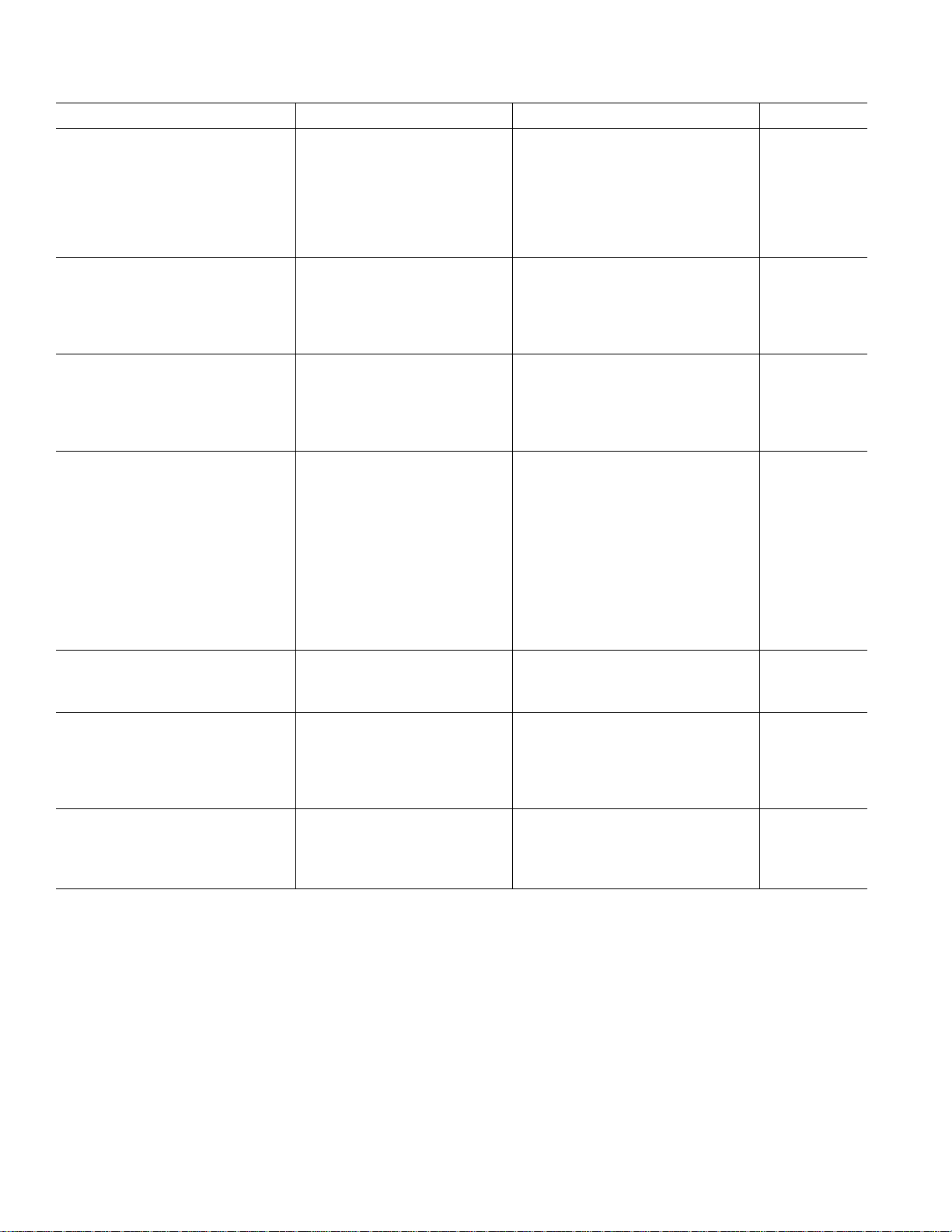

TIMING SPECIFICATIONS

AA

All specifications T

Parameter Conditions Min Typ Max Units

CLOCK CONTROL & PIXEL PORT

LOADIN Clocking Rate, f

LOADIN Cycle Time, t

LOADIN Low Time, t

LOADIN High Time, t

LCLK

1

2

3

LOADIN to LOADOUT Delay, t

Pixel Setup Time, t

Pixel Hold Time, t

5

6

4

4

MPU PORT

R/

W, C0, C1 Setup Time, t

R/

W, C0, C1 Hold Time, t

CE Low Time, t

CE High Time, t

9

10

CE Asserted to Data-Bus Driven, t

CE Asserted to Data-Bus Valid, t

CE Negated to Data-Bus Invalid, t

CE Negated to Data-Bus Three Stated, t

Write Data (D7–D0) Setup Time, t

Write Data (D7–D0) Hold Time, t

ANALOG OUTPUTS

Analog Output Delay, t

Analog Output Rise/Fall Time, t

Analog Output Transition Time, t

RGB Analog Output Skew, t

Pipeline Delay, t

PD

PLL PERFORMANCE

7

8

11

12

13

14

15

16

5

17

18

19

SK

6

Jitter (1σ) (LOADIN = 45 MHz) 55 ps rms

NOTES

1

TTL inputs values are 0 V to 3 V with input rise/fall times ≥3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Analog output load ≤10 pF. Databus (D7–D0) loaded as shown in Figure 1. Digital output load for SENSE ≤30 pF.

2

±5% for all versions.

3

Temperature range (T

4

Pixel Port consists of the following inputs: Pixel Inputs: RED [A-H], BLUE [A-H], GREEN [A-H].

5

Output Delay is measured from the 50% rising edge of LOADIN to the 50% point of full-scale transition on the A pixel. t17 includes the analog delay due to DACs

and internal gate transitions plus the pipeline stages delay. The output delay for pixels B-H will be the output delay to the A pixel (t17) plus the appropriate number

of clock cycles. Output rise/fall time is measured between the 10% and 90% points of full-scale transition. Settling time is measured from the 50% point of full-scale

transition to the output remaining within 1%. (Settling Time does not include clock and data feedthrough.)

6

Jitter is measured by triggering on the output clock, delayed by 15 µs and then measuring the time period from the trigger edge to the next edge of the output clock

after the delay. This measurement is repeated multiple times and the rms value is determined.

Specifications subject to change without notice.

MIN

to T

MAX

), 0°C to +70°C.

= +1.235 V, R

REF

to T

MIN

MAX

, R

RSET

3

GSET, RBSET

unless otherwise noted.)

= 280 V, RL = 25 V for IOG, IOR, IOB, CL = 10 pF.

10 45 MHz

16.67 ns

6.67 ns

6.67 ns

5ns

10 ns

42 ns

10 2.5 ns

10 0.5 ns

25 ns

25 ns

25 ns

20 ns

1ns

15 ns

10 ns

10 ns

@ 360 MHz 5 ns

0.8 ns

25 ns

1.5 ns

19 PCLKs

REV. 0

I

SINK

TO OUTPUT PIN +2.1V

100pF

I

SOURCE

Figure 1. LOADIN vs. Pixel Input Data

–3–

ADV7129

LOADOUT

LOADIN

t

4

t

1

t2 t

3

PIXEL

INPUT

DATA

ANALOG

OUTPUT

DATA

R/W, C0, C1

D7–D0

(READ MODE)

D7–D0

(WRITE MODE)

AN ...

H

N

DIGITAL INPUT TO ANALOG

OUTPUT PIPELINE

CE

A

... H

N–1

t

PD

t

7

A

N+1

H

N+1

N–1

CONTROL DATA

...

A

...

N+2

H

N+2

A

AN ... H

N

N+1

... H

N+1

Figure 2. LOADIN vs. Pixel Input Data

t

8

VALID

t

9

t

12

t

11

R/W = 1

R/W = 0

t

15

t

13

t

t

16

A

... H

N+2

N+2

t

10

14

Figure 3. Microprocessor Port (MPU) Interface Timing

PCLK

t

17

IOR

ANALOG

OUTPUTS

NOTE:

THIS DIAGRAM IS NOT TO SCALE.

FOR THE PURPOSES OF CLARITY, THE ANALOG OUTPUT WAVEFORM IS MAGNIFIED IN TIME AND AMPLITUDE W.R.T THE CLOCK WAVEFORM.

SYNCOUT IS A DIGITAL VIDEO OUTPUT SIGNAL.

t

17

IOG

IOB

SYNCOUT

t

18

IS THE ONLY RELEVENT TIMING SPECIFICATION FOR SYNCOUT.

t

19

WHITE LEVEL

90 %

50 %

10 %

FULL-SCALE

TRANSITION

BLACK LEVEL

Figure 4. Analog Output Response vs. LOADIN

–4–

REV. 0

ADV7129

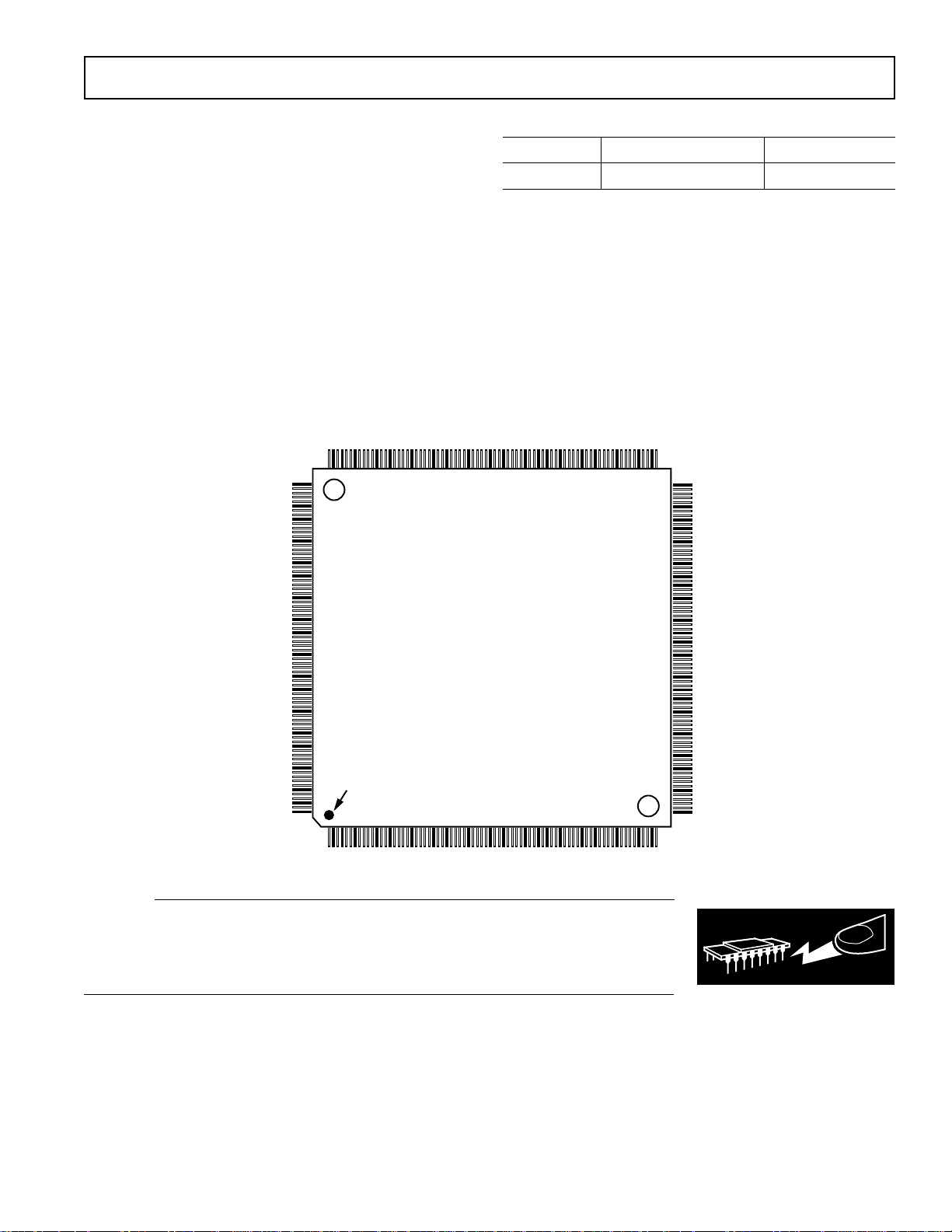

77

152

PIN NO. 1 IDENTIFIER

1

304

76

153228

229

ROW A

ROW BROW D

ADV7129

PQFP

TOP VIEW

(Not to Scale)

ROW C

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

V

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

AA

Voltage on Any Digital Pin . . . . GND – 0.5 V to V

Ambient Operating Temperature (T

Storage Temperature (T

Junction Temperature (T

) . . . . . . . . . . . . . . –65°C to +150°C

S

) . . . . . . . . . . . . . . . . . . . . . +150°C

J

1

+ 0.5 V

) . . . . . . . . 0°C to +70°C

A

AA

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . +260°C

Vapor Phase Soldering (1 minute) . . . . . . . . . . . . . . . . +220°C

Analog Outputs to GND

2

. . . . . . . . . . . GND – 0.5 V to V

AA

Current on Any DAC Output . . . . . . . . . . . . . . . . . . . . 60 mA

NOTES

1

Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those listed in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

2

Analog Output Short Circuit to any Power Supply or Common can be of an

indefinite duration.

304-LEAD PQFP PIN CONFIGURATION

ORDERING GUIDE*

Model Temperature Range Package Option

ADV7129KS 0°C to +70°C S-304

*Due to the specialized nature and application of this part, it is not automati-

cally available to order. Please contact your local sales office for details.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the ADV7129 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0

–5–

ADV7129

PIN ASSIGNMENTS

Pin No. Mnemonic Pin No. Mnemonic Pin No. Mnemonic Pin No. Mnemonic

1 GND 41 G4

2 GND 42 G4

3 GND 43 G4

4 GND 44 V

C

B

A

AA

81 GND 121 B4

82 GND 122 B4

83 G1

84 G0

5 GND 45 GND 85 G0

6 GND 46 V

7R0

8R0

9R0

10 R0

11 R0

12 G7

13 G7

14 G7

15 G7

16 G7

17 G7

18 G7

19 G7

20 G6

21 G6

22 G6

23 G6

24 G6

25 G6

26 G6

27 G6

28 G5

29 G5

30 G5

31 G5

32 G5

33 G5

34 G5

35 G5

36 G4

37 G4

38 G4

39 G4

40 G4

*No Connect.

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

47 GND 87 G0

48 G3

49 G3

50 G3

51 G3

52 G3

53 G3

54 G3

55 G3

56 G2

57 G2

58 G2

59 G2

60 G2

61 G2

62 G2

63 G2

64 G1

65 G1

66 G1

67 G1

68 G1

69 G1

70 G1

71 GND 111 B5

72 GND 112 B5

73 GND 113 B5

74 GND 114 B5

75 GND 115 B5

76 GND 116 V

77 GND 117 GND 157 GND

78 GND 118 B4

79 GND 119 B4

80 GND 120 B4

AA

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

86 G0

88 G0

89 G0

90 G0

91 G0

92 B7

93 B7

94 B7

95 B7

96 B7

97 B7

98 B7

99 B7

100 B6

101 B6

102 B6

103 B6

104 B6

105 B6

106 B6

107 B6

108 B5

109 B5

110 B5

AA

E

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

123 B4

124 B4

125 B4

126 B3

127 B3

128 B3

129 B3

130 B3

131 B3

132 B3

133 B3

134 B2

135 B2

136 B2

137 B2

138 B2

139 B2

140 B2

141 B2

142 B1

143 B1

144 B1

145 B1

146 B1

147 GND

148 GND

149 GND

150 GND

151 GND

152 GND

153 GND

154 GND

155 GND

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

156 GND

H

G

F

158 GND

159 B1

160 B1

C

B

–6–

REV. 0

ADV7129

Pin No. Mnemonic Pin No. Mnemonic Pin No. Mnemonic Pin No. Mnemonic

161 B1

162 B0

163 B0

164 B0

165 B0

166 B0

167 B0

168 B0

169 B0

A

H

G

F

E

D

C

B

A

170 BLANK 206 V

197 R

BIAS

198 SENSE/SYNCOUT 234 GND 270 R4

199 V

REF

200 GND 236 R6

201 D0 237 R6

202 D1 238 R6

203 D2 239 R6

204 D3 240 R6

205 GND 241 R6

AA

171 HSYNC 207 D4 243 R5

172 VSYNC 208 D5 244 R5

173 ODD/EVEN 209 D6 245 R5

174 NC* 210 D7 246 V

175 GND 211 CE 247 GND 283 R2

176 GND 212 R/W 248 V

177 IOB 213 C0 249 GND 285 R2

178 IOB 214 C1 250 R5

179 R

180 B

181 V

182 V

183 B

BSET

COMP

AA

AA

BIAS

184 IOG 220 R7

185 IOG 221 R7

186 R

187 G

188 V

189 V

190 G

GSET

COMP

AA

AA

BIAS

215 R7

216 R7

217 R7

218 R7

219 R7

222 R7

H

G

F

E

D

C

B

A

223 GND 259 R4

224 GND 260 R4

225 GND 261 GND 297 R0

226 GND 262 GND 298 R0

191 IOR 227 GND 263 V

233 GND 269 LOADOUT

B

235 R6

242 R6

251 R5

252 R5

253 R5

254 R5

255 R4

256 R4

257 R4

258 R4

H

G

F

E

D

C

B

A

H

G

F

AA

AA

E

D

C

B

A

H

G

F

E

D

C

AA

271 R4

272 R3

273 R3

274 R3

275 R3

276 R3

277 R3

278 R3

279 R3

280 R2

281 R2

282 R2

284 R2

286 R2

287 R2

288 R1

289 R1

290 R1

291 R1

292 R1

293 R1

294 R1

295 R1

296 R0

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

E

D

C

B

A

H

G

F

299 GND

192 IOR 228 GND 264 LPF 300 GND

193 R

194 R

195 V

196 V

*No Connect.

RSET

COMP

AA

AA

229 GND 265 GND 301 GND

230 GND 266 LOADIN 302 GND

231 GND 267 GND 303 GND

232 GND 268 CSYNC 304 GND

REV. 0

–7–

ADV7129

PIN DESCRIPTION

Mnemonic Function

R7–R0[A . . . H] Red Pixel Port Inputs (TTL Compatible Inputs). Eight sets of eight bits latched on the rising edge of

LOADIN.

G7–G0[A . . . H] Green Pixel Port Inputs (TTL Compatible Inputs). Eight sets of eight bits latched on the rising edge of

LOADIN.

B7–B0[A . . . H] Blue Pixel Port Inputs (TTL Compatible Inputs). Eight sets of eight bits latched on the rising edge of

LOADIN.

BLANK Composite Blank (TTL Compatible Input). This video control signal drives the analog outputs to the blanking

level. When

of Command Register 1.

EVEN Odd/Even Field Input (TTL Compatible Input). This input indicates which field of the frame is being dis-

ODD/

played. An even field is selected by setting ODD/

ODD/

HSYNC Horizontal-Sync Input (TTL Compatible Input). This control signal is latched on the rising edge of LOADIN.

VSYNC Vertical-Sync Input (TTL Compatible Input). This control signal is latched on the rising edge of LOADIN.

CSYNC Composite-Sync Input (TTL Compatible Input). This video control signal drives the analog outputs to the

SYNC level. It is only asserted during the blanking period and does not override any other control or data in-

put. CR14, CR13 or CR12 of Command Register 1 must be set together with CR11 or Command Register 1 to

decode

CE Chip Enable Input (TTL Compatible Input). This input must be set to logic “0” when writing or reading over

the data bus (D7–D0). Internally, data is latched on the rising edge of

W Read/Write pin (TTL Compatible Input). This signal is latched on the falling edge of CE. A high level indi-

R/

cates a read operation and a low level indicates a write operation.

C0, C1 Register select pins (TTL Compatible Inputs). These inputs select which MPU port register is selected for

writing or reading. Data is latched on the falling edge of

D7–D0 Data Bus (TTL Compatible Input/Output Bus). Data, including color palette values and device control infor-

mation is written to and read from the device over this 8-bit, bidirectional databus. Any unused bits of the

data bus should be terminated through a resistor to either the digital power plane (V

LOADIN Pixel Data Load Input (TTL Compatible Input). This input latches the multiplexed pixel data, including

BLANK, HSYNC, VSYNC, CSYNC, and ODD/EVEN into the device. This rising edge of this signal is used

to latch in the video signal inputs. It is also used as a reference frequency to generate an 8 × multiple pixel

clock using the fixed reference onboard PLL.

LOADOUT Pixel Data Load Output (TTL Compatible Output). This digital output is PCLK/8. If the onboard phase lock

loop is used, it has the same phase as LOADIN.

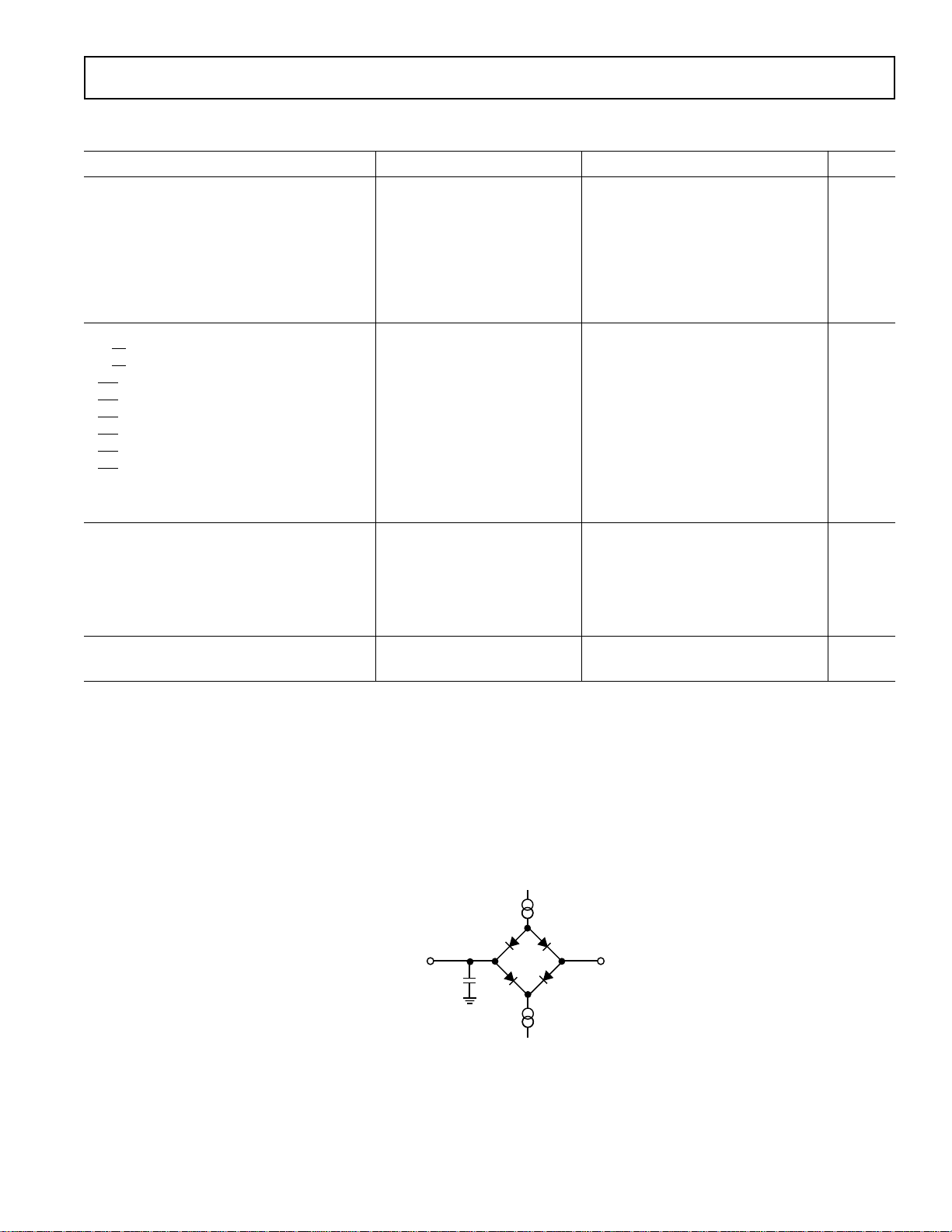

LPF Low-Pass Filter Pin. This pin stabilizes the internal PLL. The following network is recommended.

BLANK is at logic “0,” the pixel inputs are ignored. Pedestal selection is controlled by Bit CR15

BLANK is latched on the rising edge of LOADIN.

EVEN to logical “0.” An odd field is selected by setting

EVEN to logical “1.” ODD/EVEN should be changed only during vertical blank.

SYNC onto the IOR/IOR, IOG/IOG or IOB/IOB analog outputs, otherwise the SYNC input is ignored.

CE.

CE.

) or GND.

CC

0.1µF

100Ω

V

AA

LPF

Figure 5.

–8–

0.001µF

REV. 0

ADV7129

Mnemonic Function

IOR, IOG, IOB Red, Green & Blue Current Outputs (High Impedance Current Sources). These RGB video outputs are

specified to directly drive RS-343A and RS-170 video levels into doubly terminated 50 Ω or 75 Ω loads.

IOR, IOG, IOB Differential Red, Green & Blue Current Outputs (High Impedance Current Sources). These RGB video

outputs are specified to directly drive RS-343A and RS-170 video levels into doubly terminated 50 Ω or

75 Ω loads. If the complementary outputs are not required, then these outputs should be tied to GND.

R

COMP

G

COMP

B

COMP

R

RSET, RGSET, RBSET

Red Compensation pin. This pin should be bypassed to V

Green Compensation pin. This pin should be bypassed to V

Blue Compensation pin. This pin should be bypassed to V

with 0.01 µF capacitor.

AA

with 0.01 µF capacitor.

AA

with 0.01 µF capacitor.

AA

DAC Output Full-Scale Adjust Control (Analog Input): A resistor from this pin to ground sets the current

in the DACs. The current in the DACs is set according to the equations:

I

= 12,950 × V

OUT

I

= 18,137 × V

OUT

REF/RSET

(SYNC not encoded on the DAC Output)

REF/RSET

(SYNC encoded on the DAC Output)

To generate RS 343-A video levels on the DAC outputs, a resistor value of 280 Ω is recommended for

doubly terminated 50 Ω lines. Any combination of R

of

SYNC and pedestal are possible provided that the maximum DAC current and the DAC output compli-

value, DAC termination resistor and programming

SET

ance specifications are adhered to.

For example, in a doubly terminated 50 Ω system with no

an R

value of 280 Ω gives a DAC full-scale output of 52.8 mA, i.e., a white-to-black value of 1.4 V.

SET

SYNC or pedestal encoded on the DAC outputs,

This example would give a 6 dB reduction in noise and feedthrough on the DAC outputs (compared to a

0.7 V full-scale value), but may require a 0.5X splitter at the monitor.

R

BIAS

G

BIAS

B

BIAS

SENSE/

SYNCOUT Comparator Sense Output (TTL Compatible Output). This output will be logic “1” if one or more of the

Red Bias node. This node should be decoupled to V

Green Bias node. This node should be decoupled to V

Blue Bias node. This node should be decoupled to V

with a 0.01 µF capacitor.

AA

AA

with a 0.01 µF capacitor.

AA

with a 0.01 µF capacitor.

analog outputs exceeds the internal voltage of the SENSE comparator circuit. It can be used to determine

the absence of a CRT monitor. The value of the SENSE Output corresponds to the current pixel at the outputs. The output can drive one CMOS load. This pin can alternately be programmed to be a TTL sync

output which is a delayed version of

V

REF

Voltage Reference (Analog Input/Output): This should always have a 0.1 µF decoupling capacitor attached

between V

and VAA. If nothing else is connected then the DACs are driven by the internal voltage refer-

REF

CSYNC.

ence. If it is required to use a more accurate reference, then this pin acts as an overdrive input. An external

1.235 V voltage reference such as the AD1580 or equivalent is recommended to drive this input. (Note: It is

not recommended to use a resistor network to generate the voltage reference.)

V

AA

Power Supply (+5 V ± 5%). The part contains multiple power supply pins, all should be connected together

to one common +5 V filtered analog power supply.

GND Analog Ground. The part contains multiple ground pins, all should be connected together to the system’s

ground plane.

REV. 0

–9–

ADV7129

(continued from page 1)

The ADV7129 supports 24-bit true-color formats where screen

resolution is the primary design goal. The individual Red,

Green and Blue pixel input ports allow true-color image rendition at resolutions of 2048 × 2048 × 24 bit.

The ADV7129 is capable of generating RGB video output signals that are compatible with RS-343A and RS-170 video standards, without requiring external buffering.

An internal voltage reference is also provided to simplify system

design.

The ADV7129 is fabricated in a +5 V CMOS process.

The ADV7129 is packaged in a 304-pin PQFP package.

CIRCUIT DETAILS AND OPERATION

Digital video or pixel data is latched into the ADV7129 over the

pixel port. The data is multiplexed and latched into the three 8bit digital-to-analog converters (DACs) and output as an RGB

video signal.

The ADV7129 can be broken into three sections for purposes of

clarity of explanation:

1. Pixel port and clock control circuit.

2. MPU port, registers and cursor.

3. Digital-to-analog converters and video outputs.

Pixel Port and Clock Circuits

The pixel port of the ADV7129 is directly interfaced to the

video/graphics pipeline of a computer graphics subsystem. It is

connected directly through a gate array to the video RAM of the

system’s frame buffer. The pixel port of the ADV7129 consists of:

Color Data: RED, GREEN, BLUE

Pixel Controls:

HSYNC, VSYNC, CSYNC, BLANK

The associated clocking signals for the pixel port include:

Clock Input LOADIN

Clock Output LOADOUT

Pixel Port (Color Data)

The ADV7129 has 192 color data inputs. This supports 24-bit

true color with 8:1 multiplexing.

Color data is always latched on the rising edge of LOADIN.

LOADOUT is generated internally by the ADV7129. The frequency of LOADOUT is the internal clock frequency (PCLK)

divided by 8.

Other pixel data signals latched into the part by LOADIN include

HSYNC, BLANK, VSYNC and CSYNC.

HSYNC, VSYNC, CSYNC, BLANK

The BLANK and SYNC video control signals drive the analog

outputs to the blanking and sync levels respectively. These are

latched on the rising edge of LOADIN. The SYNC information

can be encoded onto any of the IOG, IOR or IOB analog outputs by setting Bits CR12, CR13 or CR14 of Command Register 1 to logic “1.”

The SYNC information is ignored if Bits CR12, CR13 and

CR14 of Command Register 1 are set to logic “0.”

The SYNC and BLANK information can be decoded onto the

inverted outputs by setting CR10 and CR11 of Command

Register 1 to logic level “1.”

SENSE

If any one or more of the analog outputs, IOG, IOR and IOB,

exceed the internal voltage reference level (due to absence of

CRT), SENSE is set to logic “1.” The SENSE output can drive

one CMOS load and can be used to determine the absence of a

CRT monitor.

CLOCK CONTROL CIRCUIT

The ADV7129 has an integrated clock control circuit. This circuit is capable of generating the internal clocking signals.

A lower frequency external clock generator is used by enabling

the onboard PLL. This fixed multiple PLL is used to speed up

LOADIN by a factor of 8. This onboard 8 × clock multiplier is

activated by setting Bit CR20 of Command Register 2 from

logic “0” to logic “1.” It must be set up after power-up.

MICROPROCESSOR (MPU) PORT

The ADV7129 supports a standard MPU interface. All the

functions of the part are controlled via this MPU port. Direct

access is gained to the address register and all the control registers as well as the cursor palette. The following sections describe the setup for reading and writing to all of the devices’

registers.

MPU Interface

The MPU interface consists of a bidirectional, 8-bit wide databus and interface control signals R/

W, CE, C1, C0. Two write

operations are required to set up the lower 8 bits and higher

2 bits of the Address Register.

Register Mapping

The ADV7129 contains a number of onboard registers including the Address Register, Command Registers and Gain Error

Registers. Control Lines C1-C0 determine whether the Address

Register is being pointed to (upper or lower bytes) or whether

the other registers are being accessed.

The R/

W and CE control inputs allow read and write access.

All registers can to read and written to.

Power-On Reset

After power-up, the ADV7129 must be set to perform a reset

operation. This is achieved by resetting the PLL (a low to high

transition on Bit CR20 of Command Register 2). This initializes the pixel port such that the pixel sequence ABCDEFGH

starts at A. This reset can be performed as the registers are being initialized. The Command Registers power up in an indeterminate state and must be set up for the required operation. The

power-on is activated when V

goes from 0 V to 5 V. This is

AA

active for 1 µs. The ADV7129 should not be accessed during

this period.

Register Accesses

The MPU can write to or read from all of the ADV7129s’ registers. Figure 6 shows the Control Registers and C1-C0 Control

Input Truth Table. The read/write timing is controlled by the

CE and R/W inputs. The Address Register determines which

Control Register is being accessed.

The registers can be addressed directly by two write cycles to set

up the high and low bytes of Address Register and then by a

read or write cycle of the MPU.

–10–

REV. 0

ADV7129

REGISTER PROGRAMMING

The following section describes each register, including Address

Register and each of the Control Registers in terms of its

configuration.

Address Register (A10–A0)

As illustrated previously, the C1–C0 inputs, in conjunction with

the Address Register specify which control register, or palette

RAM location is accessed by the MPU port. The Address Register is 16 bits wide and can be read from as well as written to.

CONTROL REGISTERS

A large bank of registers can be accessed using the Address register and C1–C0. Access is made first by writing the Address

Register with the appropriate address to point to the particular

Control Register, and then performing an MPU access to the

Control Register.

ADDRESS REGISTER

(A10–A0)

C1 C0 R/W

0 0 0 WRITE TO ADDRESS REGISTER (LOWER BYTE)

0 1 0 WRITE TO ADDRESS REGISTER (UPPER BYTE)

1 0 0 WRITE TO REGISTERS

0 0 1 READ FROM ADDRESS REGISTER (LOWER BYTE)

0 1 1 READ FROM ADDRESS REGISTER (UPPER BYTE)

1 0 1 READ FROM REGISTERS

1 1 X RESERVED

(A10–A0) REGISTER ACCESS

4FF–412 RESERVED

411 COMMAND REGISTER 2

410 RESERVED

40F RESERVED

40E RESERVED

40D RESERVED

40C RESERVED

40B RESERVED

40A RESERVED

409 RESERVED

408 RESERVED

407 BLUE DAC GAIN ERROR REGISTER

406 GREEN DAC GAIN ERROR REGISTER

405 RED DAC GAIN ERROR REGISTER

004 RESERVED

403 RESERVED

402 RESERVED

401 RESERVED

400 COMMAND REGISTER 1

000–3FF RESERVED

COMMAND REGISTER 1 (CR1)

(Address Register (A10–A0) = 400H)

This register contains a number of control bits as shown in the

diagram. CR1 is an 8-bit wide register.

Figure 7 shows the various operations under the control of CR1.

This register can be read from as well as written to. Bit CR16 is

reserved and should be set to logic “1.”

COMMAND REGISTER 1-BIT DESCRIPTION

BLANK Control on Inverted Outputs (CR10):

This bit specifies whether the video

BLANK is to be decoded

onto the inverted analog outputs or ignored.

SYNC Control on Inverted Outputs (CR11)

This bit specifies whether the video SYNC is to be decoded

onto the inverted analog outputs or ignored.

SYNC Recognition on Blue (CR12)

This bit specifies whether the video SYNC input is to be decoded onto the IOB analog output or ignored.

SYNC Recognition on Green (CR13)

This bit specifies whether the video SYNC input is to be decoded onto the IOG analog output or ignored.

SYNC Recognition on Red (CR14)

This bit specifies whether the video SYNC input is to be decoded onto the IOR analog output or ignored.

Pedestal Enable Control (CR15)

This bit specifies whether a 0 IRE or a 7.5 IRE blanking pedestal is to be generated on the video outputs.

Display Mode Control (CR17)

This bit controls whether the display is interlaced or noninterlaced.

REV. 0

Figure 6. Control Registers

CR17 CR16 CR15 CR14 CR13 CR12 CR11 CR10

INTERLACE ENABLE

CR17

0 DISABLE

1 ENABLE

ZERO MUST BE

WRITTEN TO THIS BIT

(RESERVED)

CR16 = 0

PEDESTAL ENABLE

CONTROL

CR15

0 0 IRE

1 7.5 IRE

SYNC RECOGNITION

CONTROL (IOB)

CR12

0 IGNORE

1 DECODE

SYNC RECOGNITION

CONTROL (IOG)

CR13

0 IGNORE

1 DECODE

SYNC RECOGNITION

CONTROL (IOR)

CR14

0 IGNORE

1 DECODE

CR11

0 DISABLE SYNC ON

1 DECODE SYNC ON

Figure 7. Command Register 1

–11–

PEDESTAL CONTROL

(IOR, IOG, IOB)

CR10

0 DISABLE BLANK ON

INVERTED OUTPUTS

1 DECODE BLANK ON

INVERTED OUTPUTS

SYNC CONTROL

(IOR, IOG, IOB)

INVERTED OUTPUTS

INVERTED OUTPUTS

ADV7129

COMMAND REGISTER 2 (CR2)

(Address Register (A10–A0) = 411H)

This register contains a number of control bits as shown in the

diagram. CR2 is an 8-bit wide register. CR27, CR24, CR22

and CR21 are reserved and should be set to logic “0.” Figure 8

shows the various operations under the control of CR2. This

register can be read from as well as written to.

COMMAND REGISTER 2-BIT DESCRIPTION

PLL Control (CR20)

This bit resets the PLL divider when set to logic “0” and releases it when set to logic “1.”

SYNCOUT Control (CR23)

This bit is an enable for SYNCOUT. If this bit is set to logic

“1,” the SENSE output becomes a pipelined version of

CSYNC. Otherwise the SENSE output remains unaffected.

SENSE Bit (CR25)

This output bit is used to determine the absence of a CRT

monitor. When CR25 is set to logic “1,” a CRT is not present.

With some diagnostic code, the presence of loading on the individual RGB lines can be determined. The reference is generated

by a voltage divider from the external voltage reference on the

V

pin. For the proper operation, the following levels should

RE

F

be applied to the comparator by the IOR, IOG and IOB outputs:

DAC Low Voltage ≤ 250 mV.

DAC High Voltage ≥ 450 mV.

VCO Override Bit (CR26)

This bit is used to override the VCO and set the PLL to the

lowest frequency possible. If the external LOADIN source takes

some time before it reaches its required frequency, the internal

PLL can become unstable as it tries to track to a varying

LOADIN signal. The VCO override bit can be set to logic level

“0” and then released (set to logic level “1”) to allow the VCO

to track to the input after it has stabilized. It is required to allow

200 µs before the VCO override bit is released.

GAIN ERROR REGISTERS

(Address Register (A10–A0) = 405H–407H)

The Red, Green and Blue Gain Error Registers allow the user to

compensate for any channel-to-channel variations in the video

output system. They control internal resistors from each of the

three DAC outputs to GND, i.e., they appear in parallel with

the external termination resistor across the DAC outputs. This

allows the RGB output voltages to be adjusted as the value of

R

is varied. A logic “1” on any of the control bits GR06 to

INT

GR00 switches in the appropriate resistor. A logic “0” disables

or open circuits the resistor. Bit GR07 of the Gain Error

Register enables or disables the Gain Error Adjust. Figure 9

shows the typical resistor values for these internal resistances

versus R

SET

.

CR27 CR26 CR25 CR24 CR23 CR22 CR21 CR20

RESERVED

(CR27)

THIS BIT SHOULD BE

SET TO LOGIC “0”

VCO OVERRIDE

CR26

0 VCO OVERRIDE

1 NORMAL PLL

CR25

0 MONITOR

1 MONITOR

OPERATION

SENSE OUTPUT

PRESENT

NOT PRESENT

THIS BIT SHOULD BE

SET TO LOGIC “0”

SYNCOUT CONTROL

CR23

RESERVED

(CR24)

0 IGNORE

1 DECODE

RESERVED

(CR22, CR21)

THESE BITS SHOULD BE

SET TO LOGIC “0”

Figure 8. Command Register 2

DACs

R

SET

GR07 GR06 GR05 GR04 GR03 GR02 GR01 GR00

GAIN ERROR

CONTROL

GR07

0 DISABLE GAIN ERROR ADJ

1 ENABLE GAIN ERROR ADJ

INTERNAL RESISTORS

R

6R5R4R3R2R1R0

x

x x

1

GAIN ERROR REGISTER

x x x x

REGISTER (RESET = 280Ω)

GR06 R6

GR05 R5

GR04 R4

GR03 R3

GR02 R2

GR01 R1

GR00 R0

I

OUT

PIN

47Ω

923Ω

1926Ω

3476Ω

6979Ω

16610Ω

27037Ω

CR20

0 RESET PLL

1 RELEASE PLL

(CABLE)

R

T1

PLL RESET

R

T2

(MONITOR)

Figure 9. Gain Error Register

–12–

REV. 0

ADV7129

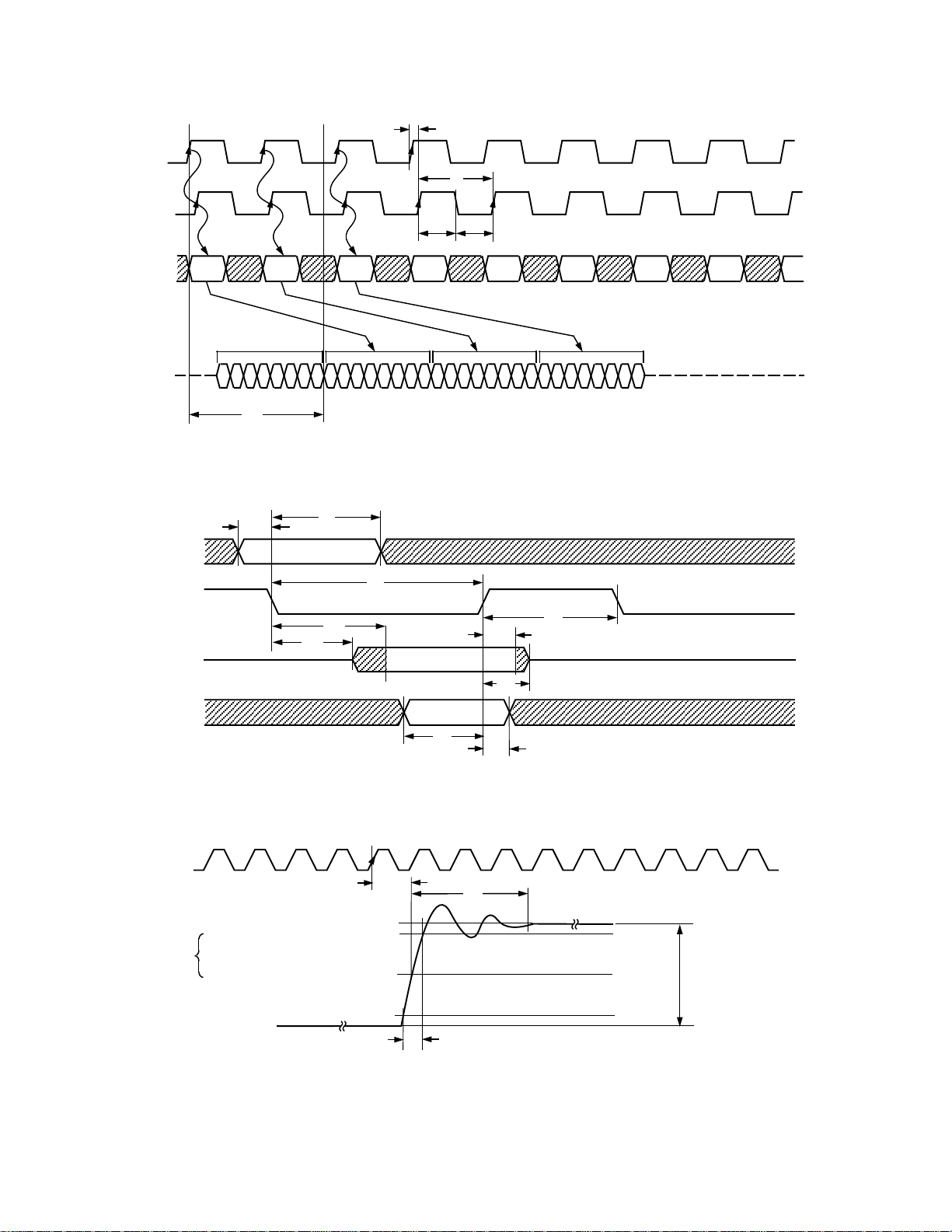

GRAY SCALE

7.5 IRE

92.5 IRE

40 IRE

SYNC LEVEL

BLANK LEVEL

BLACK LEVEL

WHITE LEVEL

DIGITAL-TO-ANALOG CONVERTERS (DACS)

AND VIDEO OUTPUTS

The ADV7129 contains three high speed video DACs. The

DAC outputs are represented as the three primary analog color

signals IOR (red video), IOG (green video) and IOB (blue

video).

DACs and Analog Outputs

The part contains three matched 8-bit digital-to-analog converters.

The DACs are designed using an advanced, high speed, segmented architecture. The bit currents corresponding to each

digital input are routed to either IOR, IOG, IOB (bit = “1”) or

IOR, IOG, IOB (bit = “0”). Normally IOR, IOG, & IOB are

connected to GND.

IOR, IOG, IOB

DACs

ZS = 50Ω

(SOURCE TERMINATION)

ZO = 50Ω

(CABLE)

ZL = 50Ω

(MONITOR)

Figure 10. DAC Output Termination (Doubly Terminated

Ω

Load)

50

The analog video outputs are high impedance current sources.

Each of the these three RGB current outputs are specified to directly drive a 25 Ω load (doubly-terminated 50 Ω).

Reference Input and R

SET

An external 1.235 V voltage reference is preferred to set up the

analog outputs of the ADV7129. The reference voltage is connected to the V

input. In the absence of an external refer-

REF

ence, the on-chip voltage reference is internally connected to

the V

pin. The internal reference will set up the DAC cur-

REF

rents, although with slightly less accuracy.

A resistor R

R

) input of the part and ground. An R

BSET

is connected between the R

SET

(R

SET

RSET

value of 280 Ω

SET

, R

GSET

,

corresponds to the generation of two times RS-343A video levels into a doubly-terminated 50 Ω load. Figure 11 illustrates the

resulting video waveform and the Video Output Truth Table illustrates the corresponding control input stimuli. On the

ADV7129

however in practice,

SYNC can be encoded on any of the analog signals,

SYNC is generally encoded on either the

IOG output or on all of the video outputs.

Any combination of R

programming of

SYNC and pedestal are possible provided that

, DAC termination resistors and

SET

the maximum DAC current of 60 mA and the DAC output

compliance specifications are adhered to. The following tables

show the current levels for different values of R

R

termination.

LOAD

resistors and

SET

Figure 11. Composite Video Waveform SYNC Decoded;

Pedestal = 7.5 IRE

REV. 0

–13–

ADV7129

Table I. Video Output Truth Table (R

= 398V, R

SET

LOAD

= 37.5

V)

O/P with Sync O/P with Sync DAC

Description Enabled (mA) Disabled (mA) SYNC BLANK Input Data

WHITE LEVEL 26.67 19.05 1 1 FFH

VIDEO Video + 9.05 Video + 1.44 1 1 Data

VIDEO to BLANK Video + 1.44 Video + 1.44 0 1 Data

BLACK LEVEL 9.05 1.44 1 1 00H

BLACK to BLANK 1.44 1.44 0 1 00H

BLANK LEVEL 7.62 0 1 0 xxH

SYNC LEVEL 0 0 0 0 xxH

Table II. Video Output Truth Table (R

= 560V, R

SET

LOAD

= 25

V)

O/P with Sync O/P with Sync DAC

Description Enabled (mA) Disabled (mA) SYNC BLANK Input Data

WHITE LEVEL 40 28.57 1 1 FFH

VIDEO Video + 13.6 Video + 2.14 1 1 Data

VIDEO to BLANK Video + 2.16 Video + 2.14 0 1 Data

BLACK LEVEL 13.6 2.14 1 1 00H

BLACK to BLANK 2.14 2.14 0 1 00H

BLANK LEVEL 11.44 0 1 0 xxH

SYNC LEVEL 0 0 0 0 xxH

Table III. Video Output Truth Table (R

= 280V, R

SET

LOAD

= 25

V)

O/P with Sync DAC

Description Disabled (mA) SYNC BLANK Input Data

WHITE LEVEL 52.8 0 0 FFH

VIDEO Video + 0 0 0 Data

VIDEO to BLACK Video + 0 0 0 Data

BLACK LEVEL 0 0 0 xxH

–14–

REV. 0

APPENDIX I

BOARD DESIGN AND LAYOUT CONSIDERATIONS

ADV7129

The ADV7129 is a highly integrated circuit containing both

precision analog and high speed digital circuitry. It has been

designed to minimize interference effects on the integrity of the

analog circuitry by the high speed digital circuitry. It is imperative that these same design and layout techniques be applied to

the system level design such that high speed, accurate performance is achieved. The “Recommended Analog Circuit Layout”

(see Figure 12) shows the analog interface between the device and

monitor.

The layout should be optimized for lowest noise on the ADV7129

power and ground lines by shielding the digital inputs and providing good decoupling. The lead length between groups of V

AA

and GND pins should by minimized so as to minimize inductive

ringing.

Ground Planes

The ground plane should encompass all ADV7129 ground pins,

voltage reference circuitry, power supply bypass circuitry for the

ADV7129, the analog output traces, and all the digital signal

traces leading up to the ADV7129. The analog ground plane

should be separated from the system ground plane by a ferrite

bead.

Power Planes

The ADV7129 and any associated analog circuitry should have its

own power plane, referred to as the analog power plane (V

AA

).

This power plane should be connected to the regular PCB power

plane (V

) at a single point through a ferrite bead. This bead

CC

should be located within three inches of the ADV7129.

The PCB power plane should provide power to all digital logic

on the PC board, and the analog power plane should provide

power to all ADV7129 power pins and voltage reference circuitry.

Plane-to-plane noise coupling can be reduced by ensuring that

portions of the regular PCB power and ground planes do not

overlay portions of the analog power plane, unless they can be

arranged such that the plane-to-plane noise is common mode.

Supply Decoupling

For optimum performance, bypass capacitors should be installed

using the shortest leads possible, consistent with reliable operation, to reduce the lead inductance. Best performance is obtained

with 0.1 µF ceramic capacitor decoupling. Each group of V

AA

pins on the ADV7129 must have at least one 0.1 µF decoupling

capacitor to GND. These capacitors should be placed as close

as possible to the device.

It is important to note that while the ADV7129 contains circuitry to reject power supply noise, this rejection decreases with

frequency. If a high frequency switching power supply is used,

the designer should pay close attention to reducing power

supply noise and consider using a three terminal voltage

regulator for supplying power to the analog power plane.

Digital Signal Interconnect

The digital inputs to the ADV7129 should be isolated as

much as possible from the analog outputs and other analog

circuitry. Also, these input signals should not overlay the

analog power plane.

Due to the high clock rates involved, long clock lines to the

ADV7129 should be avoided to reduce noise pickup.

Any active termination resistors for the digital inputs should

be connected to the regular PCB power plane (V

CC

), and

not the analog power plane.

Analog Signal Interconnect

The ADV7129 should be located as close as possible to the

output connectors to minimize noise pickup and reflections

due to impedance mismatch.

The video output signals should overlay the ground plane,

and not the analog power plane, to maximize the high frequency power supply rejection.

Digital Inputs, especially Pixel Data Inputs and clocking

signals (LOADOUT, LOADIN, etc.) should never overlay

any of the analog signal circuitry and should be kept as far

away as possible.

For best performance, the analog outputs should each have

a 50 Ω load resistor connected to GND. These resistors

should be placed as close as possible to the ADV7129 so as

to minimize reflections.

There are a number of precautions that the user can take to

minimize the effects of data feedthrough.

a. Apply external filtering to the DAC outputs.

b. Reduce input voltage risetime. From experiments, it has

been seen that a reduction from 2 ns to 4 ns gives significant improvement.

c. Reduce input voltage swing. A reduction from 5 V to 3 V

gives significant improvement.

d. Use series resistors on the pixel inputs (e.g., 100 Ω).

e. The part can be run at 2× DAC current levels as shown

in the DAC output. The differential outputs can then be

connected through a differential to single balun transformer to eliminate common-mode noise. A phase splitter should be used to reduce the 2× levels to 1× at the

monitor end.

REV. 0

–15–

ADV7129

CLOCK

(45MHz)

0.1µF

100Ω

PIXEL

DATA

BLANK

VSYNC

HSYNC

CSYNC

ODD/EVEN

LOADIN

LOADOUT

V

AA

192

0.01µF

LPF

0.1µF

V

AA

V

REF

V

AA

ADV7129

GND

0.1µF 0.01µF

+5V(VAA)

ANALOG POWER PLANE

R

BIAS

G

BIAS

B

BIAS

R

COMP

G

COMP

B

COMP

R

RSET

G

RSET

B

RSET

IOR

IOR

IOG

ANALOG GROUND PLANE

V

AA

V

AA

V

AA

IOG

IOB

IOB

SENSE/SYNCOUT

(DOESN’T SHOW MPU PORT FOR CLARITY)

(REPEATED FOR EACH GROUP OF VAA PINS)

FERRITE BEAD

10µF

EACH

0.01µF

EACH

0.01µF

EACH

280Ω

50Ω

50Ω

50Ω

FERRITE BEAD

(BOARD SUPPLY V

+5V

33µF

AN OPTIONAL BALUN TRANSFORMER

CAN BE USED ON VIDEO AND

COMPLEMENTARY OUTPUTS FOR

IMPROVED PERFORMANCE

MONITOR (CRT)

50Ω

50Ω

50Ω

BOARD GROUND

DIGITAL GROUND

PLANE

)

CC

Figure 12. Typical Connection Diagram

–16–

REV. 0

APPENDIX II

THERMAL AND ENVIRONMENTAL CONSIDERATIONS

ADV7129

The ADV7129 is a very highly integrated monolithic silicon

device. This high level of integration inevitably leads to consideration of thermal and environmental conditions which the

ADV7129 must operate in. Reliability of the device is enhanced

by keeping it as cool as possible. In order to avoid destructive

damage to the device, the absolute maximum junction temperature must never be exceeded. Certain applications, depending

on ambient temperature and pixel data rates may require forced

air cooling or external heatsinks. The following data is intended as

a guide in evaluating the operating conditions of a particular application so that optimum device and system performance is achieved.

It should be noted that information on package characteristics

published herein may not be the most up to date at the time of

reading this. Advances in package compounds and manufacture

will inevitably lead to improvements in the thermal data. Please

contact your local sales office for the most up-to-date information.

Package Characteristics

Junction-to-Case (θ

) Thermal Resistance for this particular

JC

part is:

θ

= 8.9°C/W

JC

θ

(Note:

is independent of airflow.)

JC

The maximum silicon junction temperature should be limited to

100°C. Temperatures greater than this will reduce long-term

device reliability. To ensure that the silicon junction tempera-

ture stays within prescribed limits, the addition of an external

heatsink can be used if the junction temperature is brought beyond the maximum limit.

Junction-to-Ambient (θ

) Thermal Resistance for this particu-

JA

lar part is:

θ

= 25.9°C/W (Still Air)

JA

θ

= will significantly decrease in air flow.

JA

Thermal Model

The junction temperature of the device in a specific application

is given by:

T

= TA + PD (

J

θ

+

θ

JC

) (1)

CA

or

T

= TA + PD (

J

θ

) (2)

JA

where:

T

= Junction Temperature of Silicon (°C)

J

T

= Ambient Temperature (°C)

A

P

= Power Dissipation (W)

D

θ

= Junction to Case Thermal Resistance (°C/W)

JC

θ

= Case to Ambient Thermal Resistance (°C/W)

CA

θ

= Junction to Ambient Thermal Resistance (°C/W)

JA

V

= +5V

550

525

500

475

CURRENT – mA

450

425

AA

200 240 280 320 360

160

SPEED – MHz

Figure 13. Supply Current vs. Frequency

REV. 0

–17–

ADV7129

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

304-Lead Plastic Quad Flatpack

(S-304)

SEATING

PLANE

0.0197

(0.50)

NOM

0.008

(0.20)

NOM

0.150 (3.80) NOM

0.167 (4.23)

NOM

1.677 (42.60) NOM

1.579 (40.10)

1.571 (39.90)

228 153

229

304

PIN 1 IDENTIFIER

1

ROW C

TOP VIEW

(PINS DOWN)

ROW A

ROW BROW D

152

76

1.579 (40.10)

1.571 (39.90)

77

1.677

(42.60)

NOM

–18–

REV. 0

–19–

C2215–6–10/96

–20–

PRINTED IN U.S.A.

Loading...

Loading...