Dual-Channel Isolators with isoPower

Integrated DC-to-DC Converter, 50 mW

Data Sheet

FEATURES

Integrated isolated dc-to-dc converter

Regulated 5 V/10 mA output

Dual dc to 1 Mbps (NRZ) signal isolation channels

Narrow-body, 8-lead SOIC package

RoHS compliant

High temperature operation: 105°C

Precise timing characteristics

3 ns maximum pulse width distortion

3 ns maximum channel-to-channel matching

70 ns maximum propagation delay

High common-mode transient immunity: >25 kV/μs

Safety and regulatory approvals

UL recognition

2500 V rms for 1 minute, per UL 1577

CSA Component Acceptance Notice #5A

VDE certificate of conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

V

= 560 V peak

IORM

GENERAL DESCRIPTION

The ADuM524x

integrated, isolated power. Based on the Analog Devices, Inc.,

iCoupler® technology, a chip scale dc-to-dc converter provides

up to 50 mW of regulated, isolated power at 5 V, which eliminates

the need for a separate isolated dc-to-dc converter in low power

isolated designs. The Analog Devices chip scale transformer

iCoupler technology is used both for the isolation of the logic

signals as well as for the dc-to-dc converter. The result is a small

form factor, total isolation solution.

The ADuM524x isolators provide two independent isolation

channels in a variety of channel configurations, operating from

a 5 V input supply. ADuM524x units can be used in combination

with other iCoupler products to achieve greater channel counts.

1

Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329.

1

are dual-channel digital isolators with isoPower®

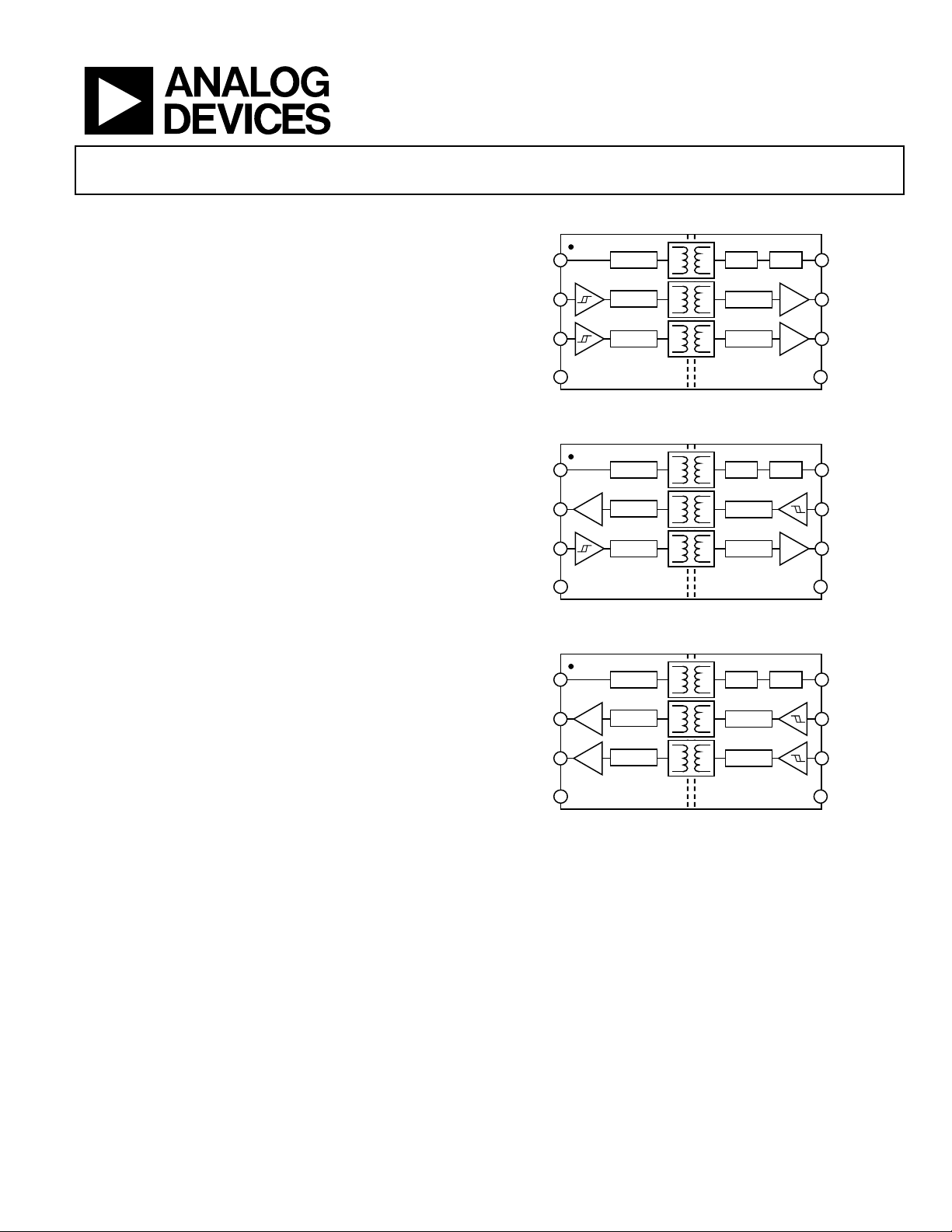

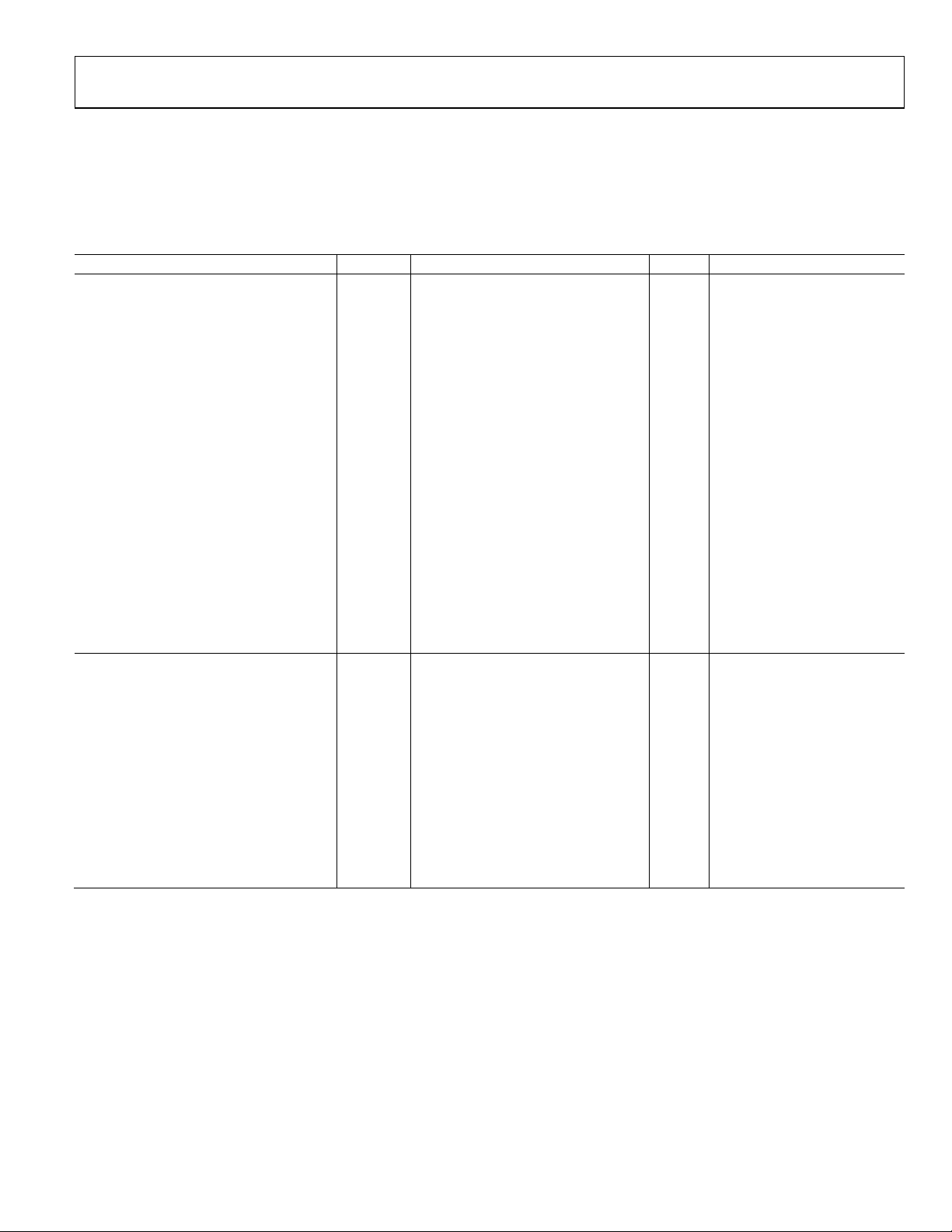

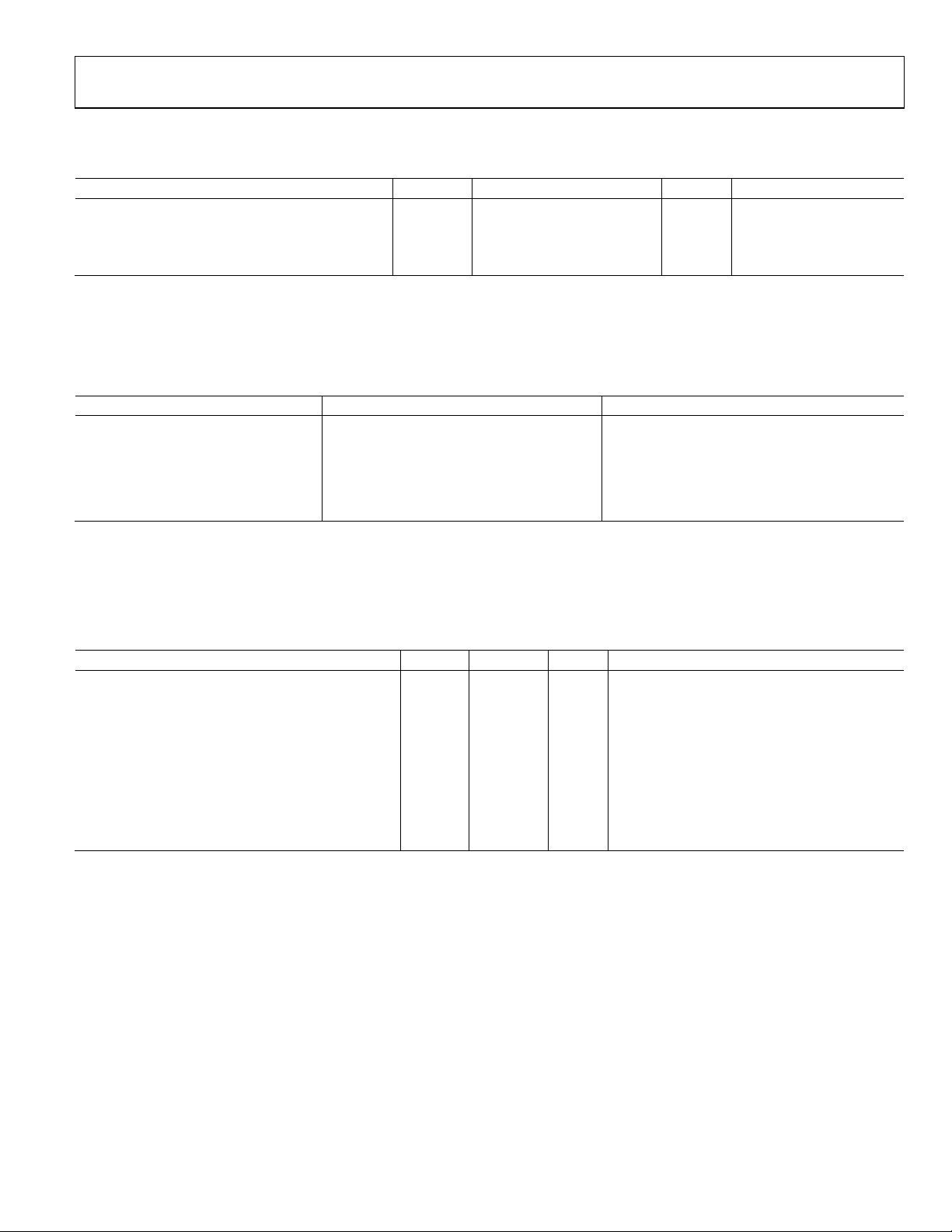

ADuM5240/ADuM5241/ADuM5242

FUNCTIONAL BLOCK DIAGRAMS

V

V

V

GND

1

DD

2

IA

3

IB

4

OSC.

ENCODE

DECODE

DECODEENCODE

Figure 1. ADuM5240

V

V

V

GND

1

DD

2

OA

3

IB

4

OSC.

DECODE

Figure 2. ADuM5241

ENCODE

DECODEENCODE

V

V

GND

1

DD

2

OA

3

OB

4

OSC.

DECODE

DECODEV

Figure 3. ADuM5242

ENCODE

ENCODE

8

REG.RECT.

REG.RECT.

REG.RECT.

V

ISO

7

V

OA

6

V

OB

5

GND

ISO

8

V

ISO

7

V

IA

6

V

OB

5

GND

ISO

8

V

ISO

7

V

IA

6

V

IB

5

GND

ISO

06014-001

06014-002

06014-003

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007–2012 Analog Devices, Inc. All rights reserved.

ADuM5240/ADuM5241/ADuM5242 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

General Description ......................................................................... 1

Functional Block Diagrams ............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Characteristics ............................................................. 3

Package Characteristics ............................................................... 5

Regulatory Information ............................................................... 5

Insulation and Safety-Related Specifications ............................ 5

DIN V VDE V 0884-10 (VDE V 0884-10) Insulation

Characteristics .............................................................................. 6

Recommended Operating Conditions ...................................... 6

Absolute Maximum Ratings ............................................................ 7

REVISION HISTORY

5/12—Rev. A to Rev. B

Created Hyperlink for Safety and Regulatory Approvals

Entry in Features Section ................................................................. 1

Change to PCB Layout Section ..................................................... 12

7/07—Rev. 0 to Rev. A

Updated VDE Certification Throughout ...................................... 1

Changes to Features .......................................................................... 1

Changes to Regulatory Information Section and Table 4 ........... 5

Changes to Table 5 and Figure 4 Caption ...................................... 6

Changes to Table 7 ............................................................................ 7

Added Table 8; Renumbered Sequentially .................................... 7

Added Insulation Lifetime Section .............................................. 13

3/07—Revision 0: Initial Version

ESD Caution...................................................................................7

Pin Configurations and Function Descriptions ............................8

Typical Performance Characteristics ........................................... 10

Applications Information .............................................................. 11

DC-to-DC Converter................................................................. 11

Propagation Delay-Related Parameters ................................... 11

DC Correctness and Magnetic Field Immunity ..................... 11

Thermal Analysis ....................................................................... 12

PCB Layout ................................................................................. 12

Increasing Available Power ....................................................... 13

Insulation Lifetime ..................................................................... 13

Outline Dimensions ....................................................................... 14

Ordering Guide .......................................................................... 14

Rev. B | Page 2 of 16

Data Sheet ADuM5240/ADuM5241/ADuM5242

DC-to-DC Converter Enabled

ISO (SET )

ISO

ISO

ISO (max)

ISO

ISO

DD (max)

ISO

ISO

DD (Q)

ISO

DD (DISABLE)

DD (DISABLE)

ADuM5242

I

DD (DISABLE)

2.2

mA

VDD = 4.0 V

ISO (DISABLE)

ISO (DISABLE)

ISO (DISABLE)

DD (ENABLE)

DD (DISABLE)

ISO

ISO

OAL

OBL

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

All voltages are relative to their respective ground. All minimum/maximum specifications apply over the entire recommended operating

range, unless otherwise noted. All typical specifications are at T

Table 1.

Parameter Symbol Min Typ Max Unit Test Conditions

DC-TO-DC CONVERTER

DC to 1 Mbps Data Rate Logic signal frequency ≤ 1 MHz

Setpoint V

Maximum V

Output Current I

Noise1 250 mV p-p

Input Supply Current

At Maximum I

No Load I

Current I

Current I

DC-to-DC Converter Disabled

Primary Side Supply Input Current2

ADuM5240 I

ADuM5241 I

= 25°C, VDD = 5.0 V, V

A

4.5 5.2 5.5 V I

10 mA V

140 mA I

104 mA I

= 5.0 V, unless otherwise noted.

ISO

= 0 mA

= 4.5 V

= 10 mA

= 0 mA

3.3 mA VDD = 4.0 V

2.7 mA VDD = 4.0 V

Secondary Side Supply Input Current3

ADuM5240 I

ADuM5241 I

ADuM5242 I

DC-to-DC Conver ter Enable Threshold4 V

DC-to-DC Converter Disable Threshold4 V

2.6 mA

2.8 mA

3.0 mA

4.2 4.5 V

3.7 V

LOGIC SPECIFICATIONS

Logic Input Currents IIA, IIB −10 +0.01 +10 µA

Logic High Input Threshold VIH 0.7 (VDD or

V

)

Logic Low Input Threshold VIL 0.3 (VDD or

Logic High Output Voltages V

OAH

, V

OBH (VDD

or V

V

V

)

)

ISO

(VDD or V

) V IOx = −20 µA, VIx ≥ VIH

ISO

V

− 0.1

(VDD or V

− 0.5

Logic Low Output Voltages V

, V

0.0 0.1 V IOx = 20 µA, VIx ≤ VIL

)

(VDD or V

ISO

)

V IOx = −4 mA, VIx ≥ VIH

ISO

− 0.2

0.0 0.4 V IOx = 4 mA, VIx ≤ VIL

Rev. B | Page 3 of 16

ADuM5240/ADuM5241/ADuM5242 Data Sheet

PHL

PLH

Pulse Width Distortion, |t

PLH

− t

PHL

|8

PWD

3

ns

CL = 15 pF, CMOS signal levels

PSK

Refresh Frequency

fr 1.0 MHz

OSC

Parameter Symbol Min Typ Max Unit Test Conditions

AC SPECIFICATIONS

Minimum Pulse Width5 PW 100 ns CL = 15 pF, CMOS signal levels

Maximum Data Rate6 1 Mbps CL = 15 pF, CMOS signal levels

Propagation Delay7 t

, t

25 70 ns CL = 15 pF, CMOS signal levels

Propagation Delay Skew8 t

Channel-to-Channel Matching,

Codirectional Channels

Channel-to-Channel Matching,

Opposing-Directional Channels

9

9

45 ns CL = 15 pF, CMOS signal levels

3 ns CL = 15 pF, CMOS signal levels

t

PSKCD

15 ns CL = 15 pF, CMOS signal levels

t

PSKCD

Output Rise/Fall Time (10% to 90%) tR/tF 2.5 ns CL = 15 pF, CMOS signal levels

Common-Mode Transient

Immunity at Logic High Output

Common-Mode Transient

Immunity at Logic Low Output

Switching Frequency f

1

Peak noise occurs at frequency corresponding to the refresh frequency (see the PCB Layout section).

2

I

supply current values are specified with no load present on the digital outputs.

DD (DISAB LE)

3

I

supply current values are specified with no load present on the digital outputs and power sourced by an external supply.

ISO (DISABLE)

4

Enable/disable threshold is the VDD voltage at which the internal dc-to-dc converter is enabled/disabled.

5

The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.

6

The maximum data rate is the fastest data rate at which the specified pulse width distortion and V

7

t

propagation delay is measured from the 50% level of the falling edge of the VIx signal to the 50% level of the falling edge of the VOx signal. t

PHL

measured from the 50% level of the rising edge of the V

8

t

is the magnitude of the worst-case difference in t

PSK

load within the recommended operating conditions.

9

Channel-to-channel matching is the absolute value of the difference in propagation delays between the two channels when operated with identical loads.

|CMH| 25 35 kV/µs VIx = VDD, V

, VCM = 1000 V,

ISO

transient magnitude = 800 V

|CML| 25 35 kV/µs VIx = 0 V, VCM = 1000 V,

transient magnitude = 800 V

300 MHz

supply voltage is guaranteed.

ISO

signal to the 50% level of the rising edge of the VOx signal.

Ix

and/or t

PHL

that is measured between units at the same operating temperature, supply voltages, and output

PLH

propagation delay is

PLH

Rev. B | Page 4 of 16

Data Sheet ADuM5240/ADuM5241/ADuM5242

Resistance (Input-to-Output)

R

I-O

1012 Ω

I-O

Single/basic insulation, 2500 V rms

Basic insulation per CSA 60950-1-03

Reinforced insulation, 560 V peak

PACKAGE CHARACTERISTICS

Table 2.

Parameter Symbol Min Typ Max Unit Test Conditions

Capacitance (Input-to-Output) C

1.0 pF f = 1 MHz

Input Capacitance CI 4.0 pF

IC Junction-to-Air Thermal Resistance θJA 80 °C/W

REGULATORY INFORMATION

The ADuM524x are approved by the organizations listed in Table 3. Refer to Table 8 and the Insulation Lifetime section for details

regarding recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

Table 3.

UL CSA VDE

Recognized under 1577

Component Recognition Program

isolation rating

1

Approved under CSA Component

Acceptance Notice #5A

and IEC 60950-1, 400 V rms (566 V peak)

Certified according to DIN V VDE V 0884-10

(VDE V 0884-10):2006-122

maximum working voltage

File E214100 File 205078 File 2471900-4880-0001

1

In accordance with UL 1577, each ADuM524x is proof-tested by applying an insulation test voltage ≥ 3000 V rms for 1 second (current leakage detection limit = 5 µA).

2

In accordance with DIN V VDE V 0884-10, each ADuM524x is proof-tested by applying an insulation test voltage ≥ 1050 V peak for 1 sec (partial discharge detection

limit = 5 pC). The asterisk (*) marking branded on the component designates DIN V VDE V 0884-10

approval.

INSULATION AND SAFETY-RELATED SPECIFICATIONS

Table 4.

Parameter Symbol Value Unit Conditions

Rated Dielectric Insulation Voltage 2500 V rms 1-minute duration

Minimum External Air Gap (Clearance) L(I01) 4.90 min mm Measured from input terminals to output

terminals, shortest distance through air

Minimum External Tracking (Creepage) L(I02) 4.01 min mm Measured from input terminals to output

terminals, shortest distance path along body

Minimum Internal Gap (Internal Clearance) 0.017 min mm Insulation distance through insulation

Tracking Resistance (Comparative Tracking Index) CTI >175 V DIN IEC 112/VDE 0303 Part 1

Isolation Group IIIa Material Group (DIN VDE 0110, 1/89, Table 1)

Maximum Working Voltage Compatible with

50-Year Service Life

V

425 V peak Continuous peak voltage across the

IORM

isolation barrier

Rev. B | Page 5 of 16

Loading...

Loading...