集成

ADuM3470/ADuM3471/

ADuM3472/ADuM3473/

ADuM3474

09369-001

CONVERTER

PRIMARY

DRIVER

PRIMARY

DATA

I/O

4CH

SECONDARY

DATA

I/O

4CH

SECONDARY

CONTROLLER

CHA

FB

T1

CHB

CHC

CHD

V

DD2

OC

FB

V

REG

I/OA

V

CC

V

DDA

V

DD1

1X2X

I/OB

I/OC

I/OD

I/OA

I/OB

I/OC

I/OD

GND

1

GND

2

REG

RECT

5V

V

ISO

9369-003

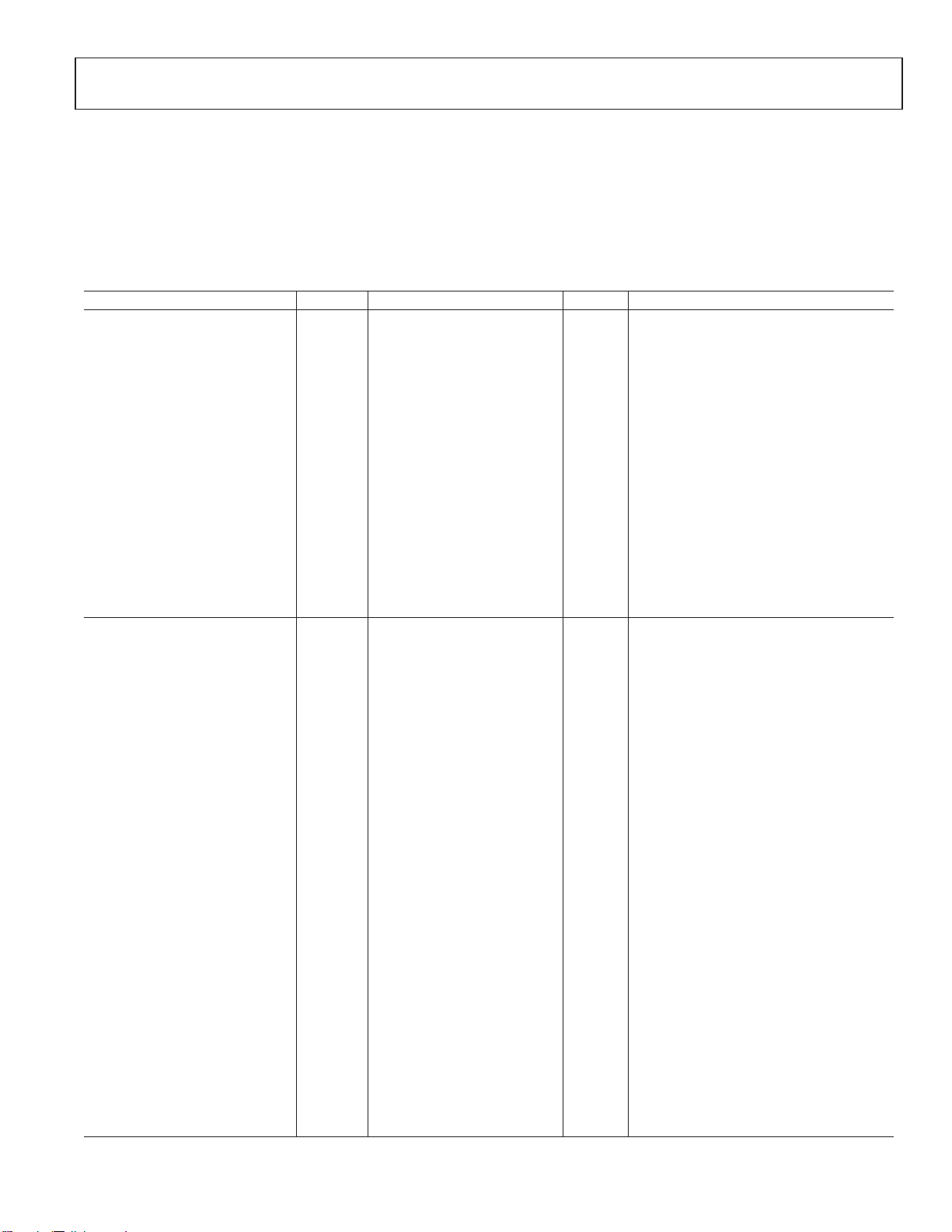

ADuM3470 ADuM3471

ADuM3472

ADuM3473 ADuM3474

PWM

控制器和变压器驱动器

的四通道隔离器

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

主要特性

隔离式

集成变压器驱动器

可调的稳压输出 :

输出功率

2 W

效率 :

四个

DC-25 Mbps (NRZ)

引脚

20

工作温度最高可达

高共模瞬变抗扰度 :

可调振荡器频率 :

上电时提供软启动功能

逐脉冲过流保护

热关断

2500 V rms

控制器

PWM

3.3 V至24 V

70%(400 mA

封装

SSOP

105

200 kHz至1 MHz

隔离

保证负载、

°

>25 kV/μs

应用

RS-232/RS-422/RS-485

工业现场总线隔离

电源启动偏置和栅极驱动

隔离传感器接口

过程控制

5.0 V

信号隔离通道

C

收发器

输出时)

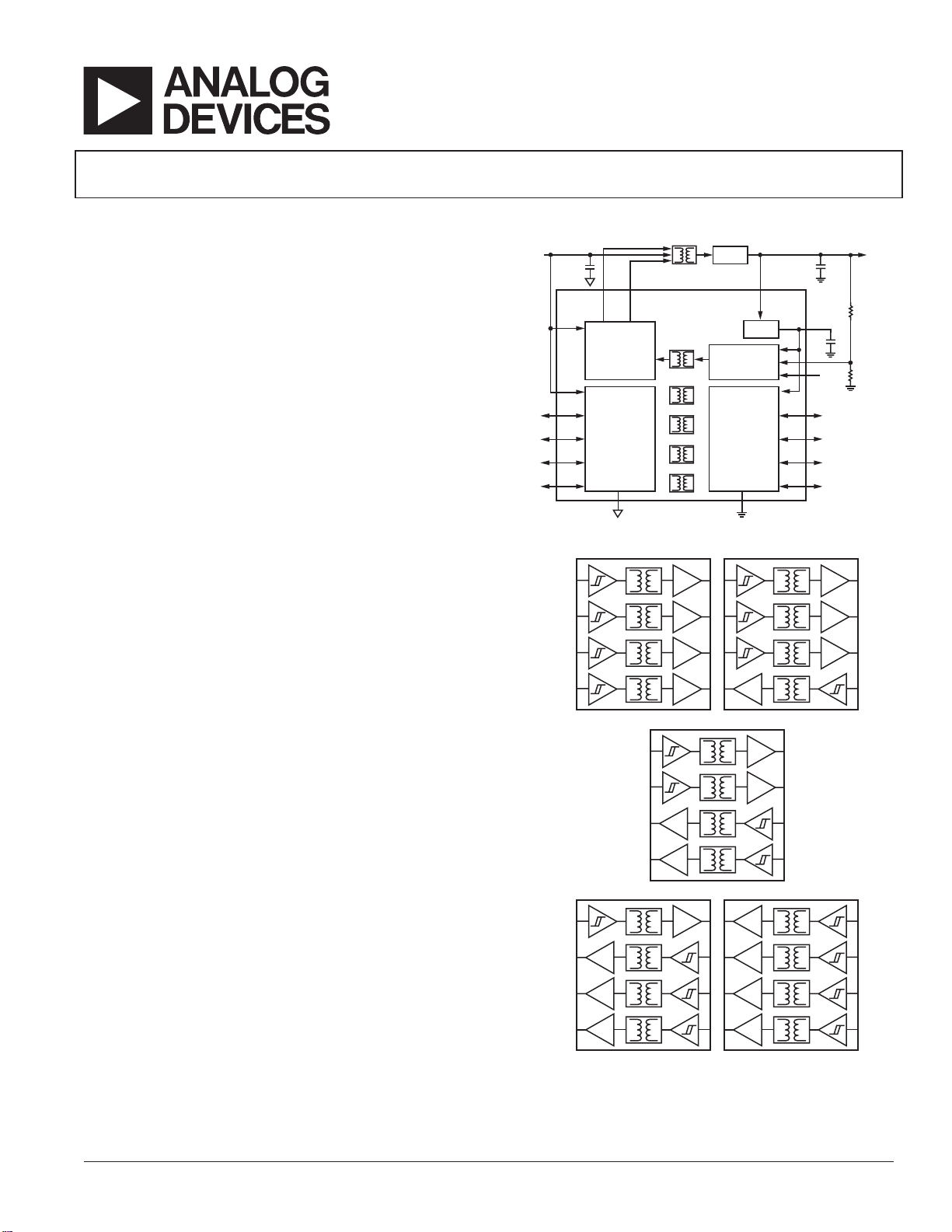

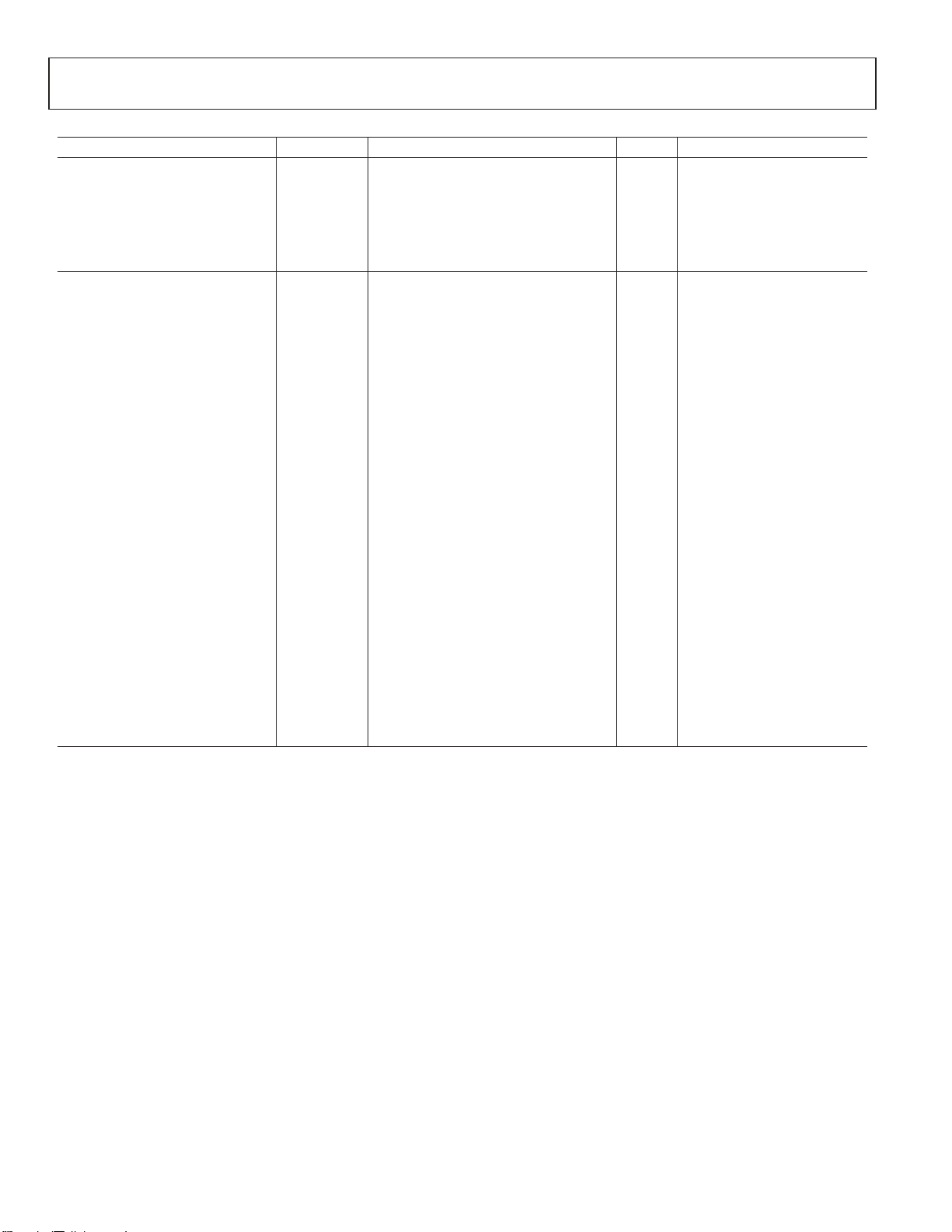

功能框图

图

功能框图

1.

概述

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

器件1为四通道数字隔离器,集成

驱动器用以驱动隔离式

基于

ADI

公司的

i

Coupler®

DC/DC

转换器。该

技术,提供

的调节隔离电源,输入电源电压为

隔离设计中,无需使用单独的隔离式

2 W

i

Coupler

芯片级变压器技术用于隔离逻辑信号 ;集成的变

压器驱动器带隔离副边控制功能,可以提高隔离式

转换器的效率,因此,可提供小尺寸、完全隔离的解决方案。

ADuM347x

隔离器提供四个独立的隔离通道,支持多种通

道配置和数据速率。(本数据手册内提及的

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

1

受第5,952,849号、6,873,065号和7075 329 B2

利正在申请中。

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parti es that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,

ADI

新英文版数据手册。

控制器和变压器

PWM

DC/DC

2 W、3.3 V至24 V

DC/DC

。这样在

转换器。

5.0 V或3.3 V

DC/DC

ADuM347x

号美国专利保护。其它专

转换器

代表

。)

图

通道框图

2. I/O

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考

ADI

www.analog.com

ADI

提供的最

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

目录

主要特性

应用

概述

功能框图

修订历史

技术规格

绝对最大额定值

............................................................................................ 1

.....................................................................................................1

.....................................................................................................1

............................................................................................ 1

............................................................................................ 2

............................................................................................ 3

电气特性—

电气特性—

电气特性—

电气特性—

封装特性

法规认证(申请中)

隔离和安全相关特性

DIN V VDE V 0884-10 (VDE V 0884-10)

建议工作条件

原边输入电源

5 V

原边输入电源

3.3 V

原边输入电源

5 V

原边输入电源

5 V

......................................................................................11

..................................................................11

................................................................11

.............................................................................12

.............................................................................13

副边隔离电源

/5 V

/3.3 V

副边隔离电源

/3.3 V

副边隔离电源

/15 V

副边隔离电源

隔离特性

.............3

.......5

..........7

...........9

...........12

应用信息

..........................................................................................25

工作原理

应用原理图

变压器设计

变压器匝数比

变压器ET常数

变压器原边电感和电阻

变压器隔离电压

开关频率

瞬态响应

元件选择

印刷电路板(

热分析

传播延迟相关参数

直流正确性和磁场抗扰度

功耗

......................................................................................25

.................................................................................25

.................................................................................26

.............................................................................26

..........................................................................26

...........................................................26

........................................................................27

......................................................................................27

......................................................................................27

......................................................................................27

)布局

PCB

..........................................................................................28

..............................................................................................30

........................................................28

.................................................................... 28

.......................................................29

警告

ESD

引脚配置和功能描述

典型工作特性

术语

......................................................................................13

.................................................................... 14

.................................................................................19

...................................................................................................24

修订历史

2010年10

月—修订版0:初始版

电源考虑

隔离寿命

外形尺寸

订购指南

......................................................................................30

......................................................................................31

..........................................................................................32

......................................................................................32

Rev. 0 | Page 2 of 32

技术规格

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

电气特性—

4.5 V ≤ (V

所有最小/最大值规格适用于整个推荐的工作范围。所有典型规格在

DD1

原边输入电源

5 V

= V

) ≤ 5.5 V,V

DDA

DD2

= V

副边隔离电源

/5 V

= V

REG

= 5.0 V,fSW = 500 kHz

ISO

,所有电压均参照其各自的地,参见图38应用原理图。除非另有说明,

TA = 25°C、V

DD1

= V

= 5.0 V和V

DDA

条件下测得。

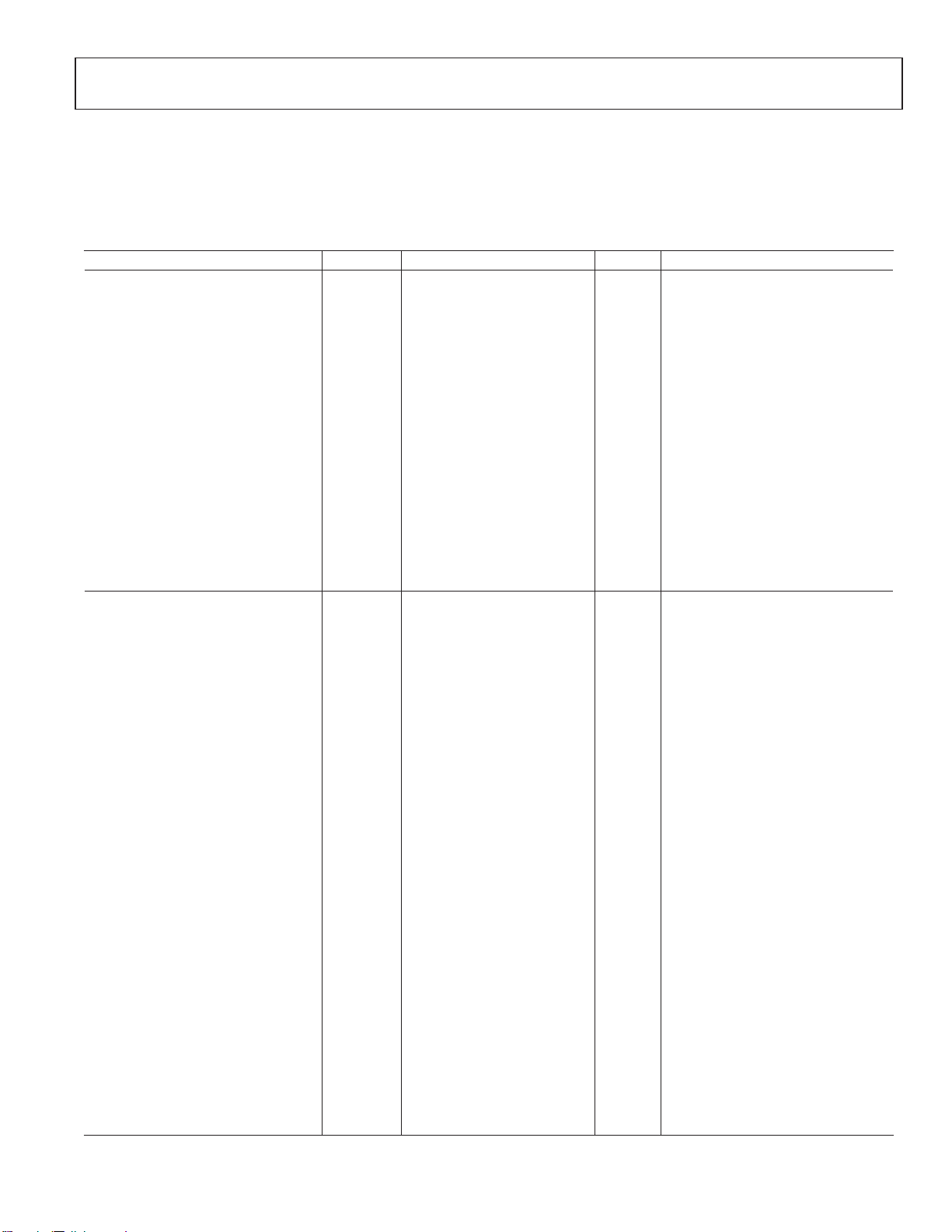

表

1

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

转换器电源

DC/DC

隔离输出电压

反馈电压设定点

电压调整率

负载调整率

输出纹波

输出噪声

开关频率

开关导通电阻

欠压闭锁,

和

V

V

CC

DD2

趋正阈值

趋负阈值

迟滞

i

Coupler

数据通道

DC至2 Mbps

数据速率

最大输出电源电流

最大输出电源电流时的效率

电源电流,无

I

CC

V

2

ISO

供电

1

负载

V

ISO

V

FB

V

ISO (LINE)

V

ISO (LOAD)

V

ISO (RIP)

V

ISO (N)

f

SW

R

ON

V

UV+

V

UV-

V

UVH

I

ISO (MAX)

3

I

CC (Q)

4.5 5.0 5.5 V I

1.15 1.25 1.35 V I

1 10 mV/V I

1 2 % I

50 mV p-p 20 MHz

100 mV p-p 20 MHz

1000

200

kHz

kHz

192 318 515 kHz VOC = V

0.5

Ω

= 0 mA, V

ISO

= 0 mA

ISO

= 50 mA,VCC = 4.5 V至5.5 V

ISO

= 50 mA至200 mA

ISO

带宽

C

= 0.1 μF||47 μF,I

OUT

带宽

C

= 0.1 μF||47 μF,I

OUT

ROC = 50 k

Ω

ROC = 270 k

(开环)

DD2

2.8 V

2.6 V

0.2 V

400 mA f ≤ 1 MHz, V

70 % I

= I

ISO

ISO (MAX)

I

= 0 mA, f ≤ 1 MHz

ISO

Ω

ADuM3470 14 30 mA

ADuM3471 15 30 mA

ADuM3472 16 30 mA

ADuM3473 17 30 mA

ADuM3474 18 30 mA

25 Mbps

数据速率(仅

电源电流,无

I

CC

V

ISO

ADuM3470 44 mA I

ADuM3471 46 mA I

ADuM3472 48 mA I

ADuM3473 50 mA I

ADuM3474 52 mA I

可用

V

ISO

电源电流

CRWZ

负载

4

级)

ICC

(D)

I

ISO (LOAD)

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

fSW= 500 kHz

ADuM3470 390 mA CL = 15 pF, f = 12.5 MHZ

ADuM3471 388 mA CL = 15 pF, f = 12.5 MHZ

ADuM3472 386 mA CL = 15 pF, f = 12.5 MHZ

ADuM3473 384 mA CL = 15 pF, f = 12.5 MHZ

ADuM3474 382 mA CL = 15 pF, f = 12.5 MHZ

电源电流,满

I

CC

输入电流

I/O

逻辑高电平输入阈值

逻辑低电平输入阈值

负载

V

ISO

ICC

L

I

V

V

(MAX)

、

、

I

I A

和

IC

IH

IL

-20 +0.01 +20 µA

I B

I

ID

2.0 V

550 mA CL = 0 pF, f = 0 MHZ, VDD = 5 V, I

0.8 V

= V

DD2

= VFB × (R1 + R2)/R2

ISO

= 100 mA

ISO

= 100 mA

ISO

= 5.0 V

ISO

, f ≤ 1 MHz

REG

= V

ISO

= 400 mA

ISO

= 5.0 V

Rev. 0 | Page 3 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

逻辑高电平输出电压

逻辑低电平输出电压

交流规格

ADuM347xARWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

传播延迟偏斜

通道间匹配

t

ADuM347xCRWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

温度变化率

传播延迟偏斜

通道间匹配,同向通道

通道间匹配,反向通道

输出上升/下降时间(

90%)

逻辑高电平输出时的共模瞬变

抗扰度

逻辑低电平输出时的共模瞬变

抗扰度

刷新速率

1

所有四个通道的电源电流值贡献以相同数据速率合并。

2

当所有数据速率均低于

率工作的各通道所消耗的额外电源电流可按照“功耗”部分所述进行计算。必须将动态

3

数据通道静态工作的功耗需求不能与电源部分分开。效率要考虑

4

此电流可用于驱动

时的可用电流计算,请参考“功耗”部分。

f

V

V

, V

,

V

0.3, V

OAH

OBH

V

, V

OCH

ODH

, V

,

OAL

OBL

V

, V

OCL

ODL

−

CC

ISO

V

0.5, V

−

CC

ISO

5.0 V IOx= −20 μA, VIx= V

0.3

−

4.8 V IOx= −4 mA, VIx= V

0.3

−

0.0 0.1 V IOx= 20 μA, VIx= V

0.0 0.4 V IOx= 4 mA, VIx= V

PW 1000 ns CL= 15 pF,CMOS

1 Mbps CL= 15 pF,CMOS

|t

PLH

| PWD 40 ns CL= 15 pF,CMOS

t

−

PHL

t

, t

PHL

PLH

PSK

PSKCD/tPSKOD

55 100 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

PW 40 ns CL= 15 pF,CMOS

25 Mbps CL= 15 pF,CMOS

, t

PHL

PLH

|t

PLH

| PWD 6 ns CL= 15 pF,CMOS

t

−

PHL

30 45 60 ns CL= 15 pF,CMOS

5 ps/°C CL= 15 pF,CMOS

t

t

t

至

10%

PSK

PSKCD

PSKOD

tR/t

F

2.5 ns CL= 15 pF,CMOS

|CMH| 25 35 kV/µs VIx = V

15 ns CL= 15 pF,CMOS

6 ns CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

或

V

DD

瞬变幅度

= 800 V

|CML| 25 35 kV/µs VIx = 0 V,V = 1000 V

度

= 800 V

r

2 Mbps时,V

输出引脚上的外部负载。同时以

V

ISO

电源电流可供外部使用。当数据速率高于

ISO

通道的静态功耗,它是内部功耗的一部分。

I/O

的最大数据速率驱动所有通道,满容性负载表示最大动态负载条件。有关低于最大数据速率

25 Mbps

1.0 Mbps

2 Mbps

时,数据

通道负载视作外部负载,并包括在

I/O

通道汲取与数据速率成正比的额外电流。以给定数据速

I/O

功耗预算中。

V

ISO

IxH

IxH

IxL

IxL

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

,

VCM = 1000 V

ISO

,

,瞬变幅

Rev. 0 | Page 4 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

电气特性—

3.0 V ≤ (V

说明,所有最小/最大值规格适用于整个推荐的工作范围。所有典型规格在

DD1

= V

原边输入电源

3.3 V

) ≤ 3.6 V,V

DDA

DD2

= V

/3.3 V

= V

REG

副边隔离电源

= 3.3 V,fSW = 500 kHz

ISO

,所有电压均参照其各自的地,参见图38应用原理图。除非另有

TA = 25°C、V

DD1

= V

= 3.3 V、V

DDA

条件下测得。

表

2

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

转换器电源

DC/DC

隔离输出电压

反馈电压设定点

电压调整率

负载调整率

输出纹波

输出噪声

开关频率

开关导通电阻

欠压闭锁,

和

V

V

CC

DD2

趋正阈值

趋负阈值

迟滞

i

Coupler

数据通道

DC至2 Mbps

数据速率

最大输出电源电流

最大输出电源电流时的效率

电源电流,无

I

CC

V

2

ISO

供电

1

负载

V

ISO

V

FB

V

ISO (LINE)

V

ISO (LOAD)

V

ISO (RIP)

V

ISO (N)

F

SW

R

ON

V

UV+

V

UV-

V

UVH

I

ISO (MAX)

3

I

CC(Q)

3.0 3.3 3.6 V I

1.15 1.25 1.35 V I

1 10 mV/V I

1 2 % I

50 mV p-p 20 MHz

100 mV p-p 20 MHz

1000

200

kHz

kHz

192 318 515 kHz VOC = V

0.6

Ω

= 0 mA, V

ISO

= 0 mA

ISO

= 50 mA,VCC = 3.0 V至3.6 V

ISO

= 20 mA至100 mA

ISO

带宽

C

= 0.1 μF||47 μF,I

OUT

带宽

C

= 0.1 μF||47 μF, I

OUT

ROC = 50 K

ROC = 270 k

(开环)

DD2

2.8 V

2.6 V

0.2 V

250 mA f < 1 MHz, V

70 % I

= I

ISO

ISO (MAX)

I

= 0 mA, f ≤ 1 MHz

ISO

Ω

Ω

ISO

, f ≤ 1 MHz

ADuM3470 9 20 mA

ADuM3471 10 20 mA

ADuM3472 11 20 mA

ADuM3473 11 20 mA

ADuM3474 12 20 mA

25 Mbps

数据速率(仅

电源电流,无

I

CC

V

ISO

ADuM3470 28 mA I

ADuM3471 29 mA I

ADuM3472 31 mA I

ADuM3473 32 mA I

ADuM3474 34 mA I

可用

V

ISO

电源电流

4

CRWZ

负载

级)

ICC

(D)

I

ISO (LOAD)

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHZ

ISO

ADuM3470 244 mA CL = 15 pF, f = 12.5 MHz

ADuM3471 243 mA CL = 15 pF, f = 12.5 MHz

ADuM3472 241 mA CL = 15 pF, f = 12.5 MHz

ADuM3473 240 mA CL = 15 pF, f = 12.5 MHz

ADuM3474 238 mA CL = 15 pF, f = 12.5 MHz

电源电流,满

I

CC

输入电流

I/O

逻辑高电平输入阈值

逻辑低电平输入阈值

负载

V

ISO

ICC

(MAX)

LIA, IIB, IIC, I

V

IH

V

IL

350 mA CL = 0 pF, f = 0 MHz, VDD = 3.3 V,

-10 +0.01 +10 µA

ID

1.6 V

0.4 V

I

= 250 mA

ISO

= V

REG

= 100 mA

ISO

= 100 mA

ISO

= V

DD2

= VFB × (R1 + R2)/R2

ISO

= 3.3 V

= 3.3 V

ISO

Rev. 0 | Page 5 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

逻辑高电平输出电压

逻辑低电平输出电压

交流规格

ADuM347xARWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

传播延迟偏斜

通道间匹配

ADuM347xCRWZ

最小脉冲宽度

最大数据速率

传播延迟

脉冲宽度失真,

温度变化率

传播延迟偏斜

通道间匹配,同向通道

通道间匹配,反向通道

输 出 上 升/下 降 时 间(

至

90%)

逻辑高电平输出时的共模瞬

变抗扰度

逻辑低电平输出时的共模瞬

变抗扰度

刷新速率

1

所有四个通道的电源电流值贡献以相同数据速率合并。

2

当所有数据速率均低于

率工作的各通道所消耗的额外电源电流可按照“功耗”部分所述进行计算。必须将动态

3

数据通道静态工作的功耗需求不能与电源部分分开。效率要考虑

4

此电流可用于驱动

时的可用电流计算,请参考“功耗”部分。

f

V

V

, V

,

V

0.2, V

OAH

OBH

V

, V

OCH

ODH

, V

,

OAL

OBL

V

, V

OCL

ODL

−

CC

V

0.5, V

−

CC

−

ISO

−

ISO

5.0 V IOx= −20 μA, VIx= V

0.2

4.8 V IOx= −4 mA, VIx= V

0.5

0.0 0.1 V IOx= 20 μA, VIx= V

0.0 0.4 V IOx= 4 mA, VIx= V

PW 1000 ns CL= 15 pF,CMOS

1 Mbps CL= 15 pF,CMOS

|t

| PWD 40 ns CL= 15 pF,CMOS

t

−

PLH

PHL

t

t

|t

| PWD 8 ns CL= 15 pF,CMOS

t

−

PLH

PHL

10%

, t

PHL

PLH

PSK

PSKCD/tPSKOD

PW 40 ns CL= 15 pF,CMOS

25 Mbps CL= 15 pF,CMOS

t

PHL

t

PSK

t

PSKCD

t

PSKOD

tR/t

, t

PLH

F

30 60 75 ns CL= 15 pF,CMOS

|CMH| 25 35 kV/μs VIx = V

60 100 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

5 ps/°C CL= 15 pF,CMOS

45 ns CL= 15 pF,CMOS

8 ns CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

2.5 ns CL= 15 pF,CMOS

或

DD

瞬变幅度

= 800 V

|CML| 25 35 kV/μs VIx = 0 V,V= 1000 V

r

2 Mbps时,V

输出引脚上的外部负载。同时以

V

ISO

电源电流可供外部使用。当数据速率高于

ISO

1.0 Mbps

时,数据

2 Mbps

通道的静态功耗,它是内部功耗的一部分。

I/O

的最大数据速率驱动所有通道,满容性负载表示最大动态负载条件。有关低于最大数据速率

25 Mbps

通道负载视作外部负载,并包括在

I/O

通道汲取与数据速率成正比的额外电流。以给定数据速

I/O

度

= 800 V

V

功耗预算中。

ISO

IxL

IxL

,

V

VCM = 1000 V

ISO

IxH

IxH

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

,

,瞬变幅

Rev. 0 | Page 6 of 32

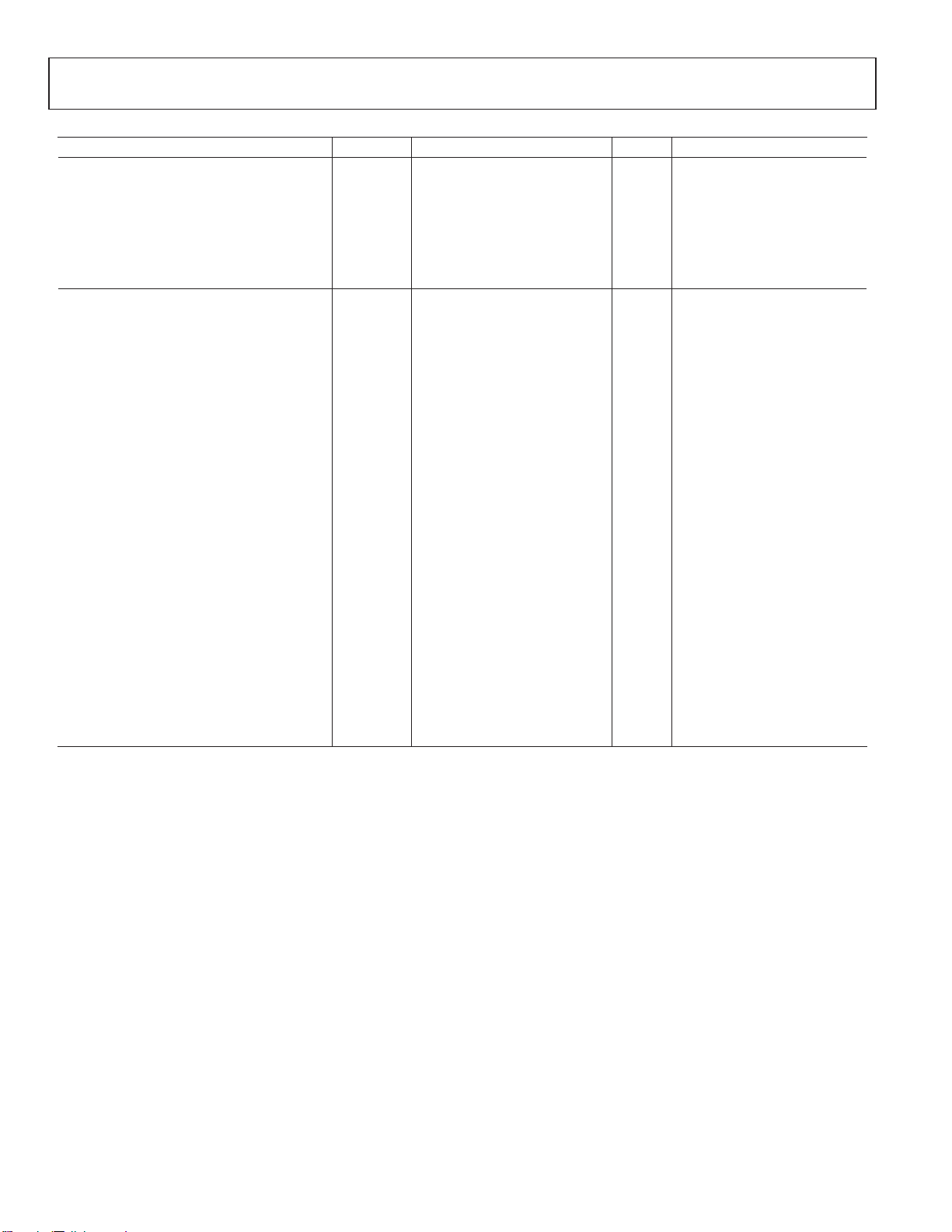

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

电气特性—

4.5 V ≤ (V

有说明,所有最小/最大值规格适用于整个推荐的工作范围。所有典型规格在

DD1

原边输入电源

5 V

= V

) ≤ 5.5 V,V

DDA

DD2

= V

/3.3 V

= V

REG

副边隔离电源

= 3.3 V,fSW = 500 kHz

ISO

,所有电压均参照其各自的地,参见图38应用原理图。除非另

= 25°C、V

T

A

DD1

= V

= 5.0 V、V

DDA

条件下测得。

表

3

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

转换器电源

DC/DC

隔离输出电压

反馈电压设定点

电压调整率

负载调整率

输出纹波

输出噪声

开关频率

开关导通电阻

欠压闭锁,

和

V

V

CC

趋正阈值

趋负阈值

迟滞

i

Coupler

数据通道

DC至2 Mbps

数据速率

最大输出电源电流

最大输出电源电流时的效率

电源电流,无

I

CC

DD2

V

2

ISO

供电

1

负载

V

ISO

V

FB

V

ISO (LINE)

V

ISO (LOAD)

V

ISO (RIP)

V

ISO (N)

f

SW

R

ON

V

UV+

V

UV-

V

UVH

I

ISO (MAX)

3

ICC

(Q)

3.0 3.3 3.6 V I

1.15 1.25 1.35 V I

1 10 mV/V I

1 2 % I

50 mV p-p 20 MHz

100 mV p-p 20 MHz

1000

200

kHz

kHz

209 318 515 kHz VOC = V

0.5

Ω

= 0 mA, V

ISO

= 0 mA

ISO

= 50 mA,VCC = 4.5 V至5.5 V

ISO

= 50 mA至200 mA

ISO

带宽

C

= 0.1 μF||47 μF,I

OUT

带宽

C

= 0.1 μF||47 μF,I

OUT

ROC = 50 k

ROC = 270 k

(开环)

DD2

2.8 V

2.6 V

0.2 V

400 mA f ≤ 1 MHz, V

70 % I

= I

ISO

ISO (MAX)

I

= 0 mA, f ≤ 1 MHz

ISO

Ω

Ω

ADuM3470 9 30 mA

ADuM3471 9 30 mA

ADuM3472 10 30 mA

ADuM3473 10 30 mA

ADuM3474 10 30 mA

25 Mbps

数据速率(仅

电源电流,无

I

CC

V

ISO

ADuM3470 33 mA I

ADuM3471 33 mA I

ADuM3472 33 mA I

ADuM3473 33 mA I

ADuM3474 33 mA I

可用

V

ISO

电源电流

4

CRWZ

负载

级)

ICC

(D)

I

ISO (LOAD)

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

ADuM3470 393 mA CL = 15 pF, f = 12.5 MHz

ADuM3471 392 mA CL = 15 pF, f = 12.5 MHz

ADuM3472 390 mA CL = 15 pF, f = 12.5 MHz

ADuM3473 389 mA CL = 15 pF,f = 12.5 MHz

ADuM3474 388 mA CL = 15 pF,f = 12.5 MHz

电源电流,满

I

CC

输入电流

I/O

逻辑高电平输入阈值

逻辑低电平输入阈值

负载

V

ISO

ICC

(MAX)

375 mA CL = 0 pF,f = 0 MHz,VDD = 5 V,

LIA, IIB, IIC, IID-20 +0.01 +20

V

IH

V

IL

2.0 V

0.8 V

I

= 400 mA

ISO

A

μ

= V

DD2

= VFB × (R1 + R2)/R2

ISO

= 3.3 V

ISO

= V

REG

= 100 mA

ISO

= 100 mA

ISO

, f ≤ 1 MHz

= 3.3 V

ISO

Rev. 0 | Page 7 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

逻辑高电平输出电压

逻辑低电平输出电压

交流规格

ADuM347xARWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

传播延迟偏斜

通道间匹配

ADuM347xCRWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

温度变化率

传播延迟偏斜

通道间匹配,同向通道

通道间匹配,反向通道

输出上升/下降时间(

逻辑高电平输出时的共模瞬变抗扰度

逻辑低电平输出时的共模瞬变抗扰度

刷新速率

1

所有四个通道的电源电流值贡献以相同数据速率合并。

2

当所有数据速率均低于

率工作的各通道所消耗的额外电源电流可按照“功耗”部分所述进行计算。必须将动态

3

数据通道静态工作的功耗需求不能与电源部分分开。效率要考虑

4

此电流可用于驱动

时的可用电流计算,请参考“功耗”部分。

f

V

V

, V

,

V

0.3,

OAH

OBH

V

, V

OCH

ODH

, V

,

OAL

OBL

V

, V

OCL

ODL

−

CC

V

0.3

−

ISO

V

0.5,

−

CC

V

0.3

−

ISO

5.0 V IOx= −20 μA, VIx= V

4.8 V IOx= −4 mA, VIx= V

0.0 0.1 V IOx= 20 μA, VIx= V

0.0 0.4 V IOx= 4 mA, VIx= V

PW 1000 ns CL= 15 pF,CMOS

1 Mbps CL= 15 pF,CMOS

|t

| PWD 40 ns CL= 15 pF,CMOS

t

−

PLH

PHL

t

t

, t

PHL

PLH

PSK

PSKCD/tPSKOD

55 100 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

PW 40 ns CL= 15 pF,CMOS

25 Mbps CL= 15 pF,CMOS

, t

PHL

PLH

|t

| PWD 8 ns CL= 15 pF,CMOS

t

−

PLH

PHL

30 50 70 ns CL= 15 pF,CMOS

5 ps/°C CL= 15 pF,CMOS

t

t

t

10%至90%) tR/t

|CMH| 25 35 kV/μs VIx = V

PSK

PSKCD

PSKOD

F

2.5 ns CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

8 ns CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

或

DD

瞬变幅度

= 800 V

|CML| 25 35 kV/μs VIx = 0 V,V = 1000 V,

2 Mbps时,V

输出引脚上的外部负载。同时以

V

ISO

电源电流可供外部使用。当数据速率高于

ISO

r

25 Mbps

瞬变幅度

1.0 Mbps

时,数据

2 Mbps

通道的静态功耗,它是内部功耗的一部分。

I/O

的最大数据速率驱动所有通道,满容性负载表示最大动态负载条件。有关低于最大数据速率

通道负载视作外部负载,并包括在

I/O

通道汲取与数据速率成正比的额外电流。以给定数据速

I/O

= 800 V

功耗预算中。

V

ISO

IxH

IxL

IxL

,

V

VCM = 1000 V,

ISO

IxH

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

Rev. 0 | Page 8 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

电气特性—

4.5 V ≤ (V

除非另有说明,所有最小/最大值规格适用于整个推荐的工作范围。所有典型规格在

V

DD2

表

DD1

= 5.0 V

4

原边输入电源

5 V

= V

) ≤ 5.5 V,V

DDA

条件下测得。

REG

= V

副边隔离电源

/15 V

= 15 V,V

ISO

= 5.0 V,fSW = 500 kHz

DD2

,所有电压均参照其各自的地,参见图39应用原理图。

= 25°C、V

T

A

DD1

= V

= 5.0 V、V

DDA

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

转换器电源

DC/DC

隔离输出电压

反馈电压设定点

线性稳压器

V

DD2

稳压器电压

压差

电压调整率

负载调整率

输出纹波

输出噪声

开关频率

开关导通电阻

欠压闭锁,

和

V

V

CC

DD2

趋正阈值

趋负阈值

迟滞

i

Coupler

数据通道

DC至2 Mbps

数据速率

最大输出电源电流

最大输出电源电流时的效率

电源电流,无

I

CC

V

2

ISO

供电

1

负载

V

ISO

V

FB

V

DD2

V

DD2DO

V

ISO (LINE)

V

ISO (LOAD)

V

ISO (RIP)

V

ISO (N)

f

SW

13.8 15 16.2 V I

1.15 1.25 1.35 V I

4.6 5.0 5.4 V V

0.5 1.5 V I

1 10 mV/V I

1 3 % I

200 mV p-p 20 MHz

500 mV p-p 20 MHz

1000

200

192 318 515 kHz VOC = V

R

ON

V

UV+

V

UV-

V

UVH

I

ISO (MAX)

3

100 mA f ≤ 1 MHz, ViSO = 5.0 V

0.5

2.8 V

2.6 V

0.2 V

70 % I

ICC (Q) I

kHz

kHz

Ω

= 0 mA, V

ISO

= 0 mA

ISO

= 7 V至15 V,I

REG

50 mA

= 50 mA

DD2

= 50 mA, VCC = 4.5 V至5.5 V

ISO

= 20 mA至100 mA

ISO

ISO

带宽

C

= 0.1 μF||47 μF,I

OUT

带宽

C

= 0.1 μF||47 μF,I

OUT

ROC = 50 k

ROC = 270 k

ISO

ISO

Ω

Ω

(开环)

DD2

= I

ISO (MAX)

, f ≤ 1 MHz

= 0 mA, f ≤ 1 MHz

ADuM3470 25 45 mA

ADuM3471 27 45 mA

ADuM3472 29 45 mA

ADuM3473 31 45 mA

ADuM3474 33 45 mA

25 Mbps

数据速率(仅

电源电流,无

I

CC

V

ISO

ADuM3470 73 mA I

ADuM3471 83 mA I

ADuM3472 93 mA I

ADuM3473 102 mA I

ADuM3474 112 mA I

可用

V

ISO

电源电流

4

CRWZ

负载

级)

I

CC(D)

I

ISO (LOAD)

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

= 0 mA, CL = 15 pF, f = 12.5 MHz

ISO

ADuM3470 91 mA CL = 15 pF, f = 12.5 MHz

ADuM3471 89 mA CL = 15 pF, f = 12.5 MHz

ADuM3472 86 mA CL = 15 pF, f = 12.5 MHz

ADuM3473 83 mA CL = 15 pF, f = 12.5 MHz

ADuM3474 80 mA CL = 15 pF, f = 12.5 MHz

电源电流,满

I

CC

输入电流

I/O

逻辑高电平输入阈值

逻辑低电平输入阈值

负载

V

ISO

ICC

(MAX)

425 mA CL = 0 p F, f = 0 MHz, VDD = 5 V,

LIA, IIB, IIC, IID-20 +0.01 +20

V

IH

V

IL

2.0 V

0.8 V

I

= 100 mA

A

μ

ISO

= V

REG

= 15 V、

ISO

= VFB × (R1 + R2)/R2

= 0 mA

DD2

= 100 mA

ISO

= 100 mA

ISO

至

Rev. 0 | Page 9 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

参数 符号 最小值 典型值 最大值 单位 测试条件/注释

逻辑高电平输出电压

逻辑低电平输出电压

交流规格

ADuM347xARWZ

最小脉冲宽度

最大数据速率

传播延迟

t

脉冲宽度失真,

传播延迟偏斜

通道间匹配

ADuM347xCRWZ

最小脉冲宽度

最大数据速率

传播延迟

脉冲宽度失真,

温度变化率

传播延迟偏斜

通道间匹配,同向通道

通道间匹配,反向通道

输出上升/下降时间(

90%)

逻辑高电平输出时的共模瞬变

抗扰度

逻辑低电平输出时的共模瞬变

抗扰度

刷新速率

1

所有四个通道的电源电流值贡献以相同数据速率合并。

2

当所有数据速率均低于

率工作的各通道所消耗的额外电源电流可按照“功耗”部分所述进行计算。必须将动态

3

数据通道静态工作的功耗需求不能与电源部分分开。效率要考虑

4

此电流可用于驱动

时的可用电流计算,请参考“功耗”部分。

f

V

V

, V

,

V

0.3, V

OAH

OBH

V

, V

OCH

ODH

, V

,

OAL

OBL

V

, V

OCL

ODL

−

CC

V

CC

0.5, V

−

ISO

ISO

5.0 V IOx= −20 μA, VIx= V

0.3

−

4.8 V IOx= −4 mA, VIx= V

0.3

−

0.0 0.1 V IOx= 20 μA, VIx= V

0.0 0.4 V IOx= 4 mA, VIx= V

PW 1000 ns CL= 15 pF,CMOS

1 Mbps CL= 15 pF,CMOS

|t

| PWD 40 ns CL= 15 pF,CMOS

t

−

PLH

PHL

t

t

|t

| PWD 6 ns CL= 15 pF,CMOS

t

−

PLH

PHL

至

10%

, t

PHL

PLH

PSK

PSKCD/tPSKOD

PW 40 ns CL= 15 pF,CMOS

25 Mbps CL= 15 pF,CMOS

t

PHL

t

PSK

t

PSKCD

t

PSKOD

tR/t

, t

PLH

F

30 45 60 ns CL= 15 pF,CMOS

|CMH| 25 35 kV/μs VIx = V

55 100 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

50 ns CL= 15 pF,CMOS

5 ps/°C CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

6 ns CL= 15 pF,CMOS

15 ns CL= 15 pF,CMOS

2.5 ns CL= 15 pF,CMOS

或

DD

瞬变幅度

= 800 V

|CML| 25 35 kV/μs VIx = 0 V,V = 1000 V

幅度

= 800 V

1.0 Mbps

2 Mbps

时,数据

通道负载视作外部负载,并包括在

I/O

通道汲取与数据速率成正比的额外电流。以给定数据速

I/O

功耗预算中。

V

ISO

2 Mbps时,V

输出引脚上的外部负载。同时以

V

ISO

电源电流可供外部使用。当数据速率高于

ISO

r

通道的静态功耗,它是内部功耗的一部分。

I/O

的最大数据速率驱动所有通道,满容性负载表示最大动态负载条件。有关低于最大数据速率

25 Mbps

IxL

IxL

,

V

VCM = 1000 V

ISO

IxH

IxH

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

信号电平

,

,瞬变

Rev. 0 | Page 10 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

封装特性

表

5

参数

电阻(输入至输出)

电容(输入至输出)

输入电容

IC

热关断

2

结至环境热阻

热关断阈值

热关断迟滞

1

假设器件为双端器件 :引脚1与引脚8短路,引脚9与引脚16短路。

2

输入电容是从任意输入数据引脚到地的容值。

3

热模型定义见热分析部分。

1

1

TS

TS

法规认证(申请中)

表

6

UL CSA VDE

UL 1577

单一保护,

文件

1

依据UL1577, 每个ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

2

依据

示通过

器件认可程序认可

2500 V rms

E214100

DIN V VDE V 0884-10

DIN V VDE V 0884-10

隔离电压

,每个

认证。

1

ADuM347x

符号

R

I-O

C

I-O

C

I

θ

JA

SD

SD-HYS

最小值 典型值 最大值 单位 测试条件/注释

10

2.2 pF f = 1 MHz

4.0 pF

50.5

150

20

元件验收通知

CSA

基本绝缘符合

600 V rms(848 V

文件

205078

器件都经过1秒钟绝缘测试电压

CSA 60950-1-03和IEC 60950-1

峰值)最大工作电压

12

#5A

批准

DIN V VDE V 0884-10 (VDE V 0884-10

Ω

°

C/W

°

C T

°

C

器件都经过1秒钟绝缘测试电压

峰值的验证测试(局部放电检测限值为

≥ 1050 V

热电偶位于封装底部中心,利用细走线的4层

电路板进行测试

上升

J

2006-12

标准,

加强绝缘,

文件

≥ 3000 V rms

3

2

认证

峰值

560 V

2471900-4880-0001

的验证测试(漏电流检测限值为

)。器件标识中的星号

5 pC

10 μA

):

)。

(*)

表

隔离和安全相关特性

表

7

参数

额定电介质绝缘电压

最小外部气隙(间隙)

最小外部爬电距离

最小内部间隙

漏电阴抗(相对漏电指数)

隔离组

2500 V rms

L

L

符号

(

H) >5.1 mm

μ

(

H) >5.1 mm

μ

CTI >400 V DIN IEC 112/VDE 0303第1

值

(最小值)

0.017

II

单位

mm

测试条件/注释

持续1分钟

测量输入端至输出端,空气最短距离

测量输入端至输出端,沿壳体最短距离

隔离距离

材料组(

部分

DIN VDE 0110,1/89,表1)

Rev. 0 | Page 11 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

0

0.25

0.50

0.75

1.00

1.25

1.50

050100 150 200

AMBIENT TEMPERATURE (° C)

SAFE OPERATING V

CC

CURRENT (mA)

09369-002

DIN V VDE V 0884-10 (VDE V 0884-10)

隔离特性

这些隔离器适合安全限制数据范围内的加强电气隔离。通过保护电路保持安全数据。封装上的星号

VDE V 0884-10

表

8

描述

DIN VDE 0110

额定电源电压

额定电源电压

额定电源电压

环境分类

污染度(

最大工作绝缘电压

输入至输出测试电压,方法

输入至输出测试电压,方法

跟随环境测试,子类

跟随输入和/或安全测试,子类2和子类

最高允许过压

安全限值

壳温

第1侧电流

在

的绝缘电阻

T

S

认证。

装置分类

≤ 150 V rms

≤ 300 V rms

≤ 400 V rms

DIN VDE 0110

,表1)

B1

A

1

测试条件/注释

符号

V

IORM

V

局部放电

V

3

V

瞬变过压,

IORM

IORM

IORM

1.875 = V

×

1.6 = V

×

1.2 = V

×

PR

< 5 pC

,

PR

,

PR

tTR= 10秒

,

t

t

出现故障时允许的最大值(见图3)

VIO= 500 V R

100%

= 60

m

= 60

m

生产测试,

秒,局部放电

秒,局部放电

秒,

t

= 1

m

V

PR

V

PR

< 5 pC 896 V

< 5 pC 672 V

V

TR

T

S

I

S1

S

标志表示通过

(*)

特性

I至IV

I至III

I至II

40/105/21

2

560 V

1050 V

4000 V

150

1.25 A

9

>10

DIN V

单位

峰值

峰值

峰值

峰值

峰值

°

C

Ω

建议工作条件

表

9

参数

工作温度

电源电压

最低负载

1

所有电压均参照各自的地。

1

当

当

当

V

ISO

V

ISO

V

ISO

= 3.3 V

= 5.0 V

= 5.0 V

时的

时的

时的

V

CC

V

CC

V

CC

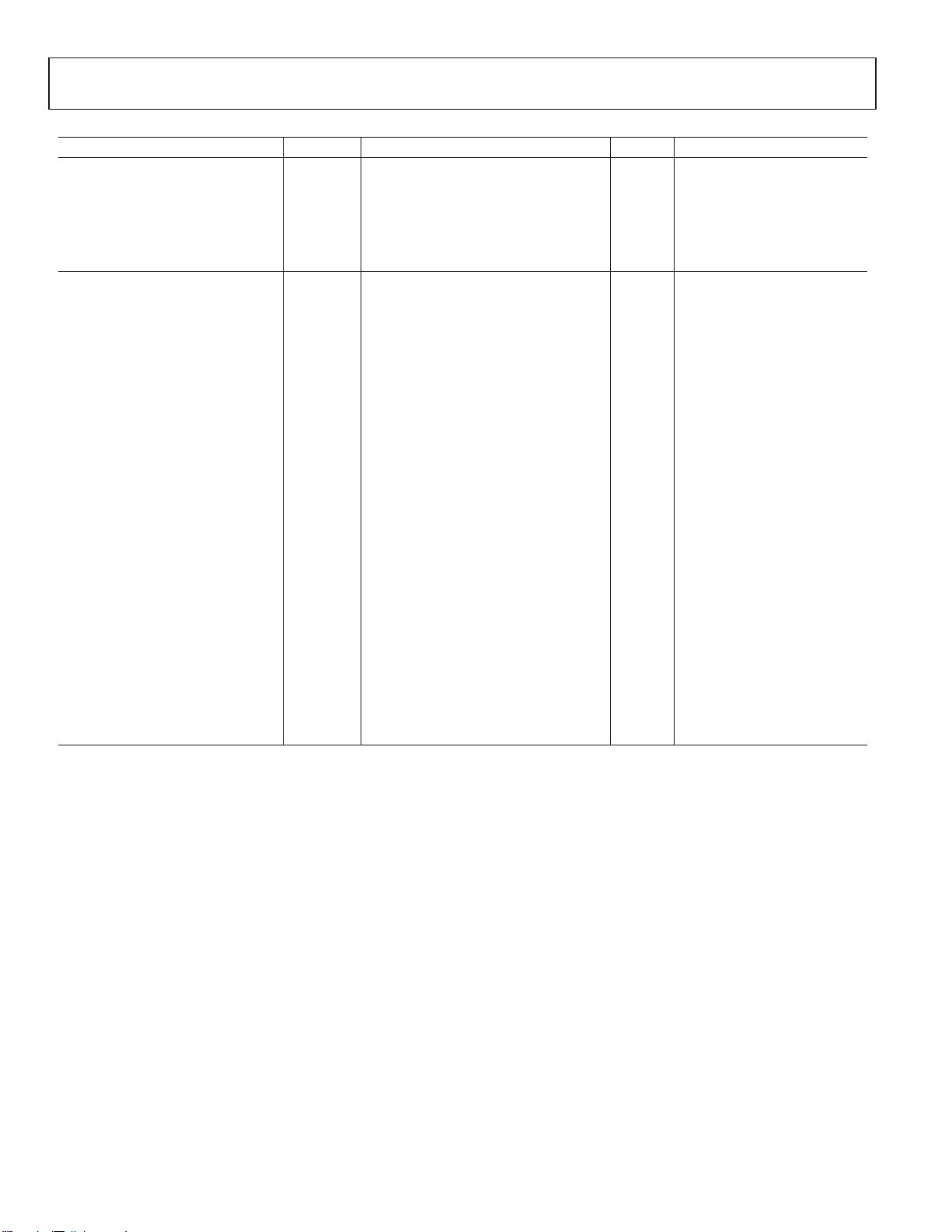

图

热减额曲线,依据

3.

DIN EN 60747-5-2

符号

T

A

获得的安全限值与壳温的关系

最小值

40

−

最大值

+105

单位

°

C

Vcc 3.0 3.6 V

Vcc 3.0 3.6 V

Vcc 4.5 5.5 V

I

ISO (MIN)

Rev. 0 | Page 12 of 32

10 mA

绝对最大额定值

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

除非另有说明,环境温度

表

10

参数

存储温度范围(

工作环境温度范围(

电源电压

V

V

DD1

, X1, X2

REG

, V

DDA

, V

输入电压(

输出电压(

VOA, VOB, VOC, V

)

T

ST

1

DD2

1

VIA, VIB, VIC, V

-55

)

T

-40°C至+105°C

A

1, 2

)

ID

)

OD

每个引脚的平均输出电流

共模瞬变

1

所有电压均参照其各自的地。

2

V

DDI

路板(

3

不同温度下的最大额定电流值参见图3。

4

指隔离栅上的共模瞬变。超过绝对最大额定值的共模瞬变可能导致闩锁

或永久损坏。

4

和

分别指给定通道的输入端和输出端 的电源电压。见“印刷电

V

DDO

)布局”部分的说明。

PCB

。

= 25°C

额定值

°

C至+150°C

-0.5 V至+7.0 V

-0.5 V至+20.0 V

-0.5 V至V

1, 2

-0.5 V至V

3

-10 mA至+10 mA

-100 kV/μs至+100 kV/μs

+ 0.5 V

DDI

+ 0.5 V

DDO

注意,超出上述绝对最大额定值可能会导致器件永久性损

坏。这只是额定最值,不表示在这些条件下或者在任何其

它超出本技术规范操作章节中所示规格的条件下,器件能

够正常工作。长期在绝对最大额定值条件下工作会影响器

件的可靠性。

1

适用认证

表

支持最短50年寿命的最大连续工作电压

11.

参数

交流电压,双极性波形

最大值 单位

565 V

峰值 所有认证工

作电压

交流电压,单极性波形

基本绝缘

848 V

峰值

IEC 60950-1

工作电压

直流电压

基本绝缘

848

V

峰值

IEC 60950-1

工作电压

1

指隔离栅上的连续电压幅度。详情见隔离寿命部分。

警告

ESD

(静电放电)敏感器件。

ESD

带电器件和电路板可能会在没有察觉的情况

下放电。尽管本产品具有专利或专有保护电

路,但在遇到高能量

因此,应当采取适当的

时,器件可能会损坏。

ESD

防范措施,以避

ESD

免器件性能下降或功能丧失。

Rev. 0 | Page 13 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

1

*GND

1

2

V

DD1

3

X2

4

V

REG

20

GND2*

19

V

DD2

18

FB

17

V

IA

5

V

IB

6

V

IC

7

V

OA

16

V

OB

15

V

OC

14

V

ID

8

V

OD

13

V

DDA

9

OC

12

*GND

1

10

GND2*

11

ADuM3470

TOP VIEW

(Not to Scale)

09369-00

RECOMMENDED. PIN 11 AND PIN 19 ARE

INTERNALLY CONNECTED, AND CONNECTING

BOTH TO GND

2

IS RECOMMENDED.

4

*PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED,

AND CONNECTING BOTH TO GND

1

IS

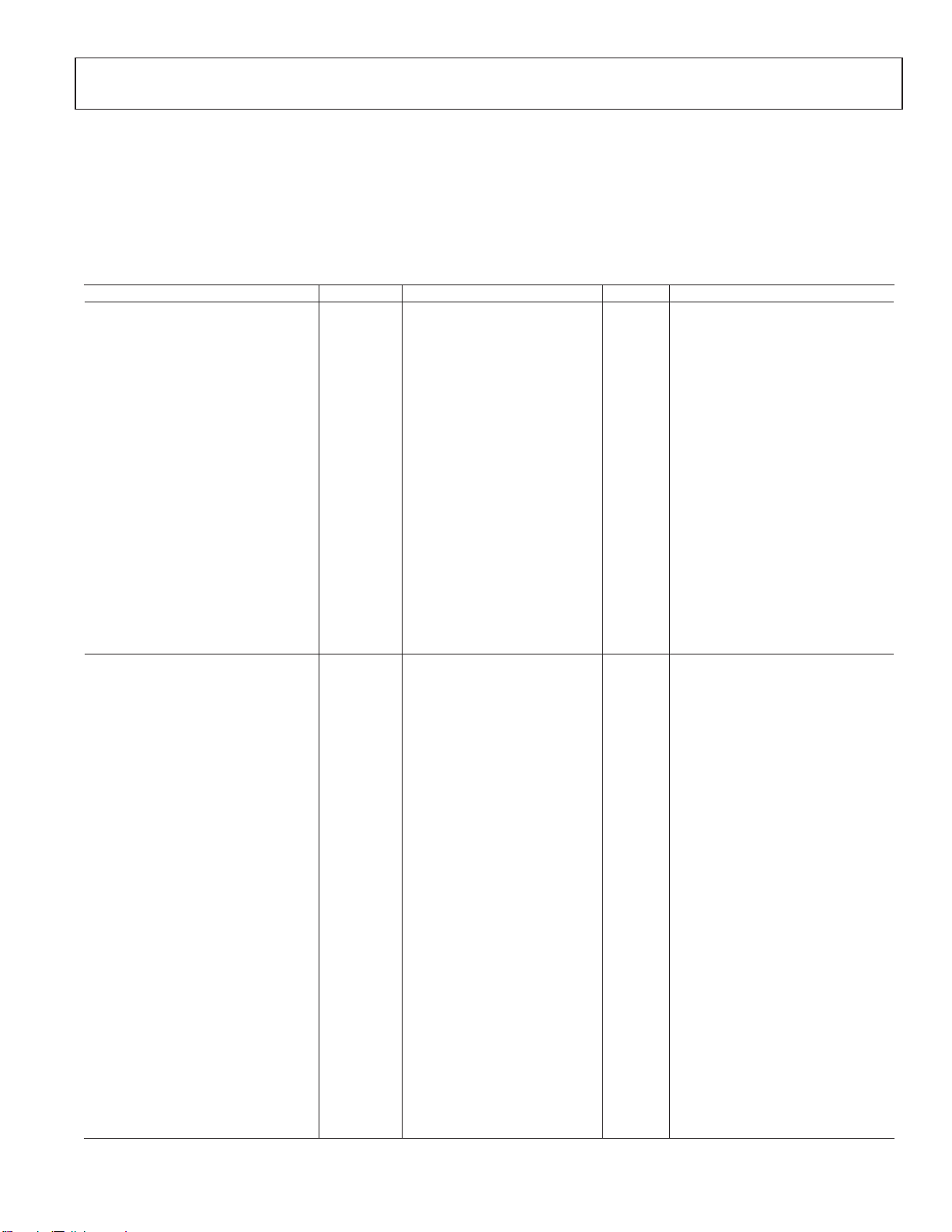

引脚配置和功能描述

表

12. ADuM3470

引脚功能描述

引脚编号 引脚名称 描述

1 X1

2, 10 GND1

3 V

DD1

4 X2

5 VIA

6 V

7 V

IB

IC

8 VID

9 V

11, 19 GND

DDA

2

12 OC

13 VOD

14 V

15 V

16 V

OC

OB

OA

17 FB

18 V

20 V

DD2

REG

图

4. ADuM3470

引脚配置

变压器驱动器输出1。

地1。隔离器原边参考地。

变压器驱动器电源电压为

变压器驱动器输出2。

逻辑输入A。

逻辑输入B。

逻辑输入C。

逻辑输入D。

原边电源电压为

隔离器第2侧的参考地。

振荡器控制引脚。当

引脚与

OC

GND

通过电阻值编程控制。

逻辑输出D。

逻辑输出C。

逻辑输出B。

逻辑输出A。

副边输出电压

计算公式为

V

V

ISO

内部电源电压引脚,可为副边控制器和第2侧数据通道供电。当向

部稳压器将

一个

0.1 μF

V

DD2

旁路电容。

3.0 V至5.5 V

。连接至

V

DDA

引脚。在

和

V

DD1

3.0 V至5.5 V

。连接至

V

DD1

引脚。在

和

V

DDA

GND

间连接一个

1

逻辑高电平

OC =

引脚之间连接一个电阻,且副边控制器的工作频率需保持在

2

时,副边控制器在开环模式下运行。为调节输出电压,需在

= V

DD2

的反馈输入。在

ISO

= V

(R1 + R2)/R2

×

FB

引脚的电压稳定在

与FB引脚之间连接一个电阻分压器,可使

V

ISO

。即使在开环模式下也需要用到电阻分压器,以便于实现软启动。

V

5.0 V

。否则,

V

DD2

应处在

REG

3.0 V至5.5 V

内部电源稳压器的输入引脚,可为副边控制器和第2侧数据通道供电。

以便将

输出电压稳定在

V

DD2

5.0 V。

GND

间连接一个

1

旁路电容。

0.1 μF

200 kHz至1 MHz

V

= 1.25 V

FB

旁路电容。

10 μF

之间,可

内部基准电平,

引脚施加足够大的外部电压后,内

之间。在

的值应处于

V

REG

与

V

DD2

5.5 V至15 V

GND

之间连接

2

之间,

Rev. 0 | Page 14 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

1

*GND

1

2

V

DD1

3

X2

4

V

REG

20

GND2*

19

V

DD2

18

FB

17

V

IA

5

V

IB

6

V

IC

7

V

OA

16

V

OB

15

V

OC

14

V

OD

8

V

ID

13

V

DDA

9

OC

12

*GND

1

10

GND2*

11

ADuM3471

TOP VIEW

(Not to Scale)

09369-005

*PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED,

AND CONNECTING BOTH TO GND

1

IS

RECOMMENDED. PIN 11 AND PIN 19 ARE

INTERNALLY CONNECTED, AND CONNECTING

BOTH TO GND

2

IS RECOMMENDED.

表

13. ADuM3471

引脚功能描述

引脚编号 引脚名称 描述

1 X1

2, 10 GND1

3 V

DD1

4 X2

5 VIA

6 V

7 V

IB

IC

8 VOD

9 V

DDA

11, 19 GND

12 OC

变压器驱动器输出1。

地1。隔离器原边参考地。

变压器驱动器电源电压为

变压器驱动器输出2。

逻辑输入A。

逻辑输入B。

逻辑输入C。

逻辑输出D。

原边电源电压为

隔离器第2侧的参考地。

2

振荡器控制引脚。当

OC

过电阻值编程控制。

13 VID

14 V

15 V

16 V

17 FB

OC

OB

OA

逻辑输入D。

逻辑输出C。

逻辑输出B。

逻辑输出A。

副边输出电压

计算公式为

18 V

DD2

内部电源电压引脚,可为副边控制器和第2侧数据通道供电。当向

部稳压器将

一个

20 V

REG

内部电源稳压器的输入引脚,可为副边控制器和第2侧数据通道供电。

以便将

引脚与

0.1 μF

V

3.0 V至5.5 V

引脚之间连接一个电阻,且副边控制器的工作频率需保持在

GND

2

的反馈输入。在

V

ISO

V

= V

×

ISO

FB

引脚的电压稳定在

V

DD2

旁路电容。

输出电压稳定在

DD2

图

3.0 V至5.5 V

。连接至

逻辑高电平

OC =

(R1 + R2)/R2

5.0 V。

5. ADuM3471

V

ISO

引脚配置

。连接至

引脚。在

V

DD1

= V

DD2

V

DDA

引脚。在

和

V

DDA

V

GND

DD1

和

GND

间连接一个

1

间连接一个

1

0.1 μF

10 μF

旁路电容。

时,副边控制器在开环模式下运行。为调节输出电压,需在

200 kHz至1 MHz

与FB引脚之间连接一个电阻分压器,可使

VFB = 1.25 V

旁路电容。

之间,可通

内部基准电平,

。即使在开环模式下也需要用到电阻分压器,以便于实现软启动。

引脚施加足够大的外部电压后,内

V

5.0 V

。否则,

V

DD2

应处在

3.0 V至5.5 V

REG

V

之间。在

的值应处于

REG

与

V

DD2

5.5 V至15 V

GND

之间连接

2

之间,

Rev. 0 | Page 15 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

1

*GND

1

2

V

DD1

3

X2

4

V

REG

20

GND2*

19

V

DD2

18

FB

17

V

IA

5

V

IB

6

V

OC

7

V

OA

16

V

OB

15

V

IC

14

V

OD

8

V

ID

13

V

DDA

9

OC

12

*GND

1

10

GND2*

11

ADuM3472

TOP VIEW

(Not to Scale)

09369-006

*PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED,

AND CONNECTING BOTH TO GND

1

IS

RECOMMENDED. PIN 11 AND PIN 19 ARE

INTERNALLY CONNECTED, AND CONNECTING

BOTH TO GND

2

IS RECOMMENDED.

表

14. ADuM3472

引脚功能描述

引脚编号 引脚名称 描述

1 X1

2, 10 GND1

3 V

DD1

4 X2

5 VIA

6 V

7 V

IB

OC

8 VOD

9 V

11, 19 GND

DDA

2

12 OC

13 VID

14 V

15 V

16 V

IC

OB

OA

17 FB

18 V

20 V

DD2

REG

图

6. ADuM3472

引脚配置

变压器驱动器输出1。

地1。隔离器原边参考地。

变压器驱动器电源电压为

变压器驱动器输出2。

逻辑输入A。

逻辑输入B。

逻辑输出C。

逻辑输出D。

原边电源电压为

隔离器第2侧的参考地。

振荡器控制引脚。当

引脚与

OC

GND

通过电阻值编程控制。

逻辑输入D。

逻辑输入C。

逻辑输出B。

逻辑输出A。

副边输出电压

计算公式为

V

V

ISO

3.0 V至5.5 V

。连接至

V

DDA

引脚。在

和

V

DD1

3.0 V至5.5 V

。连接至

V

DD1

引脚。在

和

V

DDA

GND

间连接一个

1

逻辑高电平

OC =

引脚之间连接一个电阻,且副边控制器的工作频率需保持在

2

时,副边控制器在开环模式下运行。为调节输出电压,需在

= V

DD2

的反馈输入。在

ISO

= V

(R1 + R2)/R2

×

FB

与FB引脚之间连接一个电阻分压器,可使

V

ISO

。即使在开环模式下也需要用到电阻分压器,以便于实现软启动。

内部电源电压引脚,可为副边控制器和第2侧数据通道供电。当向

内部稳压器将

连接一个

0.1 μF

引脚的电压稳定在

V

DD2

旁路电容。

5.0 V

。否则,

V

DD2

应处在

3.0 V至5.5 V

内部电源稳压器的输入引脚,可为副边控制器和第2侧数据通道供电。

以便将

输出电压稳定在

V

DD2

5.0 V。

GND

间连接一个

1

0.1 μF

旁路电容。

10 μF

旁路电容。

200 kHz至1 MHz

VFB = 1.25 V

引脚施加足够大的外部电压后,

V

REG

之间。在

的值应处于

V

REG

内部基准电平,

与

V

GND

DD2

5.5 V至15 V

之间,可

之间

2

之间,

Rev. 0 | Page 16 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

1

*GND

1

2

V

DD1

3

X2

4

V

REG

20

GND2*

19

V

DD2

18

FB

17

V

IA

5

V

OB

6

V

OC

7

V

OA

16

V

IB

15

V

IC

14

V

OD

8

V

ID

13

V

DDA

9

OC

12

*GND

1

10

GND2*

11

ADuM3473

TOP VIEW

(Not to Scale)

09369-007

*PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED,

AND CONNECTING BOTH TO GND

1

IS

RECOMMENDED. PIN 11 AND PIN 19 ARE

INTERNALLY CONNECTED, AND CONNECTING

BOTH TO GND

2

IS RECOMMENDED.

表

15. ADuM3473

引脚功能描述

引脚编号 引脚名称 描述

1 X1

2, 10 GND1

3 V

DD1

4 X2

5 VIA

6 V

7 V

OB

OC

8 VOD

9 V

DDA

11, 19 GND

12 OC

2

变压器驱动器输出1。

地1。隔离器原边参考地。

变压器驱动器电源电压为

变压器驱动器输出2。

逻辑输入A。

逻辑输出B。

逻辑输出C。

逻辑输出D。

原边电源电压为

隔离器第2侧的参考地。

振荡器控制引脚。当

OC

通过电阻值编程控制。

13 VID

14 V

15 V

16 V

17 FB

IC

IB

OA

逻辑输入D。

逻辑输入C。

逻辑输入B。

逻辑输出A。

副边输出电压

平,计算公式为

18 V

DD2

内部电源电压引脚,可为副边控制器和第2侧数据通道供电。当向

内部稳压器将

连接一个

20 V

REG

内部电源稳压器的输入引脚,可为副边控制器和第2侧数据通道供电。

以便将

引脚与

V

3.0 V至5.5 V

引脚之间连接一个电阻,且副边控制器的工作频率需保持在

GND

2

的反馈输入。在

V

ISO

V

= V

ISO

引脚的电压稳定在

V

DD2

旁路电容。

0.1 μF

输出电压稳定在

DD2

3.0 V至5.5 V

逻辑高电平

OC =

(R1 + R2)/R2

×

FB

图

7. ADuM3473

。连接至

V

5.0 V。

引脚配置

。连接至

引脚。在

V

DD1

时,副边控制器在开环模式下运行。为调节输出电压,需在

= V

DD2

与FB引脚之间连接一个电阻分压器,可使

ISO

V

DDA

引脚。在

和

V

DDA

V

GND

DD1

和

GND

间连接一个

1

间连接一个

1

旁路电容。

0.1 μF

200 kHz至1 MHz

VFB = 1.25 V

10 μF

旁路电容。

之间,可

内部基准电

。即使在开环模式下也需要用到电阻分压器,以便于实现软启动。

引脚施加足够大的外部电压后,

V

5.0 V

。否则,

V

DD2

应处在

REG

3.0 V至5.5 V

的值应处于

V

REG

之间。在

与

V

GND

DD2

5.5 V至15 V

2

之间,

之间

Rev. 0 | Page 17 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

1

*GND

1

2

V

DD1

3

X2

4

V

REG

20

GND2*

19

V

DD2

18

FB

17

V

OA

5

V

OB

6

V

OC

7

V

IA

16

V

IB

15

V

IC

14

V

OD

8

V

ID

13

V

DDA

9

OC

12

*GND

1

10

GND2*

11

ADuM3474

TOP VIEW

(Not to Scale)

09369-008

*PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED,

AND CONNECTING BOTH TO GND

1

IS

RECOMMENDED. PIN 11 AND PIN 19 ARE

INTERNALLY CONNECTED, AND CONNECTING

BOTH TO GND

2

IS RECOMMENDED.

表

16. ADuM3474

引脚功能描述

引脚编号 引脚名称 描述

1 X1

2, 10 GND1

3 V

DD1

4 X2

5 VOA

6 V

7 V

OB

OC

8 VOD

9 V

11, 19 GND

DDA

2

12 OC

13 VID

14 V

15 V

16 V

IC

IB

IA

17 FB

18 V

20 V

DD2

REG

图

8. ADuM3474

引脚配置

变压器驱动器输出1。

地1。隔离器原边参考地。

变压器驱动器电源电压为

变压器驱动器输出2。

逻辑输出A。

逻辑输出B。

逻辑输出C。

逻辑输出D。

原边电源电压为

隔离器第2侧的参考地。

振荡器控制引脚。当

引脚与

OC

GND

通过电阻值编程控制。

逻辑输入D。

逻辑输入C。

逻辑输入B。

逻辑输入A。

副边输出电压

计算公式为

V

V

ISO

3.0 V至5.5 V

。连接至

V

DDA

引脚。在

V

DD1

3.0 V至5.5 V

。连接至

V

DD1

引脚。在

和

V

DDA

GND

间连接一个

1

逻辑高电平

OC =

引脚之间连接一个电阻,且副边控制器的工作频率需保持在

2

时,副边控制器在开环模式下运行。为调节输出电压,需在

= V

DD2

的反馈输入。在

ISO

= V

(R1 + R2)/R2

×

FB

与FB引脚之间连接一个电阻分压器,可使

V

ISO

。即使在开环模式下也需要用到电阻分压器,以便于实现软启动。

内部电源电压引脚,可为副边控制器和第2侧数据通道供电。当向

内部稳压器将

连接一个

0.1 μF

引脚的电压稳定在

V

DD2

旁路电容。

5.0 V

。否则,

V

DD2

应处在

3.0 V至5.5 V

内部稳压器的输入引脚,可为副边控制器和第2侧数据通道供电。

便将

输出电压稳定在

V

DD2

5.0 V。

和

GND

间连接一个

1

0.1 μF

10 μF

旁路电容。

200 kHz至1 MHz

VFB = 1.25 V

引脚施加足够大的外部电压后,

V

REG

之间。在

的值应处于

V

REG

内部基准电平,

V

DD2

5.5 V至15 V

旁路电容。

之间,可

与

GND

2

之间,以

之间

表

真值表(正逻辑)

17.

1

输入

V

高

低

1

V

Ix

V

Ix

和

指给定通道(A、B、C或D)的输入和输出信号。

V

Ox

CC

有电

有电

状态

状态

VD

有电

有电

D2

V

高

低

1

输出

Ox

Rev. 0 | Page 18 of 32

注释

正常工作,数据为高电平

正常工作,数据为低电平

典型工作特性

1500

1400

1300

1200

1100

1000

900

800

700

600

500

400

300

200

100

0

050100 150200 250300 350400 450500

f

SW

(kHz)

ROC (Ω)

09369-009

80

70

60

50

40

30

20

10

0

005100205200305300405400510050

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-010

1MHz

700kHz

500kHz

200kHz

80

70

60

50

40

30

20

10

0

005100205200305300405400510050

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-011

1MHz

700kHz

500kHz

200kHz

80

70

60

50

40

30

20

10

0

5005100205200305300405410050

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-012

00

–40°C

25°C

105°C

80

70

60

50

40

30

20

10

0

005100205200305300405400510050

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-013

5V IN TO 5V OUT

5V IN TO 3.3V OUT

3.3V IN TO 3.3V OUT

80

70

60

50

40

30

20

10

0

014090 100110 120 1308003040506072010

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-014

1MHz

700kHz

500kHz

200kHz

图

开关频率(

9.

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

图

开关频率

)与

f

SW

电阻的关系

R

OC

12.

(

5 V

输入至

fSW=500 kHz

时,在整个温度范围内的效率

5 V

输出,

Coilcraft

变压器)

图

图

输入至

10. 5 V

输入至

11. 5 V

输出时,不同开关频率下的典型效率,

5 V

使用

Coilcraft

输出时,不同开关频率下的典型效率,

5 V

使用

Halo

变压器

变压器

图

13.

(

开关频率

图

14.

输入至

5 V

fSW=500 kHz

(

Coilcraft

时,单电源供电效率

变压器)

不同开关频率下的效率

输出,

15 V

Coilcraft

变压器)

Rev. 0 | Page 19 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

80

70

60

50

40

30

20

10

0

014090 100110 1201308003040506072010

EFFICIENCY (%)

LOAD CURRENT(mA)

09369-026

1MHz

700kHz

500kHz

200kHz

80

70

60

50

40

30

20

10

0

014090 100110 1201300405060708300102

EFFICIENCY (%)

LOAD CURRENT (mA)

09369-027

–40°C

25°C

105°C

80

70

60

50

40

30

20

10

0

014090 100110 1201308004050607300102

EFFICIENCY (%)

LOAD CURRENT(mA)

09369-028

5V IN TO 15V OUT

5V IN TO 12V OUT

15

10

5

0

202015105

DATA RATE (Mbps)

09369-029

5

VCC = 5V, V

ISO

= 5V

V

CC

= 5V, V

ISO

= 3.3V

V

CC

= 3.3V, V

ISO

= 3.3V

I

CH

(mA)

15

10

5

0

202015105

DATA RATE (Mbps)

09369-030

5

I

CH

(mA)

VCC = 5V, V

ISO

= 5V

V

CC

= 5V, V

ISO

= 3.3V

V

CC

= 3.3V, V

ISO

= 3.3V

5

4

3

2

1

0

202015105

I

ISO

(D) (mA)

DATA RATE (Mbps)

09369-031

5

VCC = 5V, V

ISO

= 5V

V

CC

= 5V, V

ISO

= 3.3V

V

CC

= 3.3V, V

ISO

= 3.3V

图

(

5 V

不同开关频率下的效率

15.

输入至

15 V

输出,

Halo

变压器)

图

每个正向数据通道的典型单电源供电

18.

(输出负载为

15 pF

)

电源电流

I

CH

图

图

开关频率

16.

图

17.

f

=500 kHz

5 V

SW

输入至

(

开关频率

(

时,在整个温度范围内的效率

输出,

15 V

fSW=500 kHz

Coilcraft

Coilcraft

时,双电源供电效率

变压器)

变压器)

Rev. 0 | Page 20 of 32

每个反向数据通道的典型单电源供电

19.

(输出负载为

图

每个输出通道的典型单电源供电

20.

(输出负载为

15 pF

15 pF

)

)

I

CH

动态电源电流

I

ISO(D)

电源电流

5

4

3

2

1

0

2052015105

I

ISO

(D) (mA)

DATA RATE (Mbps)

09369-032

VCC = 5V, V

ISO

= 5V

V

CC

= 5V, V

ISO

= 3.3V

V

CC

= 3.3V, V

ISO

= 3.3V

图

30

25

20

15

10

5

0

2052015105

I

CH

(mA)

DATA RATE (Mbps)

09369-033

VCC = 5V, V

ISO

= 15V

V

CC

= 5V, V

ISO

= 12V

30

25

20

15

10

5

0

2052015105

I

CH

(mA)

DATA RATE (Mbps)

09369-034

VCC = 5V, V

ISO

= 15V

V

CC

= 5V, V

ISO

= 12V

5

4

3

2

1

0

202015105

I

ISO (D)

(mA)

DATA RATE (Mbps)

09369-035

5

VCC = 5V, V

ISO

= 15V

V

CC

= 5V, V

ISO

= 12V

5

4

3

2

1

0

202015105

I

ISO (D)

(mA)

DATA RATE (Mbps)

09369-036

5

VCC = 5V, V

ISO

= 15V

V

CC

= 5V, V

ISO

= 12V

6

4

5

3

2

1

0

30202515105

V

ISO

(V)

TIME (ms)

09369-037

0

V

ISO

AT 10mA

V

ISO

AT 50mA

V

ISO

AT 400mA

每个输入通道的典型单电源供电

21.

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

动态电源电流

I

ISO(D)

图

每个输出通道的典型双电源供电

24.

(输出负载为

15 pF

)

I

ISO(D)

动态电源电流

图

每个正向数据通道的典型双电源供电

22.

图

每个反向数据通道的典型双电源供电

23.

(输出负载为

(输出负载为

15 pF

15 pF

)

)

电源电流

I

CH

电源电流

I

CH

Rev. 0 | Page 21 of 32

图

每个输入通道的典型双电源供电

25.

图

26. 典型V

(带有

ISO

10 mA、50 mA和400 mA

启动

5 V

输入至

动态电源电流

I

ISO(D)

输出

5 V

输出负载)

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

5

4

3

2

1

0

30020 2515105

V

ISO

(V)

TIME (ms)

09369-038

V

ISO

AT 10mA

V

ISO

AT 50mA

V

ISO

AT 400mA

5

4

3

2

1

0

30202515105

V

ISO

(V)

TIME (ms)

09369-039

0

V

ISO

AT 10mA

V

ISO

AT 50mA

V

ISO

AT 250mA

18

16

14

12

10

8

6

4

2

0

30020 2515105

V

ISO

(V)

TIME (ms)

09369-040

V

ISO

AT 10mA

V

ISO

AT 20mA

V

ISO

AT 100mA

6.0

5.5

5.0

4.5

4.5

1.0

0.5

6.0

5.5

5.0

0

–2 02468101214

V

ISO

(V)I

LOAD

(A)

TIME (ms)

09369-041

90% LOAD 10% LOAD

C

OUT

= 47µF, L1 = 100µH

C

OUT

= 47µF, L1 = 47µH

4.0

3.5

3.0

1.0

0.5

4.0

3.5

3.0

0

–2 02468101214

V

ISO

(V)I

LOAD

(A)

TIME (ms)

09369-042

C

OUT

= 47µF, L1 = 47µH

90% LOAD 10% LOAD

C

OUT

= 47µF, L1 = 100µH

4.0

3.5

3.0

1.0

0.5

4.0

3.5

3.0

0

–2 02468101214

V

ISO

(V)I

LOAD

(A)

TIME (ms)

09369-044

C

OUT

= 47µF, L1 = 47µH

90% LOAD 10% LOAD

C

OUT

= 47µF, L1 = 100µH

图

27. 典型V

(带有

图

28. 典型V

(带有

ISO

10 mA、50 mA和400 mA

ISO

10 mA、50 mA和250mA

启动

启动

5 V

3.3 V

输入至

输入至

3.3 V输出

输出负载)

3.3 V输出

输出负载)

图

30. 典型V

(开关频率

图

31. 典型V

(开关频率

f

=500 kHz

SW

f

=500 kHz

SW

负载瞬态响应

ISO

,负载为

负载瞬态响应

ISO

,负载为

输入至5V输出

5 V

400 mA的10%至90%

输入至

5 V

3.3V输出

400 mA的10%至90%

)

)

图

29. 典型V

(带有

10 mA、20 mA和100mA

ISO

启动

5 V

输入至

输出

15V

输出负载)

图

32. 典型V

(开关频率

f

=500 kHz

SW

ISO

负载瞬态响应

,负载为

3.3 V

输入至

3.3V

输出

250 mA的10%至90%

)

Rev. 0 | Page 22 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

18

16

14

12

18

16

14

12

200

100

0

–2 02468101214

V

ISO

(V)I

LOAD

(A)

TIME (ms)

09369-043

C

OUT

= 47µF, L1 = 47µH, L2 = 47µH

C

OUT

= 47µF, L1 = 100µH, L2 = 100µH

10% LOAD 90% LOAD

20

10

0

–2

V

ISO

(V)X1 (V)

TIME (µs)

09369-045

4.98

5.00

5.02

5.04

–1 012

X1 ON

X2 ON

20

10

0

–2

V

ISO

(V)X1 (V)

TIME (µs)

09369-046

3.28

3.30

3.32

3.34

–1 012

X2 ON

X1 ON

20

10

0

–2

V

ISO

(V)X1 (V)

TIME (µs)

09369-047

3.28

3.30

3.32

3.34

–1 012

X2 ON

X1 ON

20

10

0

–2

V

ISO

(V)X1 (V)

TIME (µs)

09369-048

14.6

14.8

15.0

15.2

15.4

–1 012

X2 ON

X1 ON

图

33. 典型V

(开关频率

图

(开关频率

ISO

f

=500 kHz

SW

34. 典型V

负载瞬态响应5V输入至

,负载为

输出纹波5V输入至5V输出

ISO

f

=500 kHz

SW

100 mA的10%至90%

,负载为

400 mA

15V输出

)

)

图

36. 典型V

(开关频率

图

37. 典型V

(开关频率

输出纹波

ISO

f

SW

输出纹波5V输入至

ISO

f

SW

=500 kHz

=500 kHz

3.3V

,负载为

,负载为

输入至

3.3V输出

250 mA

15V输出

100 mA

)

)

图

35. 典型V

(开关频率

输出纹波5V输入至

ISO

f

=500 kHz

SW

,负载为

3.3V输出

400 mA

)

Rev. 0 | Page 23 of 32

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

术语

I

CC (Q)

是在

I

CC(Q)

处无外部负载,并且

引脚汲取的最小工作电流,测量条件为

V

CC

引脚以低于

I/O

2 Mbps

V

ISO

的速率工作,

从而无需额外动态电源电流。

I

CC (D)

I

CC(D)

是同时以

25 Mbps

的最大数据速率驱动所有通道时的

典型输入电源电流,满容性负载表示最 大动态负载条件。

区别对待输出端的阻性负载与动态负载。

I

CC (MAX)

是满动态

I

cc(MAX)

传播延迟

t

PHL

传播延迟是从

t

PHL

降沿的

50%

水平的时间。

负载条件下的输入电流。

V

ISO

信号下降沿的

V

Ix

50%

水平到

V

信号下

Ox

传播延迟

t

PLH

传播延迟是从

t

PLH

升沿的

传播延迟偏斜

指器件在建议工作条件范围内的相同工作温度、电源电

t

PSK

水平的时间。

50%

(t

压和输出负载下工作时测得的

信号上升沿的

V

Ix

)

PSK

t

PHL

50%

和/或

水平到

t

PLH

V

Ox

的最差情况偏差。

信号上

通道间匹配

通道间匹配指两个通道在相同负载下工作时的传播延迟之

差的绝对值。

最小脉冲宽度

最小脉冲宽度指保证额定脉冲宽度失真的最短脉冲宽度。

最大数据速率

最大数据速率指保证额定脉冲宽度失真的最快数据速率。

Rev. 0 | Page 24 of 32

应用信息

R2

1R2R

V = V

FB

ISO

+

×

09369-015

ADuM3470/

ADuM3471/

ADuM3472/

ADuM3473/

ADuM3474

1 X1

2 GND

1

3 V

DD1

4 X2

5 I/OA

6 I/OB

7 I/OC

8 I/OD

9 V

DDA

10 GND

1

20 V

REG

19 GND

2

18 V

DD2

17 FB

16 I/OA

15 I/OB

14 I/OC

13 I/OD

12 OC

11 GND

2

D1

T1

L1

C

OUT

D2

V

CC

V

CC

0.1µF

C

IN

0.1µF

+5V

R1

R2

R

OC

V

FB

V

ISO

= VFB × (R1+R2)/R2

FOR V

ISO

= 3.3V OR 5V CONNECT V

REG

, V

DD2

,AND V

ISO

.

V

ISO

=

+3.3V

TO +15V

47µF

47µH

100kΩ

09369-016

ADuM3470/

ADuM3471/

ADuM3472/

ADuM3473/

ADuM3474

1 X1

2 GND

1

3 V

DD1

4 X2

5 I/OA

6 I/OB

7 I/OC

8 I/OD

9 V

DDA

10 GND

1

20 V

REG

19 GND

2

18 V

DD2

17 FB

16 I/OA

15 I/OB

14 I/OC

13 I/OD

12 OC

11 GND

2

D1

T1

L1

L2

C

OUT1

C

OUT2

D2

D3

D4

V

CC

V

CC

0.1µF

C

IN

0.1µF

+5V

R1

R2

V

FB

R

OC

V

ISO

= VFB × (R1 + R2)/R2

FOR V

ISO

= 15V OR LESS, V

REG

CAN CONNECTTO V

ISO

.

V

ISO

=

+12V TO

+24V

UNREGULATED

+6V TO

+12V

100kΩ

47µH

47µH

47µF

47µF

09369-017

ADuM3470/

ADuM3471/

ADuM3472/

ADuM3473/

ADuM3474

1 X1

2 GND

1

3 VDD1

4 X2

5 I/OA

6 I/OB

7 I/OC

8 I/OD

9 V

DDA

10 GND

1

20 V

REG

19 GND

2

18 VDD2

17 FB

16 I/OA

15 I/OB

14 I/OC

13 I/OD

12 OC

11 GND

2

D1T1L1

L2

C

OUT1

C

OUT2

D2

D3

D4

V

CC

V

CC

0.1µF

C

IN

0.1µF

+5V

R1

R2

R

OC

V

FB

V

ISO

= VFB × (R1 + R2)R2

V

ISO

=

COARSELY

REGULATED

+5V TO 15V

UNREGULATED

–5V TO –15V

47µF47µH

47µH

47µF

100kΩ

工作原理

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

ADuM347x的DC-DC

(

PWM)

反馈的副边控制器结构。

转 换 器 采 用 带 有 隔 离 脉 宽 调 制

为一个振荡电路供电;

V

CC

该电路利用X1和X2引脚处的推挽式开关,可以将电流切

换至外部电源变压器的原边。传输至变压器副边的电源经

外部肖特基二 极 管(D1和D2)全波整流,经 电 感L1和

电容

副边

(V

生成的

通过标有

原边

滤波,可调整为隔离电源电压(

COUT

控制器通过输出端电阻分压器的反馈电压

)

ISO

控制信号可以调整输出电压,该

PWM

的专用

V

FB

转换 器 可改变开关X1、X2的占 空 比,以实现

PWM

i

Coupler

数据通道传输至 原边

3.3V至15V

对振荡电路的调制并控制副边的供电。该反馈可以实现更

高的功率和效率。

ADuM347x

锁

(UVLO)

利用

。此功能确保转换器不会因为高噪声输入电源或

电源输入引脚的迟滞特性实现欠压闭

V

CC

者上电斜升速率较慢而进入振荡状态。

为了获得最佳负 载调整率,建 议最小负载电 流为

负载较小可能会因为

脉冲较短或不稳定而导致芯片

PWM

产生过大噪声。在某些情况下,这种方式所产生的过大噪

声会导致稳压控制问题。

应用原理图

ADuM347x

有一个中心抽头副边和两个肖特基二极管,可为单个输出

提供全波整流,一般适用于

电压。而对于

参考图38中关于

一个倍压电路,可用于单电源供电,其输出电压超过

这是器件的稳压器输入引脚

(

输入电压)。在如图39所示的电路中,输出电压高达

V

REG

电路,用于举例说明经初步稳压的正向供电电源和非稳压

的负向供电电源。该电路的输出电压约为

15 V

±

离输出电压 (

100 k

其中 :

的三个主要 应用原理 图见图38至图40。图

3.3 V、5 V、12 V和15 V

= 3.3 V或V

V

ISO

V

引脚的电压仅为

ISO

、

和

V

REG

DD2

V

REG

。图40所显示的同样是倍压副边

12 V

时的单电源供电,请

= 5 V

连接的说明。图39是

V

ISO

(引脚20)可接受的最高

5 V

±

。在 如 图38、图39或图40所示 的 任 一 电 路 中,隔

都经分压器R1和R2(电阻值为

V

)

ISO

)分压。应用原理图采用如下计算公式 :

Ω

是内部反馈电压,其值约为

V

FB

1.25 V

。

PWM

、

±

)。

及

V

FB

信号

。

(VCC)

。

10 mA

38

电源

15 V

,

24 V

和

12 V

至

1 k

Ω

Rev. 0 | Page 25 of 32

图

单电源供电

38.

图

双电源供电

39.

图

正电源及非稳压的负电源

40.

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

×D×2

+

=

V

VV

N

N

CC(MIN)

D

ISO

P

S

2

2

× ×

+

=

DV

V

V

N

N

CC (MIN)

D

ISO

P

S

×D×2

+

=

V

VV

N

N

CC(MIN)

D

ISO

P

S

2×

=

W(MIN)S

C(MAX)C

f

V

TE(Mni)

变压器设计

变压器被设计用于如图38、图39和图40所示的电路中 ;

表18内列出各种电压器。

非稳定输出电压的隔离式

电压由

ADuM347x的PWM

ADuM347x

DC-DC

控制器进行调整,该控制器利

用从隔离数字通道接收的副边反馈电压

关的占空比。内部控制器的最大占空比为

的变压器设计与其它

转换器的设计不同。输出

来改变原边开

V

FB

。

40%

变压器匝数比

为确定变压器匝数比,并考虑原边开关、副边二极管和电

感的功率损失,应根据如下公式计算

ADuM347x

压器匝数比 :

其中 :

为原副边匝数比。

NS /N

P

为隔离输出电源电压。

V

ISO

为肖特基二极管压降(最大值

V

D

V

D

为最小输入电源电压。

CC(MIN)

为占空比,

D

= 0.30

0.5 V

代表典型占空比

)。

30%(40%

乘法系数2用于推挽开关周期。

在图38中,采用表18的

匝数比

N

S/NP

= 2

而对于一个类似的

),匝数比

3.0 V

比

NS/NP = 2

至

5 V、5 V至3.3 V和3.3 V至3.3 V

NS/N

可应用在三种不同的单电源供电应用中(

5 V至5 V

。

3.3 V至3.3 V

也等于2。因此,同样的变压器匝数

P

参考设计,

单电源供电设计(

)。

如图39所示,电路利用双绕组和二极管对形成一个倍压电

路 ;因此,公式中需将输出电压减半,即

V

的外部变

为最大值);

V

CC (MIN)

V

。

/2

ISO

= 4.5 V

CC (MIN)

5 V

,

=

如图40所示,电路利用双绕组和二极管对形成一个倍压电

路,但因为形成了正负输出电压,公式中使用

。

V

ISO

其中 :

为原副边匝数比。

N

为隔离输出电源电压 ;由于电路采用两对二极管形成

V

ISO

一个可产生正、负输出电压的倍压电路 ;因此,在这个公

式中使用

为肖特基二极管压降(最大值

V

D

V

CC (MIN)

。

V

ISO

)。

0.5 V

为最 小 输 入 电源电压, 乘 法系数2用于 推 挽 开 关

周期。

如图40所示的电路中,较高的占空比值

占空比

35%(40%

为最大值),以降低

±

D

15 V

代表典型

= 0.35

电源二极管处

的最大电压。

在图40中,采用表18的

匝数比

NS/NP = 5

。

+5 V

至

±

15 V

参考设计,

V

CC (MIN)

= 4.5 V,

变压器ET常数

变压器设计过程中需要考虑的另一个因素是ET常数。它能

够决定工作温度范围内变压器的最小

中,

ADuM347x

采用的ET值为

14 V × μs和18 V × μs

算公式如下 :

其中 :

V

f

为最大输入电源电压。

CC(MAX)

为启动过程中的最小原边开关频率(

SW (MIN)

法系数2用于推挽开关周期。

V × μs

常数。在表

300 kHz

);乘

18

;计

为原副边匝数比。

NS /N

P

由于电路使用两对二极管来形成倍压电路,因此,在上述

公式中使用

为肖特基二极管压降(最大值

V

D

V

D

为最小输入电源电压。

CC(MIN)

为占空比,

V

ISO

D

。

/2

代表典型占空比

= 0.30

0.5 V

)。

30%(40%

为最大值);

乘法系数2用于推挽开关周期。

在图39中,采用表18的

匝数比

NS/NP = 3

5 V至15 V

。

参考设计,

V

CC (MIN)

,

= 4.5 V

Rev. 0 | Page 26 of 32

变压器原边电感和电阻

ADuM347x

ADuM347x

至

100 μH

运转,需要将原边电感值保持在该范围 ;这样能够防止变

压器产生饱和电流。如果电感被指定为两个原边绕组的电

感之和(例如 :

组之和的¼,即

ADuM347x

边电阻尽可能低(小于

户可以测量、指定直流原边电阻,如表18所示。

的变压器的重要特性之一为原边电感。建议将

的变压器的每个原边绕组的电感保持在

之间。 为 保 证

400 μH

100 μH

ADuM347x

),那么,一个绕组的电感为两个绕

。

逐脉 冲 限 流电路正常

60 μH

的变压器的另一重要特性是原边电阻。如果原

),可降低损耗、提高效率。用

1

Ω

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

表

变压器参考设计

18.

匝 数 比,

产品型号

JA4631-BL Coilcraft 1CT:2CT 18 255 0.2 2500

JA4650-BL Coilcraft 1CT:3CT 18 255 0.2 2500

KA4976-AL Coilcraft 1CT:5CT 18 255 0.2 2500

TGSAD-260V6LF Halo Electronics 1CT:2CT 14 389 0.8 2500

TGSAD-290V6LF Halo Electronics 1CT:3CT 14 389 0.8 2500

TGSAD-292V6LF Halo Electronics 1CT:5CT 14 389 0.8 2500

TGAD-260NARL Halo Electronics 1CT:2CT 14 389 0.8 1500

TGAD-290NARL Halo Electronics 1CT:3CT 14 389 0.8 1500

TGAD-292NARL Halo Electronics 1CT:5CT 14 389 0.8 1500

制造厂商

PRI:SEC

常数

ET

(V × μs

最小值

原边总电感

)

(μH)

原边总电阻

(Ω)

隔离电压

(rms)

隔离类型 参考

基本型

基本型

基本型

补充型

补充型

补充型

功能型

功能型

功能型

图

图

图

图

图

图

图

图

图

38

39

40

38

39

40

38

39

40

变压器隔离电压

隔离电压和隔离类型取决于应用的需要。表18中的变压器

的补充隔离或基本隔离额定电压值为

离电压值为

中列出的生产厂商或其它生产厂商指定。

18

1500 V rms

。其它隔离电平和隔离电压可由表

2500 V rms

,功能隔

开关频率

ADuM347x

通过改变图38、图39或图40中的

现目标开关频率所需要的

与

ROC

最大负载值的

的开关频率调 节范围为

ROC

200 kHz至1 MHz

电阻进行调节。实

ROC

电阻的值可通过开关频率

电阻的关系曲线来确定,如图9所示。当负载值为

10%至90%

之间时,

ADuM347x

的输出滤波电感值和输出电容值可保证开关频率在

至

ADuM347x

调整,且电压取决于变压器匝数比

流和

连接至

开关频率为

之间系统稳定。

1 MHz

DC-DC

V

DD2

还有一个开环模式,该模式下输出电压不经过

,以及输出负载电

NS/N

P

转换器电路损耗等输出条件。OC引脚高电平

引脚时,则选择了该开环模式。在开环模式下,

318 kHz

。

,可

应用原理图

500 kHz

瞬态响应

当器件的负载为满负载的

10%至90%

出电压负载瞬态响应如图30至图33所示(分别对应于图

和图39的应用原理图)。图中所示瞬态响应较慢,但非

38

常稳定,且在某些应用中,可产生比预期更多的输出变化。

输出电路增加额外的电感可使输出电压变化随负载瞬态变

化降低并保持输出稳定,如图30至图33所示的第二

输出波形所示。

时,

ADuM347x

的输

V

ISO

元件选择

ADuM347x

数字隔离器集成

2W DC-DC

辑接口提供额外的接口电路。输入和输出供电引脚需要电

源旁路。注意 :在第1侧的引脚9与引脚10之间和在第

侧的 引 脚18与引 脚19之间, 需 要放置一个

2

陶瓷旁路电容,此电容应尽量靠近芯片焊盘。

ESR

ADuM347X

电源部分采用较高振荡器频率,通过外部电源

变压器有效地传输功率。此外,在正常工作模式下

的数据部分在电源引脚上引入开关瞬变。在多个工作频率

下都需要旁路电容。噪声抑制需要一个 低电感高频电容,

纹波抑制和适当的调整则需要一个大容值的电容。为抑制

噪声、降低纹波,建议使用

电容。推荐的电容值为

)。这些电容的

V

ISO

采用中等的

可将两个

22 μF

1206或1210

ESR

陶瓷电容并联。表19中列出的是推荐的元件。

X5R或X7R

(用于

10 μF

较低,且当电压不高于

规格电容。当输出电压高于

转换器,无需为逻

0.1 μF

电解质型大值陶瓷

)和

V

DD1

47 μF

10 V

的低

i

Couple

(用于

时,可

10 V

时,

Rev. 0 | Page 27 of 32

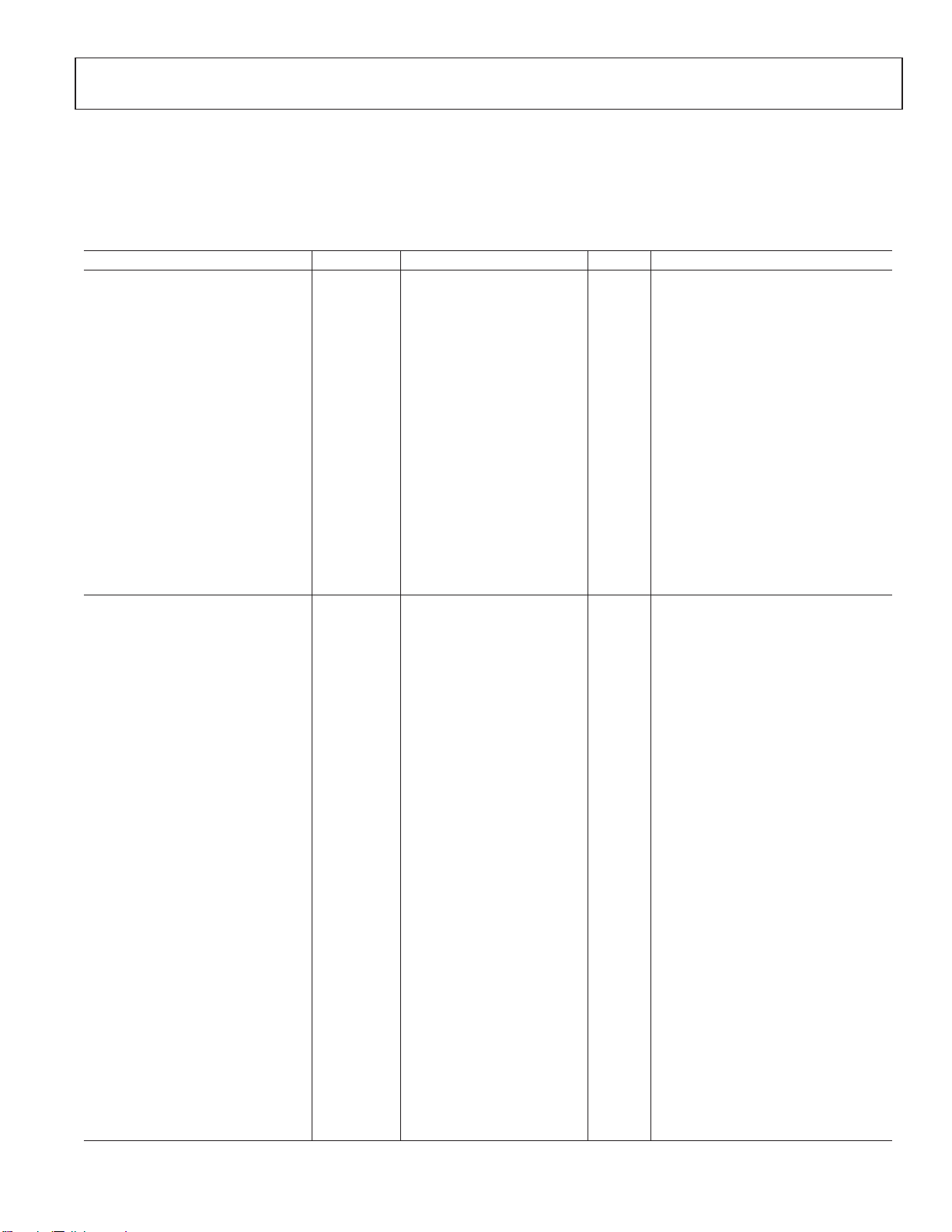

ADuM3470/ADuM3471/ADuM3472/ADuM3473/ADuM3474

X1

GND

1

V

DD1

X2

V

REG

GND

2

V

DD2

FB

V

IA/VOA

VOA/V

IA

V

IB/VOB

V

IC/VOC

VOB/V

IB

VOC/V

IC

V

ID/VOD

V

DDA

VOD/V

ID

OC

GND

1

GND

2

09369-025

INPUT (

V

Ix

)

OUTPUT (V

Ox

)

t

PLH

t

PHL

50%

50%

09369-018

用户必须根据所需的值和电源电流来选择电感。大多数开

关频率在

至

500 kHz至1 MHz

之间的应用中,都采用

90%

在开关频率低至

200 kHz

之间、负载瞬变在满负载

电感,如表19所示。

47 μH

的电源应用中,可采用

200 μH

10%

电感,

以稳定输出电 压或改善负载瞬态响应(见图30至图33)。

小型

1212或1210

电流能力的电感适用于负载低于

A

而具有

300 mA

100μH

的大部分应用。

肖特基二极管的低正向电压可降低损耗,且其高达

规格的电感见表19,具有

感值和

电流能力的电感适用于负载为

0.34A

400 mA

感值和

47 μH

的大部分应用,

40V

0.41

的

较高反向电压可承受如图39和图40所示的倍压电路产生

的峰值电压,因而推荐使用。

图

推荐的元件

19.

产品型号

制造厂商

值

GRM32ER71A476KE15L Murata 47 μF, 10 V,

X7R, 1210

GRM32ER71C226KEA8L Murata 22 μF, 16 V,

X7R, 1210

GRM31CR71A106KA01L

Murata 10 μF, 10 V,

X7R, 1206

MBR0540T1-D ON Semiconductor 0.5 A、40 V

肖特基、

、

SOD-

123

LQH3NPN470MM0 Murata 47 μH, 0.41 A,

1212

ME3220-104KL Coilcraft 100 μH, 0.34 A,

1210

印刷电路板(

PCB

)布局

ADuM347x

功耗约为

要通过

环境下,需要提供从

在电路板布局中,第1侧的

和第2侧的

为电源器件,在 满 负 载 下 以 最 大 速 度 工 作 时,

。因为不可能在隔离器上放置散热器,芯片主

1 W

引脚将热量耗散到

GND

GNDx

引脚到

GNDx

GNDx

引脚( 引 脚11和引 脚19)均 采 用 放 大

。如果器件应用在高温

PCB

地平面的散热路径。

PCB

引脚(引脚2和引脚10)

的焊盘。从焊盘到地平面和电源平面,应采用大直径过孔,

以提高导热率、降低电感。散热焊盘中的多个过孔可以显

著降低芯片内部的温度。扩大焊盘的尺寸由设计者进行评

估并由可用的电路板空间决定。

热分析

ADuM347x

的分离引线框架上。为了便于热分析,它被视为一个热单元,

其最高结温出现在表5中

到具有精细走线的

测量的。在正常工作条件下,

温度范围以满负载工作,输出电流无需减额。但是,采纳

印刷电路板