Analog Devices ADuM1100 e Datasheet

a

iCoupler® Digital Isolator

ADuM1100

FEATURES

High Data Rate: DC to 100 Mbps (NRZ)

Compatible with 3.3 V and 5.0 V Operation/

Level Translation

125ⴗC Max Operating Temperature

Low Power Operation

5 V Operation

1.0 mA Max @ 1 Mbps

4.5 mA Max @ 25 Mbps

16.8 mA Max @ 100 Mbps

3.3 V Operation

0.4 mA Max @ 1 Mbps

3.5 mA Max @ 25 Mbps

7.1 mA Max @ 50 Mbps

8-Lead SOIC Package (lead-free version available)

High Common-Mode Transient Immunity: >25 kV/s

Safety and Regulatory Information

UL Recognized

2500 V rms for 1 Minute per UL 1577

CSA Component Acceptance Notice No. 5A

VDE Certificate of Conformity

DIN EN 60747-5-2 (VDE 0884 Part 2): 2003–01

DIN EN 60950 (VDE 0805): 2001–12; EN 60950: 2000

= 560 V

V

IORM

PEAK

APPLICATIONS

Digital Fieldbus Isolation

Opto-Isolator Replacement

Computer-Peripheral Interface

Microprocessor System Interface

General Instrumentation and Data Acquisition

Applications

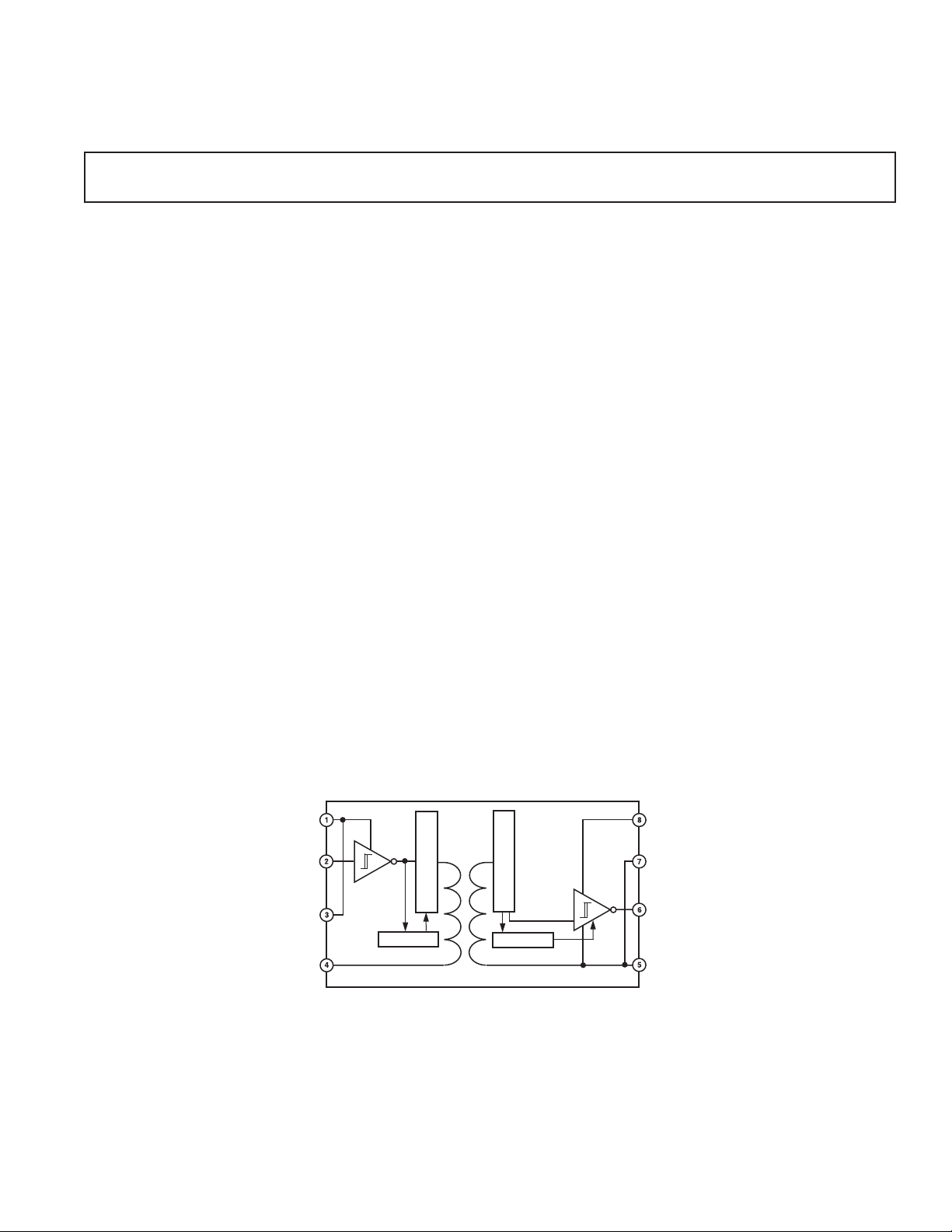

FUNCTIONAL BLOCK DIAGRAM

GENERAL DESCRIPTION

The ADuM1100 is a digital isolator based on Analog Devices’

iCoupler technology. Combining high speed CMOS and monolithic air core transformer technology, this isolation component

provides outstanding performance characteristics superior to

alternatives such as optocoupler devices.

Configured as a pin compatible replacement for existing high speed

optocouplers, the ADuM1100 supports data rates as high as

25 Mbps and 100 Mbps.

The ADuM1100 operates with either voltage supply ranging from

3.0 V to 5.5 V, boasts a propagation delay of <18 ns and edge

asymmetry of <2 ns, and is compatible with temperatures up to

125°C. It operates at very low power, less than 0.9 mA of quiescent

current (sum of both sides), and a dynamic current of less than

160 µA per Mbps of data rate. Unlike other optocoupler alternatives, the ADuM1100 provides dc correctness with a patented

refresh feature that continuously updates the output signal.

The ADuM1100 is offered in three grades. The ADuM1100AR

and ADuM1100BR can operate up to a maximum temperature

of 105°C and support data rates up to 25 Mbps and 100 Mbps,

respectively. The ADuM1100UR can operate up to a maximum

temperature of 125°C and supports data rates up to 100 Mbps.

V

DD1

(DATA IN)

V

DD1

GND

V

I

1

FOR PRINCIPLES OF OPERATION, SEE METHOD OF OPERATION,

DC CORRECTNESS, AND MAGNETIC FIELD IMMUNITY SECTION.

UPDATE

E

N

C

O

D

E

ADuM1100

REV. E

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

V

D

E

C

O

D

E

WATCHDOG

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

DD2

GND

2

V

O

(DATA OUT)

GND

2

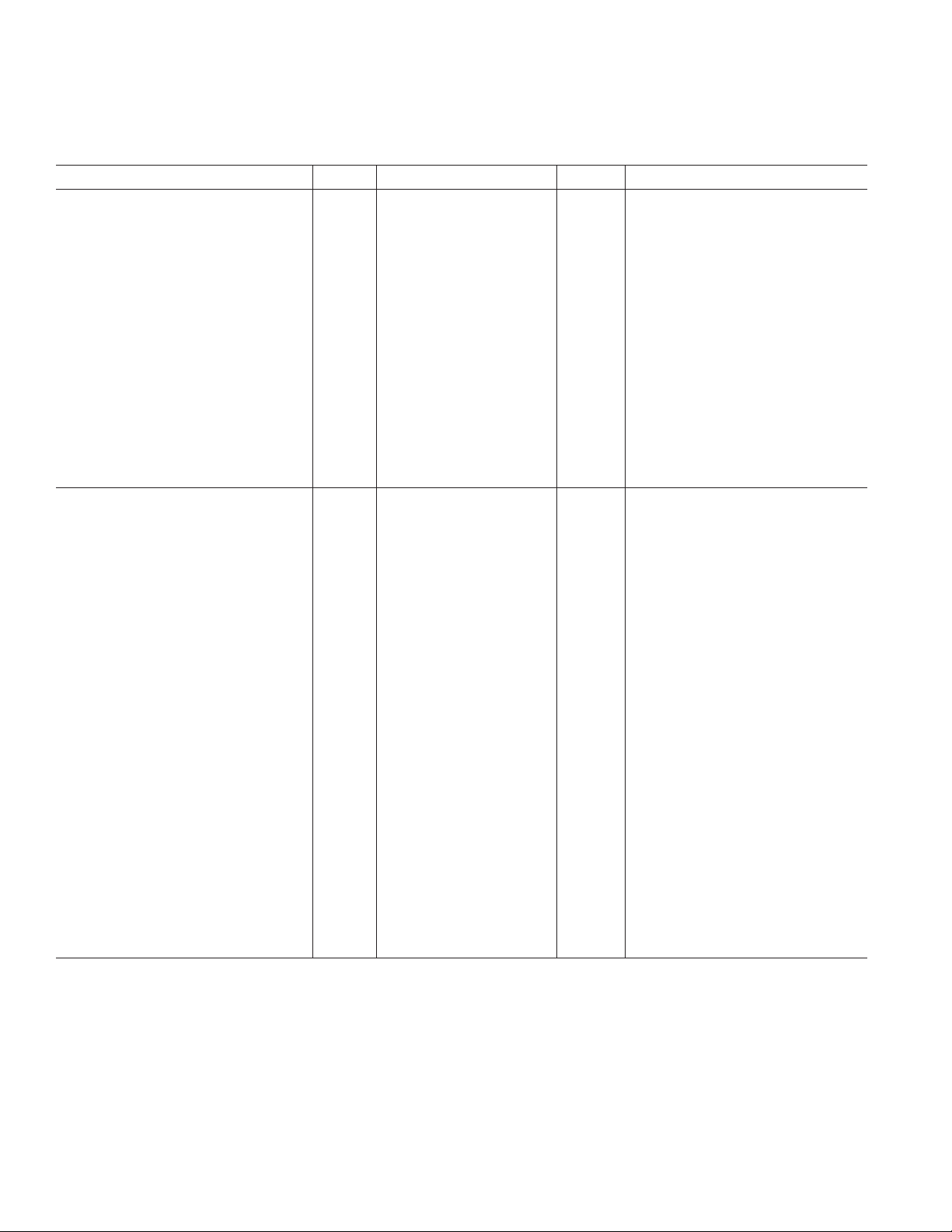

ADuM1100–SPECIFICATIONS

(4.5 V ≤ V

1

ELECTRICAL SPECIFICATIONS, 5 V OPERATION

range, unless otherwise noted. All typical specifications are at TA = 25ⴗC, V

specifications apply over the entire recommended operation

= V

DD2

= 5 V.)

DD1

Parameter Symbol Min Typ Max Unit Test Conditions

DC SPECIFICATIONS

Input Supply Current I

Output Supply Current I

Input Supply Current (25 Mbps) I

(See TPC 1)

Output Supply Current

2

(25 Mbps) I

DD1(Q)

DD2(Q)

DD1(25)

DD2(25)

0.3 0.8 mA VI = 0 V or V

0.01 0.06 mA VI = 0 V or V

2.2 3.5 mA 12.5 MHz Logic Signal Frequency

0.5 1.0 mA 12.5 MHz Logic Signal Frequency

(See TPC 2)

Input Supply Current (100 Mbps) I

(See TPC 1) ADuM1100BR/ADuM1100UR Only

Output Supply Current

2

(100 Mbps) I

DD1(100)

DD2(100)

9.0 14 mA 50 MHz Logic Signal Frequency,

2.0 2.8 mA 50 MHz Logic Signal Frequency,

(See TPC 2) ADuM1100BR/ADuM1100UR Only

Input Current I

Logic High Output Voltage V

Logic Low Output Voltage V

I

OH

OL

–10 +0.01 +10 µA0

V

– 0.1 5.0 V IO = –20 µA, VI = V

DD2

V

– 0.8 4.6 V IO = –4 mA, VI = V

DD2

0.0 0.1 V IO = 20 µA, VI = V

0.03 0.1 V IO = 400 µA, VI = V

0.3 0.8 V IO = 4 mA, VI = V

SWITCHING SPECIFICATIONS

For ADuM1100AR

Minimum Pulse Width

Maximum Data Rate

For ADuM1100BR/ADuM1100UR

Minimum Pulse Width

Maximum Data Rate

3

4

3

4

PW 40 ns CL = 15 pF, CMOS Signal Levels

25 Mbps CL = 15 pF, CMOS Signal Levels

PW 6.7 10 ns CL = 15 pF, CMOS Signal Levels

100 150 Mbps CL = 15 pF, CMOS Signal Levels

For All Grades

Propagation Delay Time t

to Logic Low Output

5, 6

PHL

10.5 18 ns CL = 15 pF, CMOS Signal Levels

(See TPC 3)

Propagation Delay Time t

to Logic High Output

5, 6

PLH

10.5 18 ns CL = 15 pF, CMOS Signal Levels

(See TPC 3)

Pulse Width Distortion |t

Change versus Temperature

Propagation Delay Skew t

(Equal Temperature)

Propagation Delay Skew t

(Equal Temperature, Supplies)

Output Rise/Fall Time tR, t

Common-Mode Transient Immunity |CM

at Logic Low/High Output

Input Dynamic Power C

Dissipation Capacitance

Output Dynamic Power C

Dissipation Capacitance

See Notes on page 5.

Specifications subject to change without notice.

6, 8

PLH

10

10

– t

|6PWD 0.5 2 ns CL = 15 pF, CMOS Signal Levels

PHL

7

PSK1

PSK2

6, 8

F

|, 25 35 kV/µsV

9

L

|CMH|Transient Magnitude = 800 V

PD1

PD2

3 ps/°CC

8nsC

6nsC

3nsC

35 pF

8pF

≤ 5.5 V, 4.5 V ≤ V

DD1

≤ 5.5 V. All min/max

DD2

DD1

DD1

≤ VIN ≤ V

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 0 or V

I

DD1

IH

IH

IL

IL

IL

, VCM = 1000 V,

DD1

–2–

REV. E

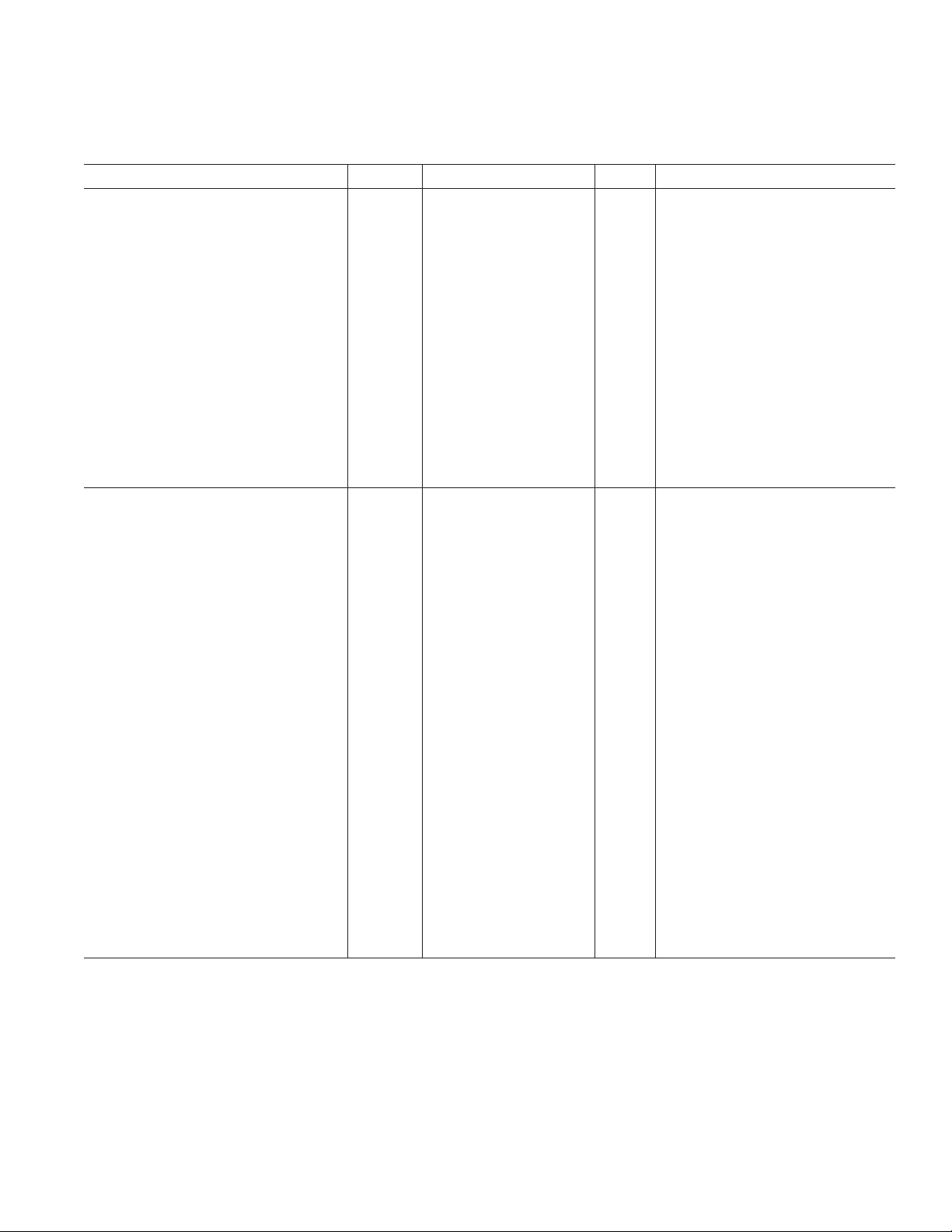

ADuM1100

ELECTRICAL SPECIFICATIONS, 3.3 V OPERATION

range, unless otherwise noted. All typical specifications are at TA = 25ⴗC, V

DD1

(3.0 V ≤ V

1

specifications apply over the entire recommended operation

= V

= 3.3 V.)

DD2

≤ 3.6 V, 3.0 V ≤ V

DD1

≤ 3.6 V. All min/max

DD2

Parameter Symbol Min Typ Max Unit Test Conditions

DC SPECIFICATIONS

Input Supply Current I

Output Supply Current I

Input Supply Current (25 Mbps) I

(See TPC 1)

Output Supply Current

2

(25 Mbps) I

DD1(Q)

DD2(Q)

DD1(25)

DD2(25)

0.1 0.3 mA VI = 0 V or V

0.005 0.04 mA VI = 0 V or V

DD1

DD1

2.0 2.8 mA 12.5 MHz Logic Signal Frequency

0.3 0.7 mA 12.5 MHz Logic Signal Frequency

(See TPC 2)

Input Supply Current (50 Mbps) I

(See TPC 1) ADuM1100BR/ADuM1100UR Only

Output Supply Current

2

(50 Mbps) I

DD1(50)

DD2(50)

4.0 6.0 mA 25 MHz Logic Signal Frequency,

1.2 1.6 mA 25 MHz Logic Signal Frequency,

(See TPC 2) ADuM1100BR/ADuM1100UR Only

Input Current I

Logic High Output Voltage V

Logic Low Output Voltage V

I

OH

OL

–10 +0.01 +10 µA0

V

– 0.1 3.3 V IO = –20 µA, VI = V

DD2

V

– 0.5 3.0 V IO = –2.5 mA, VI = V

DD2

0.0 0.1 V IO = 20 µA, VI = V

0.04 0.1 V IO = 400 µA, VI = V

0.3 0.4 V IO = 2.5 mA, VI = V

≤ VIN ≤ V

DD1

IH

IH

IL

IL

IL

SWITCHING SPECIFICATIONS

For ADuM1100AR

Minimum Pulse Width

Maximum Data Rate

For ADuM1100BR/ADuM1100UR

Minimum Pulse Width

Maximum Data Rate

3

4

3

4

PW 40 ns CL= 15 pF, CMOS Signal Levels

25 Mbps CL= 15 pF, CMOS Signal Levels

PW 10 20 ns CL= 15 pF, CMOS Signal Levels

50 100 Mbps CL= 15 pF, CMOS Signal Levels

For All Grades

Propagation Delay Time to t

Logic Low Output

5, 6

PHL

14.5 28 ns CL= 15 pF, CMOS Signal Levels

(See TPC 4)

Propagation Delay Time to t

Logic High Output

5, 6

PLH

15.0 28 ns CL= 15 pF, CMOS Signal Levels

(See TPC 4)

– t

Pulse Width Distortion |t

PLH

Change versus Temperature

Propagation Delay Skew t

(Equal Temperature)

6, 8

Propagation Delay Skew t

(Equal Temperature, Supplies)

Output Rise/Fall Time tR, t

Common-Mode Transient Immunity |CM

at Logic Low/High Output

Input Dynamic Power Dissipation C

Capacitance

Output Dynamic Power Dissipation C

Capacitance

See Notes on page 5.

Specifications subject to change without notice.

10

10

|6PWD 0.5 3 ns CL= 15 pF, CMOS Signal Levels

PHL

7

PSK1

6, 8

9

PSK2

F

|, 25 35 kV/µsVI=0 or V

L

|CMH|Transient Magnitude = 800 V

PD1

PD2

10 ps/°CCL= 15 pF, CMOS Signal Levels

15 ns CL= 15 pF, CMOS Signal Levels

12 ns CL= 15 pF, CMOS Signal Levels

3nsC

= 15 pF, CMOS Signal Levels

L

, VCM= 1000 V,

DD1

47 pF

14 pF

REV. E

–3–

ADuM1100

(5 V/3 V operation: 4.5 V ≤ V

= 5 V, V

1

≤ 5.5 V, 3.0 V ≤ V

= 3.3 V.)

DD2

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

= 15 pF, CMOS Signal Levels

L

DD2

ID

IL

IH

IL

IL

≤ 3.6 V.

≤ V

IH

IH

IL

IL

IH

IL

DD1

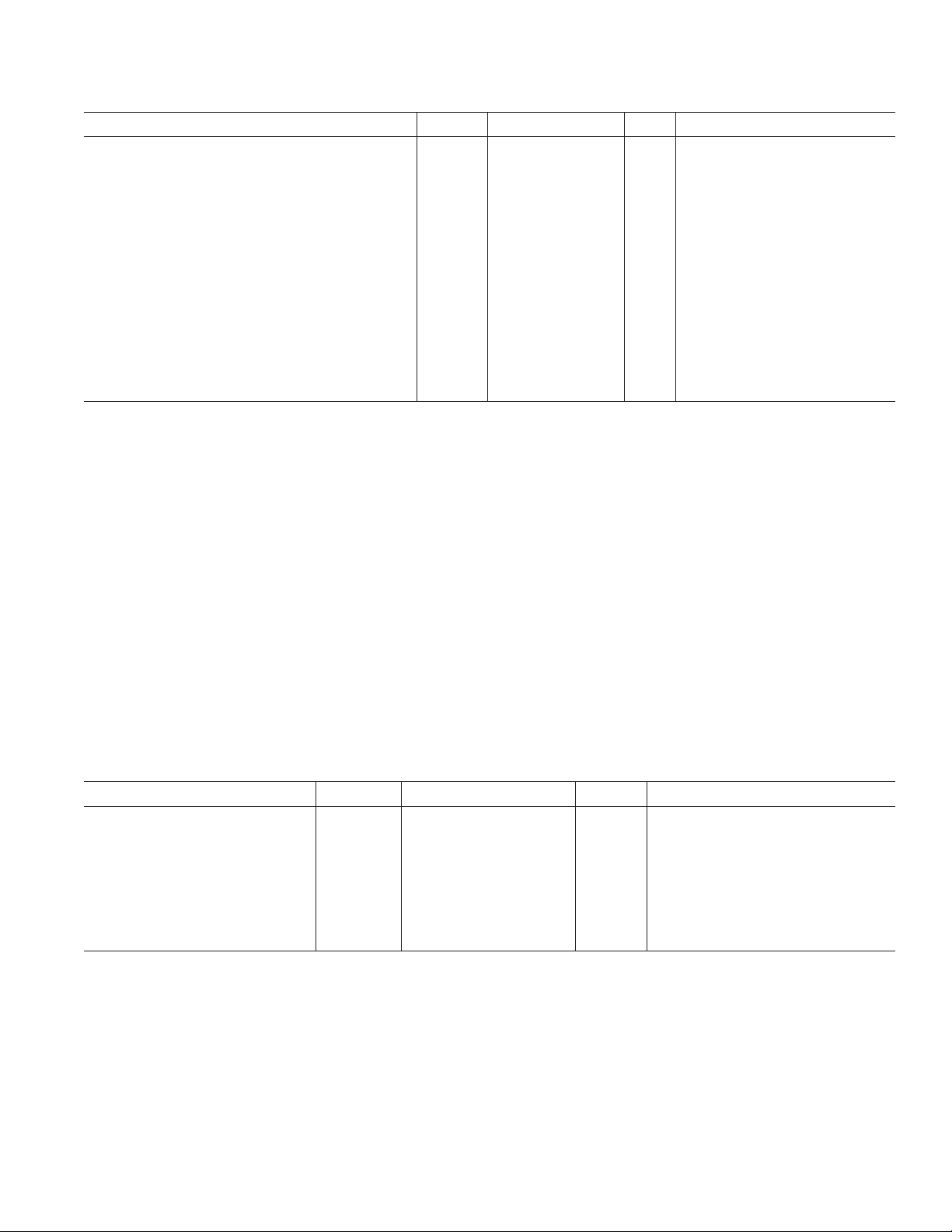

ELECTRICAL SPECIFICATIONS, MIXED 5 V/3 V or 3 V/5 V OPERATION

3 V/5 V operation: 3.0 V ≤ V

unless otherwise noted. All typical specifications are at TA = 25ⴗC, V

Parameter Symbol Min Typ Max Unit Test Conditions

DC SPECIFICATIONS

Input Supply Current, Quiescent I

5 V/3 V Operation 0.3 0.8 mA

3 V/5 V Operation 0.1 0.3 mA

Output Supply Current, Quiescent I

5 V/3 V Operation 0.005 0.04 mA

3 V/5 V Operation 0.01 0.06 mA

Input Supply Current, 25 Mbps I

5 V/3 V Operation 2.2 3.5 mA 12.5 MHz Logic Signal Frequency

3 V/5 V Operation 2.0 2.8 mA 12.5 MHz Logic Signal Frequency

Output Supply Current, 25 Mbps I

5 V/3 V Operation 0.3 0.7 mA 12.5 MHz Logic Signal Frequency

3 V/5 V Operation 0.5 1.0 mA 12.5 MHz Logic Signal Frequency

Input Supply Current, 50 Mbps I

5 V/3 V Operation 4.5 7.0 mA 25 MHz Logic Signal Frequency

3 V/5 V Operation 4.0 6.0 mA 25 MHz Logic Signal Frequency

Output Supply Current, 50 Mbps I

5 V/3 V Operation 1.2 1.6 mA 25 MHz Logic Signal Frequency

3 V/5 V Operation 1.0 1.5 mA 25 MHz Logic Signal Frequency

Input Currents I

Logic High Output Voltage, V

5 V/3 V Operation V

Logic Low Output Voltage, V

5 V/3 V Operation 0.04 0.1 V IO = 400 µA, VI = V

Logic High Output Voltage, V

3 V/5 V Operation V

Logic Low Output Voltage, V

3 V/5 V Operation 0.03 0.1 V IO = 400 µA, VI = V

SWITCHING SPECIFICATIONS

For ADuM1100AR

Minimum Pulse Width

Maximum Data Rate

For ADuM1100BR/ADuM1100UR

Minimum Pulse Width

Maximum Data Rate

For All Grades

Propagation Delay Time to Logic t

Low/High Output

5 V/3 V Operation (See TPC 5) 13 21 ns CL = 15 pF, CMOS Signal Levels

3 V/5 V Operation (See TPC 6) 16 26 ns C

Pulse Width Distortion, |t

5 V/3 V Operation 0.5 2 ns C

3 V/5 V Operation 0.5 3 ns C

Change versus Temperature

5 V/3 V Operation 3 ps/ºC C

3 V/5 V Operation 10 ps/ºC C

Propagation Delay Skew t

(Equal Temperature)

5 V/3 V Operation 12 ns CL = 15 pF, CMOS Signal Levels

3 V/5 V Operation 15 ns CL = 15 pF, CMOS Signal Levels

≤ 3.6 V, 4.5 V ≤ V

DD1

3

4

3

4

5, 6

PLH

6, 8

– t

PHL

≤ 5.5 V. All min/max specifications apply over the entire recommended operation range,

DD2

DDI(Q)

DDO(Q)

DDI(25)

DDO(25)

DDI(50)

DDO(50)

IA

OH

OL

= 3.3 V, V

DD1

–10 +0.01 +10 µA0≤ VIA, VIB, VIC, V

V

– 0.1 3.3 V IO = –20 µA, VI = V

DD2

– 0.5 3.0 V IO = –2.5 mA, VI = V

DD2

= 5 V or V

DD2

DD1

0.0 0.1 V IO = 20 µA, VI = V

0.3 0.4 V IO = 2.5 mA, VI = V

V

OH

OL

– 0.1 5.0 V IO = –20 µA, VI = V

DD2

– 0.8 4.6 V IO = –4 mA, VI = V

DD2

0.0 0.1 V IO = 20 µA, VI = V

0.3 0.8 V IO = 4 mA, VI = V

PW 40 ns CL = 15 pF, CMOS Signal Levels

25 Mbps CL = 15 pF, CMOS Signal Levels

PW 20 ns CL = 15 pF, CMOS Signal Levels

50 Mbps CL = 15 pF, CMOS Signal Levels

PHL, tPLH

6

|

PWD

PSK1

DD1

or V

DD2

–4–

REV. E

ADuM1100

Parameter Symbol Min Typ Max Unit Test Conditions

SWITCHING SPECIFICATIONS (continued)

Propagation Delay Skew t

(Equal Temperature, Supplies)

6, 8

5 V/3 V Operation 9 ns CL = 15 pF, CMOS Signal Levels

3 V/5 V Operation 12 ns C

Output Rise/Fall Time (10% to 90%) t

Common-Mode Transient Immunity at

Logic Low/High Output

8

Input Dynamic Power Dissipation Capacitance10C

5 V/3 V Operation 35 pF

3 V/5 V Operation 47 pF

Output Dynamic Power Dissipation Capacitance

5 V/3 V Operation 8 pF

3 V/5 V Operation 14 pF

NOTES

1

All voltages are relative to their respective ground.

2

Output supply current values are with no output load present. The supply current drawn at a given signal frequency when an output load is present is given by

I

= I

+ V

DD2(L)

3

The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.

4

The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.

5

t

the rising edge of the VI signal to the 50% level of the rising edge of the VO signal.

6

Since the input thresholds of the ADuM1100 are at voltages other than the 50% level of typical input signals, the measured propagation delay and pulse width distortion

DD2

is measured from the 50% level of the falling edge of the VI signal to the 50% level of the falling edge of the VO signal. t

PHL

× f × CL, where I

DD2

may be affected by slow input rise/fall times. See the Propagation Delay-Related Parameters section and Figures 3 to 7 for information on the impact of given input

rise/fall times on these parameters.

7

Pulse width distortion change versus temperature is the absolute value of the change in pulse width distortion for a 1°C change in operating temperature.

8

t

is the magnitude of the worst-case difference in t

PSK1

the recommended operating conditions. t

temperature, supply voltages, and output load within the recommended operating conditions.

9

CMH is the maximum common-mode voltage slew rate that can be sustained while maintaining VO > 0.8 V

rate that can be sustained while maintaining VO < 0.8 V. The common-mode voltage slew rates apply to both rising and falling edges. The transient magnitude is the

range over which the common-mode is slewed.

10

The dynamic power dissipation capacitance is given by

C

= (I

PDi

The supply current consumptions at a given frequency and output load are calculated as

I

= C

DD1

DDi(100)

× V

PD1

– I

DD1

DDi(Q)

× f + I

)/(V

× f), where i = 1 or 2 and f is the input signal frequency.

DDi

DD1(Q)

Specifications subject to change without notice.

is the unloaded output supply current, f is the input signal frequency, and CL is the output load capacitance.

DD2

and/or t

PHL

is the magnitude of the worst-case difference in t

PSK2

; I

= (C

DD2(L)

+ CL) × V

PD2

DD2

PSK2

= 15 pF, CMOS Signal Levels

, t

R

f

3nsC

|CML|, 25 35 kV/µsVI = 0 or V

|Transient Magnitude = 800 V

|CM

H

PD1

10

C

PD2

that will be measured between units at the same operating temperature and output load within

× f + I

PLH

, where CL is the output load capacitance.

DD2(Q)

PHL

and/or t

that will be measured between units at the same operating

PLH

. CML is the maximum common-mode voltage slew

DD2

L

= 15 pF, CMOS Signal Levels

L

, VCM = 1000 V,

DD1

is measured from the 50% level of

PLH

PACKAGE CHARACTERISTICS

Parameter Symbol Min Typ Max Unit Test Conditions

Resistance (Input-Output)

Capacitance (Input-Output)

Input Capacitance

2

1

1

Input IC Junction-to-Case θ

R

I–O

C

I–O

C

I

JCI

12

10

Ω

1pFf = 1 MHz

4.0 pF

46 °C/W Thermocouple Located at Center

Thermal Resistance Underside of Package

Output IC Junction-to-Case θ

JCO

41 °C/W

Thermal Resistance

Package Power Dissipation P

NOTES

1

Device considered a 2-terminal device: Pins 1, 2, 3, and 4 shorted together and Pins 5, 6, 7, and 8 shorted together.

2

Input capacitance is measured at Pin 2 (VI).

REV. E

PD

–5–

240 mW

Loading...

Loading...