Low Power Precision Analog Microcontroller

ARM Cortex M3, with dual Sigma-Delta ADCs

ADuCM360/ADuCM361

Rev. Pr R

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

Preliminary Technical Data

FEATURES

Analog Input/Output

Dual (24-bit) ADCs (ADuCM360)

Single (24-bit) ADC (ADuCM361)

Single Ended and fully Differential inputs

Programmable ADC output rate (4 Hz to 4 kHz)

Simultaneous 50Hz/60Hz rejection

50SPS Continuous Conversion Mode

16.67SPS Single Conversion Mode

Flexible input MUX for input channel selection to both ADCs

Primary and Auxiliary (24-bit) ADC channel

6 differential or 11 Single-Ended input channels

4 internal channels for monitoring DAC, Temperature

sensor, IOVDD and AVDD (ADC1 only)

Programmable Gain (1 to 128)

Selectable input range: ±6.64 mV to ±1.2 V

RMS noise: 43nV @3.75Hz, 180nV @ 50Hz

Programmable sensor excitation current sources

10/50/100/150/200/250/300/400/500/600/800uA and

1mA current source options

On-chip precision Voltage reference (±4 ppm/°C)

Single 12-bit voltage output DAC

NPN mode for 4-20mA loop applications

Microcontroller

ARM Cortex™-M3 32-bit processor

Serial Wire download and debug

Internal Watch crystal for wakeup timer

16 MHz Oscillator with 8-way Programmable Divider

Memory

128k Bytes Flash/EE Memory, 8k Bytes SRAM

In-circuit debug/download via Serial Wire and UART

Power

Operates directly from a 3.0V battery

Supply Range: 1.8V to 3.6V (max)

Power Consumption

MCU Active Mode: Core consumes 290µA / MHz

Active Mode: 1.0mA (All peripherals active), core

operating at 500KHz

Power down mode: 4µA (WU Timer Active)

On-Chip Peripherals

UART, I2C and 2 x SPI Serial I/O

16-bit PWM Controller

19-Pin Multi-Function GPIO Port

2 General Purpose Timers

Wake -up Ti mer/Watchdog Timer

Multi-Channel DMA and Interrupt Controller

Package and Temperature Range

48 lead LFCSP (7mm x 7mm) package –40°C to 125°C

Development Tools

Low-Cost QuickStart™ Development System

Third-Party Compiler and emulator tool Support

Multiple Functional Safety features for improved diagnostics

APPLICATIONS

Industrial automation and process control

Intelligent, precision sensing systems

4 mA to 20 mA loop-powered smart sensor systems

Medical devices, patient monitoring

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices .

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

ADuCM360/ADuCM361

Ain0

Ain1

Ain5/IEXC

Ain10

DAC

Ain4/IEXC

Ain11/VBias1

Ain3

Ain2

Ain6/IEXC

Ain7/IEXC/VBias0/EXT_REF2IN+

Ain8/EXT_REF2IN-

Ain9

AGND

IREF

AVDD

19GENERAL

PURPOSE

I/OPORTS

POR

ON-CHIP

OSC(3%)

16MHz

GPIOPORTs

UARTPORT

2 xSPI PORTs

I2CPORT

ARM

CORTEX-M3

MCU

16MHz

PRECISION

REFERENCE

RESET

XTAL0

XTAL1

VREF+

GND_SW

MEMORY

128KBFLASH

8KBSRAM

TIMER0

TIMER1

WATCHDOG

WAKEUP-TIMER

PWM

.

.

12-BIT

DAC

VREF-

MUX

SINC3/4

FILTER

AMP

.

.

.

BUF

ON-CHIP

1.8VDIGITAL

LDO

.

.

.

VBias

Gen

...

.

.

.

ON-CHIP

1.8VANALOG

LDO

DAC,

TEMP,

IOVDD/4

AVDD/4

DMA+

INTERRUPT

CONTROLLER

SERIAL WIRE

DEBUG+

PROGRAMMING

&DEBUG

BUF

...

.

SELECTABLE

VREFSources

VREF

SWCLK

SWDIO

DVDD_REG

AVDD_REG

IOVDD

IOVDD

10/50/100/200/

500/750/1000uA

Current Sources

.

BUF

INT_REF

.

.

SINC2

FILTER

.

.

.

.

.

.

Σ−∆

Modulator

24-BIT

Σ−∆

ADC

SINC3/4

FILTER

.

VREF

.

SINC2

FILTER

Σ−∆

Modulator

24-BIT

Σ−∆

ADC

.

.

AMP

..

.

.

.

.

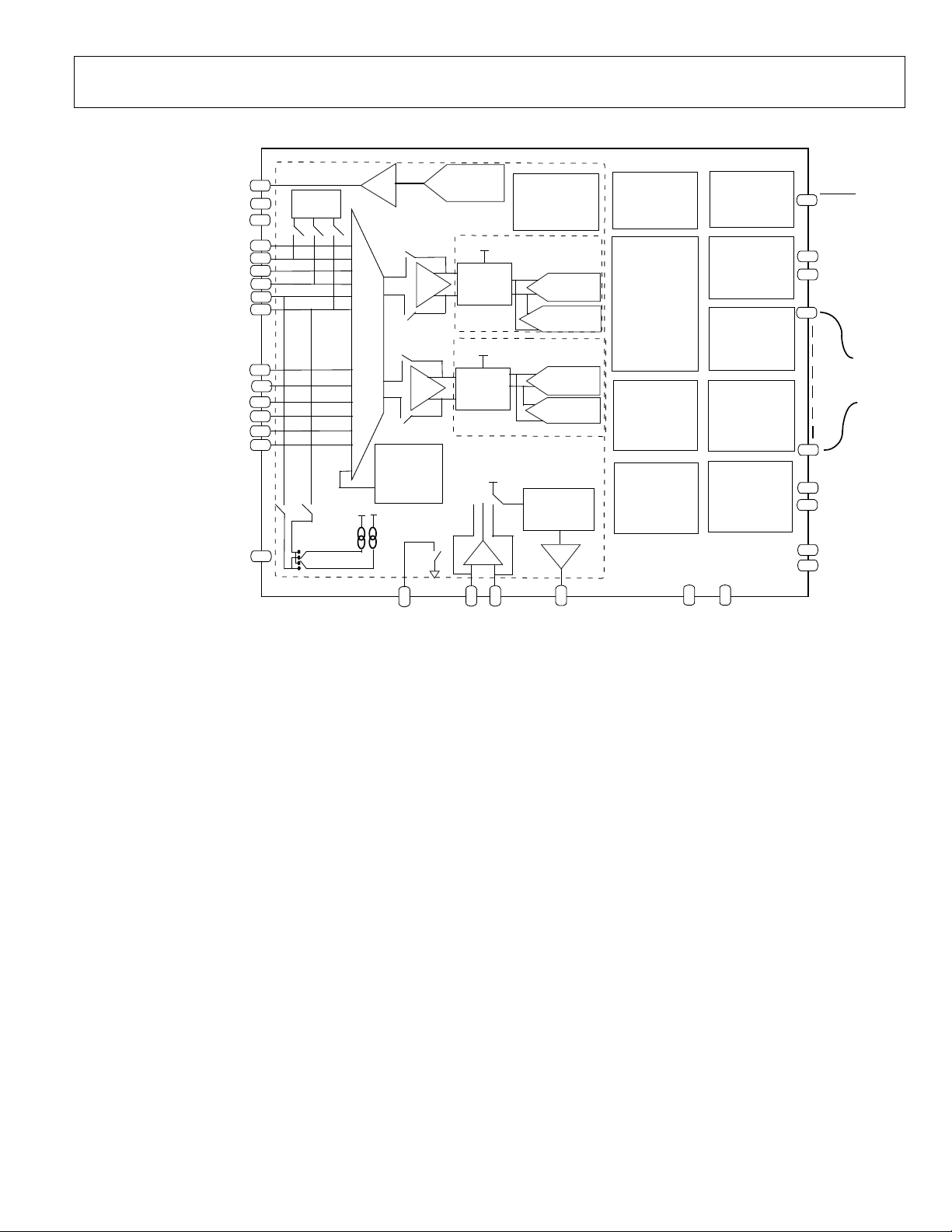

Preliminary Technical Data

FUNCTIONAL BLOCK DIAGRAM

Figure 1. ADuCM360 Block Diagram

Rev. Pr R Page 2 of 21

Preliminary Technical Data

TABLE OF CONTENTS

Features ............................................................................................... 1

Functional Block Diagram ............................................................... 2

General Description .......................................................................... 4

Specifications ..................................................................................... 5

ADuCM360/ADuCM361 Microcontroller Electrical

Specifications ................................................................................. 5

ADuCM360/ADuCM361

Noise Resolution of Primary and Auxiliary ADCs ................ 10

I2C Timing Diagrams ................................................................. 12

SPI Timing Diagrams ................................................................. 13

Absolute Maximum Ratings .......................................................... 16

ESD Caution ................................................................................ 16

Outline Dimensions ........................................................................ 21

Rev. Pr R| Page 3 of 21

ADuCM360/ADuCM361

GENERAL DESCRIPTION

The ADuCM360 is a fully integrated, 4 kSPS, 24-bit data acquisition system incorporating dual, high performance multichannel sigma-delta (Σ-Δ) analog-to-digital converters (ADCs),

32-bit ARM Cortex M3® MCU, and Flash/EE memory on a

single chip. The part is designed for direct interfacing to

external precision sensors in both wired and battery powered

applications.

The ADuCM361 contains all the features of the ADuCM360

except the primary ADC, ADC0 is not available – only the

auxiliary ADC, ADC1 is available.

The device contains an on-chip 32 KHz oscillator and an

internal 16MHz high-frequency oscillator. This clock is routed

through a programmable clock divider from which the MCU

core clock operating frequency is generated. The maximum

core clock speed is 16MHz and this is not limited by operating

voltage or temperature.

The microcontroller core is a low power Cortex-M3 core from

ARM. It is a 32-bit RISC machine, offering up to 20 MIPS peak

performance. The Cortex-M3 MCU incorporates a flexible 11channel DMA controller supporting all wired (SPI, UART, I

communication peripherals. 128k Bytes of non-volatile

Flash/EE and 8k Bytes of SRAM are also integrated on-chip.

The Analog sub-system consists of dual ADCs each connected

to a flexible input MUX. Both ADCs can operate in fully

differential and single ended modes. Other on-chip ADC

features include dual programmable excitation current sources,

burn-out current sources and a bias voltage generator of

AVDD_REG/2 (900mV) to set the common-mode voltage of an

input channel. A low-side internal ground switch is provided to

allow powering down of a bridge between conversions. The

ADCs contain two parallel filters – a Sinc3 or Sinc4 in parallel

with a Sinc2. The Sinc3 or Sinc4 filter is for precision

measurements. The Sinc2 filter is for fast measurements and for

detection of step changes in the input signal The device also

contains a low noise, low drift internal band-gap reference or

can be configured to accept up to 2 external reference sources in

ratiometric measurement configurations. An option to buffer

the external reference inputs is also provided on-chip. A singlechannel buffered voltage output DAC is also provided on chip.

2

C)

Preliminary Technical Data

The ADuCM360/ADuCM361 also integrates a range of on-chip

peripherals which can be configured under microcontroller

software control as required in the application. These

peripherals include UART, I2C and dual SPI Serial I/O

communication controllers, 19-Pin GPIO Ports, 2 General

Purpose Timers, Wake-up Timer and System Watchdog Timer.

A 16-bit PWM with six output channels is also provided.

The ADuCM360/ADuCM361 is specifically designed to operate

in battery powered applications where low power operation is

critical. The microcontroller core can be configured in a normal

operating mode consuming 290μA/MHz (including

Flash/SRAM Idd) resulting in an overall system current

consumption of 1mA when all peripherals are active.

The part can also be configured in a number of low power

operating modes under direct program control, including

hibernate mode (internal wake-up timer active) consuming

only 4µA. In hibernate mode, peripherals such as external

interrupts or the internal wake up timer can wake up the device.

This allows the part to operate in an ultra-low power operating

mode and still respond to asynchronous external or periodic

events.

On-chip factory firmware supports in-circuit serial download

via a serial wire interface (2-pin JTAG system) and UART while

non-intrusive emulation is also supported via the serial wire

interface. These features are incorporated into a low-cost

QuickStart Development System supporting this Precision

Analog Microcontroller family.

The part operates from an external 1.8V to 3.6V voltage supply

and is specified over an industrial temperature range of -40°C to

125°C.

Rev. Pr R Page 4 of 21

Preliminary Technical Data

Conversion Rate1

Chop off

4 4000

Hz

RMS Noise and Data Output

See Noise and Resolution tables

ADuCM360/ADuCM361

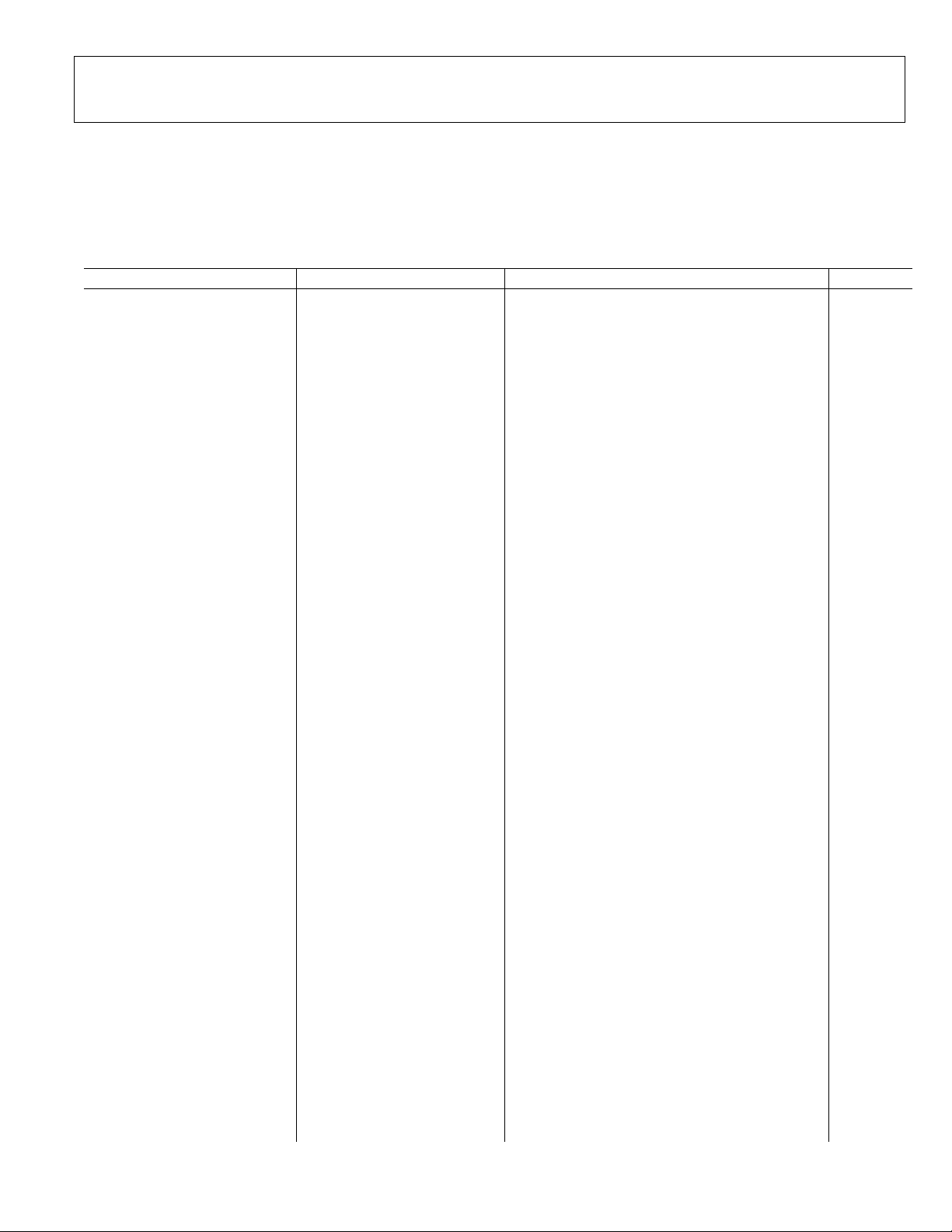

SPECIFICATIONS

ADUCM360/ADUCM361 MICROCONTROLLER ELECTRICAL SPECIFICATIONS

AVDD/IOVDD = 1.8 V to 3.6V, Internal 1.2V reference, f

noted.

Table 1. ADuCM360/ADuCM361 Specifications

Parameter Test Conditions/Comments Min Typ Max Unit

ADC SPECIFICATIONS

Chop on 4 1333 Hz

Both Primary & Auxiliary

Channels

No Missing Codes1 Chop off (f

Chop on (f

≤ 500 Hz) 24 Bits

ADC

≤ 250 Hz) 24 Bits

ADC

= 16 MHz, all specifications TA = −40°C to +125°C, unless otherwise

CORE

Rates

Integral Nonlinearity1 Gain = 1

in the User Guide

Gain = 2, 4, 8, 16, 32, 64, 128

±15

±25

ppm of FSR

Offset Error

,2, 3

Chop off, offset error is in the

±100/Gain μV

order of the noise for the programmed gain and update rate

following calibration

Offset Error

Offset Error Drift vs.

Temperature

Offset Error Drift vs. Time

Full-Scale Error

Gain Drift vs. Temperature

1,2,3

Chop on ±1.0 μV

4

Chop off 100/ Gain nV/°C

Chop on 10 nV/°C

1,5, 6,7

±0.5/Gain TBD mV

TBD nV/1000

4

Gain = 1 to 16, external

±1 ppm/°C

reference

Gain = 32 to 128 external

±3

reference

Gain Error Drift vs. Time

TBD ppm/1000

PGA Gain Mismatch Error ±0.15 %

Power Supply Rejection

1,8

Chop on, ADC = 0.25 V (Gain =

85 dB

4), ext. reference

Chop off, ADC = 7.8 mV (Gain =

100 dB

128), ext. reference

Chop off, ADC = 1 V (Gain = 1),

85 dB

ext. reference

Absolute I nput Voltage Range

Unbuffered Mode Gain=1 AGND Avdd V

Buffered Mode Gain =1 AGND+ 100mV Avdd-100mV V

Unbuffered Mode:

Differential Input Voltage

1

Ranges

Gain >=2

Gain = 1

Gain = 2

Gain = 4

Gain = 8

Gain = 16

Gain = 32 (AVDD >=2.0V)

(AVDD <2.0V)

Gain = 64 (AVDD >=2.0V)

Rev. Pr R| Page 5 of 21

AGND

Avdd

±VREF

±500

±250

±125

±62.5

±26.56

±18.75

±13.28

ppm of FSR

hours

hours

mV

mV

mV

mV

mV

mV

mV

mV

mV

ADuCM360/ADuCM361

(AVDD <2.0V)

±9.375

mV

ADC Gain =2 to 128

80

dB

mode before measurement

Voltage TC

250 mV/°C

Internal V

1.2 V

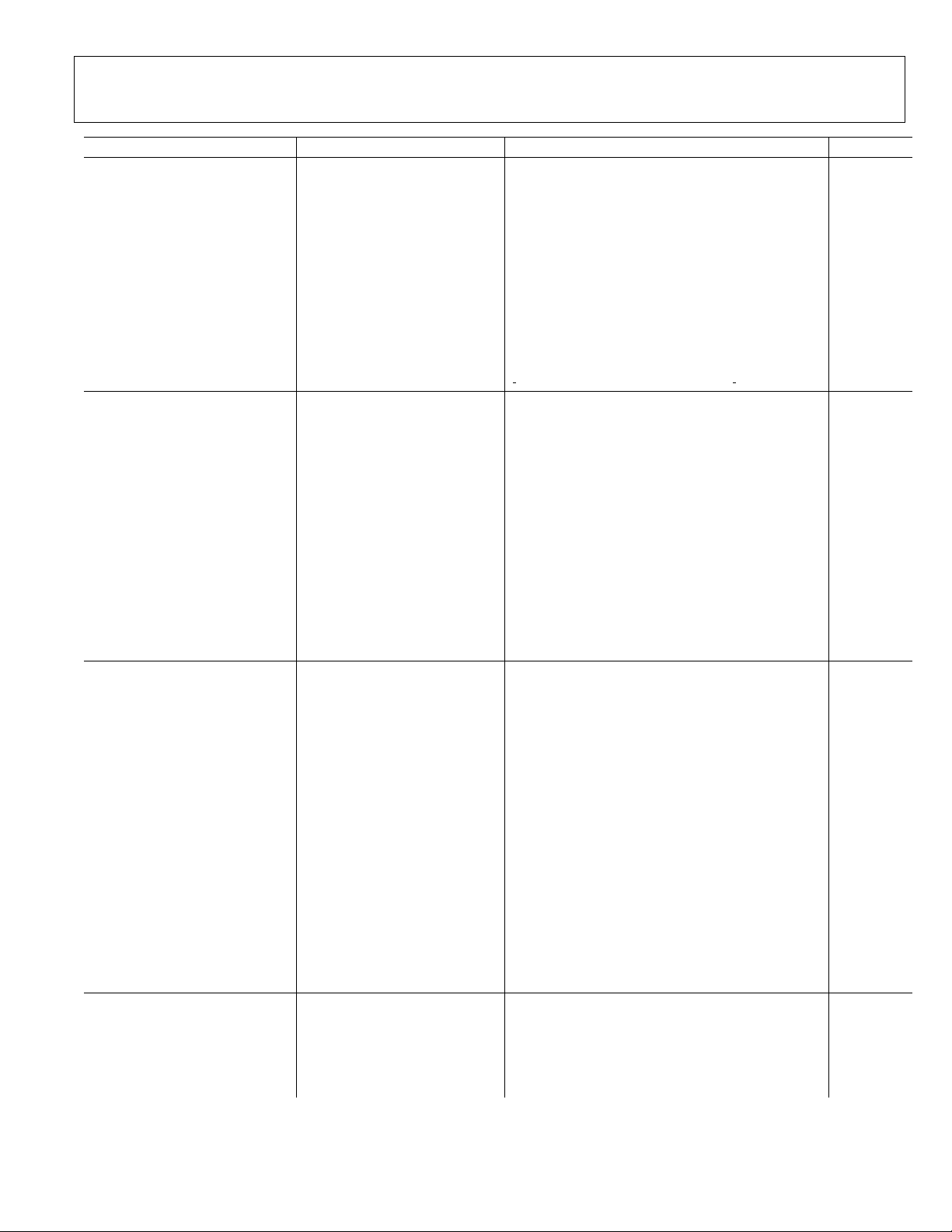

Preliminary Technical Data

Parameter Test Conditions/Comments Min Typ Max Unit

Gain = 128 (AVDD >=2.0V)

(AVDD <2.0V)

Common mode Voltage, Vcm1 Vcm=(AIN(+)+AIN(-))/2,

AGND V

±6.64

±4.6875

Gain=2 to 128

Input current will be higher

when Vcm <0.5V

Input Current

1,9

Gain = 1, Buffered mode

1 nA

(excluding pins with Vbias)

Gain >1, Buffered mode

2 nA

(excluding pins with Vbias)

Unbuffered mode. Input current

500 nA/V

will vary with input voltage

Average Input Current Drift Buffered mode:

AIN0, AIN1, AIN2, AIN3

AIN4, AIN5, AIN6, AIN7

AIN8, AIN9, AIN10, AIN11

±5

±16

±9

Unbuffered mode ±250 pA/V/°C

Common-Mode Rejection DC1

On ADC Input ADC Gain =1 70 100

Common-Mode Rejection1

50 Hz/60 Hz

50 Hz/60 Hz ± 1 Hz,

16.7 Hz update rate, chop on

50 Hz update rate, chop off

ADC Gain =1 97 dB

ADC Gain =2 to 128 90 dB

Normal-Mode Rejection

1

50 Hz/60 Hz

On ADC Input 50 Hz/60 Hz ± 1 Hz, 16.6 Hz f

chop on, 50 Hz f

chop off

ADC/

60 80 dB

ADC/

TEMPERATURE SENSOR After user calibration

Voltage Output at 25°C MCU in power down or standby

82.1 mV

mV

mV

pA/°C

pA/°C

pA/°C

Accuracy 6 °C

GROUND SWITCH

Ron 12 Ohms

Allowable Current With 20K resistor off – direct

VOLTAGE REFERENCE

ADC Precision Reference

Initial Accuracy1 Measured at TA = 25°C -0.05 0.05 %

Reference Temperature

Coefficient (Tempco)

Power Supply Rejection1 100 dB

REF

20 mA

short to ground

1,8

−15 ±8 +15 ppm/°C

Rev. Pr R Page 6 of 21

Preliminary Technical Data

Normal Mode Rejection

80

Using external 150 kΩ reference

75 ppm/°C

Parameter Test Conditions/Comments Min Typ Max Unit

External Reference Input

Range

Input Current Buffered mode 15 nA

Unbuffered mode 500 nA/V

Buffered mode

Unbuffered mode

Minimum Differential voltage

between VREF+ and VREF- pins

is 400mV

0

0

ADuCM360/ADuCM361

AVDD-0.1

AVDD

V

V

Common Mode Rejection 78

Reference Detect Levels 400 mV

EXCITATION CURRENT SOURCES

Output Current Available from each current

source – 10/50/200uA nominal

Initial Tolerance at 25°C Iout >= 50uA ±5 %

Drift1 Using internal reference resistor 200 ppm/°C

resistor between IREF pin and

AGND. Resistor must have a drift

spec of 5ppm/°C

Initial Current Matching at 25°C1 Matching between both current

sources

Drift Matching1 50 ppm/°C

Load Regulation (AVDD) 1 AVDD = 3.3 V 0.2 %/V

Output Compliance1 10uA to 210uA Iout AGND − 30 mV AVDD − 0.85 V V

Iout >210uA AGND − 30 mV AVDD − 1.1 V V

DAC CHANNEL SPECIFICATIONS RL = 5 kΩ, CL = 100 pF

Voltage Range Internal reference 0 V

External reference 0 1.8 V

DC Specifications10

Resolution 12 Bits

Relative Accuracy ±3 LSB

Differential Nonlinearity Guaranteed monotonic ±0.5 ±1 LSB

Offset Error 1.2 V internal reference ±2 ±15 mV

Gain Error

NPN Mode

Resolution

Relative Accuracy

Differential Nonlinearity

Offset Error

Gain Error

Output Current Range

DAC AC CHARACTERISTICS

Voltage Output Settling Time 10 µs

Digital-to-Analog Glitch Energy 1 LSB change at major carry

1

V

range (reference = 1.2 V)

REF

(where maximum number of

bits simultaneously change in

the DAC0DAT register)

10 50 1000 μA

±0.5 %

12

0.008

±20 nV-sec

±1.0

±0.5

±0.35

±0.75

dB

REF

±1 %

23.6

V

Bits

LSB

LSB

mA

mA

mA

Rev. Pr R| Page 7 of 21

Loading...

Loading...