Analog Devices ADuC847 pra Datasheet

MicroConverter, 10-channel 24-Bit ADC

A

d

a

with Embedded 62kB FLASH MCU

Preliminary Technical Data ADuC847

FEATURES

High Resolution Sigma-Delta ADC

24-Bit Resolution

Up to 10 ADC input channels

24-Bit No Missing Codes

20-Bit rms (17.4 Bit p-p) Effective Resolution @ 60 Hz

Offset Drift 10 nV/°C, Gain Drift 0.5 ppm/°C

Memory

62 Kbytes On-Chip Flash/EE Program Memory 4 Kbytes On-Chip Flash/EE Data Memory Flash/EE, 100 Year Retention, 100 Kcycles Endurance 3 Levels of Flash/EE Program Memory Security In-Circuit Serial Download (No External Hardware) High Speed User Download (5 Seconds) 2304 Bytes On-Chip Data RAM

8051-Based Core

8051 Compatible Instruction Set

High Performance Single Cycle Core

32 kHz External Crystal

On-Chip Programmable PLL (12.58 MHz Max)

3 x 16-Bit Timer/Counter

26 Programmable I/O Lines

11 Interrupt Sources, Two Priority Levels

Dual Data Pointer, Extended 11-Bit Stack Pointer

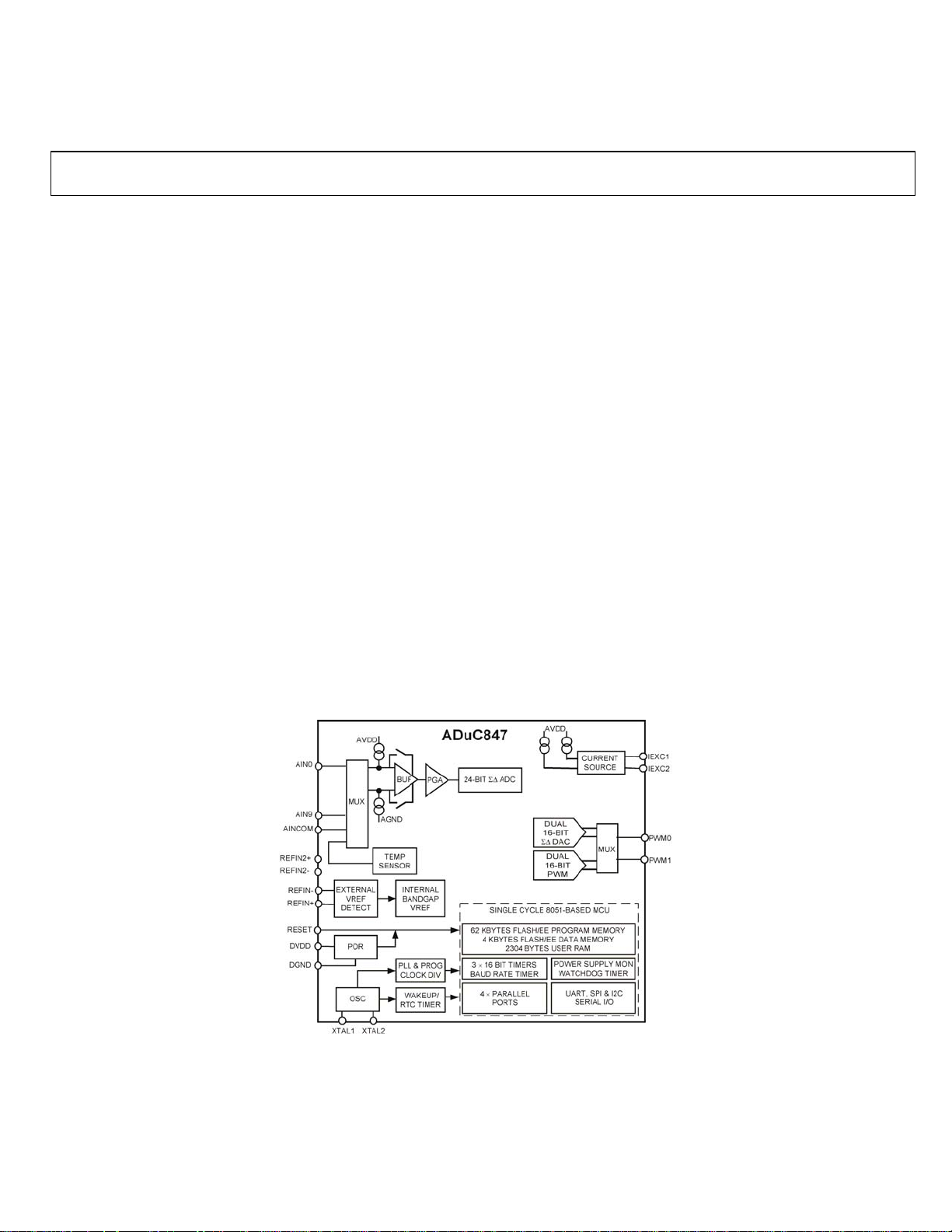

FUNCTIONAL BLOCK DIAGRAM

(Chop enabled)

On-Chip Peripherals

Internal Power on Reset Circuit

Dual 16-Bit S-D DACs/PWMs

On-Chip Temperature Sensor

Dual Excitation Current Sources

Time Interval Counter (Wakeup/RTC Timer)

UART, SPI®, and I2C® Serial I/O

High Speed Baud Rate Generator (incl 115,200)

Watchdog Timer (WDT)

Power Supply Monitor (PSM)

Power

Normal: 2.3mA Max @ 3.6 V (Core CLK = 1.57 MHz)

Power-Down: 20mA Max with Wakeup Timer Running

Specified for 3 V and 5 V Operation

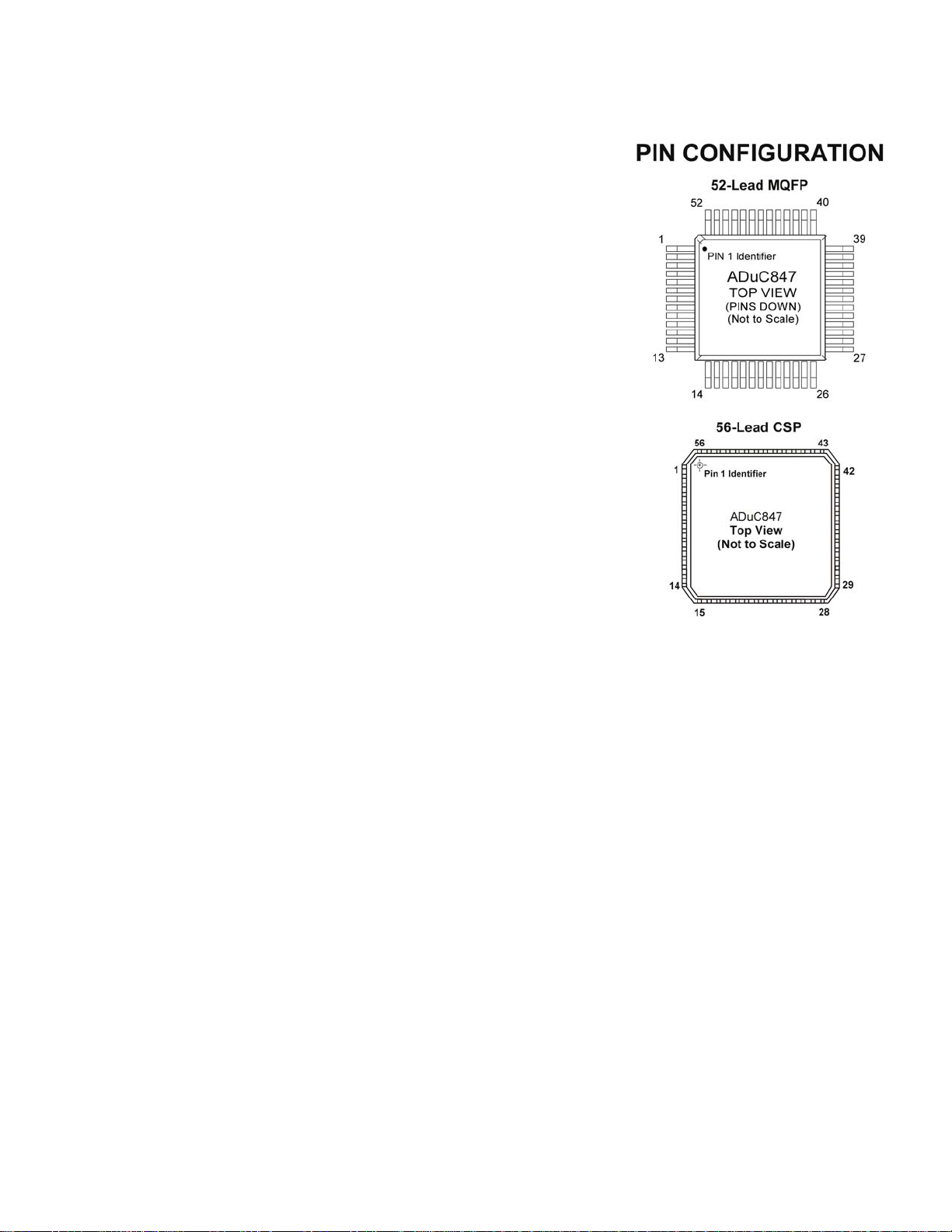

Package and Temperature Range

52-Lead MQFP (14 mm x 14 mm), –40°C to +125°C

56-Lead CSP (8 mm x 8 mm), –40°C to +85°C

APPLICATIONS

Multi channel Sensor monitoring

Industrial/Environmental Instrumentation

WeighScales

Portable Instrumentation, Battery Powered Systems

4-20mA Transmitters

Data Logging

Precision System Monitoring

REV. PrA 05/03

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or

other rights of third parties that may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices. Trademarks and registered

trademarks are the property of their respective companies.

Purchase of licensed I2C components of Analog Devices or one of its sublicensed

Associated Companies conveys a license for the purchaser under the Philips I

Patent Rights to use these components in an I

conforms to the I

2

C Standard Specification as defined by Philips

2

C system, provided that the system

2

C

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc.

ll rights reserve

Preliminary Technical Data ADuC847

SPECIFICATIONS

(AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.85 V to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V, REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768

kHz Crystal; all specifications T

PARAMETER MIN TYP MAX UNITS CONDITION

ADC (CHOP ENABLED) 1

Conversion Rate (Chop enabled) 5.4 19.79 105 Hz CHOP = 0 (ADCMODE.3)

(Chop disabled) 16.06 59.36 1365 Hz CHOP = 1 (ADCMODE.3)

No Missing Codes2 24 Bits 19.79Hz/ 59.36Hz Update Rate

Resolution (Chop enabled) 13.5 Bits Pk-Pk Range = ± 20mV, 20Hz Update Rate

(Chop disabled) 13 Bits Pk-Pk Range = ± 20mV, 59Hz Update Rate

(Chop enabled) 18.5 Bits Pk-Pk Range = ± 2.56V, 20Hz Update Rate

(Chop disabled) 17.4 Bits Pk-Pk Range = ± 2.56V, 59.4Hz Update Rate

Output Noise See Tables IV, V VI & VII in

Integral Non Linearity ±2 ± 15 ppm of FSR 1 LSB16

Offset Error3

See tables VI & VII

Offset Error Drift vs. Temp (Chop enabled) ± 10 nV/°C Chop Enabled

Offset Error Drift vs. Temp (Chop disabled) ±200 nV/°C Chop Disabled

Full-Scale Error4

Gain Error Drift vs. Temp 5

PARAMETER MIN TYP MAX UNITS CONDITION

ADC ANALOG INPUTS

Differential Input Voltage Ranges

Bipolar Mode (ADC0CON.5 = 0)

Unipolar Mode (ADC0CON.5 = 1) 0 Æ 1.024 x Vref/GAIN V V

ADC Range Matching ± 2

Power Supply Rejection 80 dBs AIN=1V, Range=± 2.56V

113 dBs AIN=7.8mV, Range=± 20mV

Common Mode DC Rejection

On AIN 95 dBs @DC, AIN=7.8mV, Range=± 20mV

On AIN 113 dBs @DC, AIN=1V, Range=± 2.56V

Common Mode 50/60Hz Rejection 20Hz Update Rate

On AIN 95 dBs 50/60Hz ± 1Hz, AIN=7.8mV, Range=± 20mV

On AIN 90 dBs 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V

59Hz Update Rate

On AIN 95 dBs 50/60Hz ± 1Hz, AIN=7.8mV, Range=± 20mV

On AIN 90 dBs 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V

Normal Mode 50/60 Hz Rejection

On AIN 60 dBs 50/60Hz ± 1Hz, 20Hz/59Hz Update Rate

Analog Input Current2

± 5 nA T

Analog Input Current Drift ± 5 pA/°C T

± 15 pA/°C T

AINCOM Input Current ± 125 nA/V ± 2.56V Range

AINCOM Input Current Drift ± 2 pA/V/°C

Absolute AIN Voltage Limits2

Absolute AINCOM Voltage Limits A

, to T

MIN

unless otherwise noted.). Buffer On unless otherwise noted.

MAX

± 0.5 ppm/°C

9, 10

A

GND

GND

Output Noise varies with selected Update Rates

ADC Description

± 3

µV

± 10

µV

± 1.024 x V

REF

/GAIN

V

µV

± 1 nA T

+ 0.1 AV

DD

– 0.1

V Ain0-Ain9 with Buffer ON

+ 0.03 AV

– 0.03 V Buffer bypassed (ADC0CON1.6=0,

DD

and Gain Range

CHOP Enabled

Offset Error is in the order of the noise for the

programmed gain and update rate following a

calibration for CHOP disabled.

V

= REFIN(+) - REFIN(-) (or Int 1.25V Ref)

REF

GAIN = 1 to 128

= REFIN(+) - REFIN(-) GAIN=1 to 128

REF

AIN=18mV

= 85°C

MAX

= 125°C

MAX

= 85°C

MAX

= 125°C

MAX

(ADC0CON1.6 = 0 & ADC0CON1.7 = 0)

ADC0CON1.7=1)

1

REV. PrA 05/03 2

Preliminary Technical Data ADuC847

EXTERNAL REFERENCE INPUTS

REFIN(+) to REFIN(–) Range2

Average Reference Input Current 1

Average Reference Input Current Drift +/- 0.1 nA/V/°C

‘NO Ext. REF’ Trigger Voltage 0.3 0.65 V NOXREF bit active if VREF<0.3V

NOXREF bit Inactive if VREF>0.65

Common Mode DC Rejection 125 dBs @DC, AIN=1V, Range=± 2.56V

Common Mode 50/60Hz Rejection 90 dBs 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V

Normal Mode 50/60 Hz Rejection 60 dBs 50/60Hz ± 1Hz, 20Hz/59.4Hz Update Rate

PARAMETER MIN TYP MAX UNITS CONDITION

ADC SYSTEM CALIBRATION

Full Scale Calibration Limit +1.05 x FS V

Zero Scale Calibration Limit -1.05 x FS V

Input Span 0.8 x FS 2.1 x FS V

INT REFERENCE (CHOP ENABLED)

ADC Reference

Reference Voltage 1.237 1.25 1.2625 V initial tolerance @ 25°C, VDD=5V

Power Supply Rejection 45 dBs

Reference Tempco 100 ppm/°C

TEMPERATURE SENSOR

Accuracy +/- 2 °C

Thermal Impedance 90 °C/W MQFP Package

52 °C/W CSP Package

TRANSDUCER BURNOUT CURRENT SOURCES

AIN+ Current -100 nA AIN+ is the selected positive input (Ain4 or

AIN- Current 100 nA AIN- is the selected negative input (Ain5 or

Initial Tolerance at 25°C +/- 10 %

Drift 0.03 %/°C

EXCITATION CURRENT SOURCES

Output Current -200

Initial Tolerance at 25°C +/-10 %

Drift 200 ppm/°C

Initial Current Matching at 25°C +/-1 % Matching between both Current Sources

Drift Matching 20 ppm/°C

Line Regulation (AVDD) 1

Load Regulation 0.1 V

Output Compliance A

PARAMETER MIN TYP MAX UNITS CONDITION

POWER SUPPLY MONITOR (PSM)

AVDD Trip Point Selection Range 2.63 4.63 V Four Trip Points selectable in this range

AVDD Trip Point Accuracy +/- 3.0 % T

AVDD Trip Point Accuracy +/- 3.0 % T

DVDD Trip Point Selection Range 2.63 4.63 V Four Trip Points selectable in this range

DVDD Trip Point Accuracy +/- 3.0 % T

DVDD Trip Point Accuracy +/- 3.0 % T

1 2.5 AV

V

DD

µA/V

ADC Enabled

Ain6 only) to the ADC

Ain7 only) to the ADC

µA

µA/V

AVDD-0.6 V

GND

Available from each Current Source

AVDD=5V +/- 5%

MAX

MAX

MAX

MAX

= 85°C

= 125°C

= 85°C

= 125°C

REV. PrA 05/03 -3-

Preliminary Technical Data ADuC847

CRYSTAL OSCILLATOR (XTAL 1AND XTAL2)

Logic Inputs, XTAL1 Only2

V

, Input Low Voltage 0.8 V DVDD = 5V

INL

0.4 V DVDD = 3V

V

, Input Low Voltage 3.5 V DVDD = 5V

INH

2.5 V DVDD = 3V

XTAL1 Input Capacitance 18 pF

XTAL2 Output Capacitance 18 pF

LOGIC INPUTS

All Inputs except SCLOCK, RESET

and XTAL1

V

2

, Input Low Voltage 0.8 V DVDD = 5V

INL

0.4 V DVDD = 3V

V

SCLOCK and RESET Only

(Schmidt Triggered Inputs)

, Input Low Voltage 2.0 V

INH

2

VT+ 1.3 3.0 V DVDD = 5V

0.95 2.5 V DVDD = 3V

VT- 0.8 1.4 V DVDD = 5V

0.4 1.1 V DVDD = 3V

VT+ - VT- 0.3 0.85 V DVDD = 5V or 3V

Input Currents 2.0 V

Port 0, P1.0ÆP1.7, EA

SCLOCK, MOSI,MISO SS13

+/-10

RESET +/-10

35 105

Port 2, Port 3 +/-10

-180 -660

-20 -75

Input Capacitance 10 pF All Digital Inputs

LOGIC OUTPUTS

All Digital Outputs except XTAL22

VOH, Output High Voltage 2.4 V

2.4 V

VOL, Output Low Voltage14 0.8 V I

0.8 V I

0.8 V I

Floating State Leakage Current +/-10

Floating State Output Capacitance 10 pF

PARAMETER MIN TYP MAX UNITS CONDITION

START UP TIME

At Power On 300 ms

After External RESET in Normal Mode 3 ms

After WDT RESET in Normal Mode 3 ms Controlled via WDCON SFR

From Idle Mode 10 us

From Power-Down Mode

Oscillator Running PLLCON.7 = 0

Wakeup with INT0 Interrupt 20 us

Wakeup with SPI Interrupt 20 us

Wakeup with TIC Interrupt 20 us

Wakeup with External RESET 3 us

Oscillator Powered Down PLLCON.7 = 1

Wakeup with INT0 Interrupt 20 us

Wakeup with SPI Interrupt 20 us

Wakeup with External RESET 5 ms

+/- 10

-10 -40

µA

µA

µA

µA

µA

µA

µA

µA

V

= 0V or VDD

IN

V

= 0V, DVDD=5V, Internal Pullup

IN

VIN = DVDD, DVDD=5V

VIN = 0V, DVDD=5V

VIN = DVDD, DVDD=5V, Internal Pull-Down

VIN = DVDD, DVDD=5V

VIN = 2V, DVDD=5V

VIN = 0.45V, DVDD=5V

DV

DD

DV

DD

= 8mA, SCLOCK, MOSI/SDATA

SINK

= 10mA, P1.0, P1.1

SINK

= 1.6mA, All Other Outputs

SINK

µA

= 5V, I

= 3V, I

SOURCE

SOURCE

= 80 µA

= 20 µA

REV. PrA 05/03 4

Preliminary Technical Data ADuC847

FLAH/EE MEMORY RELIABILITY CHARACTERISTICS

Endurance16 100,000 700,000 Cycles

Data Retention17 100 Years

POWER REQUIREMENTS

Power Supply Voltages

AVDD 3V Nominal 2.85 3.6 V

AVDD 5V Nominal 4.75 5.25 V

DVDD 3V Nominal 2.85 3.6 V

DVDD 5V Nominal 4.75 5.25 V

5V POWER CONSUMPTION

Normal Mode

18, 19

DVDD Current 4 mA core clock = 1.57MHz

13 16 mA core clock = 12.58MHz

AVDD Current 180

Power-Down Mode

18, 19

DVDD Current 53

100

DVDD Current 30

80

AVDD Current 1

3

Typical Additional Peripheral Currents (AIDD and D IDD)

Primary ADC 1 mA

Auxiliary ADC 0.5 mA

Power Supply Monitor 50

DAC 150

Dual Excitation Current Sources 400

3V POWER CONSUMPTION

Normal Mode

18, 19

DVDD Current 2.3 mA core clock = 1.57MHz

8 10 mA core clock = 12.58MHz

AVDD Current 180

Power-Down Mode

18, 19

DVDD Current 20

40

DVDD Current 10

80

AVDD Current 1

3

NOTES

1 Temperature Range for ADuC847BS (MQFP package) is –40°C to +125°C.

Temperature Range for ADuC847BCP (CSP package) is –40°C to +85°C.

2 These numbers are not production tested but are guaranteed by design and/or characterization data on production release.

3 System Zero-Scale Calibration can remove this error.

4 The ADC is factory calibrated at 25°C with AVDD = DVDD = 5 V yielding this full-scale error of 10 µV. If user power supply or temperature conditions are

significantly different from these, an Internal Full-Scale Calibration will restore this error to 10 µV. A system zero-scale and full-scale calibration will remove

this error altogether.

5 Gain Error Drift is a span drift. To calculate Full-Scale Error Drift, add the Offset Error Drift to the Gain Error Drift times the full-scale input.

6 In general terms, the bipolar input voltage range to the ADC is given by RangeADC = ±(VREF 2

VREF = REFIN(+) to REFIN(–) voltage and VREF = 1.25 V when internal ADC VREF is selected.

RN = decimal equivalent of RN2, RN1, RN0

e.g., VREF = 2.5 V and RN2, RN1, RN0 = 1, 1, 0 the RangeADC = ±1.28 V, In unipolar mode, the effective range is 0 V to 1.28 V in our example.

7 1.25 V is used as the reference voltage to the ADC when internal VREF is selected via the XREF0 and XREF 1 bits in ADC0CON2.

8 The ADuC847BCP (CSP Package) has been qualified and tested with the base of the CSP Package floating.

9 Pins configured in SPI Mode, pins configured as digital inputs during this test.

10 Pins configured in I

11 Flash/EE Memory Reliability Characteristics apply to both the Flash/EE program memory and Flash/EE data memory.

2

C Mode only.

REV. PrA 05/03 -5-

4.75V < DVDD <5.25V, AVDD= 5.25V

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

T

= 85°C; Osc ON;TIC ON

MAX

T

= 125°C; Osc ON; TIC ON

MAX

T

= 85°C; Osc OFF

MAX

T

= 125°C; Osc OFF

MAX

T

= 85°C; Osc ON or OFF

MAX

T

= 125°C; Osc ON or OFF

MAX

4.75V < DVDD <5.25V, AVDD= 5.25V

µA

µA

µA

µA

µA

µA

µA

T

MAX

T

MAX

Osc OFF

T

MAX

T

MAX

T

MAX

RN

)/125, where:

= 85°C; Osc ON;TIC ON

= 125°C; Osc ON; TIC ON

= 125°C; Osc OFF

= 85°C; Osc ON or OFF

= 125°C; Osc ON or OFF

Preliminary Technical Data ADuC847

12 Endurance is qualified to 100 Kcycles as per JEDEC Std. 22 method A117 and measured at –40 °C, +25°C, +85°C, and +125°C. Typical endurance at 25°C is

700 Kcycles.

13 Retention lifetime equivalent at junction temperature (TJ) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of

0.6eV will derate with junction temperature.

14 Power Supply current consumption is measured in Normal, Idle, and Power-Down Modes under the following conditions:

Normal Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, Core Executing internal software loop.

Idle Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, PCON.0 = 1, Core Execution suspended in idle mode.

Power-Down Mode: Reset = 0.4 V, All P0 pins and P1.2–P1.7 Pins = 0.4 V, All other digital I/O pins are open circuit, Core Clk changed via CD bits in

PLLCON, PCON.1 = 1, Core Execution suspended in power-down mode, OSC turned ON or OFF via OSC_PD bit (PLLCON.7) in PLLCON SFR.

15 DVDD power supply current will increase typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

Specifications subject to change without notice

REV. PrA 05/03 6

Preliminary Technical Data ADuC847

ABSOLUTE MAXIMUM RATINGS1

(TA = 25°C unless otherwise noted)

AVDD to AGND –0.3 V to +7 V

AVDD to DGND –0.3 V to +7 V

DVDD to AGND –0.3 V to +7 V

DVDD to DGND –0.3 V to +7 V

AGND to DGND

AVDD to DVDD –2 V to +5 V

Analog Input Voltage to AGND

Reference Input Voltage to AGND –0.3 V to AVDD +0.3 V

AIN/REFIN Current (Indefinite) 30 mA

Digital Input Voltage to DGND –0.3 V to DVDD +0.3 V

Digital Output Voltage to DGND –0.3 V to DVDD +0.3 V

Operating Temperature Range –40°C to +125°C

Storage Temperature Range –65°C to +150°C

Junction Temperature 150°C

qJA Thermal Impedance 90°C/W

Lead Temperature, Soldering Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

1

Stresses above those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

2

AGND and DGND are shorted internally on the ADuC847.

3

Applies to P1.0 to P1.7 pins operating in analog or digital input modes

2

–0.3 V to +0.3 V

3

–0.3 V to AV

DD

+0.3 V

.

REV. PrA 05/03 -7-

Preliminary Technical Data ADuC847

ORDERING GUIDE

MODEL Temperature Range Package Description Package Option

ADuC847BS62-5

ADuC847BS62-3

ADuC847BCP62-5

ADuC847BCP62-3

ADuC847BCP32-5

ADuC847BCP32-3

ADuC847BCP8-5

ADuC847BCP8-3

EVAL-ADuC847QS

EVAL-ADuC847QSP

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V

readily accumulate on the human body and test equipment and can discharge without

detection. Although the ADuC847 features proprietary ESD protection circuitry,

permanent damage may occur on devices subjected to high-energy electrostatic

discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

-40 Æ +125oC 52-Lead Plastic Quad Flatpack, 62kB, 5v S-52

-40 Æ +125oC 52-Lead Plastic Quad Flatpack, 62kB, 3v S-52

-40 Æ +85

-40 Æ +85oC 56-Lead Chip Scale Package, 62kB, 3v CP-56

-40 Æ +85oC 56-Lead Chip Scale Package, 32kB, 5v CP-56

-40 Æ +85oC 56-Lead Chip Scale Package, 32kB, 3v CP-56

-40 Æ +85

-40 Æ +85

o

C 56-Lead Chip Scale Package, 62kB, 5v CP-56

o

C 56-Lead Chip Scale Package, 8kB, 5v CP-56

o

C 56-Lead Chip Scale Package, 8kB, 3v CP-56

QuickStartTM Development System

QuickStart PLUS Development System

REV. PrA 05/03 8

Preliminary Technical Data ADuC847

PIN FUNCTION DESCRIPTIONS

Pin No:

52-MQFP

1 56 P1.0/AIN0 I By power on default P1.0/AIN0 is configured as the AIN0 Analog Input.

2 1 P1.1/AIN1 I By power on default P1.1/AIN1 is configured as the AIN1 Analog Input.

3 2 P1.2/AIN2/REFIN2+ I By power on default P1.2/AIN2 is configured as the AIN2 Analog Input.

4 3 P1.3/AIN3/REFIN2- I By power on default P1.3/AIN3 is configured as the AIN3 Analog Input.

5 4 AVDD S Analog Supply Voltage

6 5 AGND S Analog Ground.

--- 6 AGND S A second Analog ground is provided with the CSP version only*

7 7 REFIN- I External Differential Reference Input, negative terminal

8 8 REFIN+ I External Differential Reference Input, positive terminal

9 9 P1.4/AIN4 I By power on default P1.4/AIN4 is configured as the AIN4 Analog Input.

10 10 P1.5/AIN5 I By power on default P1.5/AIN5 is configured as the AIN5 Analog Input.

11 11 P1.6/AIN6/IEXC1 I/O By power on default P1.6/AIN6 is configured as the AIN6 Analog Input.

*Note: This pin is provided on the CSP version only.

Pin No:

56-CSP

Pin

Mnemonic

Type* Description

AIN0 can be used as a pseudo differential input when used with AINCOM or

as the positive input of a fully differential pair when used with AIN2.

P1.0 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally.

AIN1 can be used as a pseudo differential input when used with AINCOM or

as the negative input of a fully differential pair when used with AIN0.

P1.1 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally.

AIN2 can be used as a pseudo differential input when used with AINCOM or

as the positive input of a fully differential pair when used with AIN3.

P1.2 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally. This pin also functions as a second external

differential reference input, positive terminal.

AIN3 can be used as a pseudo differential input when used with AINCOM or

as the negative input of a fully differential pair when used with AIN2.

P1.3 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally. This pin also functions as a second external

differential reference input, negative terminal.

AIN4 can be used as a pseudo differential input when used with AINCOM or

as the positive input of a fully differential pair when used with AIN5.

P1.0 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally.

AIN5 can be used as a pseudo differential input when used with AINCOM or

as the negative input of a fully differential pair when used with AIN4.

P1.1 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally.

AIN6 can be used as a pseudo differential input when used with AINCOM or

as the positive input of a fully differential pair when used with AIN7.

One or Both current sources can also be configured at this pin.

P1.0 has no digital output driver. It can function as a digital input for which

‘0’ must be written to the port bit. As a digital input, this pin must be driven

high or low externally.

REV. PrA 05/03 -9-

Loading...

Loading...