PRELIMINARY TECHNICAL DATA

查询ADUC844供应商查询ADUC844供应商

a

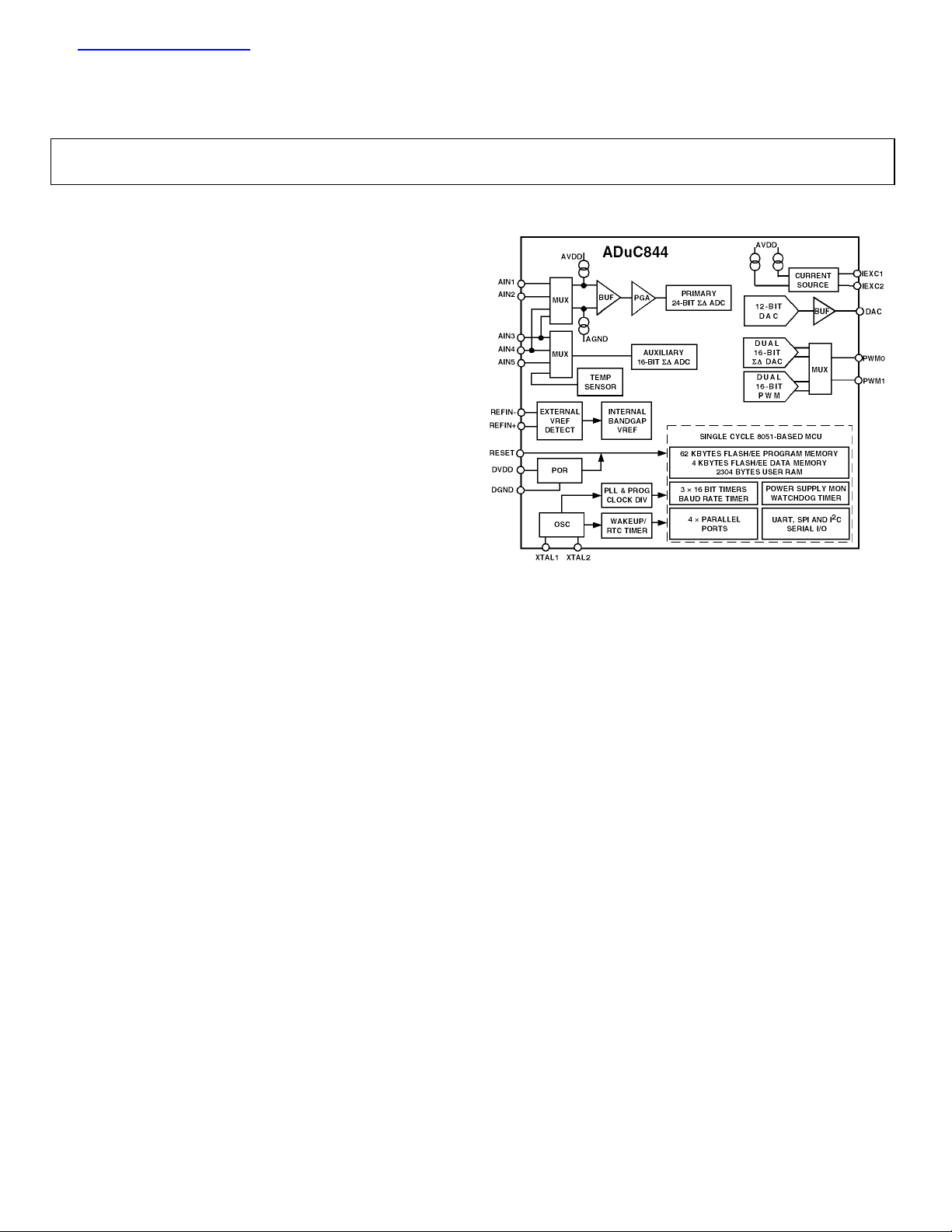

MicroConverter, Dual 16-Bit/24-Bit ADCs

with Embedded 62kB FLASH MCU

Preliminary Technical Data ADuC844

FEATURES

High Resolution Sigma-Delta ADCs

Two Independent ADCs (24-Bit and 16-Bit Resolution)

24-Bit No Missing Codes, Primary ADC

21-Bit rms (18.5 Bit p-p) Effective Resolution @ 20 Hz

Offset Drift 10 nV/°C, Gain Drift 0.5 ppm/°C

Memory

62 Kbytes On-Chip Flash/EE Program Memory

4 Kbytes On-Chip Flash/EE Data Memory

Flash/EE, 100 Year Retention, 100 Kcycles Endurance

3 Levels of Flash/EE Program Memory Security

In-Circuit Serial Download (No External Hardware)

High Speed User Download (5 Seconds)

2304 Bytes On-Chip Data RAM

8051-Based Core

8051 Compatible Instruction Set

High Performance Single Cycle Core

32 kHz External Crystal

On-Chip Programmable PLL (12.58 MHz Max)

3 ×× 16-Bit Timer/Counter

26 Programmable I/O Lines

11 Interrupt Sources, Two Priority Levels

Dual Data Pointer, Extended 11-Bit Stack Pointer

On-Chip Peripherals

Internal Power on Reset Circuit

12-Bit Voltage Output DAC

Dual 16-Bit S-D DACs/PWMs

On-Chip Temperature Sensor

Dual Excitation Current Sources

Time Interval Counter (Wakeup/RTC Timer)

UART, SPI®, and I2C® Serial I/O

High Speed Baud Rate Generator (incl 115,200)

Watchdog Timer (WDT)

Power Supply Monitor (PSM)

Power

Normal: 2.3mA Max @ 3.6 V (Core CLK = 1.57 MHz)

Power-Down: 20µµA Max with Wakeup Timer Running

Specified for 3 V and 5 V Operation

Package and Temperature Range

52-Lead MQFP (14 mm ×× 14 mm), –40°C to +125°C

56-Lead CSP (8 mm ×× 8 mm), –40°C to +85°C

APPLICATIONS

Intelligent Sensors

WeighScales

Portable Instrumentation, Battery Powered Systems

4-20mA Transmitters

Data Logging

Precision System Monitoring

REV. PrB

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

No license is granted by implication or otherwise under any patent or patent rights

of Analog Devices. Trademarks and registered trademarks are the property of their

respective companies.

GENERAL DESCRIPTION

The ADuC844 is a complete smart transducer front end, integrating

two high resolution sigma-delta ADCs, an 8-bit MCU, and

program/data Flash/EE memory on a single chip.

The two independent ADCs (primary and auxiliary) include a

temperature sensor and a PGA (allowing direct measurement of low

level signals). The ADCs with on-chip digital filtering and

programmable output data rates are intended for the measurement of

wide dynamic range, low frequency signals, such as those in weigh

scale, strain-gage, pressure transducer, or temperature measurement

applications.

The device operates from a 32 kHz crystal with an on-chip PLL

generating a high frequency clock of 12.58 MHz. This clock is routed

through a programmable clock divider from which the MCU core

clock operating frequency is generated. The microcontroller core is an

optimized single cycle 8052 offering up to 12.58MIPs performance

while maintaining the 8051 instruction set compatibility.

62 Kbytes of nonvolatile Flash/EE program memory, 4 Kbytes of

nonvolatile Flash/EE data memory, and 2304 bytes of data RAM are

provided on-chip. The program memory can be configured as data

memory to give up to 60 Kbytes of NV data memory in data logging

applications.

On-chip factory firmware supports in-circuit serial download and

debug modes (via UART), as well as single-pin emulation mode via

the EA pin. The ADuC844 is supported by a QuickStart™

development system featuring low cost software and hardware

development tools.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

FUNCTIONAL BLOCK DIAGRAM

1

PRELIMINARY TECHNICAL DATA

(AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V,

XTAL1/XTAL2 = 32.768 kHz

ADuC844 SPECIFICATIONS

PARAMETER MIN TYP MAX UNITS CONDITION

REFIN(+) = 2.5 V, REFIN(–) = AGND; AGND = DGND = 0 V;

Crystal; all specifications T

MIN

, to T

unless otherwise noted.).

MAX

PRIMARY ADC

Conversion Rate 5.35 19.79 105 Hz On Both Channels

No Missing Codes2 24 Bits 19.79Hz Update Rate

Resolution 13.5 Bits Pk-Pk Range = ± 20mV, 20Hz Update Rate

18.5 Bits Pk-Pk Range = ± 2.56V, 20Hz Update Rate

Output Noise See Tables X and XI in ADC

Description

Output Noise varies with selected Update Rates

and Gain Range

Integral Non Linearity ± 15 ppm of FSR 1 LSB16

Offset Error3 ± 3

µV

Offset Error Drift (vs. Temp) ± 10 nV/°C

Full-Scale Error4 ± 10

µV

Gain Error Drift5 (vs. Temp) ± 0.5 ppm/°C

ADC Range Matching ± 2

µV

AIN=18mV

Power Supply Rejection 80 dBs AIN=1V, Range=± 2.56V

113 dBs AIN=7.8mV, Range=± 20mV

Common Mode DC Rejection

On AIN 95 dBs @DC, AIN=7.8mV, Range=± 20mV

On AIN 113 dBs @DC, AIN=1V, Range=± 2.56V

Common Mode 50/60Hz Rejection 20 Hz Update Rate

On AIN 95 dBs 50/60Hz ± 1Hz, AIN=7.8mV, Range=± 20mV

On AIN 90 dBs 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V

Normal Mode 50/60 Hz Rejection

On AIN 60 dBs 50/60Hz ± 1Hz, 20 Hz Update Rate

PRIMARY ADC ANALOG INPUTS

Differential Input Voltage Ranges

9,10

Bipolar Mode (ADC0CON.5 = 0)

± 1.024 x V

REF

/GAIN

V

V

= REFIN(+) - REFIN(-) (or Int 1.25V Ref)

REF

GAIN = 1 to 128

Unipolar Mode (ADC0CON.5 = 1) 0 à 1.024 x REFIN/GAIN V V

= REFIN(+) - REFIN(-)

REF

GAIN=1 to 128

Analog Input Current2 ± 1 nA T

± 5 nA T

Analog Input Current Drift ± 5 pA/°C T

± 15 pA/°C T

Absolute AIN Voltage Limits2 A

EXTERNAL REFERENCE INPUTS

+ 0.1 AV

GND

– 0.1 V

DD

MAX

MAX

MAX

MAX

= 85°C

= 125°C

= 85°C

= 125°C

REFIN(+) to REFIN(–) Range2 1 2.5 AVDD V

Average Reference Input Current +/- 1

µA/V

Both ADCs Enabled

Average Reference Input Current Drift +/- 0.01 nA/V/°C

‘NO Ext. REF’ Trigger Voltage 0.3 0.65 V NOXREF bit active if VREF<0.3V

NOXREF bit Inactive if VREF>0.65

Common Mode DC Rejection 125 dBs @DC, AIN=1V, Range=± 2.56V

Common Mode 50/60Hz Rejection 90 dBs 50/60Hz ± 1Hz, AIN=1V, Range=± 2.56V

Normal Mode 50/60 Hz Rejection 60 dBs 50/60Hz ± 1Hz, 59.4 Hz Update Rate

-2- REV. PrB

ADuC844

PRELIMINARY TECHNICAL DATA

PARAMETER MIN TYP MAX UNITS CONDITION

AUXILIARY ADC

No Missing Codes2 16 Bits 20 Hz Update Rate

Resolution 16 Bits Pk-Pk Range = ± 2.5V, 20Hz Update Rate

Output Noise See Table XII Output Noise varies with selected Update Rates

Integral Non Linearity ± 15 ppm of FSR 1 LSB16

Offset Error3 -2 LSB

Offset Error Drift 1

Fullscale Error4 -2.5 LSBs

Gain Error Drift5 ± 0.5 ppm/°C

Power Supply Rejection 80 dBs AIN=1V, Range=± 2.56V

Normal Mode 50/60 Hz Rejection

On AIN 60 dBs 50/60Hz ± 1Hz, 19.79Hz Update Rate

On REFIN 60 dBs 50/60Hz ± 1Hz, 19.79Hz Update Rate

AUXILIARY ADC ANALOG INPUTS

Differential Input Voltage Ranges

9, 10

(Bipolar Mode – ADC0CON3 = 0)

(Unipolar Mode – ADC0CON3 = 1) 0 à REFIN V REFIN=REFIN(+)-REFIN(-) (or Int 1.25V Ref)

Average Analog Input Current 125 nA/V

Analog Input Current Drift ± 2 pA/V/°C

Absolute AIN Voltage Limits

2, 11

A

ADC SYSTEM CALIBRATION

Full Scale Calibration Limit +1.05 x FS V

Zero Scale Calibration Limit -1.05 x FS V

Input Span 0.8 x FS 2.1 x FS V

DAC

Voltage Range 0 à V

0 à AVDD V DACCON.2 = 1

Resistive Load 10

Capactive Load 100 pF From DAC Output to AGND

Output Impedance 0.5

I

50

SINK

DC Specifications7

Resolution 12

Relative Accuracy ± 3 LSBs

Differential NonLinearity -1 Bit Guaranteed 12-Bit Monotonic

Offset Error ± 50 mV

Gain Error8 ± 1 % AVDD Range

± 1 % V

AC Specifications

2,7

Voltage Output Settling Time 15 us Setling time to 1LSB of final value

Digital to Analog Glitch Energy 10 nVs 1 LSB change at major carry

µV /°C

± REFIN V REFIN=REFIN(+)-REFIN(-) (or Int 1.25V Ref)

GND

- 0.03

A

+ 0.03

VDD

V

V DACCON.2 = 0

REF

kΩ

Ω

µA

From DAC Output to AGND

Range

REF

REV. PrB -3-

1

PRELIMINARY TECHNICAL DATA

is the selected negative input to the primary

ADuC844 SPECIFICATIONS

PARAMETER MIN TYP MAX UNITS CONDITION

INT REFERENCE

ADC Reference

Reference Voltage 1.237 1.25 1.2625 V initial tolerance @ 25°C, VDD=5V

Power Supply Rejection 45 dBs

Reference Tempco 100 ppm/°C

DAC Reference

Reference Voltage 2.475 2.5 1.525 V initial tolerance @ 25°C, VDD=5V

Power Supply Rejection 50 dBs

Reference Tempco ± 100 ppm/°C

TEMPERATURE SENSOR

Accuracy +/- 2 °C

Thermal Impedance 90 °C/W MQFP Package

52 °C/W CSP Package

TRANSDUCER BURNOUT CURRENT SOURCES

AIN+ Current -100 nA AIN+ is the selected positive input to the

AIN- Current 100 nA AIN-

Initial Tolerance at 25°C +/- 10 %

Drift 0.03 %/°C

EXCITATION CURRENT SOURCES

Output Current -200

Initial Tolerance at 25°C +/-10 %

Drift 200 ppm/°C

Initial Current Matching at 25°C +/-1 % Matching between both Current Sources

Drift Matching 20 ppm/°C

Line Regulation (AVDD) 1

Load Regulation 0.1 V

Output Compliance A

POWER SUPPLY MONITOR (PSM)

AVDD Trip Point Selection Range 2.63 4.63 V Four Trip Points selectable in this range

AVDD Trip Point Accuracy +/- 3.0 % T

AVDD Trip Point Accuracy +/- 3.0 % T

DVDD Trip Point Selection Range 2.63 4.63 V Four Trip Points selectable in this range

DVDD Trip Point Accuracy +/- 3.0 % T

DVDD Trip Point Accuracy +/- 3.0 % T

CRYSTAL OSCILLATOR (XTAL 1AND XTAL2)

Logic Inputs, XTAL1 Only2

V

, Input Low Voltage 0.8 V DVDD = 5V

INL

0.4 V DVDD = 3V

V

, Input Low Voltage 3.5 V DVDD = 5V

INH

2.5 V DVDD = 3V

XTAL1 Input Capacitance 18 pF

XTAL2 Output Capacitance 18 pF

AVDD-0.6 V

GND

primary ADC

ADC

µA

µA/V

Available from each Current Source

AVDD=5V +/- 5%

= 85°C

MAX

= 125°C

MAX

= 85°C

MAX

= 125°C

MAX

-4- REV. PrB

PRELIMINARY TECHNICAL DATA

PARAMETER MIN TYP MAX UNITS CONDITION

LOGIC INPUTS

All Inputs except SCLOCK, RESET

and XTAL12

V

, Input Low Voltage 0.8 V DVDD = 5V

INL

0.4 V DVDD = 3V

V

, Input Low Voltage 2.0 V

INH

SCLOCK and RESET Only

(Schmidt Triggered Inputs) 2

VT+ 1.3 3.0 V DVDD = 5V

0.95 2.5 V DVDD = 3V

VT- 0.8 1.4 V DVDD = 5V

0.4 1.1 V DVDD = 3V

VT+ - VT- 0.3 0.85 V DVDD = 5V or 3V

Input Currents 2.0 V

Port 0, P1.2àP1.7, EA

SCLOCK, MOSI,MISO SS13

+/-10

RESET +/-10

35 105

P1.0, P1.1, Port 2, Port 3 +/-10

-180 -660

-20 -75

Input Capacitance 5 pF All Digital Inputs

LOGIC OUTPUTS

All Digital Outputs except XTAL22

VOH, Output High Voltage 2.4 V

2.4 V

VOL, Output Low Voltage14 0.8 V I

0.8 V I

0.8 V I

Floating State Leakage Current +/-10

Floating State Output Capacitance 5 pF

START UP TIME

At Power On 300 ms

After External RESET in Normal Mode 3 ms

After WDT RESET in Normal Mode 3 ms Controlled via WDCON SFR

From Idle Mode 10 us

From Power-Down Mode

Oscillator Running PLLCON.7 = 0

Wakeup with INT0 Interrupt 20 us

Wakeup with SPI Interrupt 20 us

Wakeup with TIC Interrupt 20 us

Wakeup with External RESET 3 us

Oscillator Powered Down PLLCON.7 = 1

Wakeup with INT0 Interrupt 20 us

Wakeup with SPI Interrupt 20 us

Wakeup with External RESET 5 ms

+/- 10

-10 -40

µA

µA

µA

µA

µA

µA

µA

µA

µA

VIN = 0V or VDD

VIN = 0V, DVDD=5V, Internal Pullup

VIN = DVDD, DVDD=5V

VIN = 0V, DVDD=5V

VIN = DVDD, DVDD=5V, Internal Pull-Down

VIN = DVDD, DVDD=5V

VIN = 2V, DVDD=5V

VIN = 0.45V, DVDD=5V

DVDD = 5V, I

DVDD = 3V, I

= 8mA, SCLOCK, MOSI/SDATA

SINK

= 10mA, P1.0, P1.1

SINK

= 1.6mA, All Other Outputs

SINK

SOURCE

SOURCE

= 80 µA

= 20 µA

ADuC844

REV. PrB -5-

1

PRELIMINARY TECHNICAL DATA

ADuC844 SPECIFICATIONS

PARAMETER MIN TYP MAX UNITS CONDITION

FLAH/EE MEMORY RELIABILITY CHARACTERISTICS

Endurance16 100,000 700,000 Cycles

Data Retention17 100

POWER REQUIREMENTS

Power Supply Voltages

AVDD 3V Nominal 2.7 3.6 V

AVDD 5V Nominal 4.75 5.25 V

DVDD 3V Nominal 2.7 3.6 V

DVDD 5V Nominal 4.75 5.25 V

5V POWER CONSUMPTION

Normal Mode

18, 19

DVDD Current 4 mA core clock = 1.57MHz

13 16 mA core clock = 12.58MHz

AVDD Current 180

Power-Down Mode

18, 19

DVDD Current 53

100

DVDD Current 30

80

AVDD Current 1

3

Typical Additional Peripheral Currents (AIDD and D IDD)

Primary ADC 1 mA

Auxiliary ADC 0.5 mA

Power Supply Monitor 50

DAC 150

Dual Excitation Current Sources 400

3V POWER CONSUMPTION

Normal Mode

18, 19

DVDD Current 2.3 mA core clock = 1.57MHz

8 10 mA core clock = 12.58MHz

AVDD Current 180

Power-Down Mode

18, 19

DVDD Current 20

40

DVDD Current 10

80

AVDD Current 1

3

4.75V < DVDD <5.25V, AVDD= 5.25V

4.75V < DVDD <5.25V, AVDD= 5.25V

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

µA

T

= 85°C; Osc ON;TIC ON

MAX

T

= 125°C; Osc ON; TIC ON

MAX

T

= 85°C; Osc OFF

MAX

T

= 125°C; Osc OFF

MAX

T

= 85°C; Osc ON or OFF

MAX

T

= 125°C; Osc ON or OFF

MAX

T

= 85°C; Osc ON;TIC ON

MAX

T

= 125°C; Osc ON; TIC ON

MAX

Osc OFF

T

= 125°C; Osc OFF

MAX

T

= 85°C; Osc ON or OFF

MAX

T

= 125°C; Osc ON or OFF

MAX

-6- REV. PrB

Loading...

Loading...