MicroConverter® Technical Note – uC019

a

DMA To XRAM on the ADuC831/832

Introduction

The on-chip ADC has been designed to run at a maximum conversion

speed of 5 uS (200 kHz sampling rate). When converting at this rate the

ADuC831/ADuC832 micro has 5 uS to read the ADC result and store

the result in memory for further post processing all within 5 uS

otherwise the next ADC sample could be lost. In an interrupt driven

routine the micro would also have to jump to the ADC Interrupt Service

routine which will also increase the time required to store the ADC

results. In applications where the ADuC831/ADuC832 cannot sustain

the interrupt rate, an ADC DMA mode is provided.

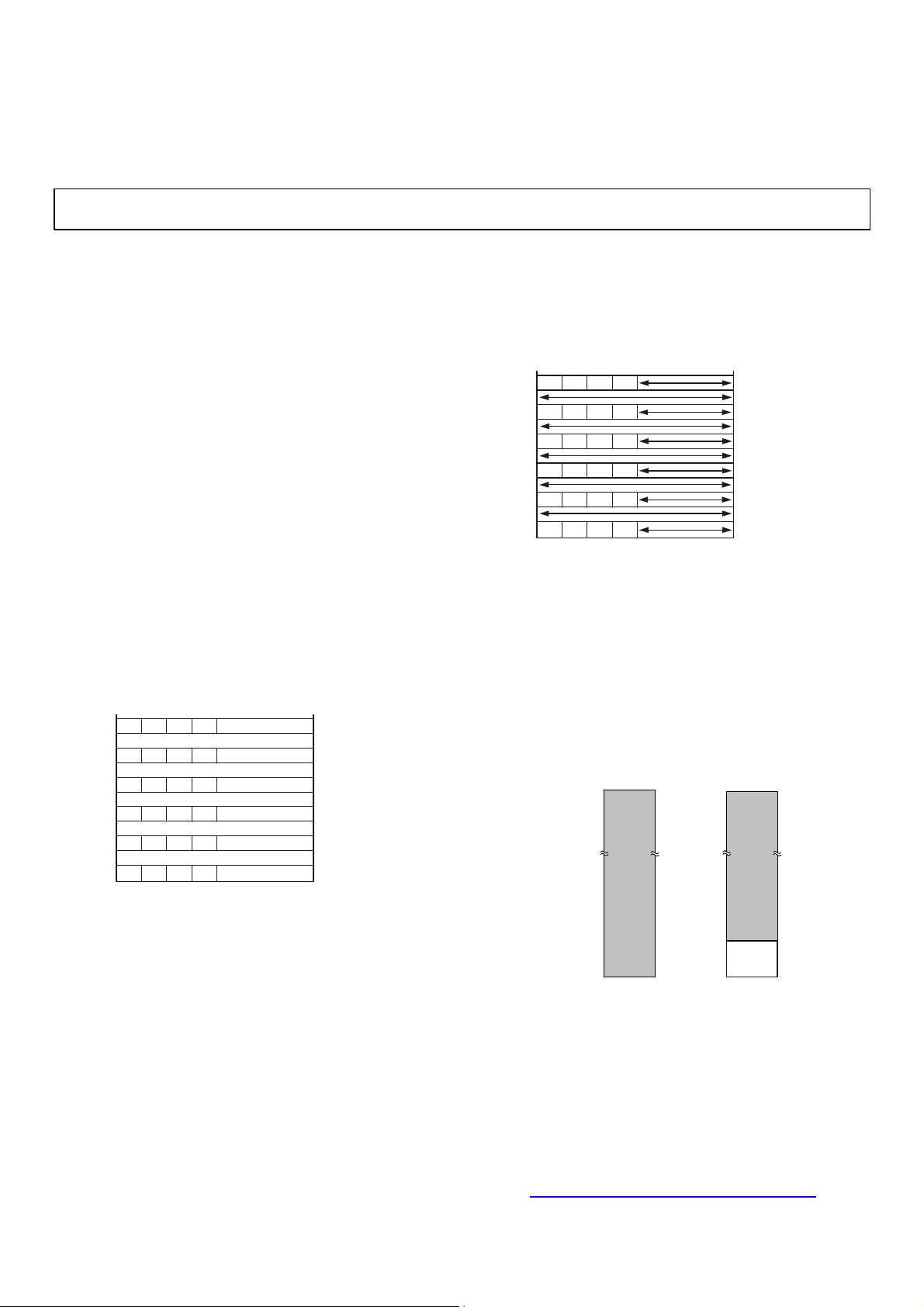

Configuring RAM for DMA

The DMA Address pointer must be set to the start address of where the

ADC Results are to be written. This is done by writing to the DMA

mode Address Pointers, DMAL, DMAH, DMAP. DMAL must be

written first, followed by DMAH and then by DMAP.

The external memory must be preconfigured. This consists of writing

the required ADC channel Ids into the top four bits of every second

memory location in the external SRAM starting at the first address

specified by the DMA address pointer. As the ADC DMA mode

operates independently form the ADuC831/ADuC832 core it is

necessary to provide it with a stop command. This is done by

duplicating the last channel ID to be converted followed by “1111” into

the next channel selection field. A typical preconfiguration of external

memory is as follows.

00000AH

1 1 1 1

0 0 1 1

0 0 1 1

1 0 0 0

STOP COMMAND

REPEAT LAST CHANNEL

FOR A VALID STOP

CONDITION

CONVERT ADC CH#3

CONVERT TEMP SENSOR

When the DMA conversions are completed, the ADC interrupt bit

ADCI is set by hardware and the external SRAM contains the new ADC

conversion results as shown below. It should be noted that no result is

written to the last two memory locations.

00000AH

000000H

1 1 1 1

0 0 1 1

0 0 1 1

1 0 0 0

0 1 0 1

0 0 1 0

Figure 2

STOP COMMAND

NO CONVERSION

RESULT WRITTEN HERE

CONVERSION RESULT

FOR ADC CH#3

CONVERSION RESULT

FOR TEMP SENSOR

CONVERSION RESULT

FOR ADC CH#5

CONVERSION RESULT

FOR ADC CH#2

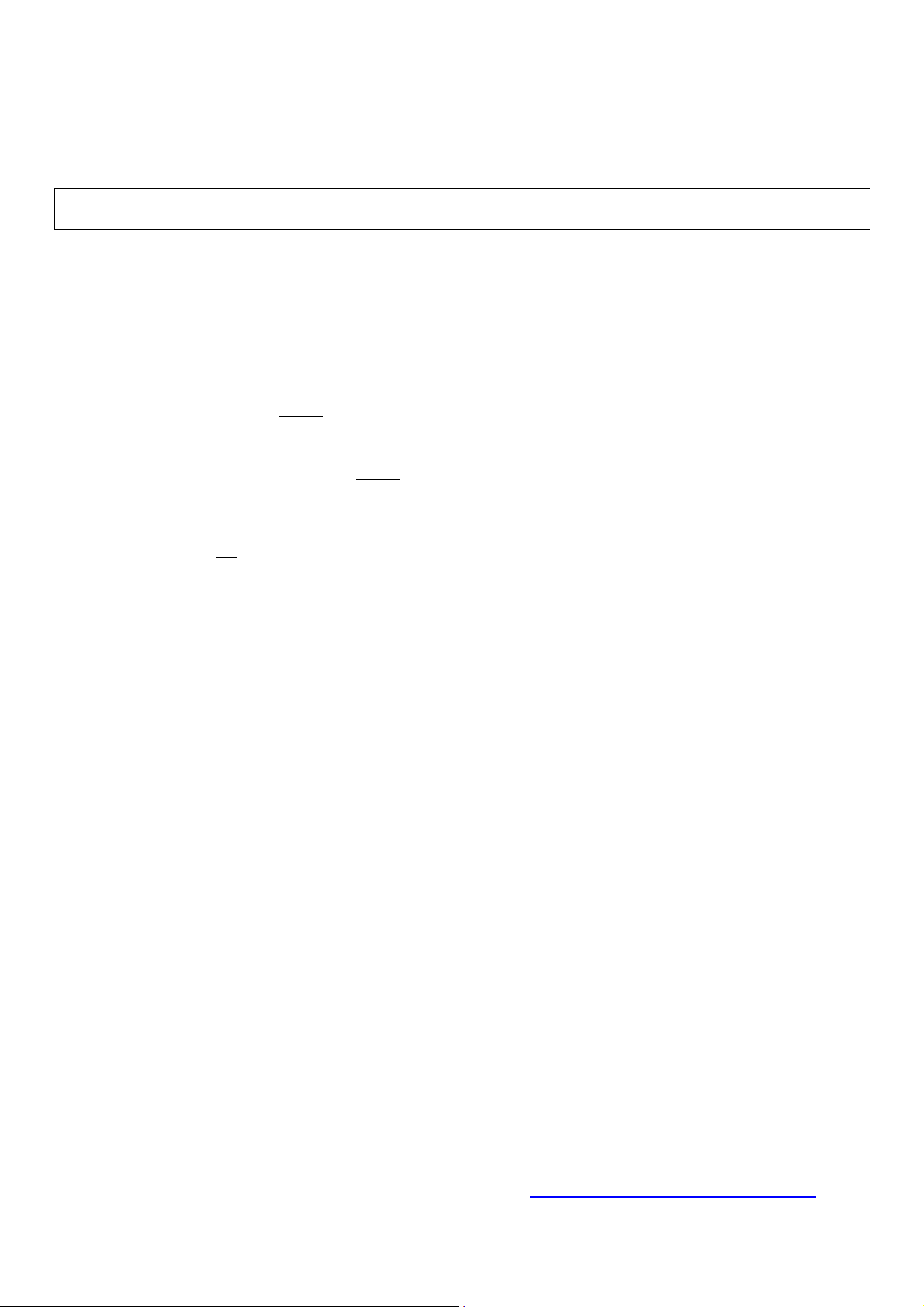

Using Internal and/or External XRAM

The CFG83x.0 bit determines whether or not the internal XRAM is

enabled. This memory maps in as shown in figure 3.

If the internal XRAM is enabled the user can use both it and the

external XRAM for DMA. The RAM is set up as above and the DMA

results automatically switch from the internal XRAM to external

XRAM.

If the internal XRAM is disabled, DMA can only be used to send results

to the external XRAM.

FFFFFFH

FFFFFFH

0 1 0 1

000000H

0 0 1 0

Figure 1

DMA Initiation

The DMA is initiated by writing to the ADC SFRs in the following

sequence.

a. ADCCON2 is written to enable the DMA mode, i.e

MOV ADCCON2, #40H ; DMA Mode enabled

b. ADCCON1 is written to configure the conversion time and

power up of the ADC. It can also enable Timer 2 driven

conversions or External Triggered conversions if required.

c. ADC conversions are initiated. This is done by starting single

conversions, starting Timer 2 running for Timer 2 conversions

or by receiving an external trigger.

CONVERT ADC CH#5

CONVERT ADC CH#2

000800H

0007FFH

000000H

EXTERNAL

DATA

MEMORY

SPACE

(24-BIT

ADDRESS

SPACE)

2 KBYTES

ON-CHIP

XRAM

CFG83x.0=1

EXTERNAL

DATA

MEMORY

000000H

SPACE

(24-BIT

ADDRESS

SPACE)

CFG83x.0=0

Figure 3

XRAM and PORT 0/2 Access

During ADC DMA mode the MicroConverter is free to continue code

execution. However certain features are gated “off” during the ADC

DMA since they are being used by the DMA mode.

REV. prA May 2002 MicroConverter Tech Note – uC019

- 1 - http://www.analog.com/microconverter

MicroConverter® Technical Note – uC019

a

DMA To XRAM on the ADuC831/832

Access to Ports 0 and 2 are also disabled when performing DMA

conversions to the external XRAM since these ports are used to

interface the external XRAM. Note that during DMA to the internally

contained XRAM ports 0 and 2 are available for use.

Since the DMA mode uses the XRAM data-bus during DMA operation

access to both the internal and external XRAM is affected by DMA

operation.

If the user has enabled the internal XRAM and doing DMA into the

internal XRAM the mircocontroller core will not be able to access the

XRAM.

If the user has not enabled the internal XRAM and is performing DMA

conversions to an external XRAM, the microcontroller will not be able

to access the external XRAM.

If the user has enabled the internal XRAM but is doing DMA

conversions to XRAM locations after 7FFH (i.e. to an external XRAM)

then the microcontroller core will be able to access the internal XRAM.

The extended stack pointer can be enabled in the CFG83x register. It

will use XRAM once the 256 bytes of internal RAM are used. The

operation of the extended stack pointer will be affected in the same way

as for the microcontroller core.

DMA ‘C’ Example

In the following example DMA conversions are performed on channel 0

of the ADC. Using the Menu driven routine results can be displayed

back on a hyperterminal window.

Note: The following code is for the ADuC832. The same code can be

used for the ADuC831 if the baud rate is adjusted for 9600. For an

11.0592MHz crystal this would be

SCON = 0x052;

T3CON = 0x085;

T3FD = 0x08;

in the

deleted.

init832

function. The line

pllcon = 0x00;

should be

REV. prA May 2002 MicroConverter Tech Note – uC019

- 2 - http://www.analog.com/microconverter

MicroConverter® Technical Note – uC019

a

DMA To XRAM on the ADuC831/832

REV. prA May 2002 MicroConverter Tech Note – uC019

- 3 - http://www.analog.com/microconverter

MicroConverter® Technical Note – uC019

a

DMA To XRAM on the ADuC831/832

REV. prA May 2002 MicroConverter Tech Note – uC019

- 4 - http://www.analog.com/microconverter

MicroConverter® Technical Note – uC019

a

DMA To XRAM on the ADuC831/832

REV. prA May 2002 MicroConverter Tech Note – uC019

- 5 - http://www.analog.com/microconverter

Loading...

Loading...