ANALOG DEVICES ADuC816 Service Manual

INSTRUCTION SET

Arithmetic Operations

ADD A,source 1,2 12

ADD A,#data 2 12

ADDC A,source 1,2 12

ADDC A,#data 2 12

SUBB A,source subtract from A 1,2 12

SUBB A,#data 2 12

INC A 1 12

INC source increment 1,2 12

INC DPTR * 1 24

DEC A 1 12

DEC source 1,2 12

MUL AB multiply A by B 1 48

DIV AB divide A by B 1 48

DA A decimal adjust 1 12

add source to A

add with carry

with borrow

decrement

Data Transfer Operations

MOV A,source 1,2 12

MOV A,#data 2 12

MOV dest,A move source 1,2 12

MOV dest,source 1,2,3 24

MOV dest,#data 2,3 12,24

MOV DPTR,#data16 3 24

MOVC A,@A+DPTR move from 1 24

MOVC A,@A+PC 1 24

MOVX A,@Ri 1 24

MOVX A,@DPTR move to/from 1 24

MOVX @Ri,A 1 24

MOVX @DPTR,A 1 24

PUSH direct push onto stack 2 24

POP direct pop from stack 2 24

XCH A,source exchange bytes 1,2 12

XCHD A,@Ri exchg low digits 1 12

ACALL addr11 2 24

LCALL addr16 3 24

RET return from sub. 1 24

RETI return from int. 1 24

AJMP addr11 2 24

LJMP addr16 3 24

SJMP rel 2 24

JMP @A+DPTR 1 24

JZ rel jump if A = 0 2 24

JNZ rel jump if A not 0 2 24

CJNE A,direct,rel 3 24

CJNE A,#data,rel compare and 3 24

CJNE Rn,#data,rel equal 3 24

CJNE @Ri,#data,rel 3 24

DJNZ Rn,rel decrement and 2 24

DJNZ direct, rel 3 24

NOP no operation 1 12

to destination

code memory

data memory

call subroutine

jump

jump if not

jump if not zero

bytes

bytes

bytes

ASSEMBLER DIRECTIVES

EQU define symbol

DATA define internal memory symbol

IDATA define indirect addressing symbol

XDATA define external memory symbol

BIT define internal bit memory symbol

CODE define program memory symbol

DS reserve bytes of data memory

DBIT reserve bits of bit memory

DB store byte values in program memory

OSC

periods

Rn register addressing using R0-R7

direct 8bit internal address (00h-FFh)

@Ri indirect addressing using R0 or R1

source any of [Rn, direct, @Ri]

dest any of [Rn, direct, @Ri]

#data 8bit constant included in instruction

#data16 16bit constant included in instruction

bit 8bit direct address of bit

rel signed 8bit offset

addr11 11bit address in current 2K page

addr16 16bit address

Legend

* INC DPTR increments the 24bit value DPP/DPH/DPL

Logical Operations

ANL A,source 1,2 12

ANL A,#data 2 12

ANL direct,A 2 12

OSC

periods

ANL direct,#data 3 24

ORL A,source 1,2 12

ORL A,#data 2 12

ORL direct,A 2 12

ORL direct,#data 3 24

XRL A,source 1,2 12

XRL A,#data 2 12

XRL direct,A 2 12

XRL direct,#data 3 24

CLR A clear A to zero 1 12

CPL A complement A 1 12

RL A rotate A left 1 12

RLC A ...through C 1 12

RR A rotate A right 1 12

RRC A ...through C 1 12

SWAP A swap nibbles 1 12

Boolean Variable ManipulationProgram Branching

OSC

periods

CLR C 1 12

CLR bit 2 12

SETB C 1 12

SETB bit 2 12

CPL C 1 12

CPL bit 2 12

ANL C,bit AND bit with C 2 24

ANL C,/bit ...NOTbit with C 2 24

ORL C,bit OR bit with C 2 24

ORL C,/bit ...NOTbit with C 2 24

MOV C,bit 2 12

MOV bit,C 2 24

JC rel jump if C set 2 24

JNC rel jmp if C not set 2 24

JB bit,rel jump if bit set 3 24

JNB bit,rel jmp if bit not set 3 24

JBC bit, rel jmp&clear if set 3 24

DW store word values in program memory

ORG set segment location counter

END end of assembly source file

CSEG select program memory space

XSEG select external data memory space

DSEG select internal data memory space

ISEG select indirectly addressed internal

BSEG select bit addressable memory space

logical AND

logical OR

logical XOR

clear bit to zero

set bit to one

complement bit

move bit to bit

data memory space

bytes

bytes

OSC

periods

OSC

periods

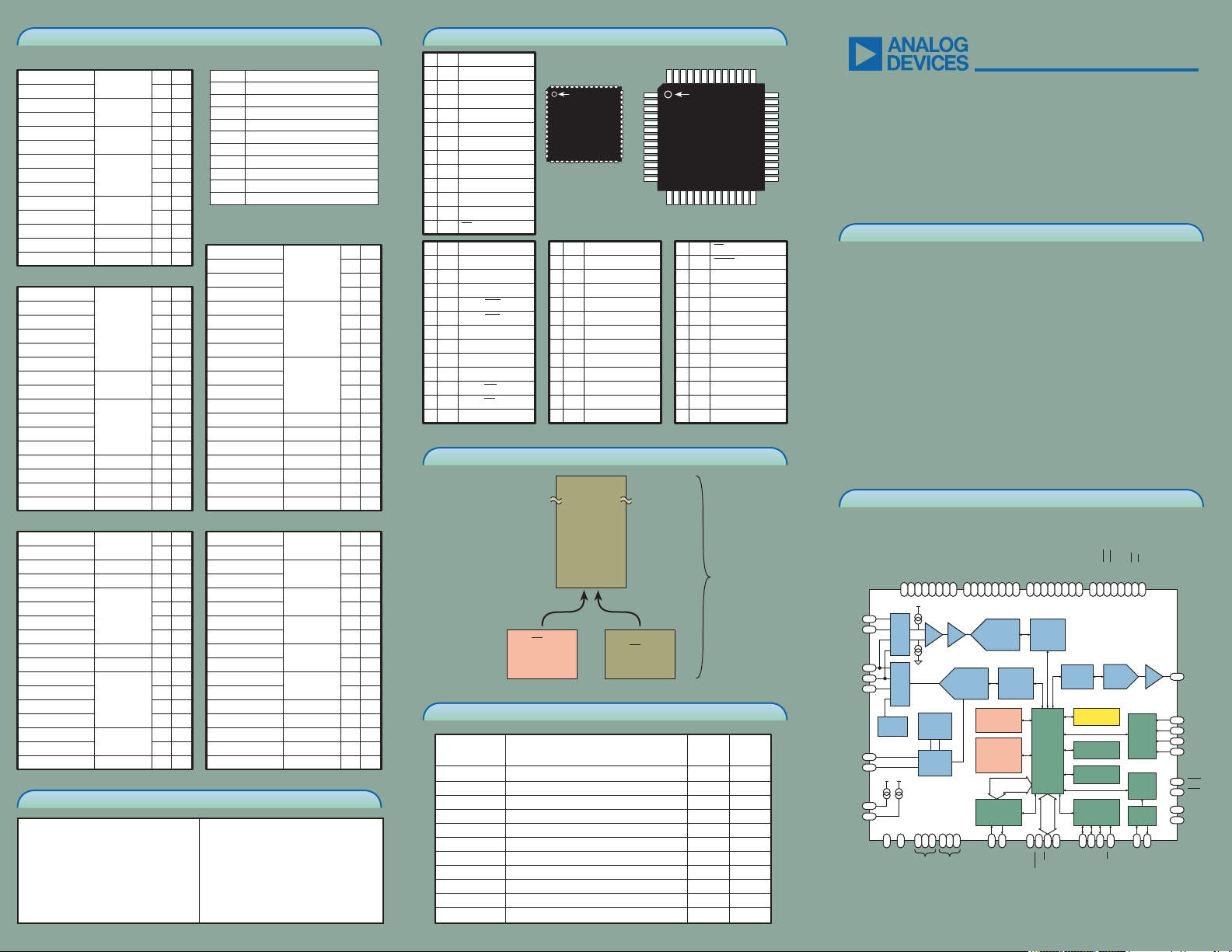

PIN FUNCTIONS

1 56 P1.0 / T2

2 1 P1.1 / T2EX

3 2 P1.2 / IEXC1 / DAC

4 3 P1.3 / IEXC2 / AIN5

5 4,5 AVDD

6 6,7,8 AGND

7 9 REFIN8 10 REFIN+

9 11 P1.4 / AIN1

10 12 P1.5 / AIN2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

545556

52

53

pin 1 identifier

ADuC816

56pin CSP

TOP VIEW

(not to scale)

15

434445464748495051

42

1 39

41

40

2

39

3

38

37

4

36

5

35

6

34

33

7

32

8

31

30

9

29

10

11

2625242322212019181716

28

27

12

13

pin 1 identifier

ADuC816

52pin PQFP

TOP VIEW

(not to scale)

11 13 P1.6 / AIN3

12 14 P1.7 / AIN4 / DAC

13 15 SS

14 16 MISO

15 17 RESET

16 18 P3.0 / RxD

17 19 P3.1 / TxD

18 20 P3.2 / INT0

19 21 P3.3 / INT1

20 22 DVDD

21 23 DGND

22 24 P3.4 / T0

23 25 P3.5 / T1

24 26 P3.6 / WR

25 27 P3.7 / RD

26 28 SCLOCK / D0

PQFP

CSP

27 29 MOSI / D1

28 30 P2.0 / A8 / A16

29 31 P2.1 / A9 / A17

30 32 P2.2 / A10 / A18

31 33 P2.3 / A11 / A19

32 34 XTAL1 (in)

33 35 XTAL2 (out)

34 36 DVDD

35 37,38 DGND

36 39 P2.4 / A12 / A20

37 40 P2.5 / A13 / A21

38 41 P2.6 / A14 / A22

39 42 P2.7 / A15 / A23

40 43 EA

41 44 PSEN

42 45 ALE

43 46 P0.0 / AD0

44 47 P0.1 / AD1

45 48 P0.2 / AD2

46 49 P0.3 / AD3

47 50 DGND

48 51 DVDD

49 52 P0.4 / AD4

50 53 P0.5 / AD5

51 54 P0.6 / AD6

52 55 P0.7 / AD7

PROGRAM MEMORY SPACE (read only)

FFFFh

external

program

memory

2000h

1FFFh

0000h

EA=1

internal

8K bytes

Flash/EE

EA=0

external

INTERRUPT VECTOR ADDRESSES

Interrupt

Bit

Interrupt Name

PSMCON.5 Power Supply Monitor Interrupt 43h 1

WDS WatchDog Timer Interrupt 5Bh 2

IE0 External Interrupt 0 03h 3

RDY0/RDY1 End of ADC Conversion Interrupt 33h 4

TF0 Timer0 Overflow Interrupt 0Bh 5

IE1 External Interrupt 1 13h 6

TF1 Timer1 Overflow Interrupt 1Bh 7

ISPI SPI Interrupt 3Bh 8

RI/TI UART Interrupt 23h 9

TF2/EXF2 Timer2 Interrupt 2Bh 10

TIMECON.2 Time Interval Counter Interrupt 53h 11

Vector

Address

40414243444546474849505152

26252423222120191817161514

64K bytes

addressable

Priority

within

Level

38

37

36

35

34

33

32

31

30

29

28

27

the ADuC816 is:

other on-chip features: calibrated temperature sensor, power supply

9

AIN1

10

AIN2

11

AIN3

12

AIN4

4AIN5

8

REFIN+

7

REFIN-

34I

1

EXC

I

2

EXC

PRINTED IN U.S.A. G02416-2.5-02/02 (A)

www.analog.com/microconverter REV. A

ADuC816

P2.3 (A11 / A19)

P2.4 (A12 / A20)

P2.5 (A13 / A21)

P2.6 (A14 / A22)

P2.7 (A15 / A23)

P2.3

P2.4

P2.5

P2.6

P2.7

DAC

control

user RAM

watchdog

power supply

synchronous

serial interface

emulator

15

RESET

®

P3.2 (INT0)

P3.1 (TxD)

P3.0 (RxD)

P3.2

P3.1

P3.0

ADuC816

DAC

256 x 8

timer

monitor

(SPI)

262714

MOSI

MISO

SCLOCK

MicroConverter

Quick Reference Guide

a “Data Acquisition System on a Chip”

ADC: 16bit Σ∆ with programmable gain,

plus 16bit Σ∆ auxiliary ADC

DAC: 12bit, 15µs, voltage output, rail-to-rail

<1LSB DNL

EEPROM: 8K bytes Flash/EE program memory

microcontroller: industry standard 8052

FUNCTIONAL BLOCK DIAGRAM

P0.5 (AD5)

P0.4 (AD4)

P0.3 (AD3)

P0.2 (AD2)

P0.1 (AD1)

P0.0 (AD0)

P0.5

P0.4

P0.3

P0.2

P0.1

P0.0

43

AIN

MUX

AIN

MUX

TEMP

bandgap

sensor

reference

(256 counts

per oC)

V

REF

detect

200µA / 400µA

5

6

2034354721

48

DD

DD

AV

AGND

DV

640 bytes Flash/EE data memory

32 I/O lines, programmable PLL clock

(98KHz to 12MHz from 32KHz crystal)

monitor, watchdog timer, flexible serial

interface ports, voltage reference, time interval

counter

2 / AIN5)

1 / DAC)

EXC

EXC

P2.1 (A9 / A17)

P2.0 (A8 / A16)

P1.7 (AIN4 / DAC)

P1.6 (AIN3)

P1.5 (AIN2)

P1.4 (AIN1)

P1.3 (I

P1.2 (I

P1.1 (T2EX)

P1.0 (T2)

P0.7 (AD7)

P0.6 (AD6)

P1.0

P0.7

P0.6

52515049464544

(primary ADC)

PGABUF

(auxillary ADC)

16 bit

Σ∆ ADC

DGND

P1.4

P1.3

P1.2

P1.1

94321

16 bit

Σ∆ ADC

640 x 8

data

Flash/EE

8K x 8

program

Flash/EE

downloader

debugger

asynchronous

serial port

(UART)

16

RxD

P1.6

P1.5

ADC

control

&

calibration

17

TxD

P1.7

P2.2 (A10 / A18)

P2.1

P2.0

P2.2

ADC

control

&

calibration

8052

MCU

core

single-pin

424140

EA

ALE

PSEN

P3.4 (T0)

P3.3 (INT1)

P3.4

P3.3

13SS

P3.6 (WR)

P3.5 (T1)

P3.6

P3.5

16bit

counter

timers

time

interval

counter

OSC &

PLL

32

XTAL1

P3.7 (RD)

P3.7

25242322191817163938373631302928121110

BUF

33

XTAL2

3

22

23

1

2

18

19

26

27 D1

DAC

T0

T1

T2

T2EX

INT0

INT1

D0

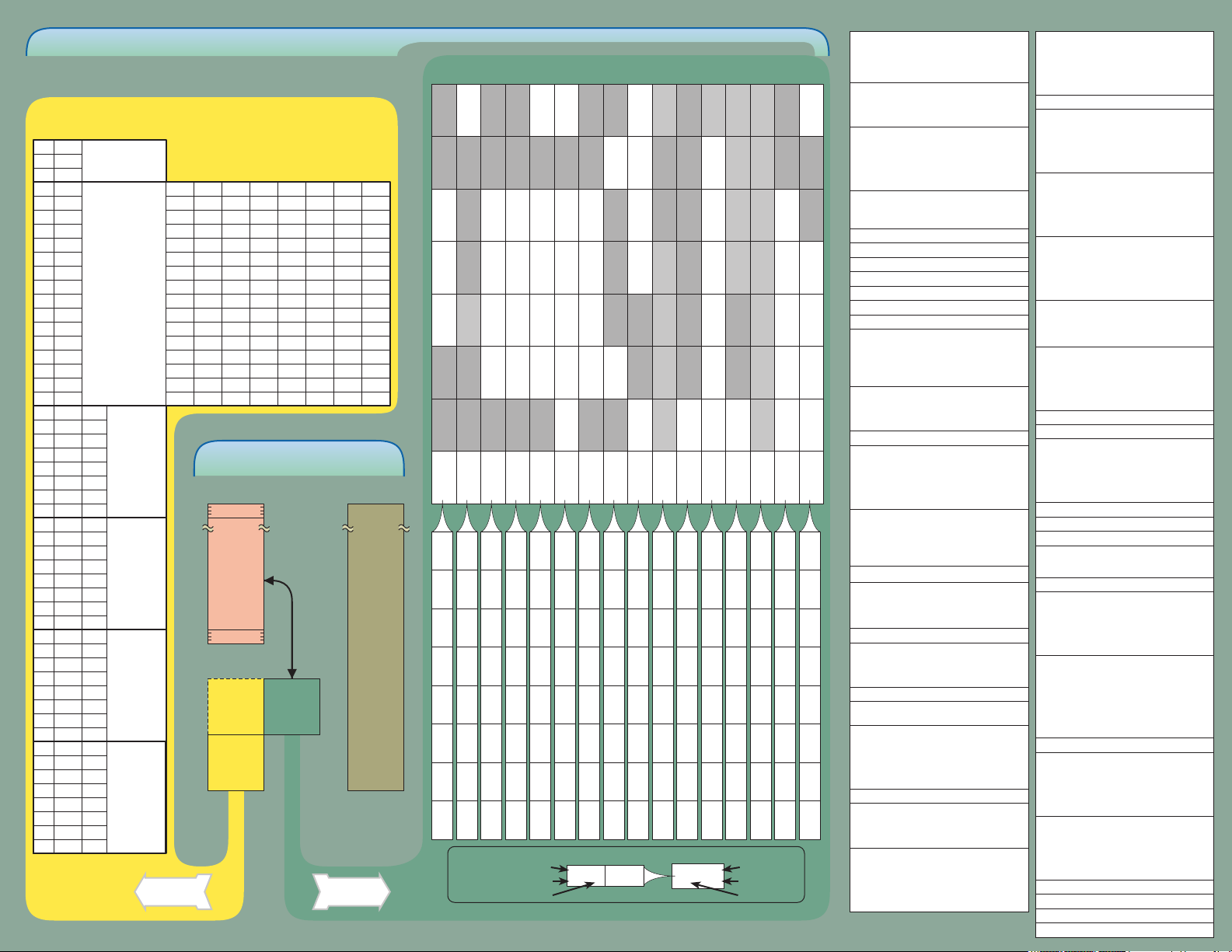

DATA MEMORY: RAM, SFRs, user Flash/EE (all read/write)

LOWER RAM

decimal

address

HEX

address

127

7Fh

...

30h

2Fh

2Eh

2Dh

2Ch

2Bh

2Ah

29h

28h

27h

26h

25h

24h

23h

22h

21h

20h

1Fh R7

1Eh R6

1Dh R5

1Ch R4

1Bh R3

1Ah R2

19h R1

18h R0

17h R7

16h R6

15h R5

14h R4

13h R3

12h R2

11h R1

10h R0

0Fh R7

0Eh R6

0Dh R5

0Ch R4

0Bh R3

0Ah R2

09h R1

08h R0

07h R7

06h R6

05h R5

04h R4

03h R3

02h R2

01h R1

00h R0

General Purpose

Area

Bit Addressable

Area

Register

Bank 3

Register

Bank 2

Register

Bank 1

Register

Bank 0

MSB

address

7Fh 7Eh 7Dh 7Ch 7Bh 7Ah 79h 78h

(bit addresses)

77h 76h 75h 74h 73h 72h 71h 70h

6Fh 6Eh 6Dh 6Ch 6Bh 6Ah 69h 68h

67h 66h 65h 64h 63h 62h 61h 60h

5Fh 5Eh 5Dh 5Ch 5Bh 5Ah 59h 58h

57h 56h 55h 54h 53h 52h 51h 50h

4Fh 4Eh 4Dh 4Ch 4Bh 4Ah 49h 48h

47h 46h 45h 44h 43h 42h 41h 40h

3Fh 3Eh 3Dh 3Ch 3Bh 3Ah 39h 38h

37h 36h 35h 34h 33h 32h 31h 30h

2Fh 2Eh 2Dh 2Ch 2Bh 2Ah 29h 28h

27h 26h 25h 24h 23h 22g 21h 20h

1Fh 1Eh 1Dh 1Ch 1Bh 1Ah 19h 18h

17h 16h 15h 14h 13h 12h 11g 10h

0Fh 0Eh 0Dh 0Ch 0Bh 0Ah 09h 08h

07h 06h 05h 04h 03h 02h 01h 00h

DATA MEMORY SPACE

(read/write area)

SFRs

(direct

addressing

only)

FFFFFFh

( page 159 )

9Fh

640 bytes

(160 pages)

data

Flash/EE

(accessible

through

SFRs) external

( page 0 )

00h

FFh

128 bytes

upper RAM

(indirect

addressing

only)

128 bytes

lower RAM

(direct or

indirect

addressing)

00h 000000h

lower RAM

details

memory

(16MEG

addressable)

SFR details

...

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

data

LSB

address

SFR MAP & RESET VALUES

SPIDAT

(reserved)

(reserved)

DACCON

FDh 00h

DACH

FCh 00h

DACL

FBh 00h

(reserved) (reserved)

SPICON

F8h 04hBF0h 00h

SPR0

F8h 0

SPR1

F9h 0

CPHA

FAh 1

CPOL

FBh 0

SPIM

FCh 0

SPE

FDh 0

WCOL

FEh 0

ISPI

FFh 0

MAP KEY

(reserved)

(reserved)(reserved)(reserved)(reserved)(reserved)

(not used)

F7h 00h

F0h 0

F1h 0

F2h 0

F3h 0

F4h 0

F5h 0D0EDh 0

F6h 0

F7h 0D1EFh 0

(reserved)

(reserved)

GN1H*

EDh ~59h

GN1L*

ECh ~9Ah

GN0H*

EBh ~53h

GN0M*

EAh ~55h

(reserved)

DCON

E8h 00h

E8h 0

E9h 0

EAh 0

D0EN

EBh 0

ECh 0

D1EN

EEh 0

mnemonic

reset value

(reserved)

(reserved)

OF1H

E5h 80h

OF1L

E4h 00h

OF0H

E3h 80h

OF0M

E2h 00h

(reserved)

ACC

E0h 00h

E0h 0

E1h 0

E2h 0

E3h 0

E4h 0

E5h 0

E6h 0

E7h 0

address

(reserved)

D7h 03h

D5h 00h

D4h 45h

D3h 00h

D2h 07h

D1h 00h

D0h 00h

D3h 0

D4h 0

(reserved)(reserved)

TH2

CDh 00h

TL2

CCh 00h

RCAP2H

CBh 00h

RCAP2L

CAh 00h

T2CON

C8h 00h

CAP2

C8h 0

CNT2

C9h 0

TR2

CAh 0

EXEN2

CBh 0

TCLK

CCh 0

RCLK

CDh 0

EXF2

CEh 0

TF2

CFh 0

(reserved)(reserved)

EADRL

CHIPID

(reserved) (reserved) (reserved)

WDCON

WDWR

WDE

WDS

WDIR

PRE0

PRE1

PRE2

PRE3

PSMCON

DFh DEh

(reserved)

ADC1H

DDh 00h

ADC1L

DCh 00h

ADC0H

DBh 00h

ADC0M

DAh 00h

(reserved)

ADCSTAT

D8h 00h

D8h 0PD0h 0

D9h 0F1D1h 0

ERR1

DAh 0OVD2h 0

RS0

ERR0

DBh 0

RS1

DCh 0

NOXREF

CAL

DDh 0F0D5h 0

RDY1

DEh 0ACD6h 0

RDY0

DFh 0CYD7h 0

PLLCON

(reserved)

ICON

SF

ADC1CON

ADC0CON

ADCMODE

PSW

these bits this byte

SPR0

SPR1

F8h 0

F9h 0

* calibration coefficients are preconfigured at power-up to factory calibrated values

(not used)

EDATA4

BFh 00h

(reserved)

BEh 00h

BDh 00h

BCh 00h

(reserved)

(reserved) (reserved)(reserved)

(reserved)

(reserved) (reserved)

C6h 00h

EDATA3

EDATA2

EDATA1

(reserved)(reserved)

C2h 16h

B9h 00h

IEIP2

(not used) (not used) (not used) (not used)

A9h A0h

ECON

C0h 10hIPB8h 00hP3B0h FFhIEA8h 00hP2A0h FFh

PX0

C0h 0

PT0

C1h 0

PX1

C2h 0

PT1

C3h 0

C4h 1PSBCh 0T0B4h 1ESACh 0

PT2

C5h 0

PADC

C6h 0

C7h 0

RXD

B8h 0

B0h 1

TXD

B9h 0

B1h 1

INT0

BAh 0

B2h 1

INT1

BBh 0

B3h 1

BDh 0T1B5h 1

BEh 0WRB6h 1

BFh 0RDB7h 1EAAFh 0

EX0

A8h 0

ET0

A9h 0

EX1

AAh 0

ET1

ABh 0

ET2

ADh 0

EADC

AEh 0

are contained in

SPICON

F8h 00h

(not used)

(not used)

INTVAL

(not used)

A6h 00h

HOUR

(not used)

A5h 00h

MIN

(not used)

A4h 00h

SEC

(reserved)(reserved)

A3h 00h

HTHSEC

A2h 00h

SBUF

TIMECON

99h 00h

A1h 00h

SCON

98h 00hP190h FFh

A0h 1RI98h 0T290h 1

A1h 1TI99h 0

RB8

A2h 1

9Ah 0

TB8

A3h 1

9Bh 0

REN

A4h 1

9Ch 0

SM2

A5h 1

9Dh 0

SM1

A6h 1

9Eh 0

SM0

A7h 1

9Fh 0

mnemonic

reset value

address

(not used)

(not used)

(not used)

(not used)(not used)(not used)(not used)

T2EX

91h 1

92h 1

93h 1

94h 1

95h 1

96h 1

97h 1

(reserved) (reserved)

TH1

8Dh 00h

TH0

8Ch 00h

TL1

8Bh 00h

TL0

8Ah 00h

TMOD

89h 00hSP81h 07h

TCON

88h 00hP080h FFh

IT0

88h 0

IE0

89h 0

IT1

8Ah 0

IE1

8Bh 0

TR0

8Ch 0

TF0

8Dh 0

TR1

8Eh 0

TF1

8Fh 0

PCON

87h 00h

(reserved) (reserved)

DPP

84h 00h

DPH

83h 00h

DPL

82h 00h

80h 1

81h 1

82h 1

83h 1

84h 1

85h 1

86h 1

87h 1

SFR DESCRIPTIONS

ADCSTAT ADC Status Register

RDY0 primary ADC ready flag

RDY1 auxiliary ADC ready flag

CAL calibration flag

NOXREF no external reference flag

ERR0 primary ADC error flag

ERR1 auxiliary ADC error flag

ADCMODEADC Mode Register

ADMODE.5 primary ADC enable bit

ADMODE.4 auxiliary ADC enable bit

ADMODE.2 mode bits

ADMODE.1 [powerdown, idle, sngl-conv, cont-conv,

ADMODE.0 zero-selfcal, fs-selfcal, zero-syscal, fs-syscal]

ADC0CON Primary ADC Control Register

AD0CON.7 (this bit must contain zero)

AD0CON.6 external reference select bit (0=internal ref)

AD0CON.5 channel selection bits:

AD0CON.4 [AIN1-AIN2,AIN3-AIN4,AIN2-AIN2,AIN3-AIN2]

AD0CON.3 unipolar select bit (0=bipolar)

AD0CON.2 range select bits:

AD0CON.1 [±20mV, ±40mV, ±80mV, ±160mV, ±320mV,

AD0CON.0 ±640mV, ±1.28V, ±2.56V]

ADC1CON Auxiliary ADC Control Register

AD1CON.6 external reference select bit (0=internal ref)

AD1CON.5 channel selection bits:

AD1CON.4 [AIN3, AIN4, TEMP, AIN5]

AD1CON.3 unipolar select bit (0 = bipolar)

SF Sync Filter Register: f

OF0H,OF0M,OF0L ADC0 offset coefficient

OF1H,OF1L ADC1 offset coefficient

GN0H,GN0M,GN0L ADC0 gain coefficient

GN1H,GN1L ADC1 gain coefficient

ADC0H,ADC0M ADC0 data

ADC1H,ADC1L ADC1 data

ICON Current Source Control Register

ICON.6 burnout current enable bit

ICON.5 ADC1 current correction bit (0=correction off)

ICON.4 ADC0 current correction bit (0=correction off)

ICON.3 I2 pin select bit [0=pin4 / 1=pin3]

ICON.2 I1 pin select bit [0=pin3 / 1=pin4]

ICON.1 I2 enable bit (0=disable)

ICON.0 I1 enable bit (0=disable)

DACCON DAC Control register

DACCON.4 DAC pin select bit [0=pin3 / 1=pin12]

DACCON.3 ModeSelect (0=12bit, 1=8bit)

DACCON.2 RangeSelect (0=2.5V, 1=AVDD)

DACCON.1 Clear DAC (0=0V, 1=normal operation)

DACCON.0 PowerDown DAC (0=off, 1=on)

DACH,DACL DAC data registers

PLLCON PLL Control Register

PLLCON.7 oscillator powerdown control bit (0=normal)

PLLCON.6 PLL lock indicator flag (0=out of lock)

PLLCON.5 (this bit must contain zero)

PLLCON.4 EA detect status bit (reflects state of EA pin)

PLLCON.3 “fast interrupt” control bit (0=normal)

PLLCON.2 3-bit clock divideer value, “CD” (default=3):

PLLCON.1

PLLCON.0

TIMECON Time Interval Counter Control Register

TIMECON.6 24hour select bit (0=255hour)

TIMECON.5 interval timebase select bits

TIMECON.4 [128th sec, seconds, minutes, hours]

TIMECON.3 single time interval control bit (0=reload&restart)

TIMECON.2 time interval interrupt bit, “TII”

TIMECON.1 time interval enable bit (0=disable&clear)

TIMECON.0 time clock enable bit (0=disable)

INTVAL TIC Interval Register

HTHSEC TIC Elapsed 128th Second Register

SEC TIC Elapsed Seconds Register

MIN TIC Elapsed Minutes Register

HOUR TIC Elapsed Hours Register

f

CORE

CHIPID Chip ID Register (1X hex = ADuC816)

ECON Data Flash/EE comand register

01h READ page

02h PROGRAM page

04h VERIFY page

05h ERASE page

06h ERASE ALL

EADRH,EADRL Data Flash/EE address registers

EDATA1,EDATA2,EDATA3,EDATA4

Data Flash/EE data registers

SPICON SPI Control register

ISPI SPI inturrupt (set at end of SPI transfer)

WCOL write collision error flag

SPE SPI enable (0=DCON enable, 1=SPI enable)

SPIM master mode select (0=slave)

CPOL clock polarity select (0=SCLK idles low)

CPHA clock phase select (0=leading edge latch)

SPR1 SPI bitrate select bits

SPR0 bitrate = F

SPIDAT SPI Data register

DCON D0 & D1 Control register

(enabled if SPE=0, see SPICON register above)

D1 D1 output bit

D1EN D1 output enable (0=disable)

D0 D0 output bit

D0EN D0 output enable (0=disable)

WDCON Watchdog Timer control register

PRE3 watchdog timeout selection bits

PRE2 0000-0111 = timeout=[15.6, 31.2, 62.5, 125, 500

PRE1 1000 = immediate reset 1000, 2000] ms

PRE0 all others codes = reserved

WDIR watchdog interrupt response enable

WDS watchdog status flag

WDE watchdog enable

WDWR watchdog write enable

= 4,096Hz ÷ (3·SF)

ADC

= 12,582,912Hz ÷ 2

81h READ byte

82h PROGRAM byte

0Fh EXIT ULOAD mode

F0h ENTER ULOAD mode

(all others reserved)

/ [2, 4, 8, 16]

CORE

CD

PSMCON Power Supply Monitor control register

PSMCON.7 DVDD compare bit (0=fault)

PSMCON.6 AVDD compare bit (0=fault)

PSMCON.5 PSM interrupt bit

PSMCON.4 DVDD trip point select bits

PSMCON.3 [4.63V, 3.08V, 2.93V, 2.63V]

PSMCON.2 AVDD trip point select bits

PSMCON.1 [4.63V, 3.08V, 2.93V, 2.63V]

PSMCON.0 PSM powerdown control (1=on / 0=off)

SP Stack Pointer

IE Interrupt Enable register #1

EA enable inturrupts (0=all inturrupts disabled)

EADC enable RDY0/RDY1 (ADC interrupt)

ET2 enable TF2/EXF2 (Timer2 overflow interrupt)

ES enable RI/TI (serial port interrupt)

ET1 enable TF1 (Timer1 overflow interrupt)

EX1 enable IE1 (external interrupt 1)

ET0 enable TF0 (Timer0 overflow interrupt)

EX0 enable IE0 (external interrupt 0)

IEIP2 Interrupt Enable/Priority register #2

IEIP2.7 (not used)

IEIP2.6 pirority of TII interrupt (timer interval)

IEIP2.5 priority of PSMI interrupt (power supply monitor)

IEIP2.4 priority of ISPI interrupt (serial interface)

IEIP2.3 (this bit must contain zero)

IEIP2.2 enable TII interrupt (timer interval)

IEIP2.1 enable PSMI interrupt (power supply monitor)

IEIP2.0 enable ISPI interrupt (serial interface)

IP Interrupt Priority register

IP.7 (not used)

PADC priority of RDY0/RDY1 (ADC interrupt)

PT2 priority of TF2/EXF2 (Timer2 overflow interrupt)

PS priority of RI/TI (serial port interrupt)

PT1 priority of TF1 (Timer1 overflow interrupt)

PX1 priority of IE1 (external INT1)

PT0 priority of TF0 (Timer0 overflow interrupt)

PX0 priority of IE0 (external INT0)

TMOD Timer Mode register

TMOD.3/.7 gate control bit (0=ignore INTx)

TMOD.2/.6 counter/timer select bit (0=timer)

TMOD.1/.5 timer mode selecton bits

TMOD.0/.4 [13bitT, 16bitT/C, 8bitT/Creload, 2x8bitT]

(upper nibble = Timer1, lower nibble = Timer0)

TCON Timer Control register

TF1 Timer1 overflow flag

TR1 Timer1 run control (0=off, 1=run)

TF0 Timer0 overflow flag

TR0 Timer0 run control (0=off, 1=run)

IE1 external INT1 flag

IT1 IE1 type (0=level trig, 1=edge trig)

IE0 external INT0 flag

IT0 IE0 type (0=level trig, 1=edge trig)

TH0,TL0 Timer0 registers

TH1,TL1 Timer1 registers

T2CON Timer2 Control register

TF2 overflow flag

EXF2 external flag

RCLK receive clock enable (0=Timer1 used for RxD clk)

TCLK transmit clock enable (0=Timer1 used for TxD clk)

EXEN2 external enable (0=ignore T2EX, 1=cap/rld on T2EX)

TR2 run control (0=stop, 1=run)

CNT2 timer/counter select (0=timer, 1=counter)

CAP2 capture/reload select (0=reload, 1=capture)

TH2,TL2 Timer2 register

RCAP2H,RCAP2L Timer2 Reload/Capture

P0 Port0 register

P1 Port1 register

P1.2-1.7 analog/digital pins (1=analog function, 0=digital input)

T2EX timer/counter 2 capture/reload trigger (or digital I/O)

T2 timer/counter 2 external input (or digital I/O)

P2 Port2 register

P3 Port3 register

RD external data memory read strobe

WR external data memory write strobe

T1 timer/counter 1 external input

T0 timer/counter 0 external input

INT1 external interrupt 1

INT0 external interrupt 0

TxD serial port transmit data line

RxD serial port receive data line

SCON Serial communications Control register

SM0 UART mode control bits baud rate:

SM1 00 - 8bit shift register - F

01 - 8bit UART - TimerOverflowRate/32(x2)

10 - 9bit UART - F

11 - 9bit UART - TimerOverflowRate/32(x2)

SM2 in modes 2&3, enables multiprocessor communication

REN receive enable control bit

TB8 in modes 2&3, 9th bit transmitted

RB8 in modes 2&3, 9th bit received

TI transmit interrupt flag

RI receive interrupt flag

SBUF Serial port Buffer register

PCON Power Control register

PCON.7 double baud rate control

PCON.6 enable serial interrupt (ISI) from power-down mode

PCON.5 enable interrupt 0 (INT0) from power-down mode

PCON.4 ALE disable (0=normal, 1=forces ALE high)

PCON.3 general purpose flag

PCON.2 general purpose flag

PCON.1 power-down control bit (0=normal)

PCON.0 idle-mode control (0=normal)

PSW Program Status Word

CY carry flag

AC auxiliary carry flag

F0 general purpose flag 0

RS1 register bank select control bits

RS0 active register bank = [0,1,2,3]

OV overflow flag

F1 general purpose flag 1

P parity of ACC

DPP Data Pointer Page

/12

CORE

/64(x2)

CORE

DPH,DPL (DPTR) Data Pointer

ACC Accumulator

B auxiliary math register

Loading...

Loading...