Low Power, Precision Analog Microcontroller

,

Dual

Sigma-Delta ADCs,

FEATURES

Analog input/output

Dual (24-bit) ADCs

Single-ended and differential inputs

Programmable ADC output rate (4 Hz to 8 kHz)

Programmable digital filters

Built-in system calibration

Low power operation mode

Primary (24-bit) ADC channel

2 differential pairs or 4 single-ended channels

PGA (1 to 512) input stage

Selectable input range: ±2.34 mV to ±1.2 V

30 nV rms noise

Auxiliary (24-bit) ADC: 4 differential pairs or 7 single-

ended channels

On-chip precision reference (±10 ppm/°C)

Programmable sensor excitation current sources

200 μA to 2 mA current source range

Single 14-bit voltage output DAC

Microcontroller

ARM7TDMI core, 16-/32-bit RISC architecture

JTAG port supports code download and debug

Multiple clocking options

Memory

32 kB (16 kB × 16) Flash/EE memory, including 2 kB kernel

4 kB (1 kB × 32) SRAM

Tools

In-circuit download, JTAG based debug

Low cost, QuickStart™ development system

Communications interfaces

SPI interface (5 Mbps)

4-byte receive and transmit FIFOs

UART serial I/O and I

On-chip peripherals

4× general-purpose (capture) timers including

Wake -up timer

Watchdog timer

Vectored interrupt controller for FIQ and IRQ

8 priority levels for each interrupt type

Interrupt on edge or level external pin inputs

16-bit, 6-channel PWM

General-purpose inputs/outputs

Up to 14 GPIO pins that are fully 3.3 V compliant

Power

AVDD/DVDD specified for 2.5 V (±5%)

Active mode: 2.74 mA (@ 640 kHz, ADC0 active)

10 mA (@ 10.24 MHz, both ADCs active)

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

2

C (master/slave)

Flash/EE, ARM7TDMI

ADuC7060/ADuC7061

Packages and temperature range

Fully specified for −40°C to +125°C operation

32-lead LFCSP (5 mm × 5 mm)

48-lead LFCSP and LQFP

Derivatives

32-lead LFCSP (ADuC7061)

48-lead LQFP and 48-lead LFCSP (ADuC7060)

APPLICATIONS

Industrial automation and process control

Intelligent, precision sensing systems, 4 mA to 20 mA

loop-based smart sensors

GENERAL DESCRIPTION

The ADuC706x series are fully integrated, 8 kSPS, 24-bit data acquisition systems incorporating high performance multichannel

sigma-delta (Σ-) analog-to-digital converters (ADCs), 16-bit/

32-bit ARM7TDMI® MCU, and Flash/EE memory on a single chip.

The ADCs consist of a primary ADC with two differential pairs or

four single-ended channels and an auxiliary ADC with up to seven

channels. The ADCs operate in single-ended or differential input

mode. A single-channel buffered voltage output DAC is available

on chip. The DAC output range is programmable to one of four

voltage ranges.

The devices operate from an on-chip oscillator and a PLL generating an internal high frequency clock up to 10.24 MHz. The

microcontroller core is an ARM7TDMI, 16-bit/32-bit RISC

machine offering up to 10 MIPS peak performance; 4 kB of SRAM

and 32 kB of nonvolatile Flash/EE memory are provided on chip.

The ARM7TDMI core views all memory and registers as a single

linear array.

The ADuC706x contains four timers. Timer1 is a wake-up timer

with the ability to bring the part out of power saving mode. Timer2

is configurable as a watchdog timer. A 16-bit PWM with six output

channels is also provided. The ADuC706x contains an advanced

interrupt controller. The vectored interrupt controller (VIC) allows

every interrupt to be assigned a priority level. It also supports

nested interrupts to a maximum level of eight per IRQ and FIQ.

When IRQ and FIQ interrupt sources are combined, a total of 16

nested interrupt levels is supported. On-chip factory firmware

supports in-circuit serial download via the UART serial interface

ports and nonintrusive emulation via the JTAG interface. The parts

operate from 2.375 V to 2.625 V over an industrial temperature

range of −40°C to +125°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2011 Analog Devices, Inc. All rights reserved.

ADuC7060/ADuC7061

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 3

Functional Block Diagram .............................................................. 4

Specifications..................................................................................... 5

Electrical Specifications............................................................... 5

Timing Specifications ................................................................10

Absolute Maximum Ratings.......................................................... 14

ESD Caution................................................................................ 14

Pin Configurations and Function Descriptions ......................... 15

Terminology .................................................................................... 20

Overview of the ARM7TDMI Core ............................................. 21

Thumb Mode (T)........................................................................ 21

Multiplier (M)............................................................................. 21

EmbeddedICE (I) ....................................................................... 21

ARM Registers ............................................................................ 21

Interrupt Latency........................................................................ 22

Memory Organization ............................................................... 22

Flash/EE Control Interface........................................................ 23

Memory Mapped Registers....................................................... 27

Complete MMR Listing............................................................. 28

Reset .............................................................................................33

Oscillator, PLL, and Power Control .............................................34

Clocking System ......................................................................... 34

Power Control System................................................................ 34

ADC Circuit Information.............................................................. 38

Reference Sources....................................................................... 39

Diagnostic Current Sources...................................................... 39

Sinc3 Filter................................................................................... 40

ADC Chopping........................................................................... 40

Programmable Gain Amplifier................................................. 40

Excitation Sources...................................................................... 40

ADC Low Power Mode.............................................................. 40

ADC Comparator and Accumulator .......................................41

Temperature Sensor ................................................................... 41

ADC MMR Interface .................................................................41

Example Application Circuits................................................... 54

DAC Peripherals............................................................................. 56

DAC.............................................................................................. 56

Rev. C | Page 2 of 108

MMR Interface ........................................................................... 56

Using the DAC............................................................................ 57

Nonvolatile Flash/EE Memory ..................................................... 58

Flash/EE Memory Reliability.................................................... 58

Programming.............................................................................. 58

Processor Reference Peripherals................................................... 59

Interrupt System......................................................................... 59

IRQ............................................................................................... 59

Fast Interrupt Request (FIQ) .................................................... 60

Programmed Interrupts............................................................. 61

Vectored Interrupt Controller (VIC)....................................... 61

VIC MMRs.................................................................................. 61

Timers .............................................................................................. 66

Timer0.......................................................................................... 67

Timer1 or Wake-Up Timer....................................................... 69

Timer2 or Watchdog Timer...................................................... 71

Timer3.......................................................................................... 73

Pulse-Width Modulator................................................................. 75

Pulse-Width Modulator General Overview ........................... 75

UART Serial Interface.................................................................... 80

Baud Rate Generation................................................................ 80

UART Register Definitions....................................................... 80

I2C..................................................................................................... 86

Configuring External Pins for I2C Functionality................... 86

Serial Clock Generation ............................................................ 87

I2C Bus Addresses....................................................................... 87

I2C Registers................................................................................ 87

Serial Peripheral Interface............................................................. 96

MISO (Master In, Slave Out) Pin............................................. 96

MOSI (Master Out, Slave In) Pin............................................. 96

SCLK (Serial Clock I/O) Pin..................................................... 96

Slave Select (P0.0/SS) Input Pin ............................................... 96

Configuring External Pins for SPI Functionality................... 96

SPI Registers................................................................................ 97

General-Purpose I/O ................................................................... 101

GPxCON Registers................................................................... 101

GPxDAT Registers ................................................................... 102

GPxSET Registers..................................................................... 102

GPxCLR Registers.................................................................... 102

GPxPAR Registers .................................................................... 102

ADuC7060/ADuC7061

Hardware Design Considerations.............................................. 104

Power Supplies.......................................................................... 104

REVISION HISTORY

5/11—Rev. B to Rev. C

Change to Figure 1............................................................................4

Changes to Table 1 ............................................................................6

Add Temporary Protection Section and Keyed Permanent

Protection Section...........................................................................25

Added Permanent Protection Section and Sequence to Write

the Software Protection Key and Set Permanent Protection

Section ..............................................................................................26

Changes to Power Control System Section..................................35

Changes to Bit 9:6, Table 43 ...........................................................45

Changes to Primary Channel ADC Data Register Section and

Table 49.............................................................................................50

Changes to IRQEN Section and IRQCLR Section .....................59

Changes to Timer1 or Wake-Up Timer Section .........................69

Changes to Table 108 ....................................................................101

2/10—Rev. A to Rev. B

Changes to Features Section............................................................1

Changes to Table 1 ............................................................................4

Changes to Digital I/O Voltage to DGND Parameter ................14

Changes to Pin 19, Pin 20, and Pin 45 Descriptions (Table 8)..16

Changes to Pin 13, Pin 14, and Pin 29 Descriptions (Table 9)..18

Changes to Bit 8 in Table 14...........................................................23

Changes to Table 20 ........................................................................28

Changes to Power Control System Section..................................34

Added Table 32 ................................................................................35

Changes to Endnote 2 and Endnote 3 of Table 34 ......................36

Changes to Table 42 ........................................................................42

Changes to Bit 12 and Bits[3:0] in Table 43 .................................44

Changes to Bit 12 in Table 44 ........................................................45

Changes to Endnote 2 in Table 45.................................................47

Changes to Bit 5 in Table 63...........................................................55

Changes to Serial Downloading (In-Circuit Programming)

Section ..............................................................................................57

Changes to Priority Registers Section ..........................................61

Changes to GPxPAR Registers Section ......................................101

6/09—Rev. 0 to Rev. A

Added ADuC7061.............................................................. Universal

Added New Package CP-32-4........................................... Universal

Changes to Features Section............................................................1

Changes to General Description Section .......................................1

Changes to Figure 1...........................................................................4

Outline Dimensions......................................................................105

Ordering Guide.........................................................................106

Changes to Table 1 ............................................................................7

Deleted Endnote to Table 2............................................................10

Changes to Endnotes, Table 3 and Table 4...................................11

Changes to Endnotes, Table 5........................................................12

Changes to Endnotes, Table 6........................................................13

Changes to Figure 7 and Table 8 ...................................................15

Added Figure 8 and Table 9, Renumbered Sequentially............18

Changes to Flash EE/Control Interface Section..........................23

Change to Code 0x04 Description, Table 15...............................24

Change to Bit 31 Description, Table 16........................................25

Changes to Table 17 ........................................................................27

Changes to Table 19 T0CLRI and Table 20..................................28

Changes to Endnote, Table 21 .......................................................29

Change to SPITX Default Value, Table 25...................................30

Changes to External Clock Selection Section .............................33

Changes to ADC Circuit Information Section............................36

Change to Column Heading Table 35 ..........................................37

Change to Bit 6 Description, Table 39..........................................40

Change to Bit 12 Description, Table 43........................................44

Changes to Primary Channel ADC Data Register Section

and Auxiliary Channel ADC Data Register Section ..................48

Change to Table 59 and Figure 17.................................................51

Changes to Using the DAC Section .............................................. 55

Changes to Nonvolatile Flash/EE Memory Section and

Programming Section.....................................................................56

Changes to Vectored Interrupt Controller (VIC) Section.........59

Changes to Priority Registers Section ..........................................60

Change to Table 73..........................................................................61

Changes to Figure 23......................................................................65

Changes Table 78.............................................................................66

Changes to Figure 24 and Table 79 ............................................... 68

Changes to Timer2 Interface Section and Figure 25 ..................69

Changes to Timer3 Capture Register Section .............................71

Change to Bits[16:12] Description, Table 81...............................72

Changes Pulse-Width Modulator General Overview Section,

Table 82, and Figure 26...................................................................73

Changes to Table 84 Column Headings.......................................75

Changes to Table 92 ........................................................................82

Changes to Bit 1, Table 102............................................................90

Changes to Bit 11 Description, Table 105 ....................................95

Changes to SPIMDE Bit Description, Table 106.........................97

Updated Outline Dimensions......................................................103

Changes to Ordering Guide.........................................................104

4/09—Revision 0: Initial Version

Rev. C | Page 3 of 108

ADuC7060/ADuC7061

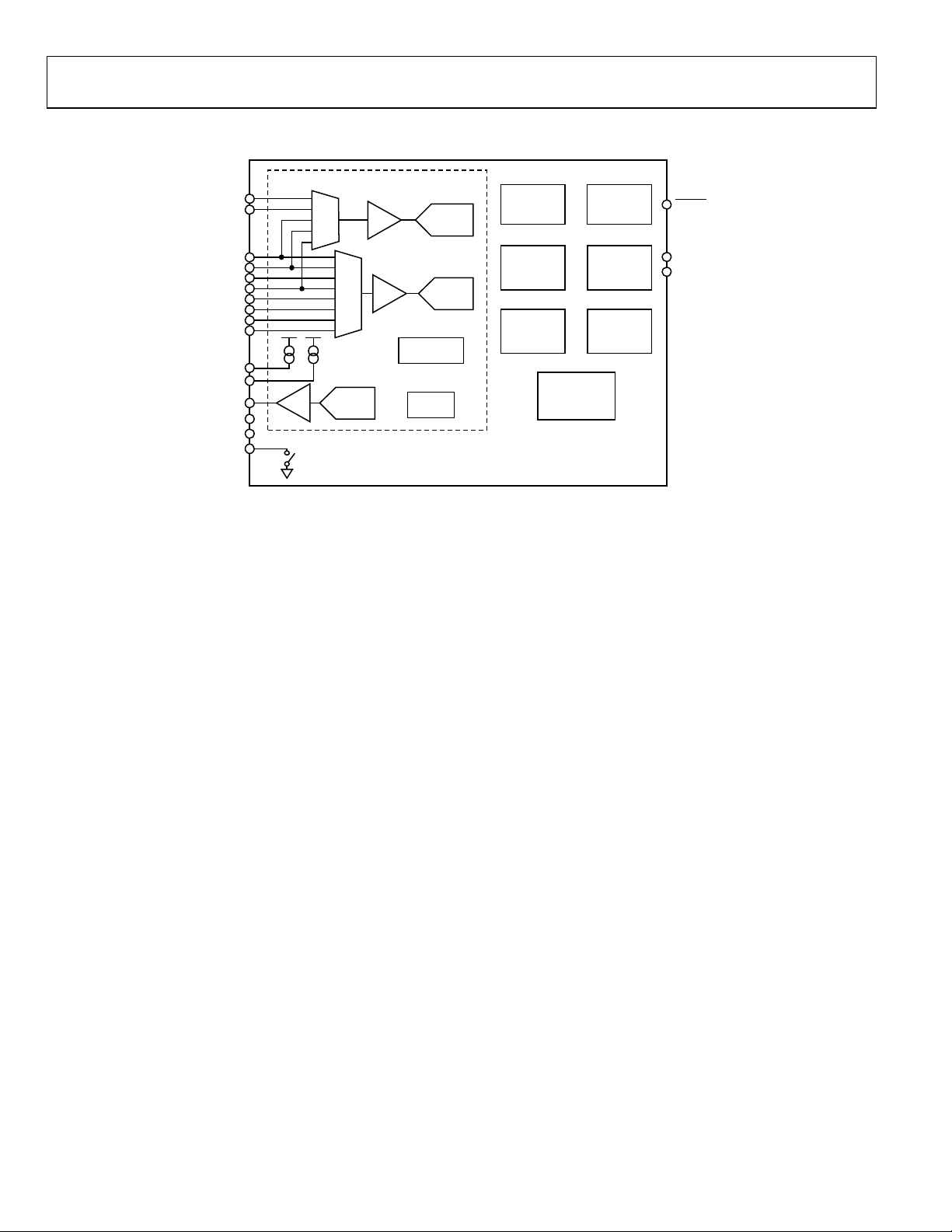

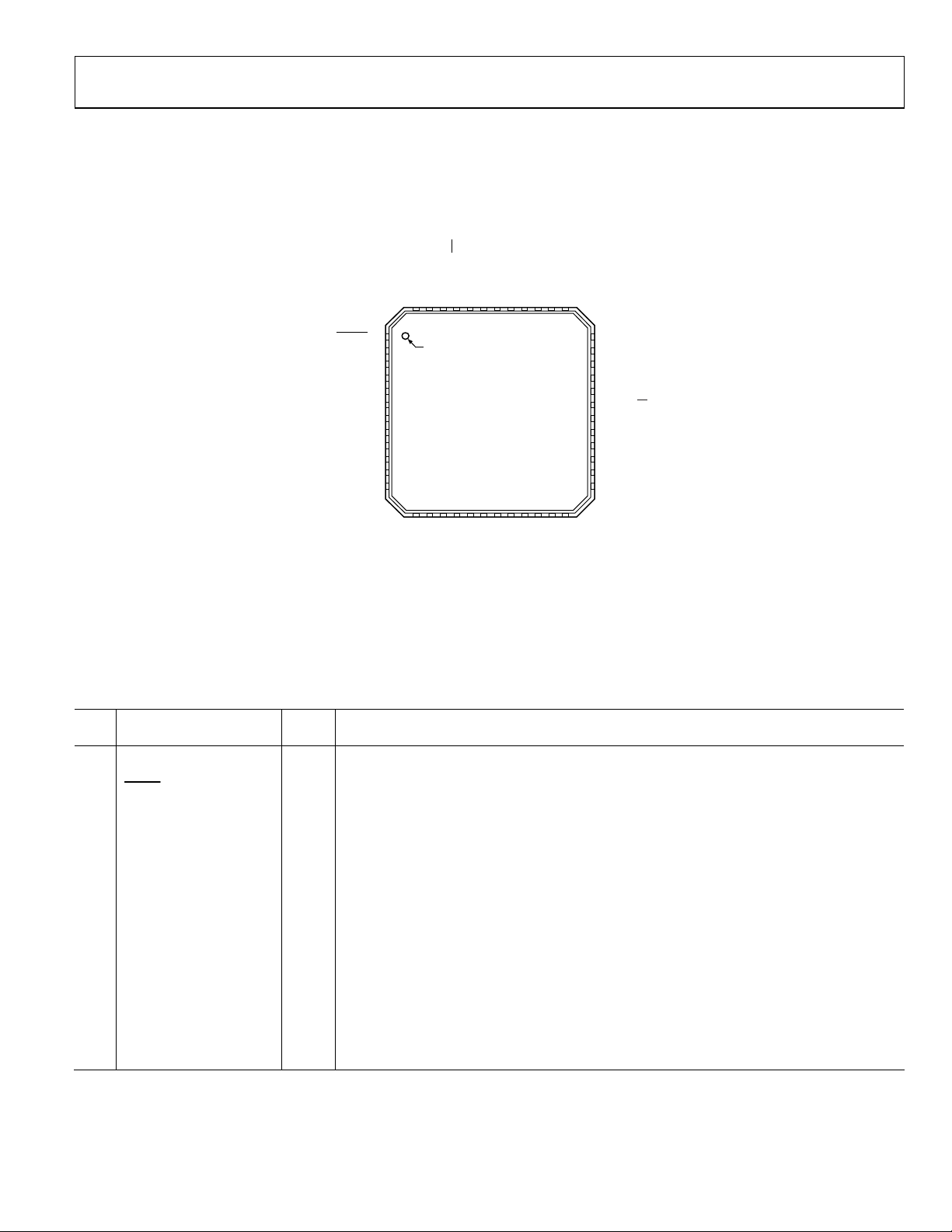

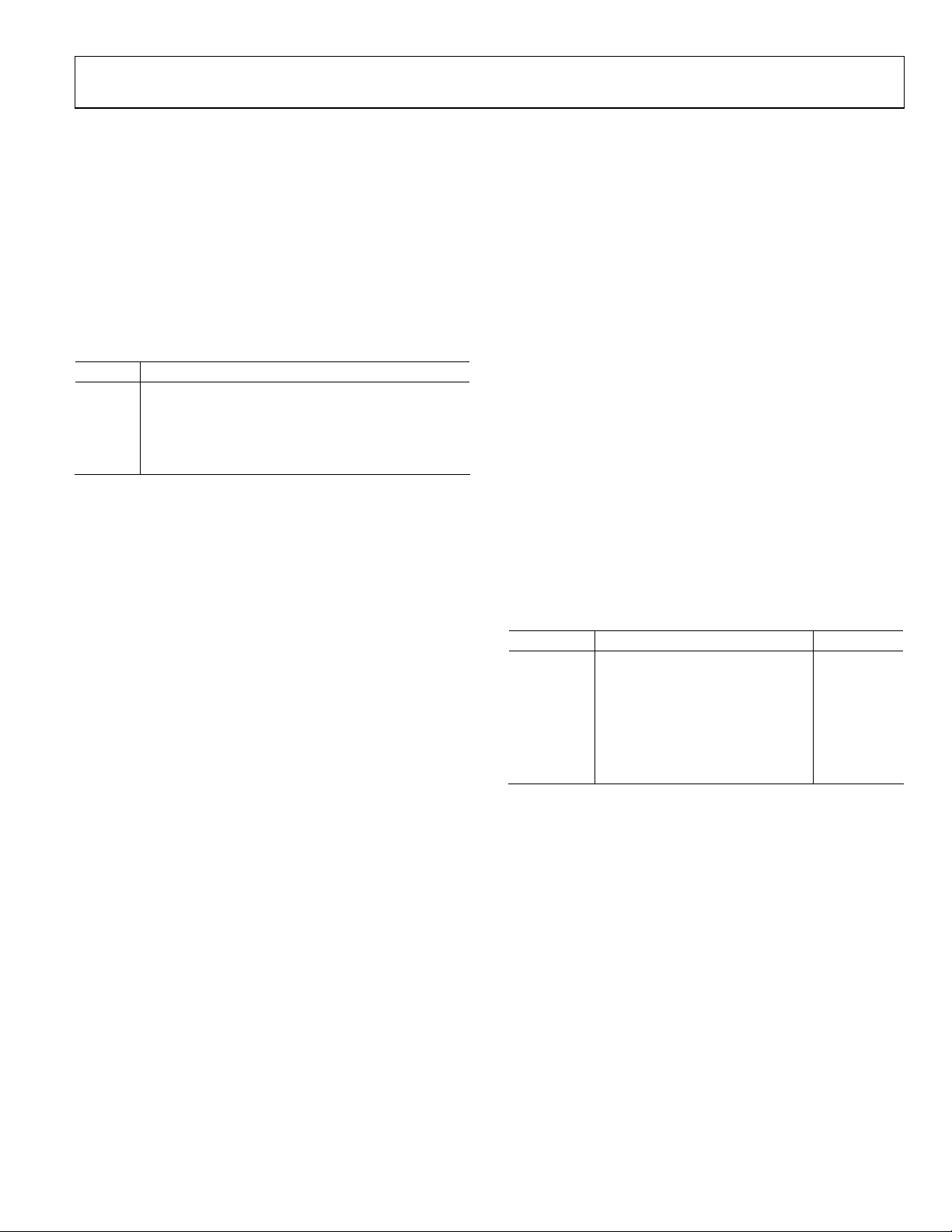

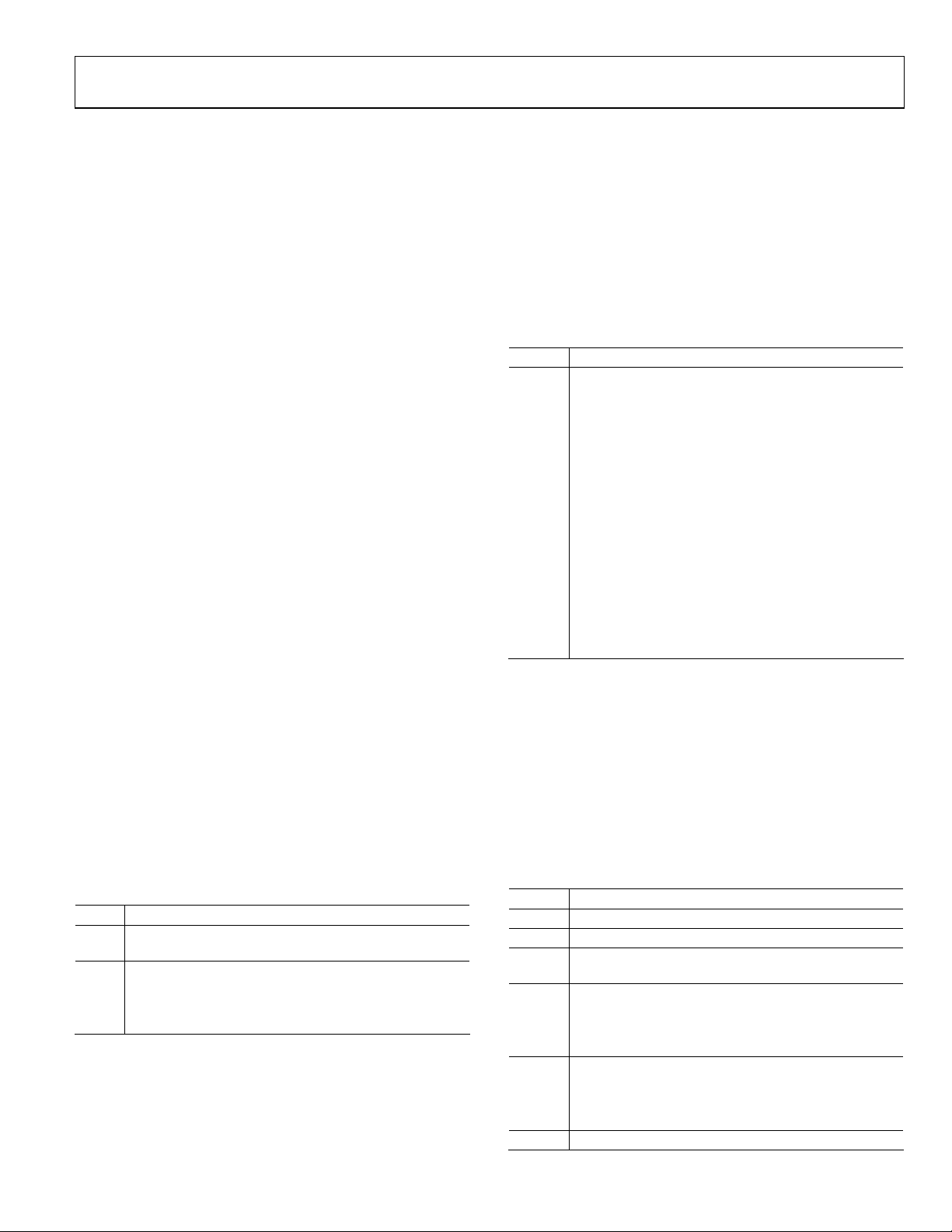

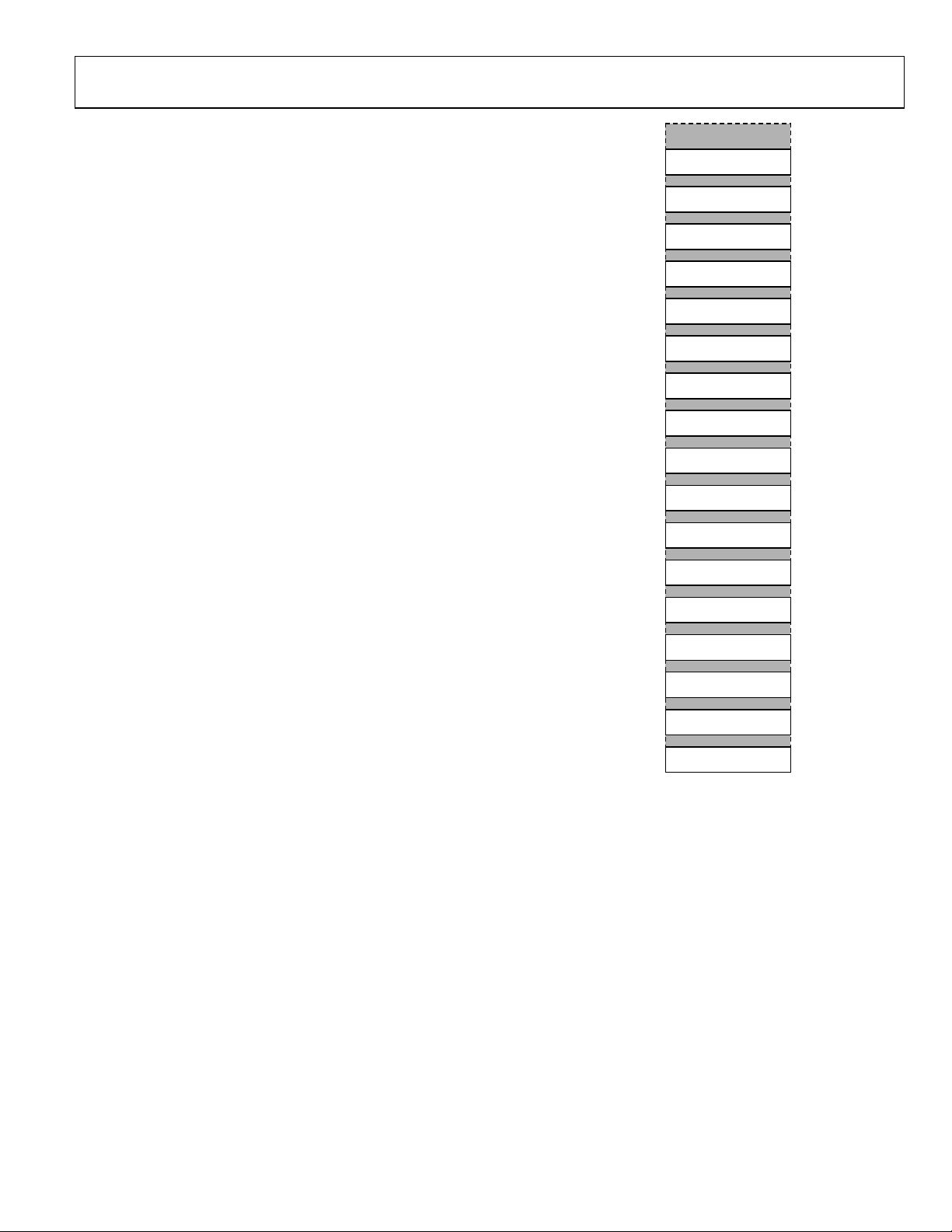

FUNCTIONAL BLOCK DIAGRAM

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC6

ADC7

ADC8

ADC9

IEXC0

IEXC1

DAC0

VREF+

VREF–

GND_SW

PRECISIO N ANALOG P ERIPHERALS

MUX

BUF

MUX

14-BIT

DAC

PGA

BUF

PRECISION

REFERENCE

TEMP

SENSOR

24-BIT

Σ-∆ ADC

24-BIT

Σ-∆

ADC

POR

ARM7TDMI

MCU

10MHz

4× TIME RS

WDT

W/U TIMER

PWM

CONTROL LER)

(VECTORED

INTERRUPT

MEMORY

32kB FLASH

4kB RAM

ON-CHIP

OSC (3%)

PLL

GPIO PORT

UART PORT

SPI PORT

2

C PORT

I

VIC

ADuC7060/

ADuC7061

RESET

XTALI

XTALO

07079-001

Figure 1.

Rev. C | Page 4 of 108

ADuC7060/ADuC7061

SPECIFICATIONS

ELECTRICAL SPECIFICATIONS

VDD = 2.5 V ± 5%, VREF+ = 1.2 V, VREF− = GND, f

specifications T

= −40°C to +125°C, unless otherwise noted. Output noise specifications can be found in Ta b le 3 6 (primary ADC) and

A

Tabl e 38 (ADC auxiliary channel).

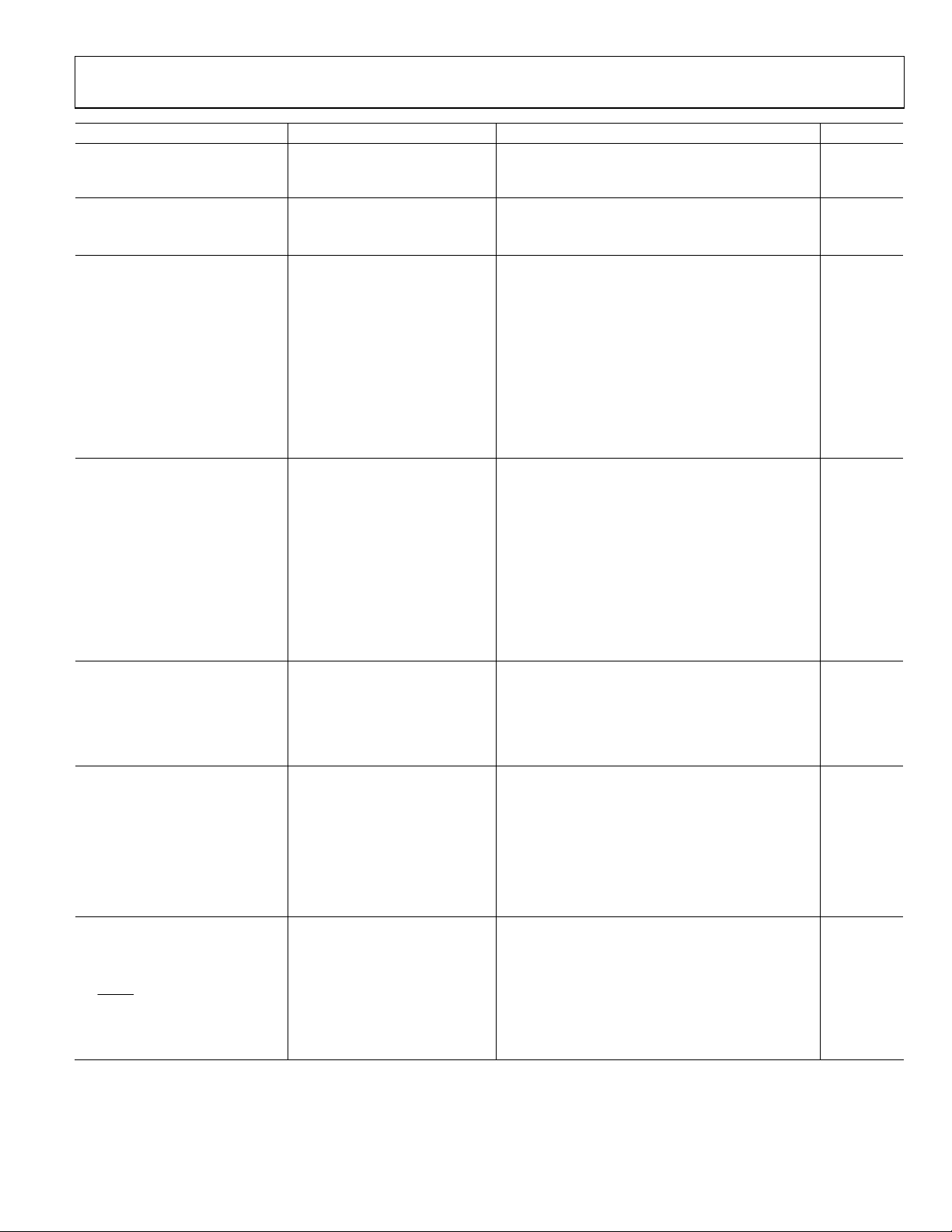

Table 1. ADuC706x Specifications

Parameter Test Conditions/Comments Min Typ Max Unit

ADC SPECIFICATIONS

For all ADC specifications,

assume normal operating mode

unless specifically stated

otherwise

Conversion Rate1

Chop off, ADC normal operating

mode

Chop on, ADC normal operating

mode

Chop on, ADC low power mode 1 650 Hz

Main Channel

No Missing Codes1 Chop off (f

Chop on (f

Integral Nonlinearity

Offset Error

3, 4

1, 2

Gain = 4 ±15 ppm of FSR

Chop off, offset error is in the

order of the noise for the pro-

grammed gain and update rate

following calibration

Offset Error

Offset Error Drift vs.

Temperature

Full-Scale Error

Full-Scale Error

1, 3, 4

Chop on −2.7 ±0.5 +2.7 V

5

Chop off (with gain ≤ 64) 650/PGA_GAIN nV/°C

Chop on (with gain ≤ 64) 10 nV/°C

1, 6 , 7 , 8

6, 8

Normal mode −1 ±0.5 +1 mV

Low power mode −2 ±1.0 +2 mV

Gain Drift vs. Temperature9 5 ppm/°C

PGA Gain Mismatch Error ±0.1 %

Power Supply Rejection1 Chop on, ADC = 1 V (gain = 1) 65 dB

Chop on, ADC = 7.8 mV (gain =

128)

Chop off, ADC = 1 V (gain = 1) 56 65 dB

Auxiliary Channel

No Missing Codes

1

Chop off (f

Chop on (f

Integral Nonlinearity1 ±15 ppm of FSR

Offset Error

Offset Error

Offset Error Drift vs.

Temperature

4

1, 4

Chop off −120 ±30 +100 V

Chop on −1.5 ±0.5 +3.2 V

5

Chop off 200 nV/°C

Chop on 10 nV/°C

Full-Scale Error

Full-Scale Error

1, 6, 7, 8

Normal mode −1 ±0.5 +1 mV

1, 6, 8

Low power mode −2 ±1.0 +2 mV

Gain Drift vs. Temperature9 3 ppm/°C

Power Supply Rejection1 Chop on, ADC = 1 V 55 65 dB

Chop off, ADC = 1 V 53 65 dB

= 10.24 MHz driven from an external 32.768 kHz watch crystal or on-chip oscillator, all

CORE

50 8000 Hz

4 2600 Hz

≤ 1 kHz) 24 Bits

ADC

≤ 666 Hz) 24 Bits

ADC

−27 ±8 +27 V

84.7 113 dB

≤ 1 kHz) 24 Bits

ADC

≤ 666 Hz) 24 Bits

ADC

Rev. C | Page 5 of 108

ADuC7060/ADuC7061

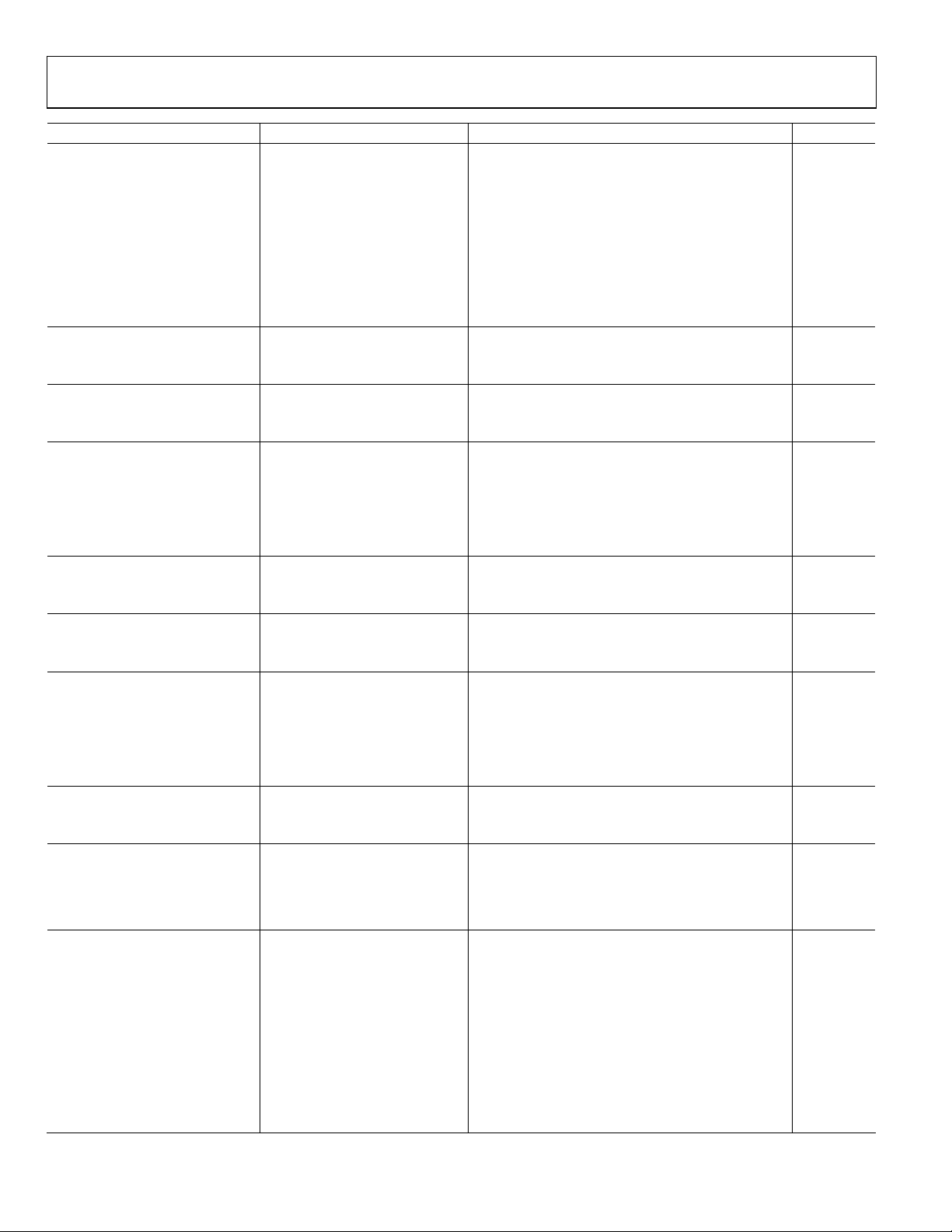

Parameter Test Conditions/Comments Min Typ Max Unit

ADC SPECIFICATIONS: ANALOG

Internal V

INPUT

Main Channel

Absolute Input Voltage Range Applies to both VIN+ and VIN− 0.1 VDD − 0.7 V

Input Voltage Range Gain = 11 0 1.2 V

Gain = 2

Gain = 4

Gain = 81 0 150 mV

Gain = 161 0 75 mV

Gain = 321 0 37.5 mV

Gain = 641 0 18.75 mV

Gain = 1281 0 9.375 mV

Common Mode Voltage, VCM

= (AIN(+) + AIN(−))/2,

V

CM

gain = 4 to 128

Input Leakage Current

1

ADC0 and ADC1 10 181 nA

ADC2, ADC3, ADC4, and ADC5 15 301 nA

ADC6, ADC7, ADC8, and ADC9,

VREF+, VREF−

Common-Mode Rejection DC1

On ADC Input ADC = 7.8 mV 113 dB

ADC = 1 V

Common-Mode Rejection

50 Hz/60 Hz

1

50 Hz/60 Hz ± 1 Hz, 16.6 Hz and

50 Hz update rate, chop on

ADC = 7.8 mV, range ± 20 mV 95 dB

ADC = 1 V, range ± 1.2 V 90 dB

Normal-Mode Rejection

50 Hz/60 Hz

1

On ADC Input

50 Hz/60 Hz ± 1 Hz, 16.6 Hz f

chop on

50 Hz/60 Hz ± 1 Hz, 16.6 Hz f

chop off

Auxiliary Channel

Absolute Input Voltage

Range

1

Buffer enabled 0.1 AVDD − 0.1 V

Buffer disabled AGND AVDD V

Input Voltage Range Range-based reference source 0 1.2 V

Common-Mode Rejection DC1

On ADC Input ADC = 1 V

Common-Mode Rejection

50 Hz/60 Hz

1

50 Hz/60 Hz ± 1 Hz, 16.6 Hz and

50 Hz update rate, chop on

ADC = 1 V, range ± 1.2 V 90 dB

Normal-Mode Rejection

50 Hz/60 Hz

1

On ADC Input

50 Hz/60 Hz ± 1 Hz, 16.6 Hz f

chop on

50 Hz/60 Hz ± 1 Hz, 16.6 Hz f

chop off

VOLTAGE REFERENCE

ADC Precision Reference

Internal V

Initial Accuracy

Reference Temperature

Coefficient (Tempco)

1.2 V

REF

1, 10

Measured at TA = 25°C −0.1 +0.1 %

−20 ±10 +20 ppm/°C

Power Supply Rejection1 70 dB

= 1.2 V

REF

1

1

0 600 mV

0 300 mV

0.5 V

1

15 25

1

95 dB

nA

75 dB

,

ADC

67 dB

,

ADC

1

87 dB

75 dB

,

ADC

67 dB

,

ADC

Rev. C | Page 6 of 108

ADuC7060/ADuC7061

Parameter Test Conditions/Comments Min Typ Max Unit

External Reference Input

V

11

Range

REF

Divide-by-2 Initial Error

DAC CHANNEL SPECIFICATIONS RL = 5 kΩ, CL = 100 pF

Voltage Range 0 V

0 AVDD − 0.2 V

DAC 12-BIT MODE

DC Specifications12

Resolution 12 Bits

Relative Accuracy ±2 LSB

Differential Nonlinearity Guaranteed monotonic ±0.2 ±1 LSB

Offset Error 1.2 V internal reference ±2 ±15 mV

Gain Error V

AVDD range ±1 %

Gain Error Mismatch 0.1

DAC 16-BIT MODE1 Only monotonic to 14 bits

DC Specifications13

Resolution 14 Bits

Relative Accuracy For 14-bit resolution ±3 LSB

Differential Nonlinearity Guaranteed monotonic (14 bits) ±0.5 ±1 LSB

Offset Error 1.2 V internal reference ±2 ±15 mV

Gain Error V

AVDD range ±1 %

Gain Error Mismatch 0.1

DAC AC CHARACTERISTICS

Voltage Output Settling Time 10 µs

Digital-to-Analog Glitch Energy

TEMPERATURE SENSOR

1, 14

After user calibration

Accuracy

Voltage Output at 0°C Typical value 96 mV

Voltage Tempco Typical value 0.28 mV/°C

Thermal Impedance 48-lead LFCSP 27 °C/W

48-lead LQFP 55 °C/W

32-lead LFCSP 30 °C/W

POWER-ON RESET (POR)

POR Trip Level1 Refers to voltage at DVDD pin

Power-on level 2.0 V

Power-down level 2.25 V

RESET Timeout from POR Maximum supply ramp between

0.1 AVDD V

1

0.1 %

V

REF

range (reference = 1.2 V) ±1 %

REF

% of full

scale on

DAC

range (reference = 1.2 V) ±1 %

REF

% of full

scale on

DAC

1 LSB change at major carry

±20 nV-sec

(where maximum number of

bits simultaneously change in

the DAC0DAT register)

MCU in power-down or standby

±4 °C

mode

128 ms

1.8 V and 2.25 V; after POR trip,

DVDD must reach 2.25 V within

this time limit

Rev. C | Page 7 of 108

ADuC7060/ADuC7061

Parameter Test Conditions/Comments Min Typ Max Unit

EXCITATION CURRENT SOURCES

Output Current

Available from each current

source

Initial Tolerance at 25°C ±5 %

Drift1 0.06 %/°C

Initial Current Matching at 25°C

Matching between both current

sources

Drift Matching1 20 ppm/°C

Line Regulation (AVDD)1 AVDD = 2.5 V ± 5% 0.2 %/V

Output Compliance1 AVDD − 0.7 V AGND − 30 mV V

WATCHD OG T IME R ( WDT )

Timeout Period

1

32.768 kHz clock, 256 prescale 0.008 512 sec

Timeout Step Size 7.8 ms

FLASH/EE MEMORY

1

Endurance15 10,000 Cycles

Data Retention

16

20 Years

DIGITAL INPUTS All digital inputs except NTRST

Input Leakage Current Input (high) = DVDD ±1 ±10 µA

Input Pull-Up Current Input (low) = 0 V 10 20 80 µA

Input Capacitance 10 pF

Input Leakage Current NTRST only: input (low) = 0 V ±1 ±10 µA

Input Pull-Down Current NTRST only: input (high) = DVDD 30 55 100 µA

LOGIC INPUTS

1

All logic inputs

Input Low Voltage (VINL) 0.4 V

Input High Voltage (VINH) 2.0 V

LOGIC OUTPUTS1 All logic outputs except XTALO

Output Low Voltage (VOL) I

Output High Voltage (VOH) I

CRYSTAL OSCILLATOR

1

= 1.6 mA 0.6 V

SOURCE

= 1.6 mA 2.0 V

SOURCE

Logic Inputs, XTALI Only

Input Low Voltage (VINL) 0.8 V

Input High Voltage (VINH) 1.7 V

XTALI Capacitance 12 pF

XTALO Capacitance 12 pF

ON-CHIP OSCILLATORS

Oscillator 32,768 kHz

Accuracy −3 +3 %

MCU CLOCK RATE

Eight programmable core clock

selections within this range:

binary divisions 1, 2, 4, 8 . . . 64, 128

Using an External Clock to

0.08 10.24 MHz

P2.0/EXTCLK Pin

MCU START-UP TIME

At Power-On

Includes kernel power-on

execution time

After Reset Event

Includes kernel power-on

execution time

From MCU Power-Down

PLL On

Wake-Up from Interrupt CD = 0 4.8 s

PLL Off

Wake-Up from Interrupt CD = 0 66 s

Internal PLL Lock Time 1 ms

200 1000 A

±0.5 %

0.08 1.28 10.24 MHz

134 ms

5 ms

Rev. C | Page 8 of 108

ADuC7060/ADuC7061

Parameter Test Conditions/Comments Min Typ Max Unit

POWER REQUIREMENTS

Power Supply Voltages

DVDD (±5%) 2.375 2.5 2.625 V

AVDD (±5%) 2.375 2.5 2.625 V

Power Consumption

IDD (MCU Normal Mode)17

MCU clock rate = 10.24 MHz,

ADC0 on

MCU clock rate = 640 kHz,

ADC0 on, G = 4, ADC1/DAC off,

SPI on; POWCON1 = 0x4

Full temperature range 3.1 mA

Reduced temperature range

−40°C to +85°C

1

IDD (MCU Powered Down)1 Full temperature range 55 350 µA

Reduced temperature range

−40°C to +85°C

IDD (Primary ADC)

PGA enabled, normal mode/low

power mode; current is

dependent on gain setting

ADC0 on, G = 1, normal mode 0.03 mA

ADC0 on, G = 4, normal mode 0.44 mA

ADC0 on, G = >128, normal mode 0.63 mA

IDD (Auxiliary ADC) Normal mode/low power mode 0.35/0.1 mA

IDD (DAC) DAC0CON = 0x10 0.33 mA

PWM 0.34 mA

1

These numbers are not production tested but are guaranteed by design and/or characterization data at production release.

2

Valid for primary ADC gain setting of PGA = 4 to 64.

3

Tested at gain range = 4 after initial offset calibration.

4

Measured with an internal short. A system zero-scale calibration removes this error.

5

Measured with an internal short.

6

These numbers do not include internal reference temperature drift.

7

Factory calibrated at gain = 1.

8

System calibration at a specific gain range removes the error at this gain range.

9

Measured using an external reference.

10

Measured using the box method.

11

References up to AVDD are accommodated by setting ADC0CON Bit 12.

12

Reference DAC linearity is calculated using a reduced code range of 171 to 4095.

13

Reference DAC linearity is calculated using a reduced code range of 2731 to 65,535.

14

Die temperature.

15

Endurance is qualified to 10,000 cycles as per JEDEC Std. 22 Method A117 and measured at −40°C, +25°C, and +125°C. Typical endurance at 25°C is 170,000 cycles.

16

Retention lifetime equivalent at junction temperature (TJ) = 85°C as per JEDEC Std. 22 Method A117. Retention lifetime derates with junction temperature.

17

Typical additional supply current consumed during Flash/EE memory program and erase cycles is 7 mA and 5 mA, respectively.

6 10 mA

2.74 mA

55 120 µA

0.6/0.3 mA

Rev. C | Page 9 of 108

ADuC7060/ADuC7061

S

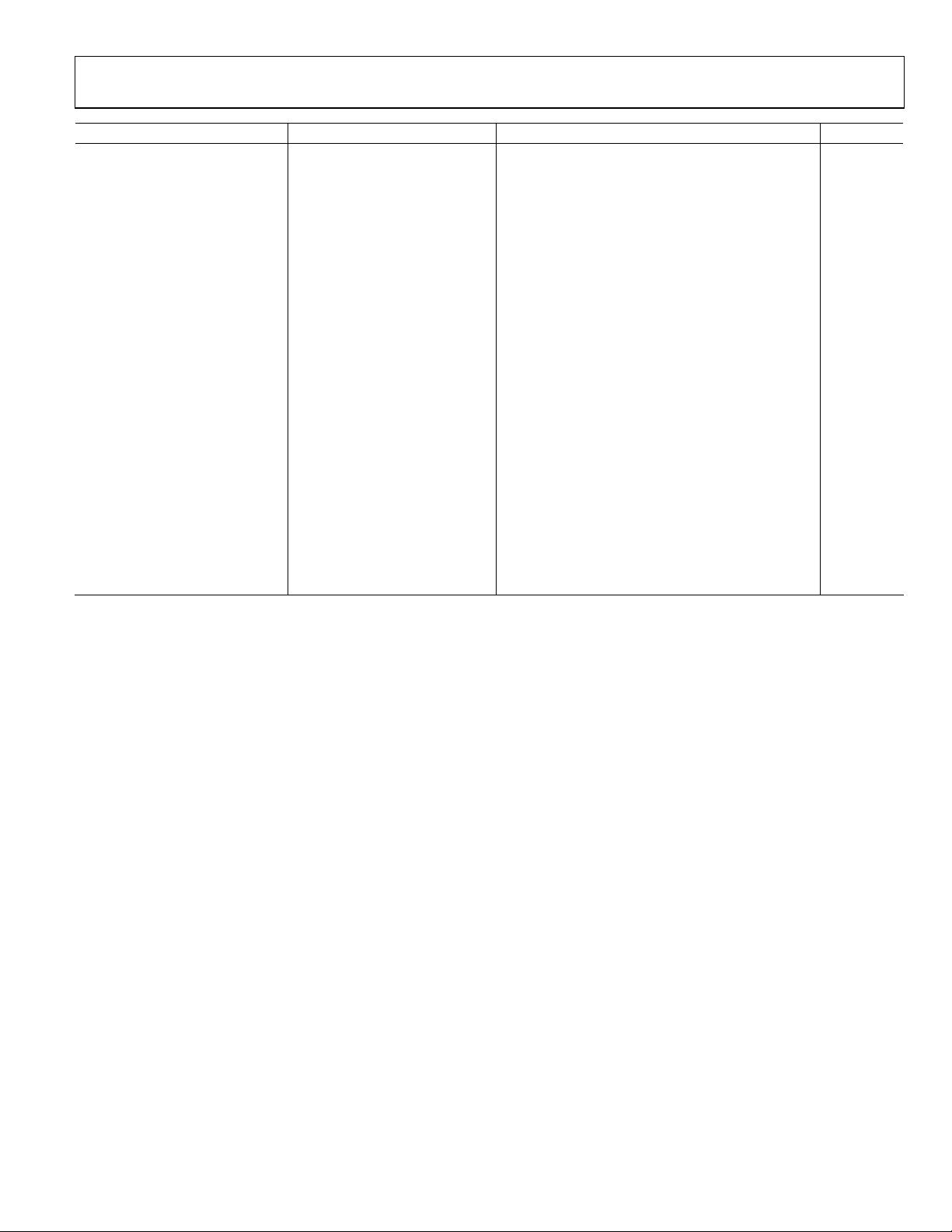

TIMING SPECIFICATIONS

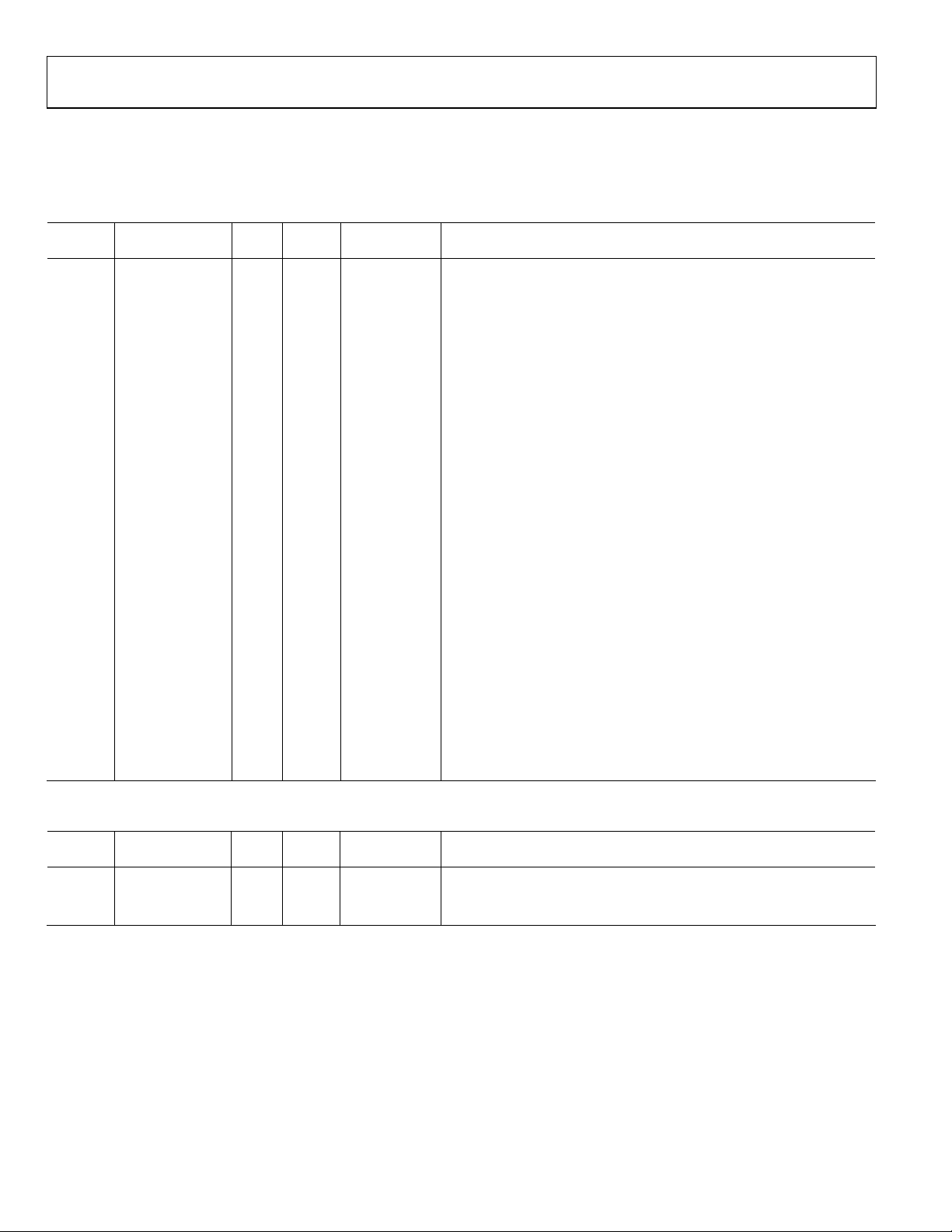

I2C Timing

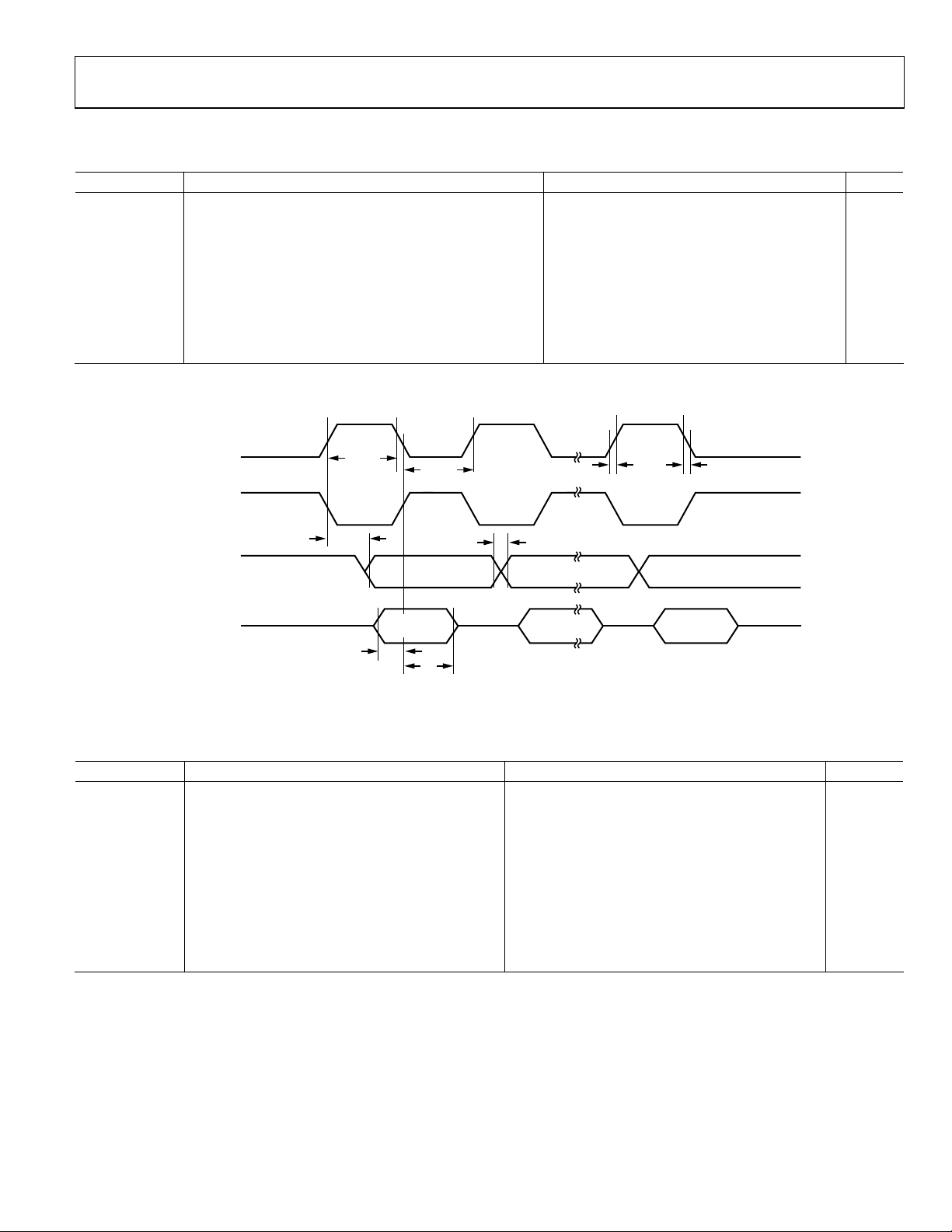

Table 2. I2C® Timing in Standard Mode (100 kHz)

Slave

Parameter Description Min Max Unit

tL SCLOCK low pulse width 4.7 µs

tH SCLOCK high pulse width 4.0 ns

t

Start condition hold time 4.0 µs

SHD

t

Data setup time 250 ns

DSU

t

Data hold time 0 3.45 µs

DHD

t

Setup time for repeated start 4.7 µs

RSU

t

Stop condition setup time 4.0 µs

PSU

t

Bus-free time between a stop condition and a start condition 4.7 µs

BUF

tR Rise time for both CLOCK and SDATA 1 µs

tF Fall time for both CLOCK and SDATA 300 ns

t

BUF

DATA (I/O)

SCLK (I)

t

PSU

PS

STOP

CONDITIO N

CONDITION

t

START

MSB LSB ACK MSB

DSU

t

SHD

t

DHD

Figure 2. I

t

H

t

L

2

C Compatible Interface Timing

t

DSU

t

RSU

t

DHD

REPEATED

START

S(R)

t

R

t

F

t

R

1982–71

t

F

7079-029

Rev. C | Page 10 of 108

ADuC7060/ADuC7061

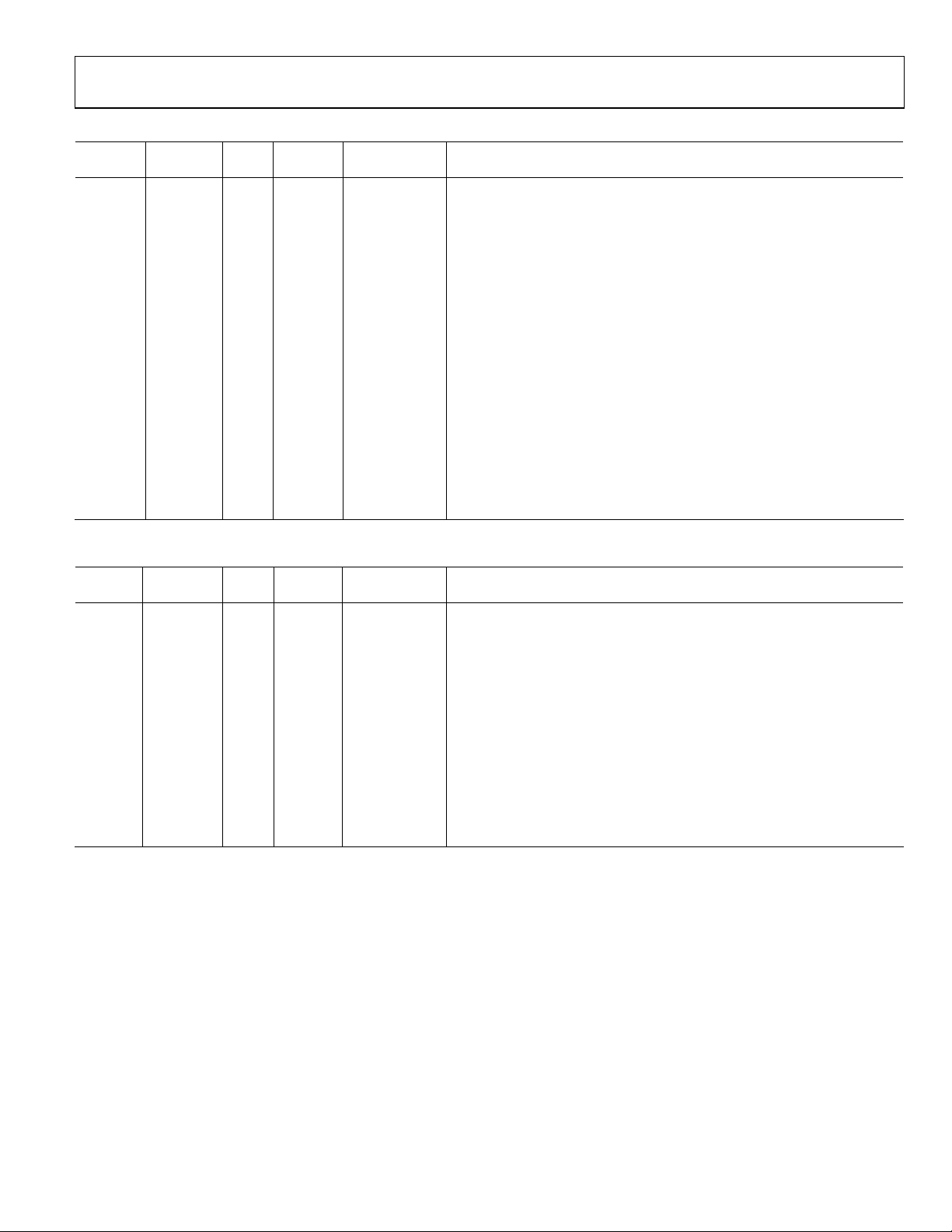

SPI Timing

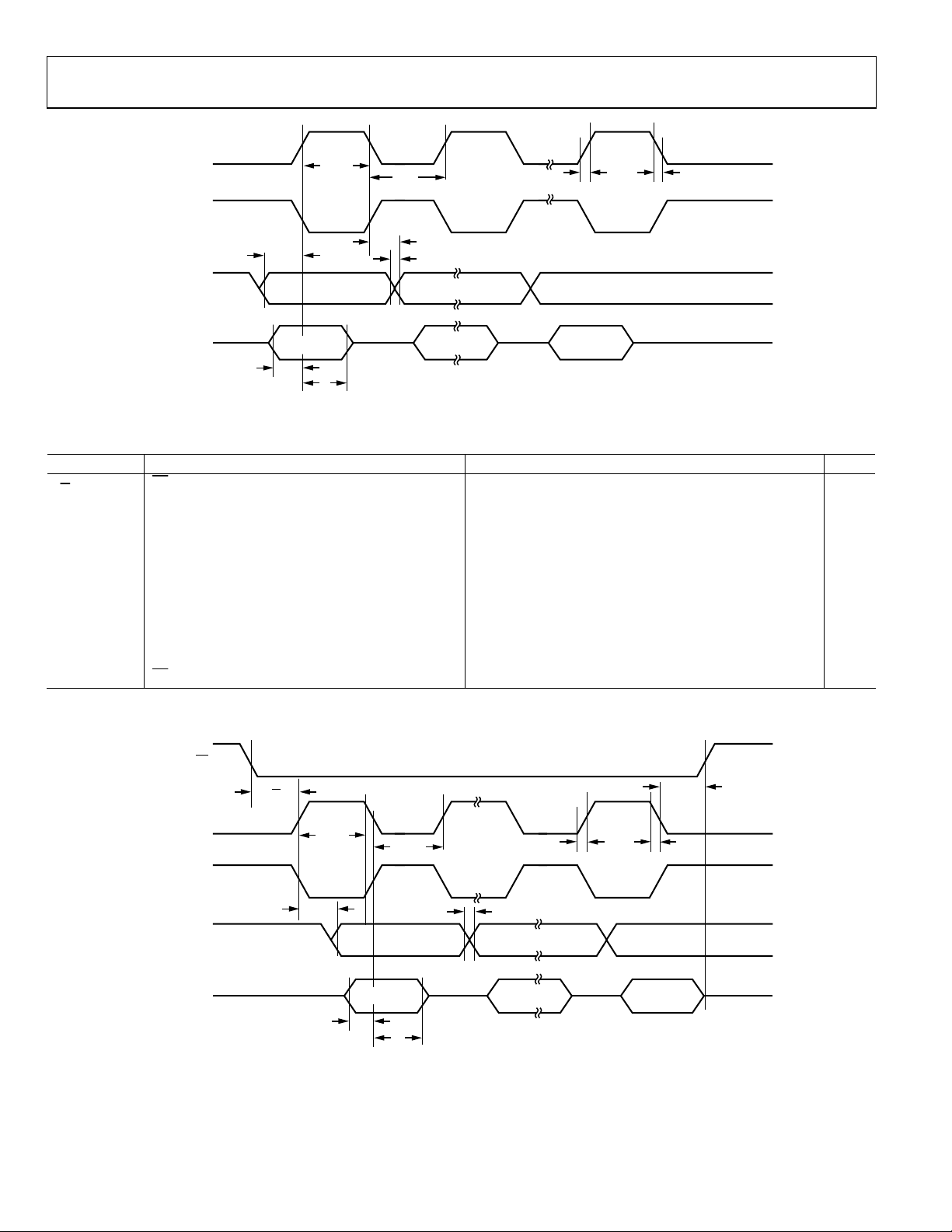

Table 3. SPI Master Mode Timing (Phase Mode = 1)

Parameter Description Min Typ Max Unit

tSL SCLOCK low pulse width (SPIDIV + 1) × t

tSH SCLOCK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLOCK edge 25 ns

DAV

t

Data input setup time before SCLOCK edge1 1 × t

DSU

t

Data input hold time after SCLOCK edge1 2 × t

DHD

ns

UCLK

ns

UCLK

tDF Data output fall time 30 40 ns

tDR Data output rise time 30 40 ns

tSR SCLOCK rise time 30 40 ns

tSF SCLOCK fall time 30 40 ns

1

t

= 97.6 ns. It corresponds to the 10.24 MHz internal clock from the PLL.

UCLK

ns

HCLK

ns

HCLK

SCLOCK

(POLARITY = 0)

SCLOCK

(POLARITY = 1)

MOSI MSB BITS 6 TO 1 LSB

MISO MSB IN BITS 6 TO 1 LSB IN

t

SH

t

DAV

t

DSU

t

DHD

t

SL

t

DF

t

DR

t

SR

t

SF

7079-030

Figure 3. SPI Master Mode Timing (Phase Mode = 1)

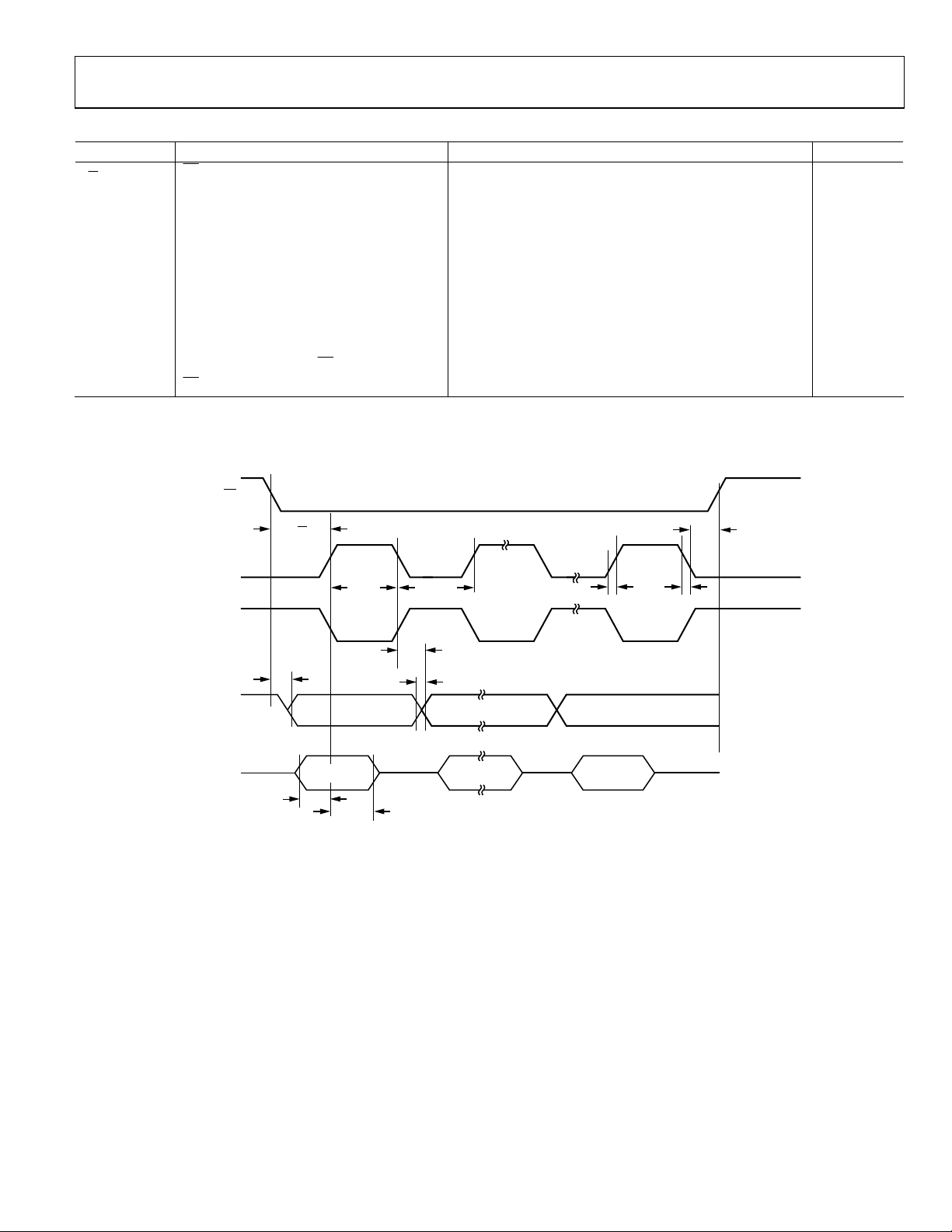

Table 4. SPI Master Mode Timing (Phase Mode = 0)

Parameter Description Min Typ Max Unit

tSL SCLOCK low pulse width (SPIDIV + 1) × t

tSH SCLOCK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLOCK edge 25 ns

DAV

t

Data output setup before SCLOCK edge 90 ns

DOSU

t

Data input setup time before SCLOCK edge1 1 × t

DSU

t

Data input hold time after SCLOCK edge1 2 × t

DHD

ns

UCLK

ns

UCLK

ns

HCLK

ns

HCLK

tDF Data output fall time 30 40 ns

tDR Data output rise time 30 40 ns

tSR SCLOCK rise time 30 40 ns

tSF SCLOCK fall time 30 40 ns

1

t

= 97.6 ns. It corresponds to the 10.24 MHz internal clock from the PLL.

UCLK

Rev. C | Page 11 of 108

ADuC7060/ADuC7061

SCLOCK

(POLARITY = 0)

SCLOCK

(POLARITY = 1)

t

DOSU

MOSI MSB BITS 6 TO 1 LSB

MISO MSB IN BITS 6 TO 1 LSB IN

t

DSU

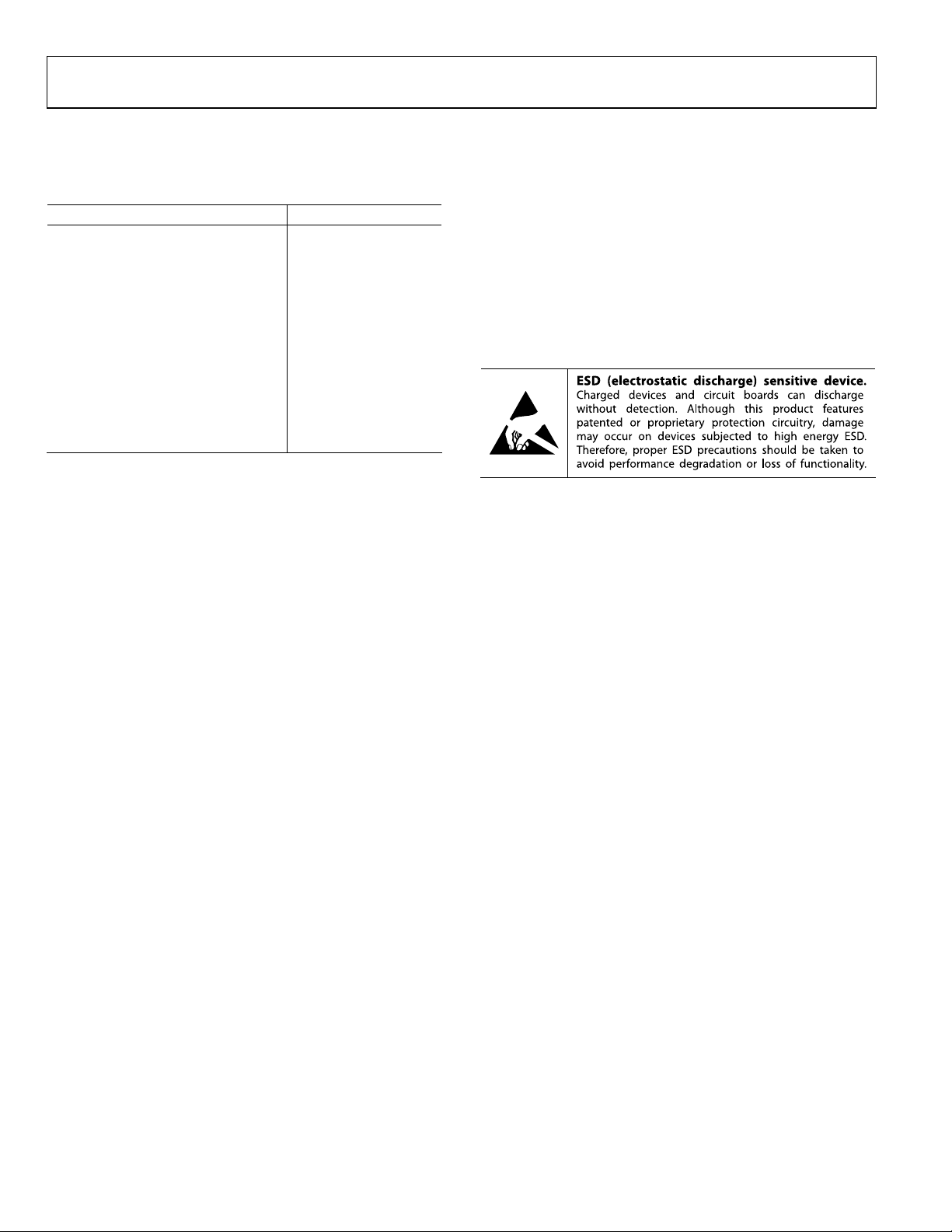

Table 5. SPI Slave Mode Timing (Phase Mode = 1)

Parameter Description Min Typ Max Unit

tCS

to SCLOCK edge1

CS

tSL SCLOCK low pulse width (SPIDIV + 1) × t

tSH SCLOCK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLOCK edge 40 ns

DAV

t

Data input setup time before SCLOCK edge1 1 × t

DSU

t

Data input hold time after SCLOCK edge1 2 × t

DHD

tDF Data output fall time 30 40 ns

tDR Data output rise time 30 40 ns

tSR SCLOCK rise time 1 ns

tSF SCLOCK fall time 1 ns

t

SFS

1

t

= 97.6 ns. It corresponds to the 10.24 MHz internal clock from the PLL.

UCLK

high after SCLOCK edge

CS

t

t

SH

DHD

t

SL

t

DAV

t

DF

t

DR

Figure 4. SPI Master Mode Timing (Phase Mode = 0)

(2 × t

) + (2 × t

HCLK

ns

UCLK

ns

UCLK

0 ns

t

SR

) ns

UCLK

t

SF

07079-031

ns

HCLK

ns

HCLK

CS

t

t

SCLOCK

(POLARITY = 0)

SCLOCK

(POLARITY = 1)

MISO MSB BITS 6 TO 1 LSB

MOSI MSB IN BITS 6 TO 1 LSB IN

CS

t

t

t

DAV

DSU

SH

t

DHD

t

SL

t

DF

t

DR

t

SR

SFS

t

SF

07079-032

Figure 5. SPI Slave Mode Timing (Phase Mode = 1)

Rev. C | Page 12 of 108

ADuC7060/ADuC7061

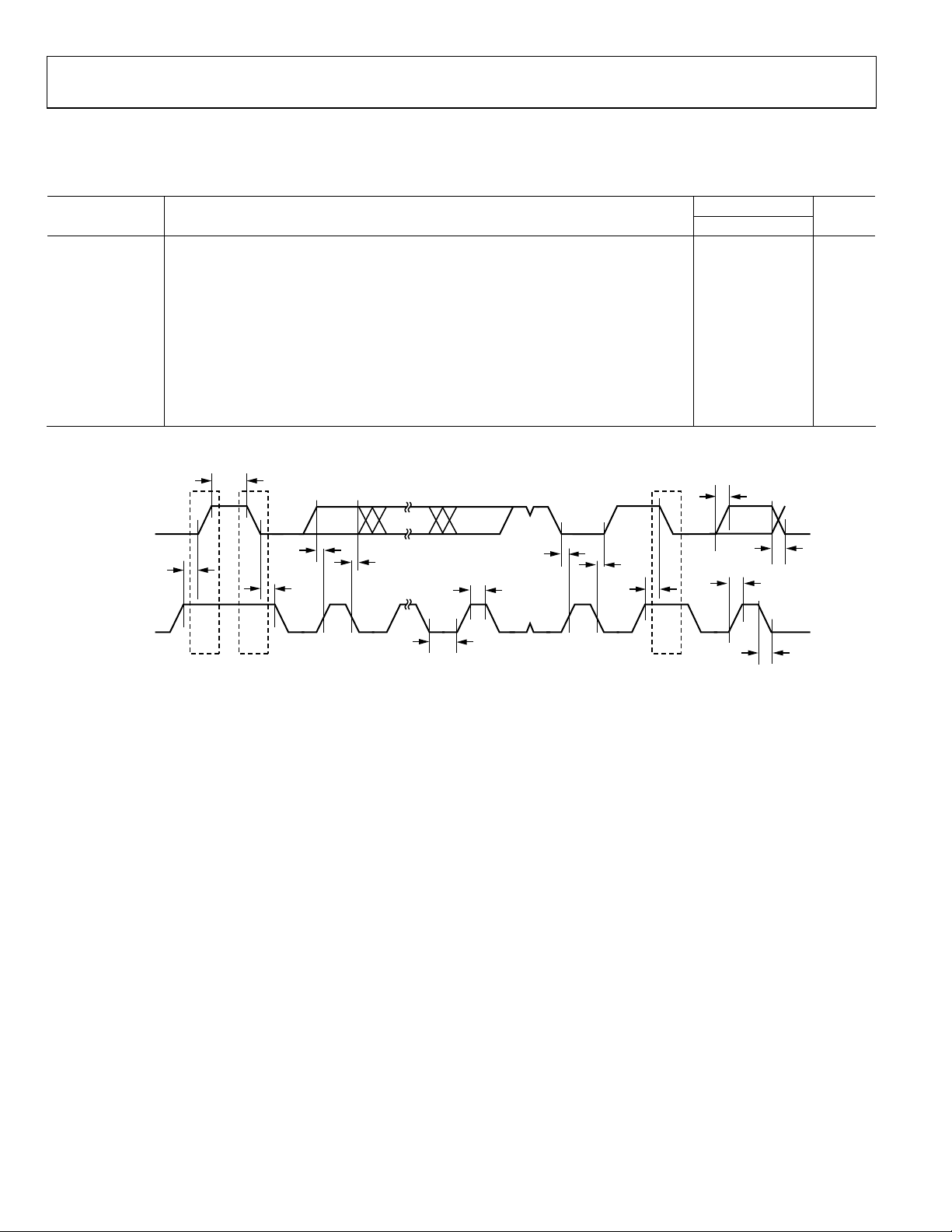

Table 6. SPI Slave Mode Timing (Phase Mode = 0)

Parameter Description Min Typ Max Unit

tCS

to SCLOCK edge1

CS

tSL SCLOCK low pulse width (SPIDIV + 1) × t

tSH SCLOCK high pulse width (SPIDIV + 1) × t

t

Data output valid after SCLOCK edge 40 ns

DAV

t

Data input setup time before SCLOCK edge1 1 × t

DSU

t

Data input hold time after SCLOCK edge1 2 × t

DHD

tDF Data output fall time 30 40 ns

tDR Data output rise time 30 40 ns

tSR SCLOCK rise time 1 ns

tSF SCLOCK fall time 1 ns

t

DOCS

t

SFS

1

t

= 97.6 ns. It corresponds to the 10.24 MHz internal clock from the PLL.

UCLK

Data output valid after CS

high after SCLOCK edge

CS

edge

CS

t

CS

SCLOCK

(POLARITY = 0)

t

SH

SCLOCK

(POLARITY = 1)

t

DAV

t

DF

MISO

t

DOCS

MSB BITS 6 TO 1 LSB

(2 × t

) + (2 × t

HCLK

ns

UCLK

ns

UCLK

) ns

UCLK

ns

HCLK

ns

HCLK

10 ns

0 ns

t

SFS

t

SL

t

DR

t

SR

t

SF

MOSI

MSB IN BIT S 6 TO 1 LSB IN

t

DSU

t

DHD

07079-033

Figure 6. SPI Slave Mode Timing (Phase Mode = 0)

Rev. C | Page 13 of 108

ADuC7060/ADuC7061

ABSOLUTE MAXIMUM RATINGS

TA = −40°C to +125°C, unless otherwise noted.

Table 7.

Parameter Rating

AGND to DGND to AVDD to DVDD −0.3 V to +0.3 V

Digital I/O Voltage to DGND −0.3 V to +3.3 V

VREF± to AGND −0.3 V to AVDD + 0.3 V

ADC Inputs to AGND −0.3 V to AVDD + 0.3 V

ESD (Human Body Model) Rating

All Pins ±2 kV

Storage Temperature 125°C

Junction Temperature

Transient 150°C

Continuous 130°C

Lead Temperature

Soldering Reflow (15 sec) 260°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. C | Page 14 of 108

ADuC7060/ADuC7061

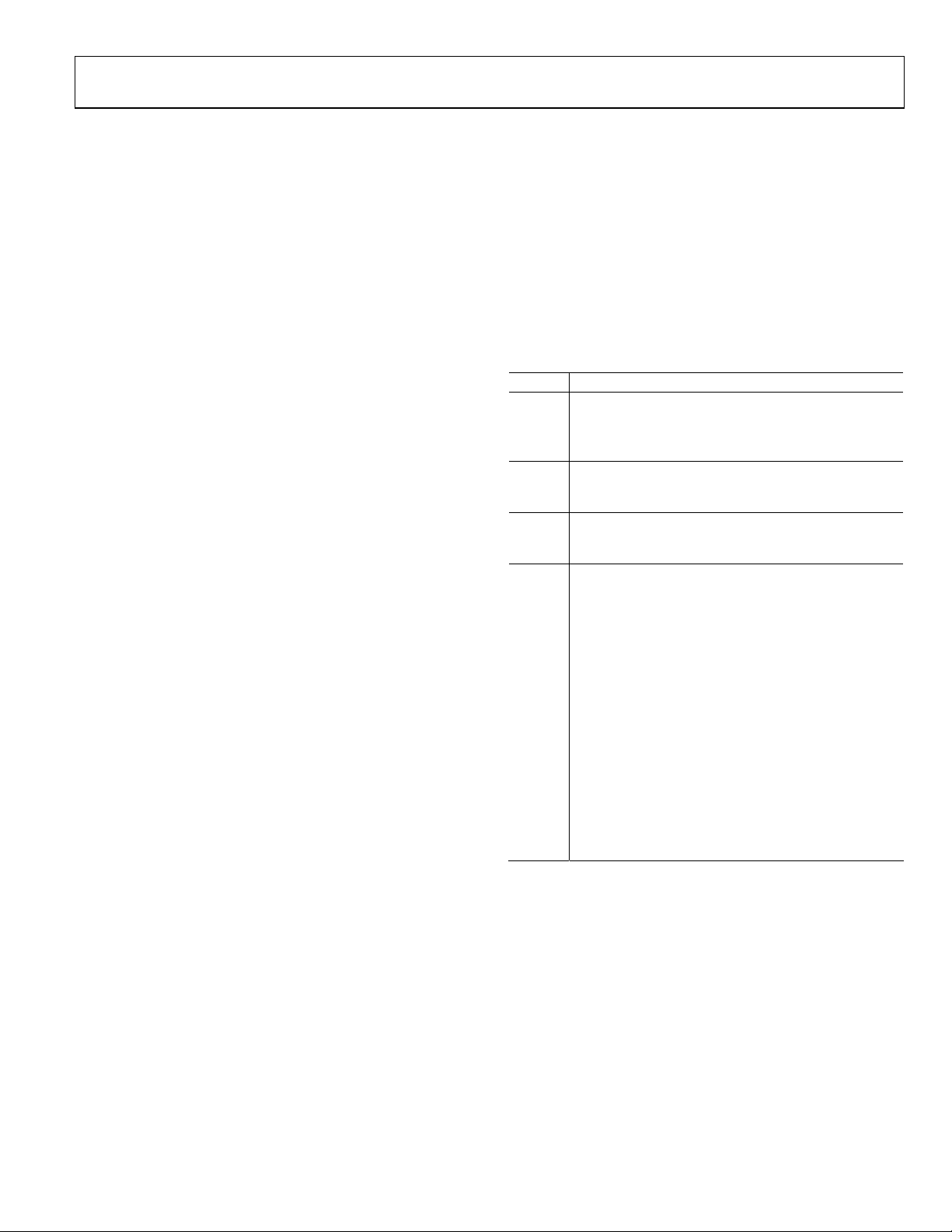

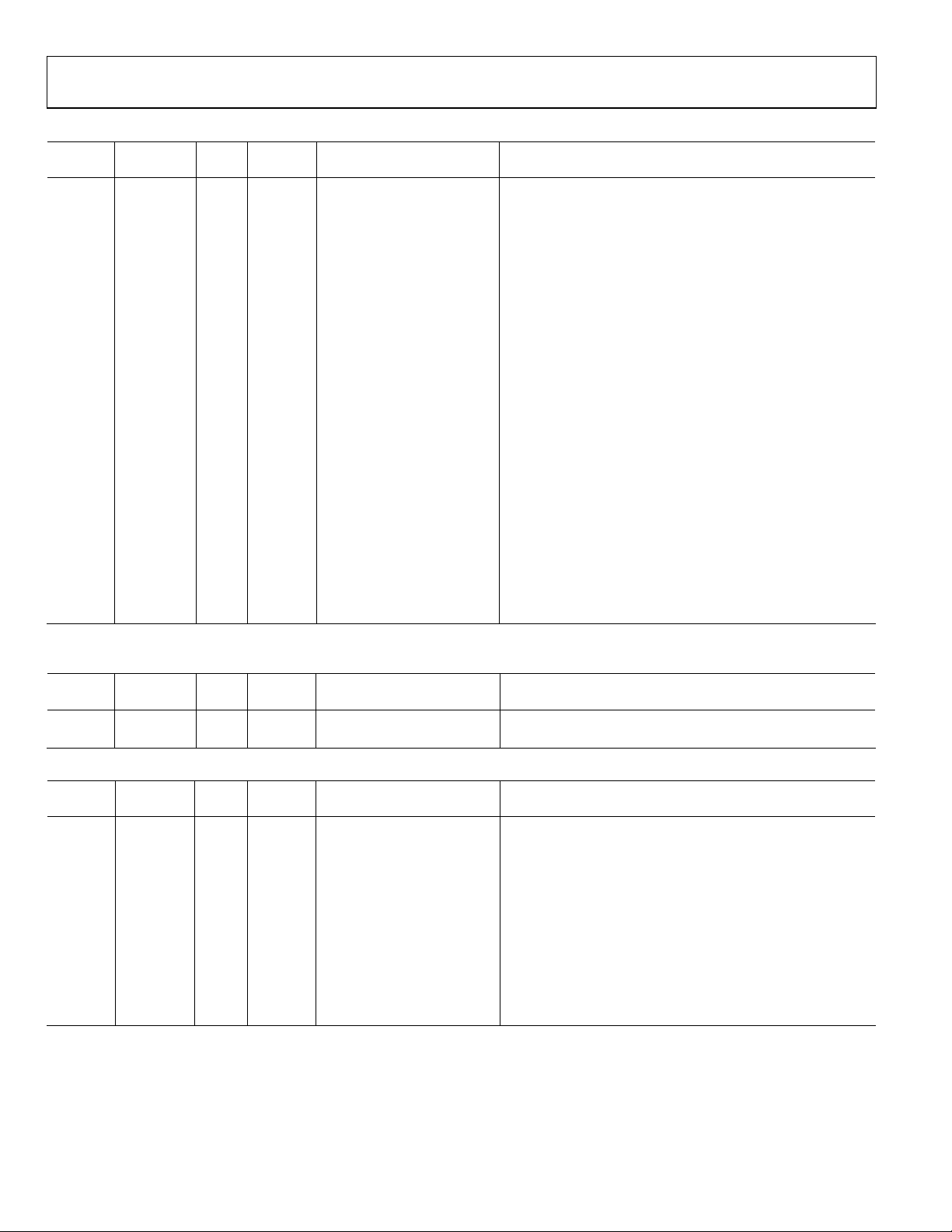

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

TRST/BM

TCK

TDI

TDO

DVDD

DGND

P2.1/IRQ3/PWM5

P1.6/PWM4

P1.5/PWM3

P1.4/PWM2

P2.0/IRQ2/PWM0/EXTCLKP0.4/IRQ0/PWM1

37

XTALI

36

XTALO

35

P0.3/MOSI/SDA

34

33

P0.2/MISO

P0.1/SCLK/SCL

32

P0.0/SS

31

30

DVDD

29

DGND

ADC9

28

ADC8

27

26

ADC7

25

ADC6

RESET

TMS

P1.0/IRQ1/SIN/T0

P1.1/SOUT

P1.2/SYNC

P1.3/TRIP

P0.5/CTS

P0.6/RTS

DVDD

DGND

DAC0

ADC5/EXT_REF2IN−

N

4847464544434241403938

1

2

3

4

5

6

7

8

9

10

11

12

PIN 1

INDICAT OR

ADuC7060

TOP VIEW

(Not to Scale)

1314151617181920212223

ADC3

ADC2

NOTES

1. THE LFCSP_VQ ONLY HAS AN EXPOSED PADDLE THAT MUST BE LEFT UNCONNECTED.

THIS DOES NOT APPLY TO THE LQFP.

ADC4/EXT_REF 2IN+

ADC1

IEXC1

ADC0

IEXC0

GND_SW

24

AVDD

AGND

VREF+

VREF−

07079-002

Figure 7. 48-Lead LQFP and 48-Lead LFCSP_VQ Pin Configuration

Table 8. ADuC7060 Pin Function Descriptions

Pin

No.

Mnemonic Type

0 EP

1

Description

Exposed Paddle. The LFCSP_VQ only has an exposed paddle that must be left unconnected.

This does not apply to the LQFP.

1

RESET

2 TMS I

I Reset. Input pin, active low. An external 1 kΩ pull-up resistor is recommended with this pin.

JTAG Test Mode Select. Input pin used for debug and download. An external pull-up resistor

(~100 kΩ) should be added to this pin.

3 P1.0/IRQ1/SIN/T0 I/O

General-Purpose Input and General Purpose Output P1.0/External Interrupt Request 1/Serial

Input/Timer0 Input. This is a multifunction input/output pin offering four functions.

4 P1.1/SOUT I/O

General-Purpose Input and General-Purpose Output P1.1/Serial Output. This is a dual function

input/output pin.

5 P1.2/SYNC I/O

General-Purpose Input and General-Purpose Output P1.2/PWM External Sync Input. This is a

dual function input/output pin.

6 P1.3/TRIP I/O

General-Purpose Input and General-Purpose Output P1.3/PWM External Trip Input. This is a

dual function input/output pin.

7 P0.5/CTS I/O General-Purpose Input and General-Purpose Output P0.5/Clear-to-Send Signal in UART Mode.

8 P0.6/RTS I/O General-Purpose Input and General-Purpose Output P0.6/Request-to-Send Signal in UART Mode.

9 DVDD S Digital Supply Pin.

10 DGND S Digital Ground.

11 DAC0 O DAC Output. Analog output pin.

Rev. C | Page 15 of 108

ADuC7060/ADuC7061

Pin

No. Mnemonic Type

12 ADC5/EXT_REF2IN− I

13 ADC4/EXT_REF2IN+ I

14 ADC3 I Single-Ended or Differential Analog Input 3. Analog input for the primary and auxiliary ADCs.

15 ADC2 I Single-Ended or Differential Analog Input 2. Analog input for the primary and auxiliary ADCs.

16 IEXC1 O Programmable Current Source. Analog output pin.

17 IEXC0 O Programmable Current Source. Analog output pin.

18 GND_SW I

19 ADC1 I

20 ADC0 I

21 VREF+ I External Reference Positive Input for the Primary Channel. Analog input pin.

22 VREF− I External Reference Negative Input for the Primary Channel. Analog input pin.

23 AGND S Analog Ground.

24 AVDD S Analog Supply Pin.

25 ADC6 I Analog Input 6 for Auxiliary ADC. Single-ended or differential Analog Input 6.

26 ADC7 I Analog Input 7 for Auxiliary ADC. Single-ended or differential Analog Input 7.

27 ADC8 I Analog Input 8 for Auxiliary ADC. Single-ended or differential Analog Input 8.

28 ADC9 I Analog Input 9 for Auxiliary ADC. Single-ended or differential Analog Input 9.

29 DGND S Digital Ground.

30 DVDD S Digital Supply Pin.

31

P0.0/SS

32 P0.1/SCLK/SCL I/O

33 P0.2/MISO I/O

34 P0.3/MOSI/SDA I/O

35 XTALO O External Crystal Oscillator Output Pin.

36 XTALI I External Crystal Oscillator Input Pin.

37 P0.4/IRQ0/PWM1 I/O

38 P2.0/IRQ2/PWM0/EXTCLK I/O

39 P1.4/PWM2 I/O

40 P1.5/PWM3 I/O

41 P1.6/PWM4 I/O

42 P2.1/IRQ3/PWM5 I/O

1

Description

Single-Ended or Differential Analog Input 5/External Reference Negative Input. This is a dual

function analog input pin. ADC5 serves as the analog input for the auxiliary ADC. EXT_REF2IN−

serves as the external reference negative input by ADC for the auxiliary channel.

Multifunction Analog Input Pin. This pin can be used for the single-ended or differential

Analog Input 4, which is the analog input for the auxiliary ADC, or it can be used for the

external reference positive input for the auxiliary channel.

Switch to Internal Analog Ground Reference. When this input pin is not used, connect it

directly to the AGND system ground.

Single-Ended or Differential Analog Input 1. Analog input for the primary ADC. Negative differential

input for primary ADC.

Single-Ended or Differential Analog Input 0. Analog input for the primary ADC. Positive differential

input for primary ADC.

I/O

General-Purpose Input and General-Purpose Output P0.0/SPI Slave Select Pin (Active Low). This

is a dual function input/output pin.

General-Purpose Input and General-Purpose Output P0.1/SPI Clock Pin/I

triple function input/output pin.

General-Purpose Input and General-Purpose Output P0.2/SPI Master Input Slave Output. This is

a dual function input/output pin.

General-Purpose Input and General-Purpose Output P0.3/SPI Master Output Slave Input/I

Data Pin. This is a triple function input/output pin.

General-Purpose Input and General-Purpose Output P0.4/External Interrupt Request 0/PWM1

Output. This is a triple function input/output pin.

General-Purpose Input and General-Purpose Output P2.0/External Interrupt Request 2/PWM0

Output/External Clock Input. This is a multifunction input/output pin.

General-Purpose Input and General-Purpose Output P1.4/PWM2 Output. This is a dual function

input/output pin.

General-Purpose Input and General-Purpose Output P1.5/PWM3 Output. This is a dual function

input/output pin.

General-Purpose Input and General-Purpose Output P1.6/PWM4 Output. This is a dual function

input/output pin.

General-Purpose Input and General-Purpose Output P2.1/External Interrupt Request 3/PWM5

Output. This is a triple function input/output pin.

2

C Clock Pin. This is a

2

C

Rev. C | Page 16 of 108

ADuC7060/ADuC7061

Pin

No. Mnemonic Type

43 DGND S Digital Ground.

44 DVDD S Digital Supply Pin.

45

NTRST/BM

46 TDO O JTAG Data Out. Output pin used for debug and download only.

47 TDI I

48 TCK I

1

I = input, O = output, I/O = input/output, and S = supply.

1

Description

I

JTAG Reset/Boot Mode. Input pin used for debug and download only and boot mode (BM). The

ADuC7060 enters serial download mode if BM

high at reset through a 13 kΩ resistor.

JTAG Data In. Input pin used for debug and download only. Add an external pull-up resistor

(~100 kΩ) to this pin.

JTAG Clock Pin. Input pin used for debug and download only. Add an external pull-up resistor

(~100 kΩ) to this pin.

is low at reset and executes code if BM is pulled

Rev. C | Page 17 of 108

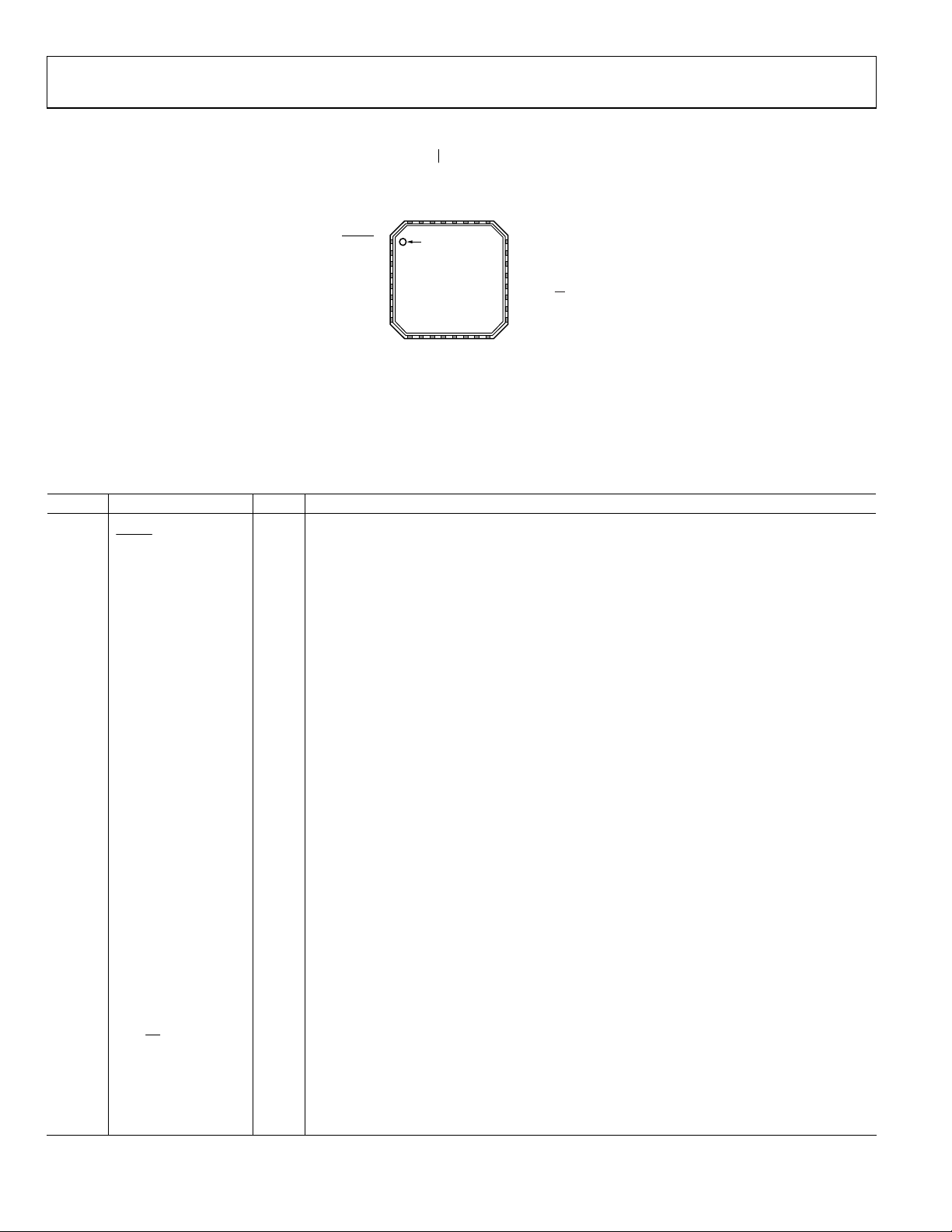

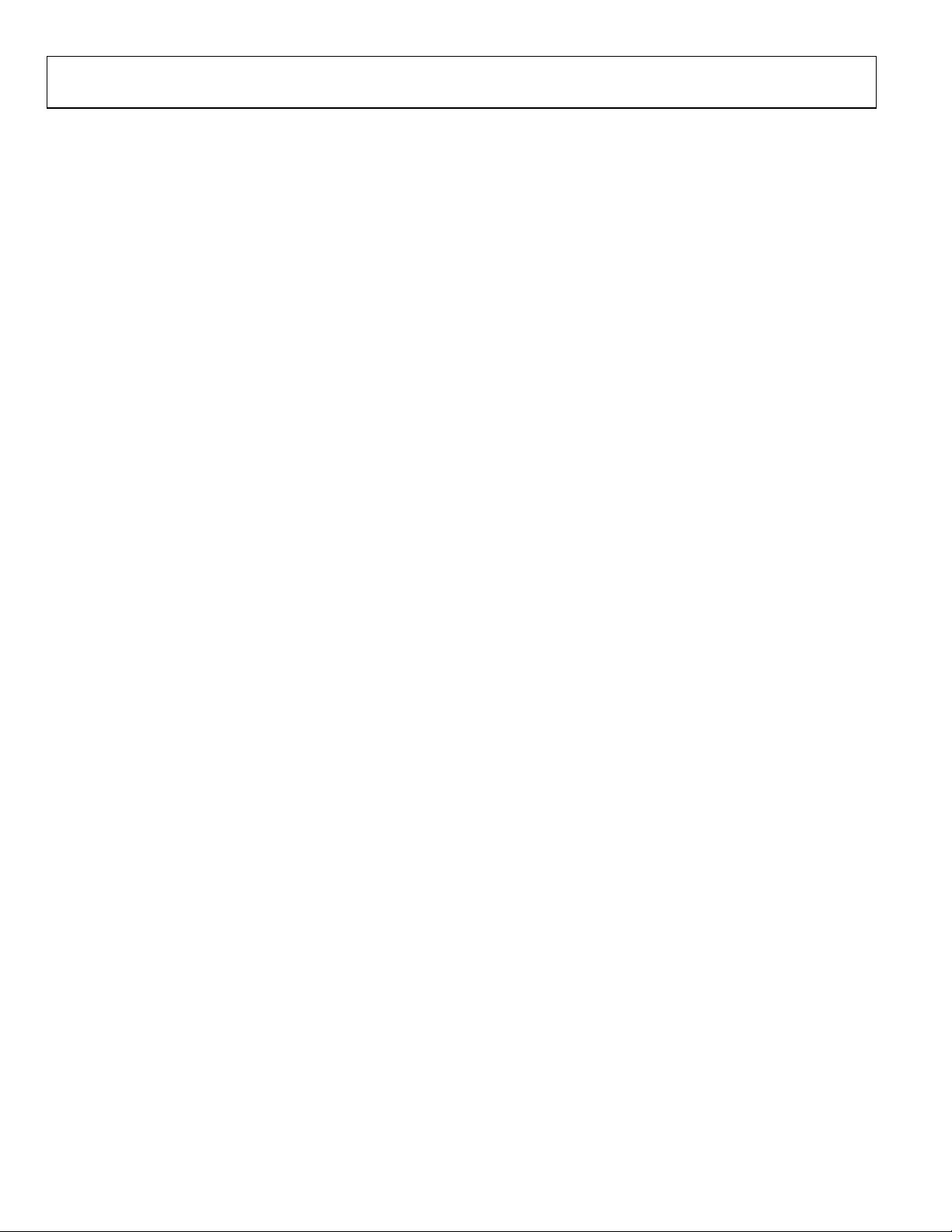

ADuC7060/ADuC7061

WM0

ST/BM

TCK

TDI

TDO

NTR

DVDD

P0.4/IRQ0/PWM1

DGND

P2.0/IRQ2/P

32

31

30

29

28

25

27

26

PIN 1

1RESET

INDICATO R

2TMS

3P1.0/IRQ1/SIN/T0

ADuC7061

4P1.1/SOUT

TOP VIEW

5DAC0

(Not to Scale)

6ADC5/EXT_REF 2IN−

7ADC4/EXT_REF 2IN+

8ADC3

9

10

11

12

13

ADC2

ADC1

IEXC1

IEXC0

NOTES

1. THE 32-LEAD LFCSP _VQ HAS AN EXPOSED PADDLE. T HIS EXPO SED

PADDLE MUST BE L EFT UNCONNECTED.

GND_SW

Figure 8. 32-Lead LFCSP Pin Configuration

Table 9. ADuC7061 Pin Function Descriptions

Pin No. Mnemonic Type1 Description

0 EP Exposed Paddle. The 32-lead LFCSP_VQ has an exposed paddle that must be left unconnected.

1

RESET

2 TMS I

I Reset Pin. Input pin, active low. An external 1 kΩ pull-up resistor is recommended with this pin.

JTAG Test Mode Select. Input pin used for debug and download. An external pull-up resistor

(~100 kΩ) should be added to this pin.

3 P1.0/IRQ1/SIN/T0 I/O

General-Purpose Input and General-Purpose Output P1.0/External Interrupt Request 1/Serial

Input/Timer0 Input. This is a multifunction input/output pin offering four functions.

4 P1.1/SOUT I/O

General-Purpose Input and General-Purpose Output P1.1/Serial Output. This is a dual function

input/output pin.

5 DAC0 O DAC Output. Analog output pin.

6 ADC5/EXT_REF2IN− I

Single-Ended or Differential Analog Input 5/External Reference Negative Input. This is a dual

function analog input pin. The ADC5 serves as the analog input for the auxiliary ADC. The

EXT_REF2IN− serves as the external reference negative input by ADC for the auxiliary channel.

7 ADC4/EXT_REF2IN+ I

Multifunction Analog Input Pin. This pin can be used for the single-ended or differential Analog

Input 4, which is the analog input for the auxiliary ADC, or it can be used for the external

reference positive input for the auxiliary channel.

8 ADC3 I Single-Ended or Differential Analog Input 3. Analog input for primary and auxiliary ADCs.

9 ADC2 I Single-Ended or Differential Analog Input 2. Analog input for primary and auxiliary ADCs.

10 IEXC1 O Programmable Current Source. Analog output pin.

11 IEXC0 O Programmable Current Source. Analog output pin.

12 GND_SW I

Switch to Internal Analog Ground Reference. When this input pin is not used, connect it directly

to the AGND system ground.

13 ADC1 I

Single-Ended or Differential Analog Input 1. Analog input for the primary ADC. Negative differential

input for primary ADC.

14 ADC0 I

Single-Ended or Differential Analog Input 0. Analog input for the primary ADC. Positive differential

input for primary ADC.

15 AGND S Analog Ground.

16 AVDD S Analog Supply Pin.

17 VREF+ I External Reference Positive Input for the Primary Channel. Analog input pin.

18 VREF− I External Reference Negative Input for the Primary Channel. Analog input pin.

19

P0.0/SS

/ADC6

I/O

General-Purpose Input and General-Purpose Output P0.0/SPI Slave Select (Active Low)/Input to

Auxiliary ADC6. This is a multifunction input/output pin. Single-ended or differential Analog

Input 6. Analog input for the auxiliary ADC.

20 P0.1/SCLK/SCL/ADC7 I/O

General-Purpose Input and General-Purpose Output P0.1/SPI Clock/I

ADC7. This is a multifunction input/output pin. Single-ended or differential Analog Input 7.

Analog input for the auxiliary ADC.

24 XTALI

23 XTALO

22 P0.3/MOSI/SDA/ADC9

21 P0.2/MISO/ADC8

20 P0.1/SCLK/SCL/ADC7

19 P0.0/SS/ADC6

18 VREF–

17 VREF+

14

15

16

D

ADC0

AVD

AGND

07079-003

2

C Clock/Input to Auxiliary

Rev. C | Page 18 of 108

ADuC7060/ADuC7061

Pin No. Mnemonic Type1 Description

21 P0.2/MISO/ADC8 I/O

22 P0.3/MOSI/SDA/ADC9 I/O

23 XTALO O External Crystal Oscillator Output Pin.

24 XTALI I External Crystal Oscillator Input Pin.

25 P0.4/IRQ0/PWM1 I/O

26 P2.0/IRQ2/PWM0 I/O

27 DGND S Digital Ground.

28 DVDD S Digital Supply Pin.

29

NTRST/BM

I

30 TDO O JTAG Data Out. Output pin used for debug and download only.

31 TDI I

32 TCK I

1

I = input, O = output, I/O = input/output, and S = supply.

General-Purpose Input and General-Purpose Output P0.2/SPI Master Input Slave

Output/Auxiliary ADC8 Input. This is a triple function input/output pin. Single-ended or

differential Analog Input 8. Analog input for the auxiliary ADC.

2

General-Purpose Input and General-Purpose Output P0.3/SPI Master Output Slave Input/I

C

Data Pin/Auxiliary ADC9 Input. This is a multifunction input/output pin. Single-ended or

differential Analog Input 9. Analog input for the auxiliary ADC.

General-Purpose Input and General-Purpose Output P0.4/External Interrupt Request 0/PWM1

Output. This is a triple function input/output pin.

General-Purpose Input and General-Purpose Output P2.0/External Interrupt Request 2/PWM0

Output. This is a triple function input/output pin.

JTAG Reset/Boot Mode. Input pin used for debug and download only and boot mode (BM). The

ADuC7061 enters serial download mode if BM

is low at reset and executes code if BM is pulled

high at reset through a 13 kΩ resistor.

JTAG Data In. Input pin used for debug and download only. Add an external pull-up resistor

(~100 kΩ) to this pin.

JTAG Clock. Input pin used for debug and download only. Add an external pull-up resistor

(~100 kΩ) to this pin.

Rev. C | Page 19 of 108

ADuC7060/ADuC7061

TERMINOLOGY

Conversion Rate

The conversion rate specifies the rate at which an output result

is available from the ADC, when the ADC has settled.

The sigma-delta (Σ-) conversion techniques used on this part

mean that whereas the ADC front-end signal is oversampled at

a relatively high sample rate, a subsequent digital filter is used to

decimate the output, giving a valid 24-bit data conversion result

at output rates from 1 Hz to 8 kHz.

Note that, when software switches from one input to another

(on the same ADC), the digital filter must first be cleared and

then allowed to average a new result. Depending on the configuration of the ADC and the type of filter, this can take

multiple conversion cycles.

Integral Nonlinearity (INL)

INL is the maximum deviation of any code from a straight line

passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale, a point ½ LSB

below the first code transition, and full scale, a point ½ LSB

above the last code transition (111 . . . 110 to 111 . . . 111).

The error is expressed as a percentage of full scale.

No Missing Codes

No missing codes is a measure of the differential nonlinearity

of the ADC. The error is expressed in bits and specifies the

number of codes (ADC results) as 2N bits, where N is no

missing codes guaranteed to occur through the full ADC

input range.

Offset Error

Offset error is the deviation of the first code transition ADC

input voltage from the ideal first code transition.

Offset Error Drift

Offset error drift is the variation in absolute offset error with

respect to temperature. This error is expressed as least

significant bits per degree Celsius.

Gain Error

Gain error is a measure of the span error of the ADC. It is a

measure of the difference between the measured and the ideal

span between any two points in the transfer function.

Output Noise

The output noise is specified as the standard deviation (or 1 ×

Sigma) of the distribution of the ADC output codes collected

when the ADC input voltage is at a dc voltage. It is expressed as

micro root mean square. The output, or root mean square (rms)

noise, can be used to calculate the effective resolution of the

ADC as defined by the following equation:

Effective Resolution = log2(Full-Scale Range/rms Noise) bits

The peak-to-peak noise is defined as the deviation of codes that

fall within 6.6 × Sigma of the distribution of ADC output codes

collected when the ADC input voltage is at dc. The peak-to-peak

noise is, therefore, calculated as

6.6 × rms Noise

The peak-to-peak noise can be used to calculate the ADC

(noise free code) resolution for which there is no code flicker

within a 6.6-Sigma limit as defined by the following equation:

Noise Free Code Resolution = log2

Data Sheet Acronyms

ADC analog-to-digital converter

ARM advanced RISC machine

JTAG joint test action group

LSB least significant byte/bit

LVF low voltage flag

MCU microcontroller

MMR memory mapped register

MSB most significant byte/bit

PID protected identifier

POR power-on reset

PSM power supply monitor

rms root mean square

⎛

⎜

⎜

⎝

−

RangeScaleFull

−−

⎞

⎟

bits

⎟

NoisePeaktoPeak

⎠

Rev. C | Page 20 of 108

ADuC7060/ADuC7061

OVERVIEW OF THE ARM7TDMI CORE

The ARM7® core is a 32-bit, reduced instruction set computer

(RISC), developed by ARM® Ltd. The ARM7TDMI is a

von Neumann-based architecture, meaning that it uses a single

32-bit bus for instruction and data. The length of the data can

be 8, 16, or 32 bits, and the length of the instruction word is

either 16 bits or 32 bits, depending on the mode in which the

core is operating.

The ARM7TDMI is an ARM7 core with four additional

features, as listed in Tabl e 10 .

Table 10. ARM7TDMI Features

Feature Description

T Support for the Thumb® (16-bit) instruction set

D Support for debug

M Enhanced multiplier

I

Includes the EmbeddedICE® module to support

embedded system debugging

THUMB MODE (T)

An ARM instruction is 32 bits long. The ARM7TDMI processor

supports a second instruction set compressed into 16 bits, the

Thumb instruction set. Faster code execution from 16-bit memory

and greater code density is achieved by using the Thumb instruction set, making the ARM7TDMI core particularly suited for

embedded applications.

However, the Thumb mode has three limitations.

• Relative to ARM, the Thumb code usually requires more

instructions to perform the same task. Therefore, ARM

code is best for maximizing the performance of timecritical code in most applications.

• The Thumb instruction set does not include some

instructions that are needed for exception handling, so

ARM code can be required for exception handling.

• When an interrupt occurs, the core vectors to the interrupt

location in memory and executes the code present at that

address. The first command is required to be in ARM code.

MULTIPLIER (M)

The ARM7TDMI instruction set includes an enhanced

multiplier, with four extra instructions to perform 32-bit by

32-bit multiplication with a 64-bit result, and 32-bit by 32-bit

multiplication-accumulation (MAC) with a 64-bit result.

EmbeddedICE (I)

The EmbeddedICE module provides integrated on-chip debug

support for the ARM7TDMI. The EmbeddedICE module

contains the breakpoint and watchpoint registers that allow

nonintrusive user code debugging. These registers are controlled through the JTAG test port. When a breakpoint or

watchpoint is encountered, the processor halts and enters the

debug state. When in a debug state, the processor registers can

be interrogated, as can the Flash/EE, SRAM, and memory

mapped registers.

Rev. C | Page 21 of 108

ARM7 Exceptions

The ARM7 supports five types of exceptions, with a privileged

processing mode associated with each type. The five types of

exceptions are as follows:

Type 1: normal interrupt or IRQ. This is provided to service

general-purpose interrupt handling of internal and external

events. Note that the ADuC706x supports eight configurable

priority levels for all IRQ sources.

Type 2: fast interrupt or FIQ. This is provided to service data

transfer or a communication channel with low latency. FIQ has

priority over IRQ. Note that the ADuC706x supports eight

configurable priority levels for all FIQ sources.

Type 3: memory abort (prefetch and data).

Type 4: attempted execution of an undefined instruction.

Type 5: software interrupts (SWI) instruction that can be used

to make a call to an operating system.

Typically, the programmer defines interrupts as IRQ, but for

higher priority interrupts, the programmer can define

interrupts as the FIQ type.

The priority of these exceptions and vector addresses are listed

in Tabl e 1 1 .

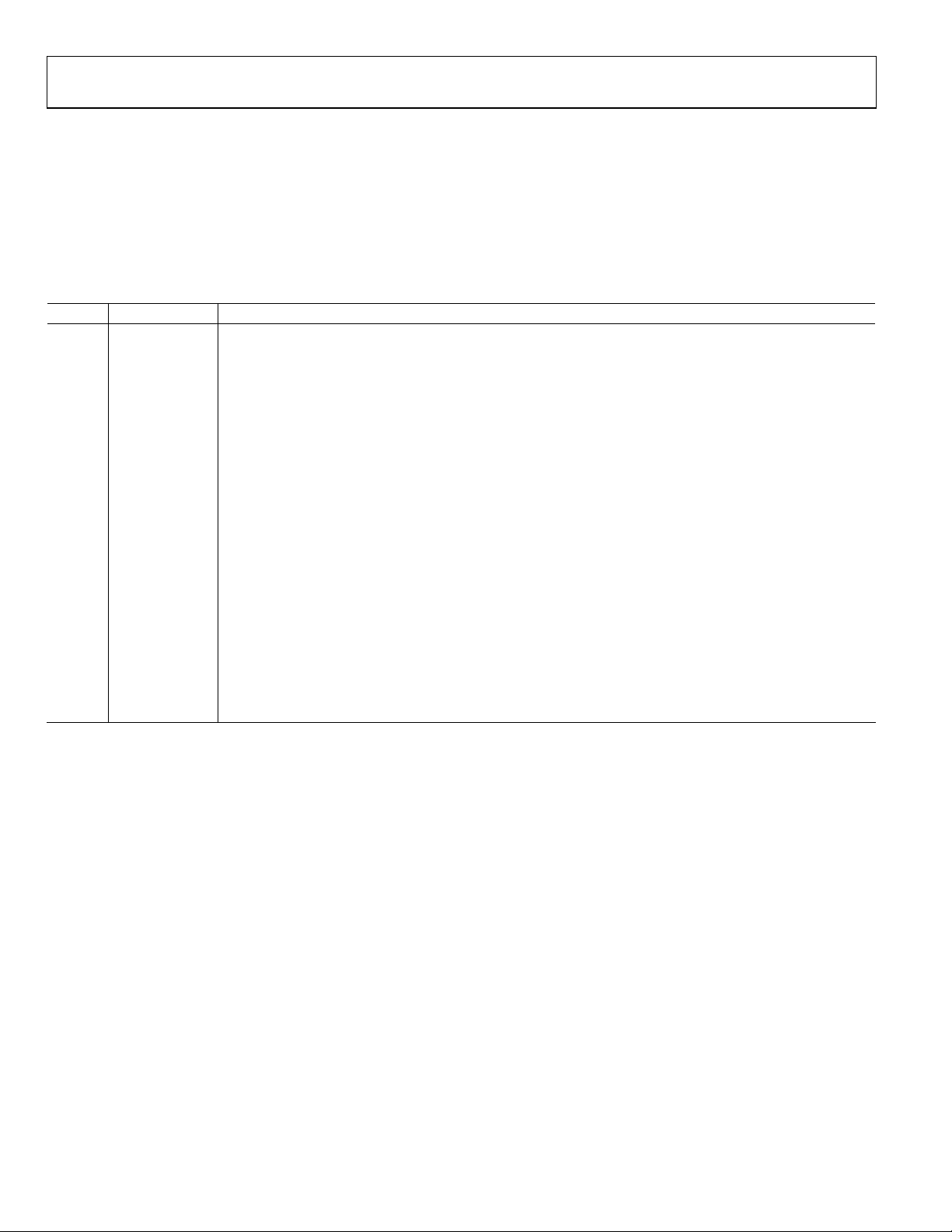

Table 11. Exception Priorities and Vector Addresses

Priority Exception Address

1 Hardware reset 0x00

2 Memory abort (data) 0x10

3 FIQ 0x1C

4 IRQ 0x18

5 Memory abort (prefetch) 0x0C

6 Software interrupt1 0x08

6 Undefined instruction1 0x04

1

A software interrupt and an undefined instruction exception have the same

priority and are mutually exclusive.

The exceptions listed in Table 1 1 are located from 0x00 to 0x1C,

with a reserved location at 0x14.

ARM REGISTERS

The ARM7TDMI has 16 standard registers. R0 to R12 are for

data manipulation, R13 is the stack pointer, R14 is the link

register, and R15 is the program counter that indicates the

instruction currently being executed. The link register contains

the address from which the user has branched (when using the

branch and link command) or the command during which an

exception occurred.

The stack pointer contains the current location of the stack.

Generally, on an ARM7TDMI, the stack starts at the top of the

available RAM area and descends using the area as required. A

separate stack is defined for each of the exceptions. The size of

each stack is user configurable and is dependent on the target

application. When programming using high level languages,

ADuC7060/ADuC7061

such as C, it is necessary to ensure that the stack does not overflow.

This is dependent on the performance of the compiler that is used.

When an exception occurs, some of the standard registers are

replaced with registers specific to the exception mode. All

exception modes have replacement banked registers for the

stack pointer (R13) and the link register (R14) as represented

in Figure 9. The FIQ mode has more registers (R8 to R12)

supporting faster interrupt processing. With the increased

number of noncritical registers, the interrupt can be processed

without the need to save or restore these registers, thereby

reducing the response time of the interrupt handling process.

More information relative to the programmer’s model and the

ARM7TDMI core architecture can be found in ARM7TDMI

technical and ARM architecture manuals available directly from

ARM Ltd.

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15 (PC)

CPSR

USER MODE

R8_FIQ

R9_FIQ

R10_FIQ

R11_FIQ

R12_FIQ

R13_FIQ

R14_FIQ

SPSR_FIQ

FIQ

MODE

R13_SVC

R14_SVC

SPSR_SVC

SVC

MODE

SPSR_ABT

Figure 9. Register Organization

INTERRUPT LATENCY

The worst-case latency for an FIQ consists of the longest time

that the request can take to pass through the synchronizer, plus

the time for the longest instruction to complete (the longest

instruction is an LDM) that loads all the registers including the

PC, plus the time for the data abort entry, plus the time for FIQ

entry. At the end of this time, the ARM7TDMI is executing the

instruction at 0x1C (FIQ interrupt vector address). The maximum

total time is 50 processor cycles, or just over 4.88 s in a system

using a continuous 10.24 MHz processor clock. The maximum

IRQ latency calculation is similar but must allow for the FIQ

having higher priority, which can delay entry into the IRQ

handling routine for an arbitrary length of time. This time can be

reduced to 42 cycles if the LDM command is not used; some

compilers have an option to compile without using this command.

Another option is to run the part in Thumb mode where this

time is reduced to 22 cycles.

The minimum latency for FIQ or IRQ interrupts is five cycles.

This consists of the shortest time that the request can take through

the synchronizer plus the time to enter the exception mode.

USABLE IN USER MODE

SYSTEM MODES ONLY

R13_ABT

R14_ABT

ABORT

MODE

R13_IRQ

R14_IRQ

SPSR_IRQ

IRQ

MODE

R13_UND

R14_UND

SPSR_UND

UNDEFINED

MODE

Rev. C | Page 22 of 108

Note that the ARM7TDMI initially (first instruction) runs in

ARM (32-bit) mode when an exception occurs. The user can

immediately switch from ARM mode to Thumb mode if required,

for example, when executing interrupt service routines.

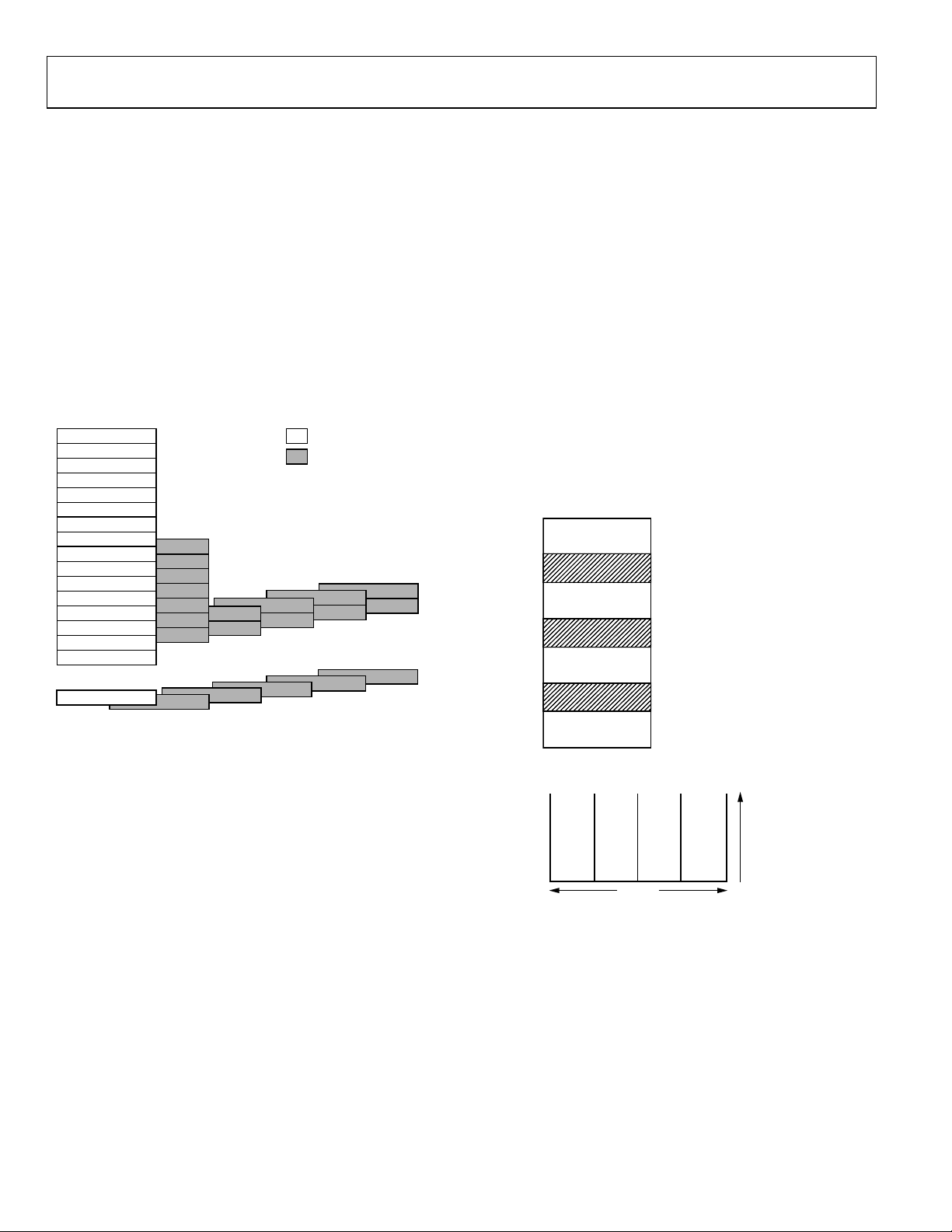

MEMORY ORGANIZATION

The ARM7, a von Neumann architecture MCU core, sees

memory as a linear array of 232-byte locations. As shown in

Figure 10, the ADuC706x maps this into four distinct user

areas: a memory area that can be remapped, an SRAM area, a

Flash/EE area, and a memory mapped register (MMR) area.

The first 30 kB of this memory space is used as an area into

which the on-chip Flash/EE or SRAM can be remapped. Any

access, either reading or writing, to an area not defined in the

memory map results in a data abort exception.

Memory Format

The ADuC706x memory organization is configured in little

endian format: the least significant byte is located in the lowest

byte address and the most significant byte in the highest byte

address (see Figure 11).

0xFFFFFFFF

0xFFFF0000

0x00087FFF

0x00080000

0x00040FFF

0x00040000

0x00007FFF

07079-004

0x00000000

BIT 31

BYTE 3

BYTE 2

.

.

.

B

7

3

Figure 11. Little Endian Format

SRAM

The ADuC706x features 4 kB of SRAM, organized as 1024 ×

32 bits, that is, 1024 words located at 0x40000. The RAM space

can be used as data memory as well as volatile program space.

ARM code can run directly from SRAM at full clock speed

given that the SRAM array is configured as a 32-bit wide memory

array. SRAM is read/writable in 8-, 16-, and 32-bit segments.

Remap

The ARM exception vectors are all situated at the bottom of the

memory array, from Address 0x00000000 to Address 0x00000020.

MMRs

RESERVED

FLASH/EE

RESERVED

SRAM

RESERVED

REMAPPABLE MEMORY SPACE

(FLASH/EE OR SRAM)

Figure 10. Memory Map

BYTE 1

.

.

.

A

6

2

32 BITS

BYTE 0

.

.

.

.

.

.

9

8

5

4

1

0

BIT 0

0xFFFFFFFF

0x00000004

0x00000000

07079-005

7079-006

ADuC7060/ADuC7061

By default, after a reset, the Flash/EE memory is logically

mapped to Address 0x00000000. It is possible to logically remap

the SRAM to Address 0x00000000 by setting Bit 0 of the remap

MMR located at 0xFFFF0220. To revert Flash/EE to 0x00000000,

Bit 0 of remap is cleared.

It is sometimes desirable to remap RAM to 0x00000000 to optimize

the interrupt latency of the ADuC706x because code can run in

full 32-bit ARM mode and at maximum core speed. Note that,

when an exception occurs, the core defaults to ARM mode.

Remap Operation

When a reset occurs on the ADuC706x, execution starts automatically in the factory programmed internal configuration code.

This so-called kernel is hidden and cannot be accessed by user

code. If the ADuC706x is in normal mode, it executes the poweron configuration routine of the kernel and then jumps to the

reset vector, Address 0x00000000, to execute the user’s reset

exception routine. Because the Flash/EE is mirrored at the

bottom of the memory array at reset, the reset routine must

always be written in Flash/EE.

The remap command must be executed from the absolute Flash/EE

address and not from the mirrored, remapped segment of memory,

because this may be replaced by SRAM. If a remap operation is

executed while operating code from the mirrored location, prefetch/data aborts can occur, or the user can observe abnormal

program operation. Any kind of reset logically remaps the Flash/EE

memory to the bottom of the memory array.

Remap Register

Name: Remap

Address: 0xFFFF0220

Default value: 0x0000

Access: Read and write

Function: This 8-bit register allows user code to remap

either RAM or Flash/EE space into the bottom

of the ARM memory space starting at

Address 0x00000000.

Table 12. Remap MMR Bit Designations

Bit Description

7:1

0 Remap bit.

Set by user to remap the SRAM to 0x00000000.

Reserved. These bits are reserved and should be written

as 0 by user code.

Cleared automatically after reset to remap the Flash/EE

memory to 0x00000000.

FLASH/EE CONTROL INTERFACE

Serial and JTAG programming use the Flash/EE control

interface, which includes the eight MMRs outlined in this

section. Note that the flash page size is 512 bytes.

FEESTA Register

FEESTA is a read-only register that reflects the status of the

flash control interface as described in Tab l e 13 .

Name: FEESTA

Address: 0xFFFF0E00

Default value: 0x0020

Access: Read

Table 13. FEESTA MMR Bit Designations

Bit Description

15:6 Reserved.

5 Reserved.

4 Reserved.

3

2

1

0

Flash interrupt status bit. Set automatically when an

interrupt occurs, that is, when a command is complete

and the Flash/EE interrupt enable bit in the FEEMOD

register is set. Cleared when reading the FEESTA

register.

Flash/EE controller busy. Set automatically when the

controller is busy. Cleared automatically when the

controller is not busy.

Command fail. Set automatically when a command

completes unsuccessfully. Cleared automatically when

reading the FEESTA register.

Command pass. Set by the MicroConverter® when a

command completes successfully. Cleared

automatically when reading the FEESTA register.

FEEMOD Register

FEEMOD sets the operating mode of the flash control interface.

Tabl e 14 lists FEEMOD MMR bit designations.

Name: FEEMOD

Address: 0xFFFF0E04

Default value: 0x0000

Access: Read and write

Table 14. FEEMOD MMR Bit Designations

Bit Description

15:9 Reserved.

8 Reserved. Always set this bit to 1.

7:5

4 Flash/EE interrupt enable.

Cleared by user to disable the Flash/EE interrupt.

3 Erase/write command protection.

Set by user to enable the erase and write commands.

2:0 Reserved. Always set these bits to 0.

Reserved. Always set these bits to 0 except when

writing keys.

Set by user to enable the Flash/EE interrupt. The

interrupt occurs when a command is complete.

Cleared to protect the Flash/EE against the erase/write

command.

Rev. C | Page 23 of 108

ADuC7060/ADuC7061

FEECON Register

FEECON is an 8-bit command register. The commands are

described in Ta bl e 15 .

Table 15. Command Codes in FEECON

Code Command Description

0x001 Null Idle state.

0x011 Single read Load FEEDAT with the 16-bit data. Indexed by FEEADR.

0x021 Single write Write FEEDAT at the address pointed to by FEEADR. This operation takes 50 s.

0x031 Erase/write

0x041 Single verify

0x051 Single erase Erase the page indexed by FEEADR.

0x061 Mass erase

0x07 Reserved Reserved.

0x08 Reserved Reserved.

0x09 Reserved Reserved.

0x0A Reserved Reserved.

0x0B Signature

0x0C Protect

0x0D Reserved Reserved.

0x0E Reserved Reserved.

0x0F Ping No operation; interrupt generated.

1

The FEECON register always reads 0x07 immediately after execution of any of these commands.

Erase the page indexed by FEEADR and write FEEDAT at the location pointed to by FEEADR. This operation takes

approximately 24 ms.

Compare the contents of the location pointed to by FEEADR to the data in FEEDAT. The result of the

comparison is returned in FEESTA Bit 0 and Bit 1.

Erase 30 kB of user space. The 2 kB of kernel are protected. To prevent accidental execution, a command

sequence is required to execute this instruction. See the Command Sequence for Executing a Mass Erase

section.

This command results in a 24-bit LFSR-based signature being generated and loaded into the FEESIGN MMR.

This operation takes 16,389 clock cycles.

This command can run only once. The value of FEEPRO is saved and is removed only with a mass erase (0x06)

or the key.

Name: FEECON

Address: 0xFFFF0E08

Default value: 0x07

Access: Read and write

Rev. C | Page 24 of 108

ADuC7060/ADuC7061

FEEDAT Register

FEEDAT is a 16-bit data register. This register holds the data

value for flash read and write commands.

Name: FEEDAT

Address: 0xFFFF0E0C

Default value: 0xXXXX

Access: Read and write

FEEHIDE Register

The FEEHIDE MMR provides immediate protection. It does

not require any software key. Note that the protection settings

in FEEHIDE are cleared by a reset (see Table 16).

Name: FEEHIDE

Address: 0xFFFF0E20

Default value: 0xFFFFFFFF

Access: Read and write

FEEADR Register

FEEADR is a 16-bit address register used for accessing

individual pages of the 32 kB flash block. The valid address

range for a user is: 0x0000 to 0x77FF. This represents the 30 kB

flash user memory space. A read or write access outside this

boundary causes a data abort exception to occur.

Name: FEEADR

Address: 0xFFFF0E10

Default value: 0x0000

Access: Read and write

FEESIGN Register

The FEESIGN register is a 24-bit MMR. This register is updated

with the 24-bit signature value after the signature command is

executed. This value is the result of the linear feedback shift

register (LFSR) operation initiated by the signature command.

Name: FEESIGN

Address: 0xFFFF0E18

Default value: 0xFFFFFF

Access: Read

FEEPRO Register

The FEEPRO MMR provides protection following a subsequent

reset of the MMR. It requires a software key (see Tab l e 1 6 ).

Name: FEEPRO

Address: 0xFFFF0E1C

Default value: 0x00000000

Access: Read and write

Table 16. FEEPRO and FEEHIDE MMR Bit Designations

Bit Description

31 Read protection.

Cleared by user to protect all code. No JTAG read

accesses for protected pages if this bit is cleared.

Set by the user to allow reading the code via JTAG.

30

29

28:0

Protection for Page 59 (0x00087600 to 0x000877FF).

Set by the user to allow writing to Page 59. Cleared to

protect Page 59.

Protection for Page 58 (0x00087400 to 0x000875FF).

Set by the user to allow writing to Page 58. Cleared to

protect Page 58.

Write protection for Page 57 to Page 0. Each bit

represents two pages. Each page is 512 bytes in size.

Bit 0 is protection for Page 0 and Page 1 (0x00080000

to 0x000803FF). Set by the user to allow writing Page 0

and Page 1. Cleared to protect Page 0 and Page 1.

Bit 1 is protection for Page 2 and Page 3 (0x00080400

to 0x000807FF. Set by the user to allow writing Page 2

and Page 3. Cleared to protect Page 2 and Page 3.

…

…

Bit 27 is protection for Page 54 and Page 55

(0x00087000 to 0x000873FF). Set by the user to allow

writing to Page 54 and Page 55. Cleared to protect

Page 54 and Page 55.

Bit 28 is protection for Page 56 and Page 57

(0x00087400 to 0x000877FF). Set by the user to allow

writing to Page 56 and Page 57. Cleared to protect

Page 56 and Page 57.

Temporary Protection

Temporary protection can be set and removed by writing

directly into the FEEHID MMR. This register is volatile and,

therefore, protection is only in place for as long as the part

remains powered on. The protection setting is not reloaded

after a power cycle.

Keyed Permanent Protection

Keyed permanent protection can be set via FEEPRO to lock the

protection configuration. The software key used at the start of