Integrated Precision Battery Sensor for

Silicon Anomaly

This anomaly list describes the known bugs, anomalies, and workarounds for the ADuC7033 integrated precision battery sensor. The

anomalies listed apply to all ADuC7033 packaged material branded as follows:

First Line ADuC7033

Second Line BSTZ-88

Analog Devices, Inc. is committed, through future silicon revisions, to continuously improving silicon functionality. Analog Devices tries

to ensure that these future silicon revisions remain compatible with your present software/systems by implementing the recommended

workarounds outlined here.

Automotive System

ADuC7033

ADuC7033 FUNCTIONALITY ISSUES

Silicon

Revision

Identifier

8L/88 A60

Kernel

Revision

Identifier

Chip Marking

ADuC7033

BSTZ-88

Silicon

Status

Release Rev. B 4

Anomaly Sheet No. of Reported Anomalies

ADuC7033 PERFORMANCE ISSUES

Silicon

Revision

Identifier

8L/88 A60

Kernel

Revision

Identifier

Chip Marking

ADuC7033

BSTZ-88

Silicon

Status

Release Rev. B 2

Anomaly Sheet No. of Reported Anomalies

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

ADuC7033 Silicon Anomaly

ANOMALIES

ADuC7033 Functionality Issues

1. LIN Communication with VDD > 31 V [er001]:

Background:

Issue:

Workaround:

Related Issues:

2. LIN Short-Circuit Recognition [er002]:

Background:

Issue:

Workaround:

Related Issues:

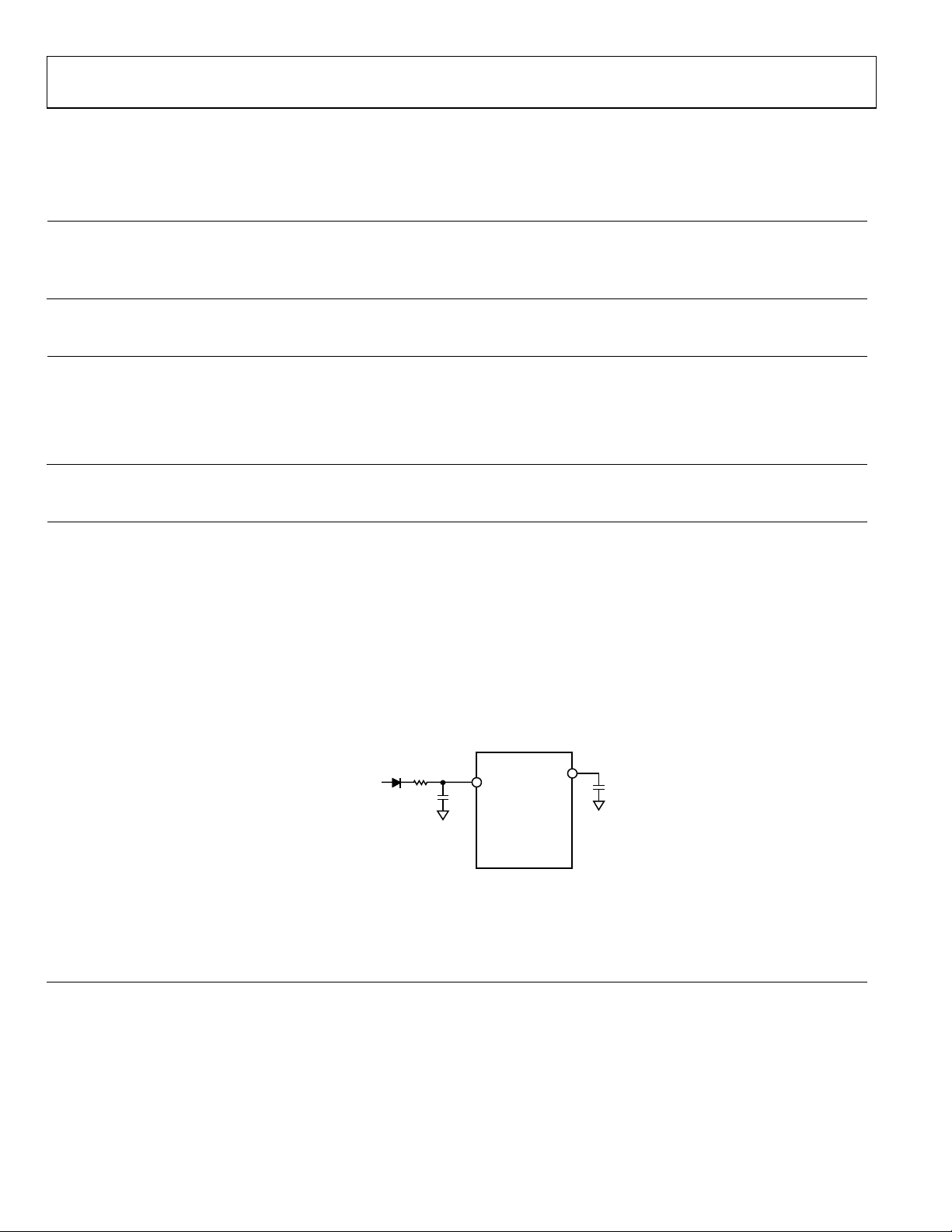

3. Power-On Reset [er003]:

Background:

Issue:

Workaround:

The ADuC7033 is specified for operation up to 40 V.

If the LIN communication occurs with VDD > 31 V, the ADuC7033 resets.

Pending.

None.

The ADuC7033 features LIN short-circuit protection. In the event of a short circuit on the LIN bus, an interrupt is

generated. HVCFG1[2] allows users to enable/disable this interrupt. It is enabled by default.

If the LIN is shorted to VDD with a resistance lower than 120 Ω, LIN can oscillate over temperature and supply and a

short may not be detected.

Pending.

None.

The ADuC7033 integrates a power-on reset (POR) circuit holding the ASIC in reset for 20 ms typically after VDD reaches

3 V typically.

Under particular conditions, the POR does not release the reset signal, that is, the ASIC remains in reset until a power

cycle occurs. This POR issue only occurs under three specific and coincident power-on conditions:

• Fast ramp on VDD, nominally faster than 100 s from V

• Initial value of VDD (V

) ~1.2 V

init

to 12 V

init

• Voltage on REG_DVDD at time the VDD ramp is reapplied ~175 mV

A fast VDD ramp (that is, ramping from ~1.2 V to 12 V in <100 µs) is required as one of the conditions to initiate the

reported POR issue. Analog Devices recommends careful selection of external power supply decoupling components

to ensure that the VDD supply ramp rate can always be guaranteed to be >100 µs under all VBAT power-on conditions.

Specifically, in modules that already incorporate a series resistor and decoupling capacitor to ground on the VDD line

between the reverse protection diode and the VDD pin (see Figure 1), choose the series resistor/decoupling capacitor

combination to give an RC time constant of at least 100 µs, such as 10 Ω and 10 µF.

10Ω

VDD

10µF

ADuC7033

REG_DVDD

2.2µF

Related Issues:

07069-002

Figure 1.

Alternatively, in the specific case of customer modules where the VDD decoupling capacitor cannot be increased

beyond 4.7 µF, then increasing the series resistor to 20 Ω and increasing the REG_DVDD decoupling capacitor from

2.2 µF to 10 µF also slews the VDD supply power-on ramp to ~200 µs. This is also an appropriate and recommended

containment measure.

None.

Rev. B | Page 2 of 4

Silicon Anomaly ADuC7033

4. ADC Overrange [er004]:

Background:

Issue:

Workaround:

Related Issues:

The ADuC7033 integrates a number of flags or status bits (ADCSTA[14:12]) to monitor overrange and underrange

conditions in the ADC interface. These bits, automatically set by the hardware, are set to 1 to indicate an underrange

or overrange has occurred in the ADC conversion. When this occurs, the data in the data register (ADCxDAT ) is invalid.

The conversion result in the data register (ADCxDAT) is clamped to negative full scale (underrange) or positive full scale

(overrange).

Under certain limited operating conditions a large negative overrange does not produce the expected clamp to

negative full scale. Two situations may occur:

• Issue 1: A clamp to positive full scale can occur with the error bits (ADCSTA[14:12]) set correctly.

• Issue 2: The error bits are not set correctly, and the ADC data register is not clamped to positive full scale or

negative full scale. This occurs when the ADCFLT register has the following settings:

ADCFLT[15] = 1 and ADCFLT[6:0] = 0x7E or 0x7F.

Workarounds for these two issues, when using the I-ADC, are as follows:

• Issue 1: The error bits (ADCSTA[14:12]) can be monitored to identify an overrange or underrange condition in the

ADC conversion.

• Issue 2: It is recommended not to use these two ADC filter configurations (ADCFLT[6:0] = 0x7E or 0x7F, when

ADCFLT[15] = 1).

If it is necessary to use these configurations, a workaround for the I-ADC is available by using the overrange

(ADCSTA[3]) bit in the ADCSTA register. Two configurations are available:

• This can be configured to produce an interrupt whenever the I-ADC input becomes grossly (133% of full scale)

overrange in the positive or negative direction. Therefore, this interrupt, or status bit, can be monitored to indicate

that the input has overranged, allowing the PGA gain to be changed without having to wait until the full ADC

conversion is complete.

• If an interrupt is not required, this bit can be used as an additional validation of the data register. The I-ADC data

register (ADC0DAT) is valid if the ADCSTA[0] is 1, and the ADCSTA[3] is 0.

None.

Rev. B | Page 3 of 4

ADuC7033 Silicon Anomaly

ANOMALIES

ADuC7033 Performance Issues

1. ESD [pr001]:

Background:

Issue:

Workaround:

Related Issues:

2. WU Pin Latch-Up [pr002]:

Background:

Issue:

Workaround:

The ADuC7033 is intended to be classified for HBM ESD rating of 2 kV and FICDM ESD rating of 500 V.

For silicon branded 8L, HBM ESD is specified to 800 V and FICDM ESD is specified to 400 V and 750 V for the corner pins.

Pending.

None.

The latch-up condition on the WU pin should follow the AECQ100 specification and should be able to sink up to

−100 mA at 125°C.

The WU pin fails the AECQ100 specification.

It is recommended to use a protection diode such as a BAS52, as shown in Figure 2, to avoid destructive damage to

the part.

39Ω

LOAD

07069-001

Related Issues:

WU

Figure 2. Protection Diode on WU Pin

None.

SECTION 1. ADuC7033 FUNCTIONALITY ISSUES

Reference Number Description Status

er001 LIN communication with VDD > 31 V Open

er002 LIN short-circuit recognition Open

er003 Power-on reset Open

er004 ADC overrange Open

SECTION 2. ADuC7033 PERFORMANCE ISSUES

Reference Number Description Status

pr001 ESD Open

pr002 WU pin latch-up Open

©2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

S07069-0-5/10(B)

Rev. B | Page 4 of 4

Loading...

Loading...