ANALOG DEVICES ADT7470 Service Manual

Temperature Sensor Hub and Fan Controller

FEATURES

Monitors up to 10 remote temperature sensors

Monitors and controls speed of up to 4 fans independently

PWM outputs drive each fan under software control

FULL_SPEED

external hardware

SMBALERT

Three-state ADDR pin allows up to 3 devices on a single bus

Temperature decoder interprets TMP05/TMP06 temperature

sensors and communicates values over I

Limit comparison of all monitored values

Supports fast I

Meets SMBus 2.0 electrical specifications

(fully SMBus 1.1-compliant)

Footprint-compatible with ADT7460

APPLICATIONS

Servers

Networking and telecommunications equipment

Desktops

input allows fans to be blasted PWMMAX by

interrupt signals failures to system controller

2

C bus

2

C standard (400 kHz max)

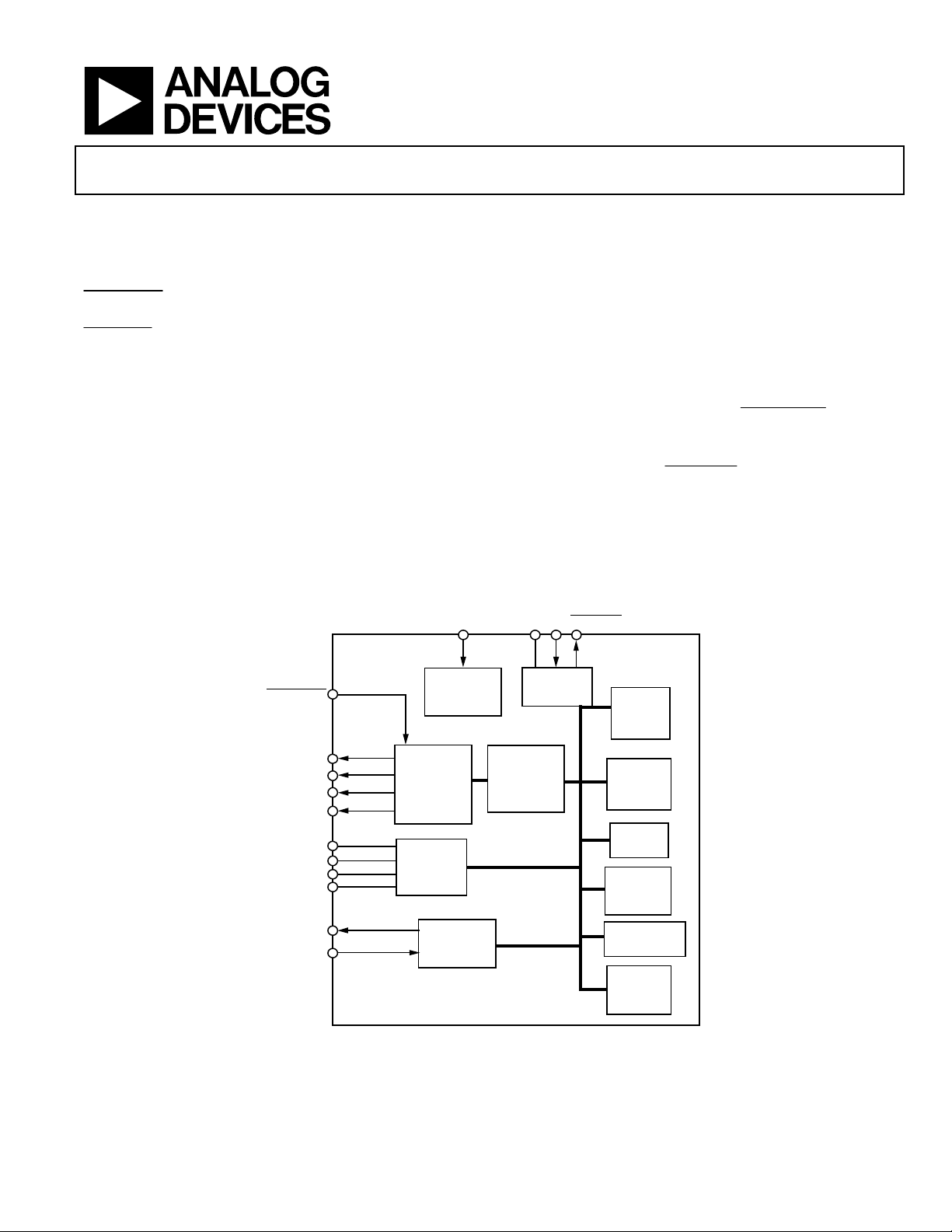

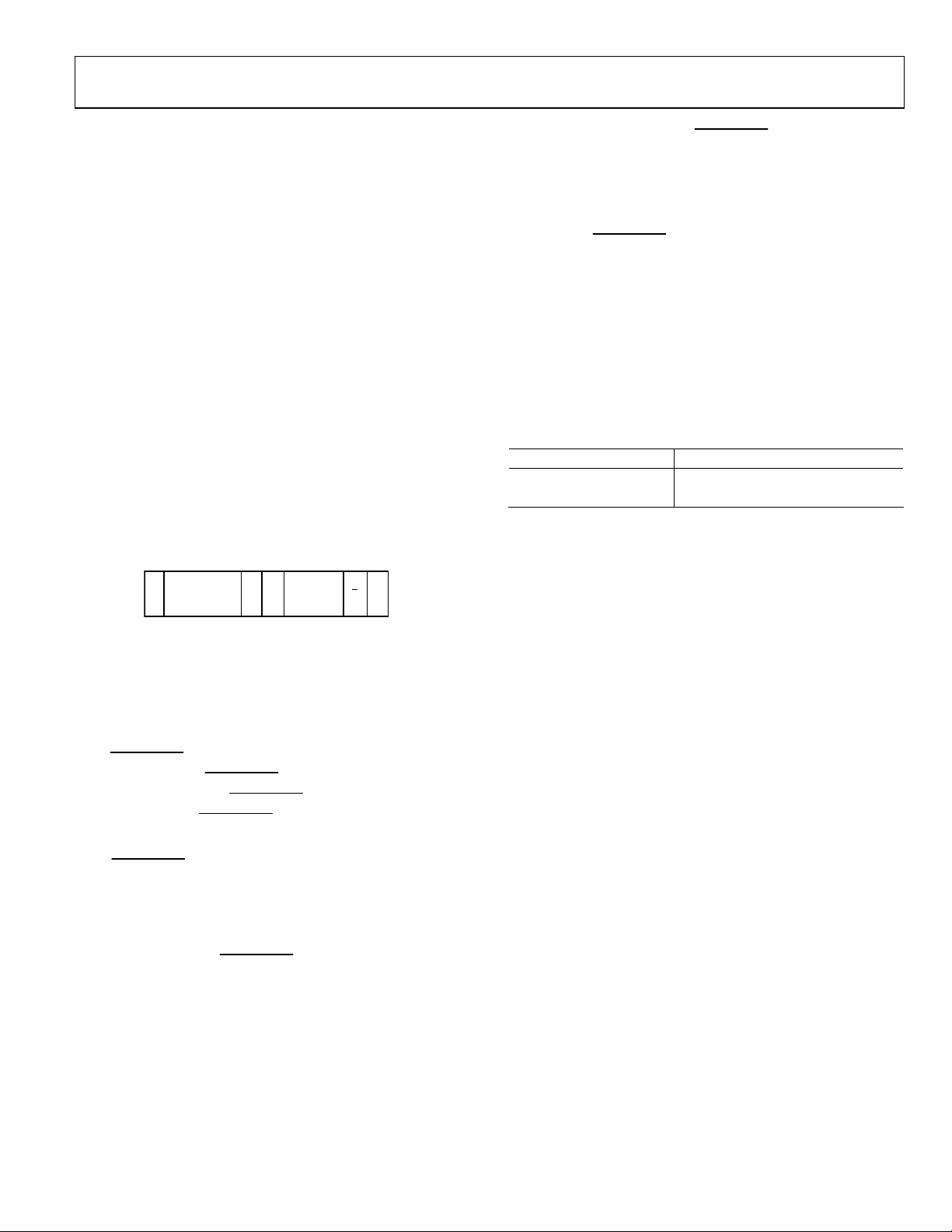

FUNCTIONAL BLOCK DIAGRAM

ADDR SDASCL

ADT7470

GENERAL DESCRIPTION

The ADT7470 controller is a multichannel temperature sensor

and PWM fan controller and fan speed monitor for noisesensitive systems requiring active system cooling. It is designed

to interface directly to an I

fans using a service processor. The aim is to quickly develop

systems that are modular and can easily be expanded depending

on the system’s cooling requirements. The device can monitor

up to 10 temperature sensors. It can also monitor and control

the speed of four fans so that they operate at the lowest possible

speed for minimum acoustic noise. A

provided to allow the fans to be “blasted” to PWMMAX, via

external hardware control, under extreme thermal conditions

or on system startup. An

error conditions such as fan underspeed and fan failure to the

system service processor. Individual error conditions can then

be read from status registers over the I

failure condition, any or all PWM outputs can be programmed to

automatically adjust to PWMMAX to provide fail-safe cooling.

SMBALERT

2

C® bus and control and monitor the

SMBALERT

FULL_SPEED

interrupt communicates

2

C bus. In the event of a fan

input is

ADT7470

FULL_SPEED

PWM1

PWM2

PWM3

PWM4

TACH1

TACH2

TACH3

TACH4

TMP_START

TMP_IN

SMBus

ADDRESS

SELECTION

PWM

REGISTERS

AND

CONTROLLERS

FAN SPEED

COUNTERS

TEMPERATURE

DECODER

SERIAL BUS

INTERFACE

AUTOMATIC

FAN SPEED

CONTROL

ADDRESS

POINTER

REGISTER

PWM

CONFIG

REGISTERS

INTERRUPT

MASKING

INTERRUPT

STATUS

REGISTERS

LIMIT

COMPARATORS

VALUE AND

LIMIT

REGISTERS

Figure 1.

Protected by Patent Numbers US6,188,189, US6,169,442, US6,097,239, US5,982,221, US5,867,012. Other patents pending.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

04684-0-001

ADT7470

TABLE OF CONTENTS

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

Thermal Characteristics .............................................................. 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Functional Description .................................................................... 7

General Description..................................................................... 7

Fan Speed Measurement.............................................................. 7

Internal Registers of the ADT7470 ............................................ 7

SMBus/I2C Communications Interface..................................... 7

Address Selection ......................................................................... 7

Write Operations ........................................................................ 10

Read Operations ......................................................................... 11

SMBus Timeout .......................................................................... 11

General-Purpose I/O Pins (Open Drain) ............................... 11

Limit Values ................................................................................ 14

8-Bit Limits.................................................................................. 14

16-Bit Limits ............................................................................... 14

Out-of-Limit Comparisons....................................................... 15

Monitoring Cycle Time ............................................................. 16

Status Registers ........................................................................... 16

SMBALERT

Handling

Masking Interrupt Sources........................................................ 18

Enabling the

Fan Drive Using PWM Control.................................................... 19

Fan Speed Measurement................................................................ 20

Tac h Input s .................................................................................. 20

Fan Speed Measurement ........................................................... 20

Fan Speed Control.......................................................................... 23

Interrupt Behavior ............................................... 17

SMBALERT

SMBALERT

Interrupts............................................. 17

Interrupt Output ........................... 18

Temperature Measurement Using TMP05/TMP06 ................... 12

Measuring Temperature ............................................................ 12

TMP05/TMP06 Decoder........................................................... 12

Thermal Zones............................................................................ 12

Temp e ratu re R e adi ng ..................................................................... 13

Interrupt Functionality and Status Registers ..............................14

REVISION HISTORY

7/05—Rev. A to Rev. B

References to PWM_IN changed to TMP_IN ...............Universal

Changes to T

Added Address Selection Section................................................... 7

Added Thermal Zones Section ..................................................... 12

Added Temperature Reading Section .......................................... 13

Added Note to Table 39 ................................................................. 32

Registers Section.................................................. 7

MIN

PWM Logic State........................................................................ 23

Manual Fan Speed Control ....................................................... 23

Automatic Fan Speed Control .................................................. 23

Registers........................................................................................... 24

Outline Dimensions ....................................................................... 39

Ordering Guide .......................................................................... 39

2/05—Rev. 0 to Rev. A

Added General-Purpose I/O Pins (Open Drain) Section......... 11

11/04—Revision 0: Initial Version

Rev. B | Page 2 of 40

ADT7470

SPECIFICATIONS

TA = T

Table 1.

Parameter

POWER SUPPLY1

FAN RPM-TO-DIGITAL CONVERTER

329 RPM Fan count = 0x3FFF

5,000 RPM Fan count = 0x0438

10,000 RPM Fan count = 0x021C

OPEN-DRAIN DIGITAL OUTPUTS, PWM1–PWM4, SMBALERT

OPEN-DRAIN SERIAL DATA BUS OUTPUT (SDA)

SMBus DIGITAL INPUTS (SCL, SDA)

DIGITAL INPUT LOGIC LEVELS (TACH INPUTS, FULL_SPEED, GPIO)

DIGITAL INPUT LOGIC LEVELS (TMP_IN)

DIGITAL INPUT CURRENT

SERIAL BUS TIMING

MIN

to T

MAX

1, , , , 2 3 4 5

, VCC = V

MIN

to V

, unless otherwise noted. T

MAX

= −40oC, T

MIN

= +125oC.

MAX

Min Typ Max Unit Test Conditions/Comments

Supply Voltage 3.0 3.3 5.5 V

Supply Current, I

Standby Current, I

CC

CC

0.5 0.8 mA

4 µA

Accuracy ±12 %

Full-Scale Count 65,535

Nominal Input RPM 109 RPM Fan count = 0xBFFF

Output Low Voltage, V

OL

High Level Output Current, I

Output Low Voltage, V

OL

High Level Output Current, I

Input High Voltage, V

Input Low Voltage, V

IH

IL

OH

OH

0.4 V I

0.1 1 µA V

0.4 V I

0.1 1 µA V

= –8.0 mA, VCC = +3.3 V

OUT

= V

OUT

= –4.0 mA, VCC = +3.3 V

OUT

= V

OUT

2.4 V

0.4 V

CC

CC

Hysteresis 500 mV

Input High Voltage, V

Input Low Voltage, V

IH

IL

2.4 V

0.8 V

Hysteresis 50 mV p-p

Input High Voltage, V

Input Low Voltage, V

Input High Current, I

Input Low Current, I

Input Capacitance, C

Clock Frequency, f

Glitch Immunity, t

Bus Free Time, t

Start Setup Time, t

Start Hold Time, t

SCL Low Time, t

SCL High Time, t

SCLK

SW

BUF

SU;STA

HD;STA

LOW

HIGH

SCL, SDA Rise Time, t

IH

IL

IH

IL

IN

r

VDD – 0.3 V

0.4 V

–5 µA VIN = V

CC

5 µA VIN = 0

5 pF

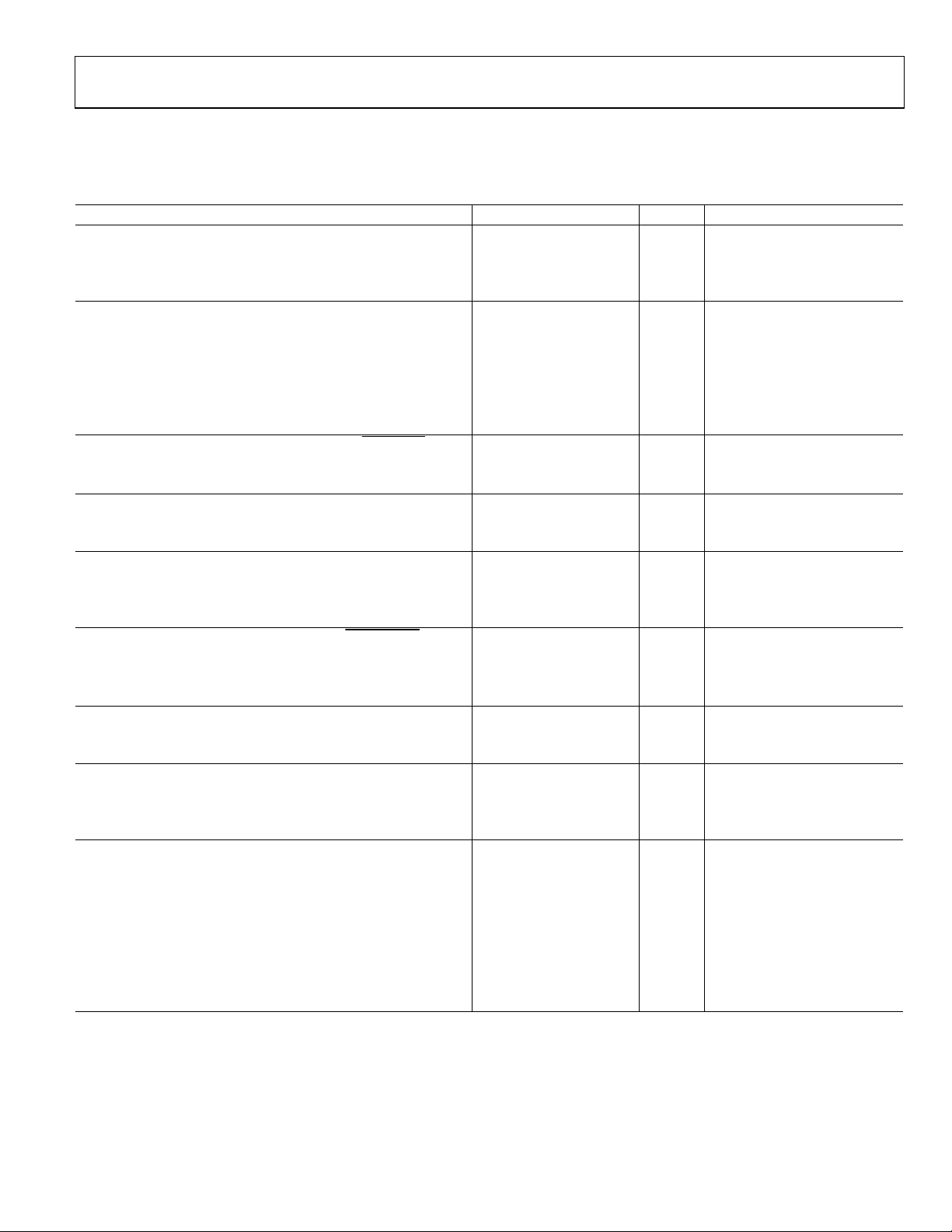

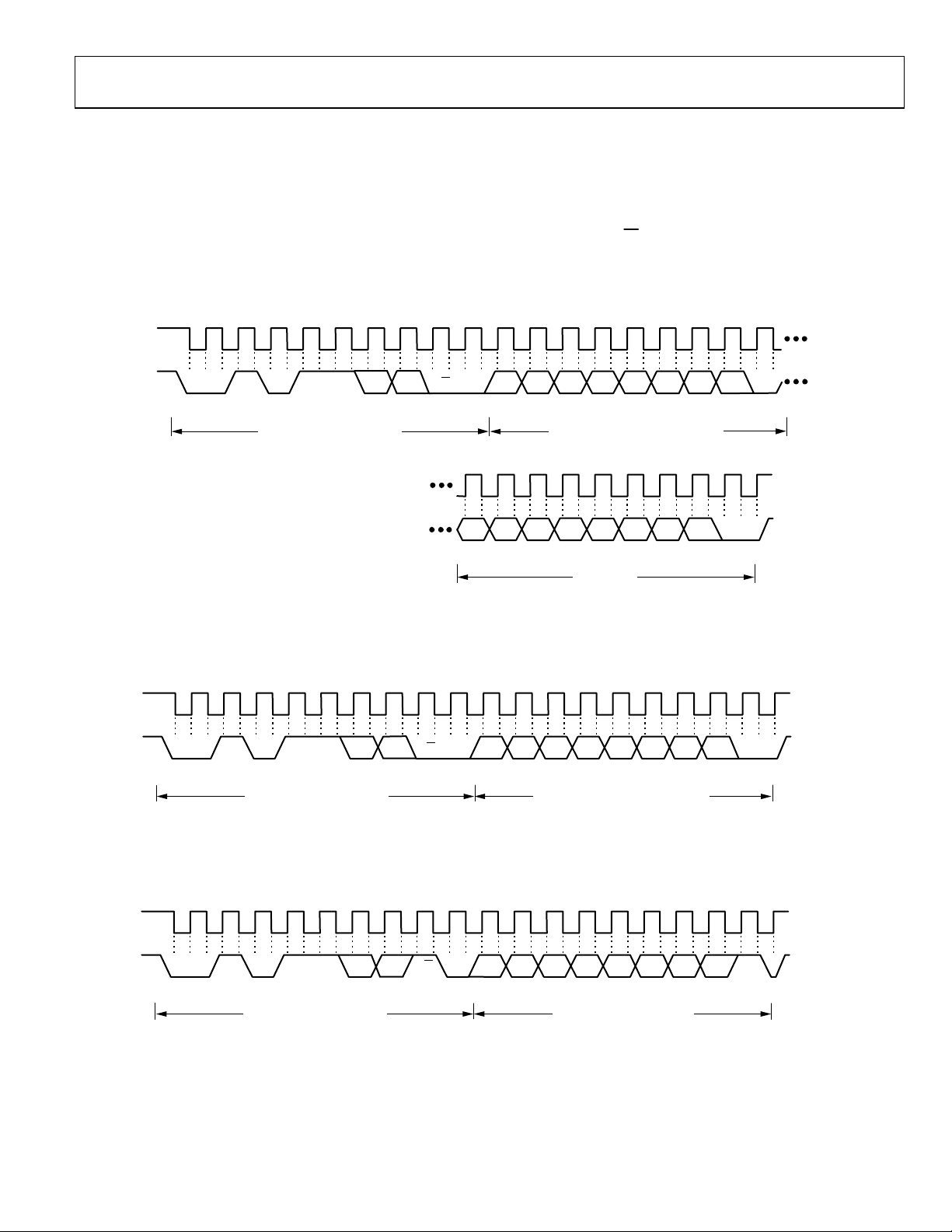

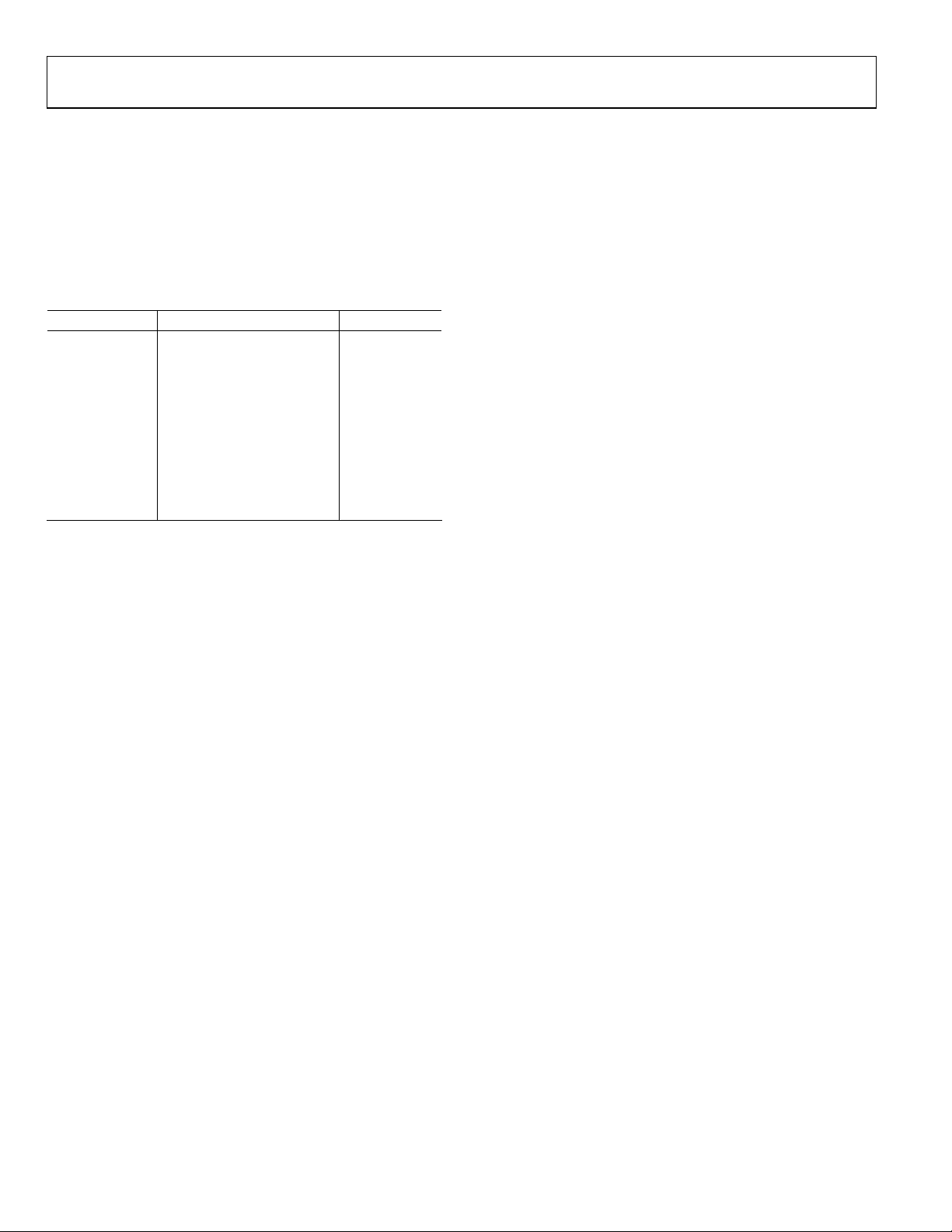

400 kHz See Figure 2

50 ns See Figure 2

1.3 µs See Figure 2

600 ns See Figure 2

600 ns See Figure 2

1.3 µs See Figure 2

0.6 µs See Figure 2

300 ns See Figure 2

Rev. B | Page 3 of 40

ADT7470

Parameter

SCL, SDA Fall Time, t

Data Setup Time, t

Detect Clock Low Timeout, t

1

VDD should never be floated in the presence of SCL/SDA activity. Charge injection can be sufficient to induce approximately 0.6 V on V

2

All voltages are measured with respect to GND, unless otherwise specified.

3

Typical values are at %A = 25°C and represent the most likely parametric norm.

4

Logic inputs accept input high voltages up to 5 V even when the device is operating at supply voltages below 5 V.

5

Timing specifications are tested at logic levels of VIL = 0.8 V for a falling edge and VIH = 2.0 V for a rising edge.

1, 2, 3, 4, 5

f

SU;DAT

TIMEOUT

Min Typ Max Unit Test Conditions/Comments

300 ns See Figure 2

100 ns See Figure 2

25 28 31 ms Can be optionally disabled

SCL

SDA

t

BUF

PS

t

HD;STA

t

LOW

t

R

t

HD;DAT

t

F

t

HIGH

t

SU;DAT

SP

Figure 2. Serial Bus Timing Diagram

t

SU;STA

t

HD;STA

t

SU;STO

DD.

04684-0-002

Rev. B | Page 4 of 40

ADT7470

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Positive Supply Voltage (VCC) 6.5 V

Voltage on Any Tach or PWM Pin –0.3 V to +6.5 V

Voltage on Any Input or Output Pin –0.3 V to VCC + 0.3 V

Maximum Junction Temperature (TJ max) 150°C

Storage Temperature Range –65°C to +150°C

Lead Temperature, Soldering

Vapor Phase, 60 sec 215°C

Infrared, 15 sec 200°C

ESD Rating 3000 V

THERMAL CHARACTERISTICS

16-Lead QSOP Package:

= 105°C/W

θ

JA

= 39°C/W

θ

JC

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. B | Page 5 of 40

ADT7470

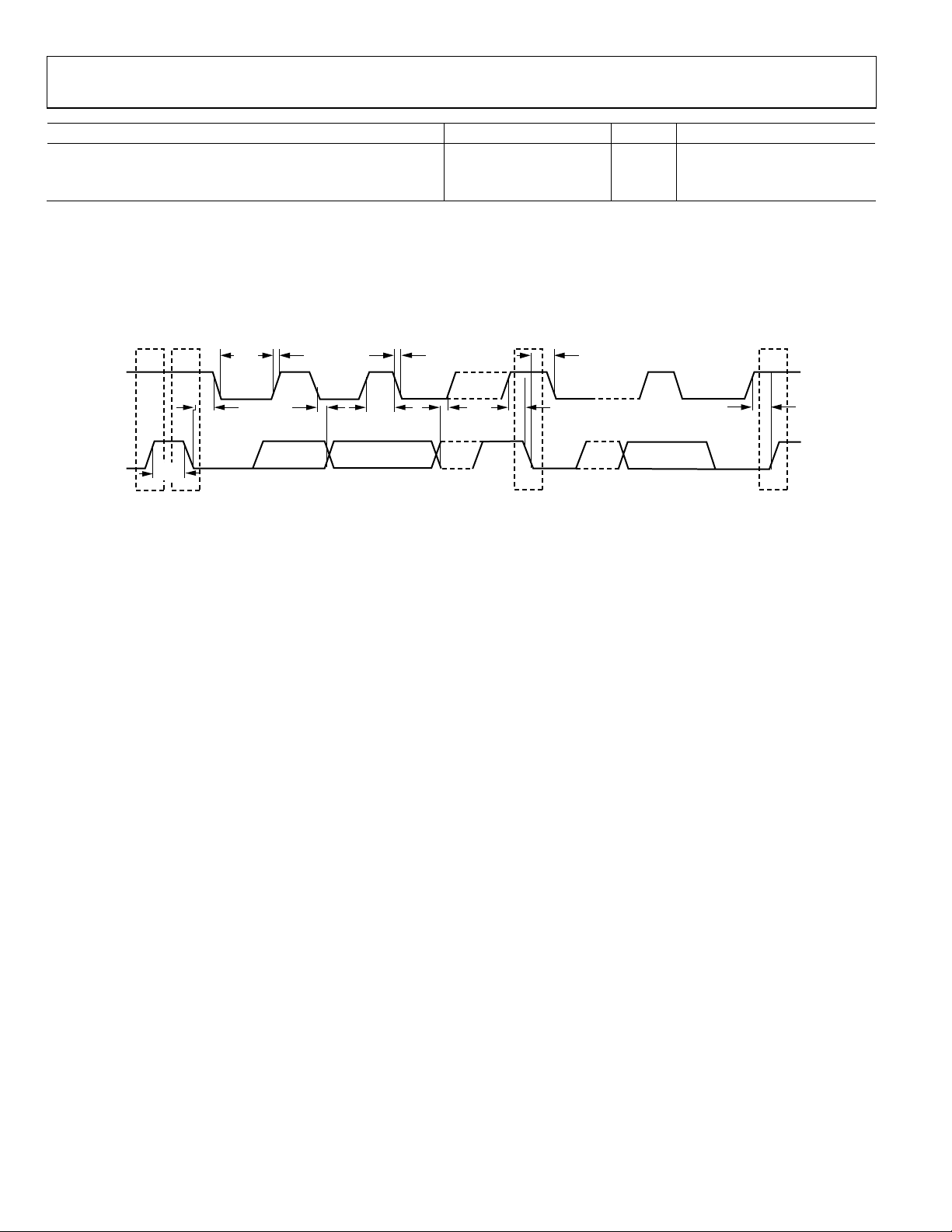

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

SCL

2

GND

3

V

CC

TACH3

PWM2

TACH1

TACH2

PWM3 TACH4

4

5

6

7

8

ADT7470

TOP VIEW

(Not to Scale)

16

SDA

15

PWM1

14

SMBALERT

13

FULL_SPEED/TMP_START

12

TMP_IN

11

ADDR

10

PWM4

9

04684-0-003

Figure 3. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 SCL Digital Input (Open Drain). SMBus serial clock input. Requires SMBus pull-up.

2 GND Ground Pin.

3 V

CC

Power Supply Pin. Can be powered by 3.3 V standby if operation in low power states is required.

4 TACH3 Digital Input (Open Drain). Fan tachometer input to measure the speed of Fan 3.

5 PWM2

Digital I/O (Open Drain). Requires 10 kΩ typical pull-up. Pulse-width modulated output to control

the speed of Fan 2. Can be configured as GPIO by setting Bit 0x7F<2> = 1.

6 TACH1 Digital Input (Open Drain). Fan tachometer input to measure the speed of Fan 1.

7 TACH2 Digital Input (Open Drain). Fan tachometer input to measure the speed of Fan 2.

8 PWM3

Digital I/O (Open Drain). Pulse-width modulated output to control the speed of Fan 3.

Requires 10 kΩ typical pull-up. Can be configured as GPIO by setting Bit 0x7F<1> = 1.

9 TACH4 Digital Input (Open Drain). Fan tachometer input to measure the speed of Fan 4.

10 PWM4

Digital I/O (Open Drain). Pulse-width modulated output to control the speed of Fan 4.

Requires 10 kΩ typical pull-up. Can be configured as GPIO by setting Bit 0x7F<0> = 1.

11 ADDR Three-state Input. Used to set the SMBus device address.

12 TMP_IN

Digital Input (Open Drain). PWM input to PWM processing engine that interprets daisy-chained output

from multiple TMP05 temperature sensors. Readings from individual TMP05 temperature sensors are

available by reading the temperature reading registers over the SMBus.

13

FULL_SPEED Digital Input Active Low (Open Drain). This input blasts the fans to PWMMAX when the pin is pulled low

externally.

13 TMP_START

Digital Output (Open Drain). This pin can be used as an output to start daisy-chained temperature

measurements from TMP05 or TMP06 temperature sensors.

14

SMBALERT Digital Output Active Low (Open Drain). This pin can be reconfigured as an SMBALERT interrupt output

to signal out-of-limit conditions such as fan failures.

15 PWM1

Digital I/O (Open Drain). Pulse-width modulated output to control the speed of Fan 1.

Requires 10 kΩ typical pull-up. Can be configured as GPIO by setting Bit 0x7F<3> = 1.

16 SDA Digital I/O (Open Drain). SMBus bidirectional serial data. Requires SMBus pull-up.

Rev. B | Page 6 of 40

ADT7470

FUNCTIONAL DESCRIPTION

GENERAL DESCRIPTION

The ADT7470 is a multichannel, pulse-width modulation

(PWM) fan controller and monitor for any system requiring

monitoring and cooling. The device communicates with the

system via a serial system management bus. The device has a

single address line for address selection (Pin 11), a serial data

line for reading and writing addresses and data (Pin 16), and

an input line for the serial clock (Pin 1). All control and

programming functions of the ADT7470 are performed over

2

the serial bus, which supports both SMBus and fast I

specifications. In addition, an

SMBALERT

interrupt output

C

is provided to indicate out-of-limit conditions.

FAN SPEED MEASUREMENT

When the ADT7470 monitoring sequence is started, it cycles

through each fan tach input to measure fan speed. Measured

values from these inputs are stored in value registers. These

can be read out over the serial bus, or they can be compared

with programmed limits stored in the limit registers. The results

of out-of-limit comparisons are stored in the status registers,

which can be read over the serial bus to flag out-of-limit

conditions. If fan speeds drop below preset levels or a fan stalls,

an interrupt is generated, and the fans can automatically blast

to PWMMAX. Likewise, the ADT7470 can flag fan overspeed

conditions by using fan tach max registers.

INTERNAL REGISTERS OF THE ADT7470

A brief description of the ADT7470’s principal internal registers

is given in the following sections. For detailed information on

the function of each register, see the register map in Table 21.

Configuration Registers

These registers provide control and configuration of the

ADT7470, including alternate pinout functionality such as

a fan blast input (

measurement (start) output.

Address Pointer Register

This register contains the address that selects one of the other

internal registers. When writing to the ADT7470, the first byte

of data is always a register address that is written to the address

pointer register.

Status Registers

These registers provide status of each limit comparison and are

used to signal out-of-limit conditions on the fan speed channels,

or on the temperature channels if monitored using the TMP_IN

feature. If Pin 14 (

asserts low whenever a status bit is set, signaling an out-of-limit

condition.

FULL_SPEED

SMBALERT

) or daisy-chained TMP05

) is used in the system, this pin

Interrupt Mask Registers

The interrupt mask registers allow each interrupt status event

to be individually masked from driving the

SMBALERT

output

as required. This is useful where fan tach inputs are unused and

left floating, or if temperature inputs from TMP05s are ignored

from an interrupt perspective. Masking interrupt status bits

prevents the

SMBALERT

output from being driven, although

the status bits still reflect out-of-limit conditions. This can prevent a service processor from being continually tied up in an

interrupt service routine if a value remains outside limits for

a relatively long duration.

Value and Limit Registers

The results of fan speed measurements are stored in these registers, along with their limit values. The limit values store the

slowest speed at which the fans are expected to run. Alternatively,

the limit value can determine the expected fan failure in terms

of running speed, in case the fan does not completely stall.

If TMP05s and TMP06s are daisy-chained in through the

TMP_IN pin, the measured temperatures are stored in temperature value registers.

Registers

T

MIN

These registers program the starting temperature for each fan

under automatic fan speed control. T

= T

Therefore, T

MAX

+ 20°C. Fan on/off hysteresis is set

MIN

is set to 20°C.

RANGE

at 4°C so that the fans turn off 4°C below the temperature

at which they turn on. This prevents fan chatter in the system.

SMBus/I2C COMMUNICATIONS INTERFACE

Serial Bus Interface

Control of the ADT7470 is carried out using the serial system

management bus (SMBus). This interface is fully compatible

with SMBus 2.0 electrical specifications and meets 400 pF bus

2

capacitance requirements. The device also supports fast I

C

(400 kHz max). The ADT7470 is connected to the bus as a slave

device under the control of a master controller or service

processor.

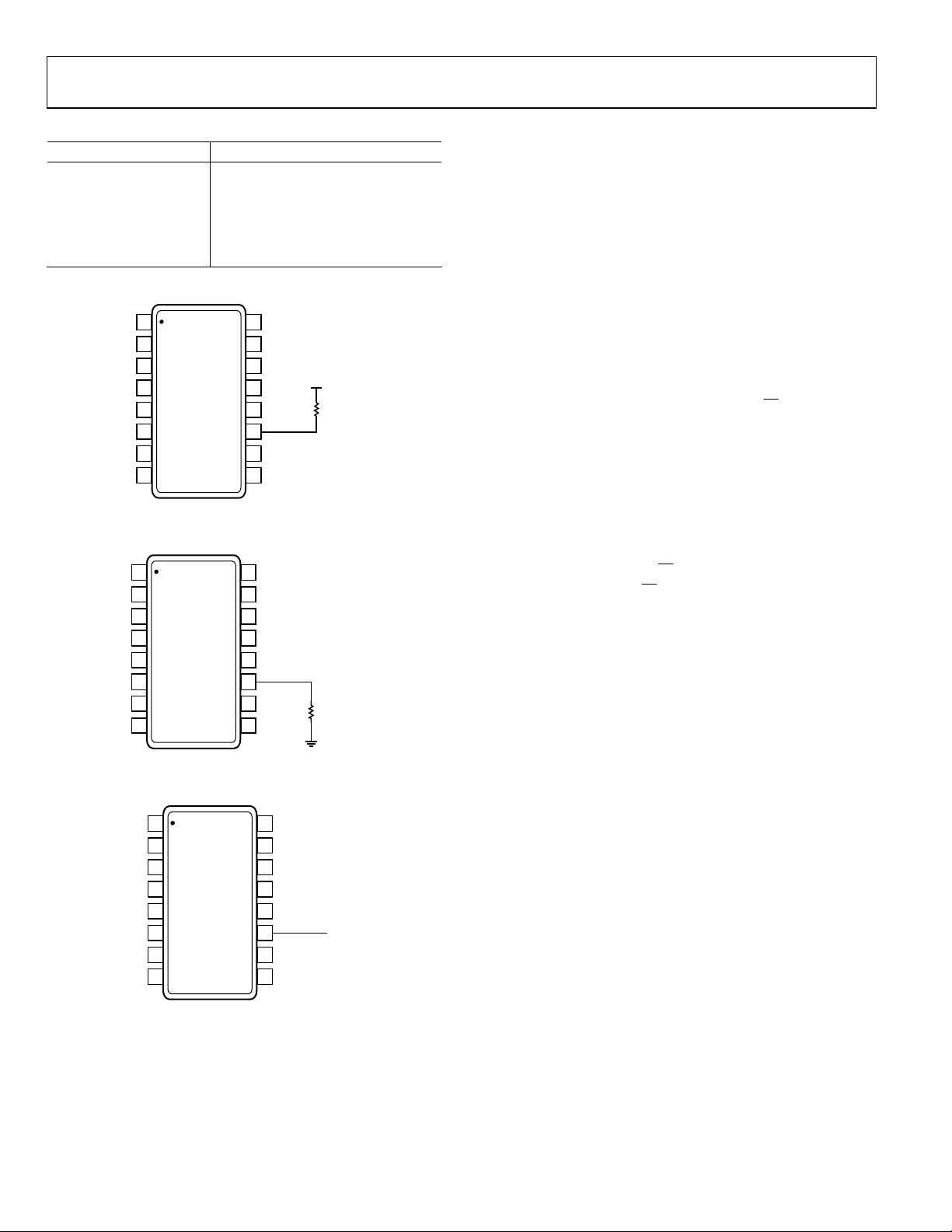

ADDRESS SELECTION

The ADT7470 has a 7-bit serial bus address. When the device

is powered up with Pin 11 (ADDR) high, the ADT7470 has an

SMBus address of 010 1111 or 0x5E (left-justified). Because the

address is 7 bits, it can be left- or right-justified; this determines

whether the address reads as 0x5x or 0x2x. Pin 11 can be left

floating or tied low for other addressing options, as shown in

Table 4. See also Figure 4, Figure 5, and Figure 6.

Rev. B | Page 7 of 40

ADT7470

Table 4. ADT7470 Address Select Mode

Pin 11 (ADDR) State Address

High (10 kΩ to VCC)

Low (10 kΩ to GND)

Floating (no pull-up)

1

2

3

4

5

6

7

8

Figure 4. SMBus Address = 0x5E or 0x2F (Pin 11 = 1)

1

2

3

ADT7470

4

5

6

7

8

Figure 5. SMBus Address = 0x58 or 0x2C (Pin 11 = 0)

1

2

3

4

5

6

7

8

Figure 6. SMBus Address = 0x5C or 0x2E (Pin 11 = Floating)

010 1111 (0x5E left-justified or

0x2F right-justified)

010 1100 (0x58 left-justified or

0x2C right-justified)

010 1110 (0x5C left-justified or

0x2E right-justified)

16

15

ADT7470

ADT7470

14

13

12

ADDR

11

10

9

16

15

14

13

12

ADDR

11

10

9

16

15

14

13

12

ADDR

11

10

9

The device address is sampled and latched on the first valid

SMBus transaction, so any additional attempted addressing

changes have no immediate effect. The facility to make

hardwired changes to the SMBus slave address allows the user

to avoid conflicts with other devices sharing the same serial bus,

for example, if more than one ADT7470 is used in a system.

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a start

condition, defined as a high-to-low transition on the serial

data line, SDA, while the serial clock line, SCL, remains

high. This indicates that an address/data stream follows.

V

CC

10kΩ

TYP

All slave peripherals connected to the serial bus respond

to the start condition, and shift in the next 8 bits, consist-

W

ing of a 7-bit address (MSB first) and an R/

bit. This

determines the direction of the data transfer, that is,

whether data is written to or read from the slave device.

The peripheral whose address corresponds to the transmit-

04684-0-004

ted address responds by pulling the data line low during

the low period before the 9th clock pulse, known as the

acknowledge bit. All other devices on the bus now remain

idle while the selected device waits for data to be read from

W

or written to it. If the R/

slave device. If the R/

bit is 0, the master writes to the

W

bit is 1, the master reads from the

slave device.

2. Data is sent over the serial bus in sequences of 9 clock pulses:

8 bits of data followed by an acknowledge bit from the slave

device. Transitions on the data line must occur during the

10kΩ

TYP

04684-0-005

low period of the clock signal and remain stable during the

high period. This is because a low-to-high transition when

the clock is high might be interpreted as a stop signal. The

number of data bytes that can be transmitted over the serial

bus in a single read or write operation is limited only by

what the master and slave devices can handle.

3. After all data bytes are read or written, stop conditions

are established. In write mode, the master pulls the data

line high during the 10th clock pulse to assert a stop

condition. In read mode, the master device overrides

the acknowledge bit by pulling the data line high during

the low period before the 9th clock pulse. This is known as

No Acknowledge. The master then takes the data line low

during the low period before the 10th clock pulse, then

high during the 10th clock pulse to assert a stop condition.

04684-0-006

Any number of bytes of data can be transferred over the serial

bus in one operation. However, it is not possible to mix read

and write in one operation, because the type of operation is

determined at the beginning and subsequently cannot be

changed without starting a new operation.

Rev. B | Page 8 of 40

ADT7470

A

A

A

In the ADT7470, write operations contain either one or two

bytes, and read operations contain one byte and perform the

following functions.

To write data to one of the device data registers or read data

from it, the address pointer register must be set so that the

correct data register is addressed. Then data can be written into

that register or read from it. The first byte of a write operation

1

SCL

991

always contains an address that is stored in the address pointer

register. If data is to be written to the device, the write operation

contains a second data byte that is written to the register selected

by the address pointer register.

This is illustrated in Figure 7. The device address is sent over the

W

bus followed by R/

set to 0. This is followed by two data bytes.

SD

START BY

MASTER

001 1 1 A1 A0 R/W

FRAME 1

SERIAL BUS ADDRESS

BYTE

SCL (CONTINUED)

SDA (CONTINUED)

ACK. BY

ADT7470

D7 D6 D5 D4 D3 D2 D1 D0

FRAME 3

DATA

BYTE

FRAME 2

ADDRESS POINTER REGISTER BYTE

1

D7 D6 D5 D4 D3 D2 D1 D0

9

ACK. BY

ADT7470

ACK. BY

ADT7470

STOP BY

MASTER

04684-0-007

Figure 7. Writing a Register Address to the Address Pointer Register, Then Writing Data to the Selected Register

991

R/W D7 D6 D5 D4 D3 D2 D1 D0

ACK. BY

ADT7470

ADDRESS POINTER REGISTER BYTE

FRAME 2

ACK. BY

ADT7470

STOP BY

MASTER

04684-0-008

SCL

SD

START BY

MASTER

1

01 01 1A1A0

FRAME 1

SERIAL BUS ADDRESS

BYTE

Figure 8. Writing to the Address Pointer Register Only

1

SCL

991

SD

START BY

MASTER

01 01 1A1A0

FRAME 1

SERIAL BUS ADDRESS

BYTE

R/W D7 D6 D5 D4 D3 D2 D1 D0

ACK. BY

ADT7470

FRAME 2

DATA BYTE FROM

ADT7470

NO ACK.

BY MASTER

STOP BY

MASTER

04684-0-009

Figure 9. Reading Data from a Previously Selected Register

Rev. B | Page 9 of 40

ADT7470

The first data byte is the address of the internal data register

to be written to, which is stored in the address pointer register.

The second data byte is the data to be written to the internal

data register.

How data is read from a register depends on whether or not

the address pointer register value is known.

If the ADT7470 address pointer register value is unknown or

not the desired value, it is first necessary to set it to the correct

value before data can be read from the desired data register.

This is done by performing a write to the ADT7470 as before,

but only the data byte containing the register address is sent,

because data cannot be written to the register. This is shown

in Figure 8.

A read operation is then performed consisting of the serial bus

W

address, R/

the data register. This is shown in Figure 9.

If the address pointer register is known to be already at the

desired address, data can be read from the corresponding data

register without first writing to the address pointer register,

so the operation shown in Figure 8 can be omitted.

Note the following:

• Although it is possible to read a data byte from a data

register without first writing to the address pointer register

if the address pointer register is already at the correct value,

it is not possible to write data to a register without writing

to the address pointer register. This is because the first data

byte of a write is always written to the address pointer

register.

• In Figure 7 to Figure 9, the serial bus address is shown as

the default value 01011(A1)(A0), where A1 and A0 are set

by the address select mode function previously defined.

• In addition to supporting the send byte and receive byte

protocols, the ADT7470 also supports the read byte

protocol. See System Management Bus Specifications

Rev. 2.0 for more information.

• If it is required to perform several read or write operations

in succession, the master can send a repeat start condition

instead of a stop condition to begin a new operation.

WRITE OPERATIONS

The SMBus specification defines several protocols for different

types of read and write operations. The protocols used in the

ADT7470 are discussed in the following sections. The following

abbreviations are used in the diagrams:

S—Start

P—Stop

R—Read

W—Wri te

A—Acknowl edge

A

—No Acknowledge

bit set to 1, followed by the data byte read from

The ADT7470 uses the following SMBus write protocols.

Send Byte

In this protocol, the master device sends a single command byte

to a slave device, as follows:

1. The master device asserts a start condition on SDA.

2. The master sends the 7-bit slave address followed by

the write bit (low).

3. The addressed slave device asserts ACK on SDA.

4. The master sends a command code.

5. The slave asserts ACK on SDA.

6. The master asserts a stop condition on SDA,

and the transaction ends.

For the ADT7470, the send byte protocol is used to write a

register address to RAM for a subsequent single byte read

from the same address. This is shown in Figure 10.

12 3 4 56

SLAVE

SWA A

ADDRESS

Figure 10. Setting a Register Address for Subsequent Read

REGISTER

ADDRESS

P

04684-0-010

If it is required to read data from the register immediately after

setting up the address, the master can assert a repeat start condition immediately after the final ACK and carry out a singlebyte read without asserting an intermediate stop condition.

Write Byte

In this operation, the master device sends a command byte and

one data byte to the slave device, as follows:

1. The master device asserts a start condition on SDA.

2. The master sends the 7-bit slave address followed by the

write bit (low).

3. The addressed slave device asserts ACK on SDA.

4. The master sends a command code.

5. The slave asserts ACK on SDA.

6. The master sends a data byte.

7. The slave asserts ACK on SDA.

8. The master asserts a stop condition on SDA to end

the transaction.

This is shown in Figure 11.

12 3 4 5678

SLAVE

SWA AADATA

ADDRESS

Figure 11. Single-Byte Write to a Register

REGISTER

ADDRESS

P

04684-0-011

Rev. B | Page 10 of 40

ADT7470

READ OPERATIONS

The ADT7470 uses the following SMBus read protocols.

Receive Byte

This is useful when repeatedly reading a single register.

The register address must be set up previously. In this

operation, the master device receives a single byte from

a slave device, as follows:

4. If more than one device’s

the one with the lowest device address has priority,

in accordance with normal SMBus arbitration.

5. Once the ADT7470 responds to the alert response

address, the master must read the status registers,

and the

SMBALERT

tion is gone.

SMBALERT

output is low,

is cleared only if the error condi

1. The master device asserts a start condition on SDA.

2. The master sends the 7-bit slave address followed by

the read bit (high).

3. The addressed slave device asserts ACK on SDA.

4. The master receives a data byte.

5. The master asserts NO ACK on SDA.

6. The master asserts a stop condition on SDA

and the transaction ends.

In the ADT7470, the receive byte protocol is used to read a

single byte of data from a register whose address was previously

set by a send byte or write byte operation.

12 3456

SLAVE

S R A DATA A P

ADDRESS

Figure 12. Single-Byte Write from a Register

04684-0-012

Alert Response Address

Alert response address (ARA) is a feature of SMBus devices,

which allows an interrupting device to identify itself to the host

when multiple devices exist on the same bus.

SMBALERT

The

or can be used as an

connected to a common

master. If a device’s

output can be used as an interrupt output

SMBALERT

SMBALERT

SMBALERT

. One or more outputs can be

line connected to the

line goes low, the following

occurs:

SMBALERT

1.

is pulled low.

2. The master initiates a read operation and sends the alert

response address (ARA = 000 1100). This is a general call

address that must not be used as a specific device address.

3. The device whose

SMBALERT

output is low responds to

the alert response address, and the master reads its device

address. The address of the device is now known, and it

can be interrogated in the usual way.

SMBus TIMEOUT

The ADT7470 includes an SMBus timeout feature. If there is no

SMBus activity for more than 31 ms, the ADT7470 assumes that

the bus is locked and releases the bus. This prevents the device

from locking or holding the SMBus expecting data. Some SMBus

controllers cannot handle the SMBus timeout feature, so it can

be disabled.

Table 5. Configuration Register 1—Register 0x40

Bit Address and Value Description

<3> TODIS = 0 SMBus timeout enabled (default).

<3> TODIS = 1 SMBus timeout disabled.

Although the ADT7470 supports packet error checking (PEC),

its use is optional. It is triggered by supplying the extra clock

for the PEC byte. The PEC byte is calculated using CRC-8.

The frame check sequence (FCS) conforms to CRC-8 by the

following polynomial:

8

C(x) = x

+ x2 + x1 + 1

Consult the SMBus 1.1 Specification for more information

(www.smbus.org).

GENERAL-PURPOSE I/O PINS (OPEN DRAIN)

The ADT7470 has four pins that can be configured as either

general-purpose logic pins or as PWM outputs They are configured as general-purpose logic pins by setting Bit 0 to Bit 3

of the TMP05 COEF Select 2 Register (Address 0x07F). Each

GPIO pin has three data bits associated with it: two bits in the

GPIO configuration register (Address 0x80) and one in the

GPIO status register (Address 0x81).

Setting a direction bit to 1 in the GPIO configuration register

makes the corresponding GPIO pin an output. Clearing the

direction bit to 0 makes it an input. Setting a polarity bit to 1

makes the corresponding GPIO pin active high. Clearing the

polarity bit to 0 makes it active low. When a GPIO pin is configured as an input, the corresponding bit in the GPIO status

register is read-only and is set when the input is asserted.

When a GPIO pin is configured as an output, the corresponding

bit in one of the GPIO status registers becomes read/write.

Setting this bit asserts the GPIO output. Note that whether a

GPIO pin is configured as an input or as an output, “asserted”

can be high or low, depending on the setting of the polarity bit.

Rev. B | Page 11 of 40

ADT7470

TEMPERATURE MEASUREMENT USING TMP05/TMP06

MEASURING TEMPERATURE

For more information, refer to the TMP05/TMP06 data sheet.

TMP05 generates a PWM output proportional to temperature,

which can be easily interfaced to most microprocessors or CPUs.

Table 6 lists the temperature reading registers on the ADT7470.

Table 6. Temperature Reading Registers

Register Reading Default

0x20 Temperature 1 Reading 0x00

0x21 Temperature 2 Reading 0x00

0x22 Temperature 3 Reading 0x00

0x23 Temperature 4 Reading 0x00

0x24 Temperature 5 Reading 0x00

0x25 Temperature 6 Reading 0x00

0x26 Temperature 7 Reading 0x00

0x27 Temperature 8 Reading 0x00

0x28 Temperature 9 Reading 0x00

0x29 Temperature 10 Reading 0x00

Reporting of 8-bit temperature values occurs in the preceding

registers only if the TMP_IN function is used and if TMP05s

and TMP06s are daisy-chained according to their data sheet

and connected as shown in Figure 13. This device does not have

any temperature measurement capability when used as a standalone device without TMP05s and TMP06s connected.

TMP05/TMP06 DECODER

The ADT7470 includes a PWM processing engine to decode the

daisy-chained PWM output from multiple TMP05s and TMP06s.

It then passes each decoded temperature value to temperature

value registers. This allows the ADT7470 to do high/low limit

comparisons of temperature and to automatically control fan

speed based on measured temperature. The PWM processing

engine contains all necessary logic to initiate start conversions

on the first daisy-chained TMP05/TMP06 and to synchronize

with each temperature value as it is fed back to the device through

the daisy chain. The start function is multiplexed onto the same

pin that can be used to blast the fans to full speed. The start

conversion for TMP05/TMP06 temperature measurement is

fully transparent to the user and does not require any software

intervention to function.

THERMAL ZONES

Using Reg7Ch and Reg7Dh, the user can set up which TMP05

controls which fan. An individual TMP05, or the hottest TMP05

in the daisy chain, can control each fan. This allows the ADT7470

to create and control up to four independent thermal zones. In a

system with n TMP05s, it is possible to have 1 or n TMP05s

controlling each fan.

Rev. B | Page 12 of 40

Loading...

Loading...