Datasheet ADSP-BF522C, ADSP-BF523C, ADSP-BF524C, ADSP-BF525C, ADSP-BF526C Datasheet (ANALOG DEVICES)

...Page 1

Blackfin Embedded

Processor with Codec

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

PROCESSOR FEATURES

Up to 600 MHz high performance Blackfin processor

RISC-like register and instruction model for ease of

programming and compiler-friendly support

Advanced debug, trace, and performance monitoring

Accepts a wide range of supply voltages for internal and I/O

operations. See operating conditions in the published

ADSP-BF52x processor data sheet.

Programmable on-chip voltage regulator (ADSP-BF523/

ADSP-BF525/ADSP-BF527processors only)

Embedded low power audio codec

289-ball (12 mm x 12 mm) CSP_BGA package

132K bytes of on-chip memory

External memory controller with glueless support for SDRAM

and asynchronous 8-bit and 16-bit memories

Flexible booting options from external flash, SPI and TWI

memory or from host devices including SPI, TWI, and UART

Code security with Lockbox Secure Technology

one-time-programmable (OTP) memory

Memory management unit providing memory protection

2 dual-channel memory DMA controllers

EMBEDDED CODEC FEATURES

Stereo, 24-bit ADCs and DACs

DAC SNR: 100 dB (A-weighted), THD: –80 dB at 48 kHz, 3.3 V

ADC SNR: 90 dB (A-weighted), THD: –80 dB at 48 kHz, 3.3 V

Highly efficient headphone amplifier

Stereo line input and monaural microphone input

Low power

7 mW stereo playback (1.8 V supply)

14 mW record and playback (1.8 V supply)

Low supply voltages

Analog: 1.8 V to 3.6 V

Digital core: 1.8 V min

Digital I/O: 1.8 V to 3.6 V

256 × f

/384 × fS oversampling rate in normal mode;

S

250 × fS/272 × fS oversampling rate in USB mode

Audio sampling rates: 8 kHz, 11.025 kHz, 12 kHz, 16 kHz,

22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz,

and 96 kHz

PERIPHERALS

See the published ADSP-BF52x processor data sheet for

additional peripherals

WATCHDOG TIMER

VOLTAGE REGULATOR*

B

L1 INSTRUCTION

MEMORY

EAB

USB

*REGULATOR AVAILABLE ON ADSP-BF523/ADSP-BF525/ADSP-BF527 PROCESSORS ONLY

Blackfin and the Blackfin logo are registered trademarks of Analog Devices, Inc.

16

EXTERNAL PORT

FLASH, SDRAM CONTROL

JTAG TEST AND EMULATION

CONTROLLER

L1 DATA

MEMORY

CONTROLLER

DCB

INTERRUPT

DMA

DEB

PERIPHERAL

ACCESS BUS

DMA

ACCESS

BUS

BOOT

ROM

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

OTP MEMORY

RTC

COUNTER

SPORT0

SPORT1

UART 1

UART 0

NFC

PPI

SPI

TIMER7-1

TIMER0

EMAC

HOST DMA

TWI

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2010 Analog Devices, Inc. All rights reserved.

GPIO

PORT F

GPIO

PORT G

GPIO

PORT H

PORT J

CODEC

Page 2

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

TABLE OF CONTENTS

Processor Features ................................................... 1

Embedded Codec Features ......................................... 1

Peripherals ............................................................. 1

Table of Contents ..................................................... 2

Revision History ...................................................... 2

General Description ................................................. 3

Codec Description ................................................ 3

ADC and DAC ..................................................... 4

ADC High-Pass and DAC De-Emphasis Filters ............ 4

Analog Audio Interfaces ......................................... 4

Stereo Line and Monaural Microphone Inputs .......... 4

Bypass and Sidetone Paths to Output ...................... 5

Line and Headphone Outputs ............................... 5

Digital Audio Interface ........................................... 6

Recording Mode ................................................ 8

Playback Mode .................................................. 8

Digital Audio Data Sampling Rate .......................... 8

Software Control Interface .................................... 11

Codec Pin Descriptions ........................................... 12

Register Details ..................................................... 15

Bit Descriptions .................................................. 16

Specifications ........................................................ 21

Operating Conditions ........................................... 21

Codec Electrical Characteristics .............................. 21

Absolute Maximum Ratings ................................... 23

ESD Sensitivity ................................................... 23

Package Information ............................................ 23

Power Consumption ............................................ 24

Timing Specifications ........................................... 25

TWI Timing ................................................... 25

SPI Timing ..................................................... 26

Digital Audio Interface Slave Mode Timing ............ 27

Digital Audio Interface Master Mode Timing .......... 28

System Clock Timing ........................................ 29

Digital Filter Characteristics ................................ 30

Converter Filter Response ..................................... 30

Digital De-Emphasis ............................................ 31

289-Ball CSP_BGA Ball Assignment ........................ 32

Outline Dimensions ................................................ 35

Ordering Guide ..................................................... 36

REVISION HISTORY

3/10—Rev. 0 to Rev. A

Revised the following figures.

Recommended Application Circuit Using SPI Control ... . 13

Recommended Application Circuit Using TWI Control .. 14

Added Sampling Rate = 48 kHz to all figures in

Converter Filter Response ........................................ 30

Revised Ordering Guide .......................................... 36

Rev. A | Page 2 of 36 | March 2010

Page 3

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

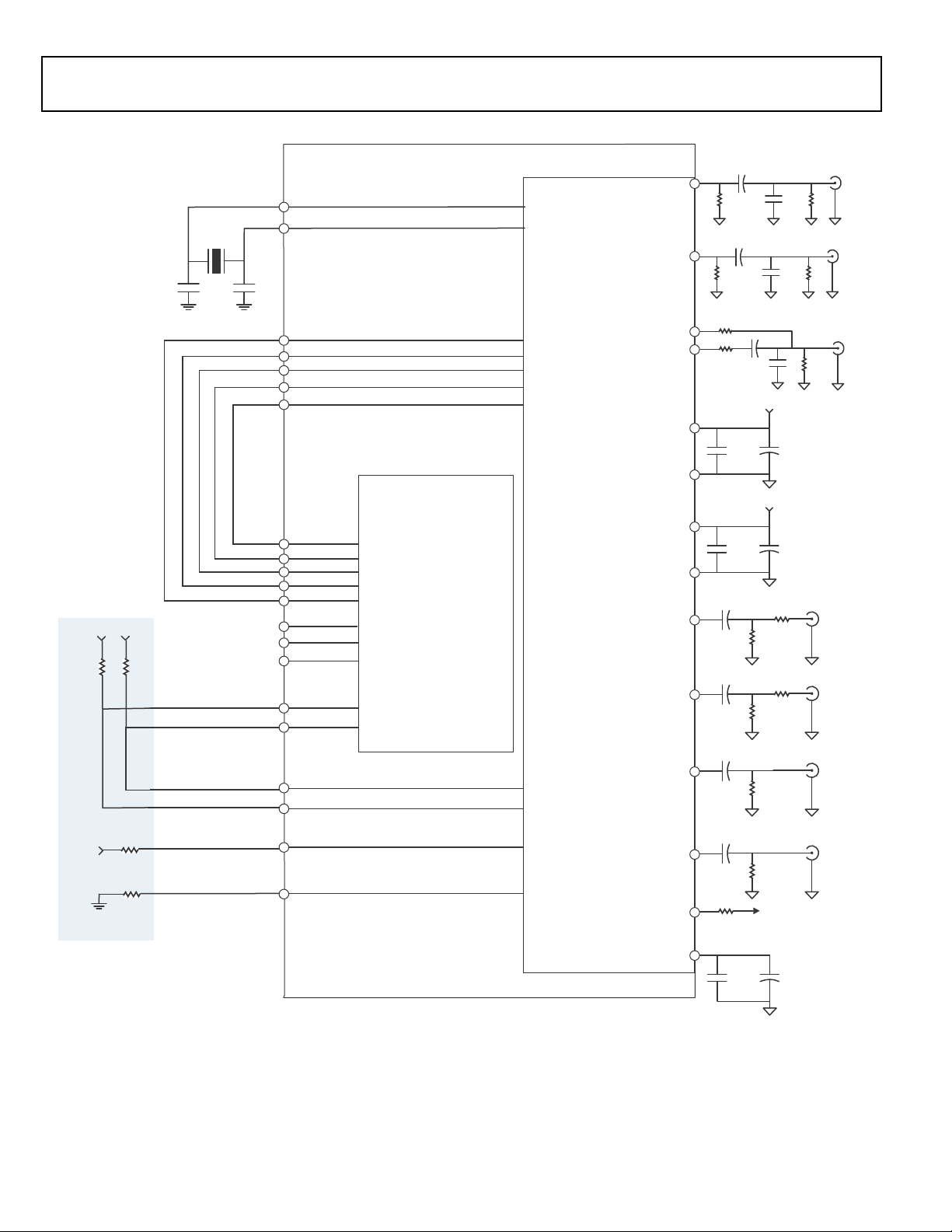

CODEC

AVDD

VMID

AGND

MICBIAS

CSB CSDA CSCL CMODE

CONTROL INTERFACE

RLINEIN

MICIN

LLINEIN

OSCPD

OSC

CLKIN

DIVIDER

CLKOUT

DIVIDER

DIGITAL AUDIO INTERFACE

VOLUME

VOLUME

MIC

BOOST

MUTE

MUTE

MUTE

MUTE

MUX

MUX

ADC

ADC

DIGITAL

FILTERS

HPVDD

HPGND

RHPOUT

ROUT

LOUT

LHPOUT

HEADPHONE

DRIVER

HEADPHONE

DRIVER

VOLUME/

MUTE

VOLUME/

MUTE

MUTE

ATTEN/

MUTE

ATTEN/

MUTE

MUTEDAC

DAC MUTE

MUTE

Σ

Σ

XTO

XTI/CODEC_MCLK

CODEC_CLKOUT

DACDAT

DACLRC

CODEC_BCLK

ADCLRC

ADCDAT

GENERAL DESCRIPTION

This document describes the differences between the

ADSP-BF52xC and the ADSP-BF52x standard Blackfin

®

product. Please refer to the published ADSP-BF52x data sheet for

general description and specifications. This document only

describes the differences from that data sheet.

The ADSP-BF52xC processors add a low power, high quality

stereo audio codec for portable digital audio applications with

one set of stereo programmable gain amplifier (PGA) line

inputs and one monaural microphone input. It features two 24bit analog-to-digital converter (ADC) channels and two 24-bit

digital-to-analog (DAC) converter channels.

The codec can operate as a master or a slave. It supports various

master clock frequencies, including 12 MHz or 24 MHz for USB

devices; standard 256 × f

or 384 × fS based rates, such as

S

12.288 MHz and 24.576 MHz; and many common audio sampling rates, such as 96 kHz, 88.2 kHz, 48 kHz, 44.1 kHz, 32 kHz,

24 kHz, 22.05 kHz, 16 kHz, 12 kHz, 11.025 kHz, and 8 kHz.

The codec can operate at power supplies as low as 1.8 V for the

analog circuitry and as low as 1.8 V for the digital circuitry. The

maximum voltage supply is 3.6 V for all supplies.

The codec software-programmable stereo output options

provide the programmer with many application possibilities

because the device can be used as a headphone driver or as a

speaker driver. Its volume control functions provide a large

range of gain control of the audio signal.

CODEC DESCRIPTION

The ADSP-BF52xC codec contains a central clock source, called

the codec master clock (CODEC_MCLK) that produces a reference clock for all internal audio data processing and synchronization. When using an external clock source to drive the

CODEC_MCLK pin, care should be taken to select a clock

source with less than 50 ps of jitter. Without careful generation

of the CODEC_MCLK signal, the digital audio quality

will suffer.

To enable the codec to generate the central reference clock

in a system, connect a crystal oscillator between the XTI/

CODEC_MCLK input pin and the XTO output pin.

Rev. A | Page 3 of 36 | March 2010

Figure 1. Codec Block Diagram

Page 4

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

ADC

OR

BYPASS

RLINEIN

or

LLINEIN

AVDD

VMID

AGND

+

–

INTERNAL CIRCUITRY

To allow an external device to generate the central reference

clock, apply the external clock signal directly through the XTI/

CODEC_MCLK input pin. In this configuration, the oscillator

circuit of the codec can be powered down by using the OSCPD

bit (Register R6, Bit D5) to reduce power consumption.

To accommodate applications with very high frequency master

clocks, the internal core reference clock of the codec can be set

to either CODEC_MCLK or CODEC_MCLK divided by 2. This

is enabled by adjusting the setting of the CLKDIV2 bit (Register

R8, Bit D6). The CODEC_CLKOUT pin can also drive external

clock sources with either the codec clock signal or codec clock

divided by 2 by enabling the CLKODIV2 bit (Register R8,

Bit D7).

ADC AND DAC

The codec contains a pair of oversampling Σ-Δ ADCs. The

maximum ADC full-scale input level is 1.0 V

AVDD = 3.3 V. If the input signal to the ADC exceeds this

level, data overloading occurs and causes audible distortion.

The ADC can accept analog audio input from either the stereo

line inputs or the monaural microphone input. Note that the

ADC can only accept input from a single source, so the programmer must choose either the line inputs or the microphone

input using the INSEL bit (Register R4, Bit D2). The digital data

from the ADC output, once converted, is processed using the

ADC filters.

Complementary to the Σ-Δ ADC channels, the codec contains a

pair of oversampling DACs that convert the digital audio data

from the internal DAC filters into an analog audio signal. The

DAC output can also be muted by setting the DACMU bit (Register R5, Bit D3) in the control register.

rms

when

ANALOG AUDIO INTERFACES

The codec includes stereo single-ended line inputs and a monaural microphone input to the on-board ADC. Either the line

inputs or the microphone input, but not both simultaneously,

can be connected to the ADC by setting the INSEL bit (Register

R4, Bit D2).

The codec also includes line and headphone outputs from the

on-board DAC. The line or microphone inputs can be routed

and mixed directly to the output terminals.

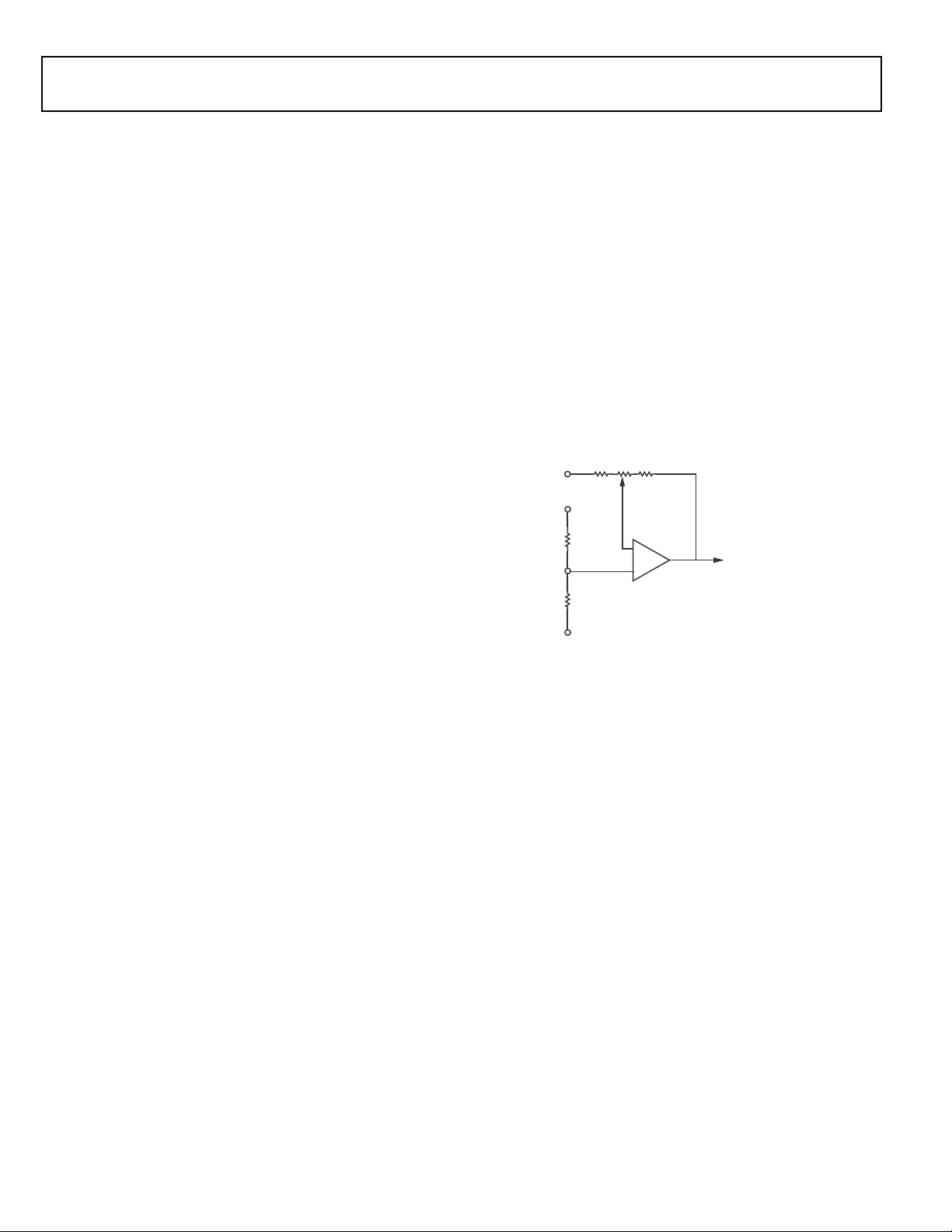

Stereo Line and Monaural Microphone Inputs

The single-ended stereo line inputs (RLINEIN and LLINEIN)

are internally biased to VMID by way of a voltage divider

between AVDD and AGND (see Figure 2). The line input signal

can be connected to the internal ADC and, if desired, routed

directly to the outputs via the bypass path by using the BYPASS

bit (Register R4, Bit D3).

Figure 2. Line Input to ADC

ADC HIGH-PASS AND DAC DE-EMPHASIS FILTERS

The ADC and DAC employ separate digital filters that perform

24-bit signal processing. The digital filters are used for both

record and playback modes and are optimized for each individual sampling rate used.

For recording mode operations, the unprocessed data from the

ADC enters the ADC filters and is converted to the appropriate

sampling frequency, then is output to the digital audio interface.

For playback mode operations, the DAC filters convert the digital audio interface data to oversampled data using a sampling

rate selected by the programmer. The oversampled data is processed by the DAC and sent to the analog output mixer by

enabling the DACSEL (Register R4, Bit D4).

Programmers have the option of setting up the device so that

any dc offset in the input source signal is automatically detected

and removed. To accomplish this, enable the digital high-pass

filter (see Table 22 on Page 30 for characteristics) contained in

the ADC digital filters by using the ADCHPD bit (Register R5,

Bit D0).

In addition, programmers can implement digital de-emphasis

by using the DEEMPH bits (Register R5, Bit D1 and Bit D2).

Rev. A | Page 4 of 36 | March 2010

The line input volume can be adjusted from –34.5 dB to +33 dB

in steps of +1.5 dB by setting the LINVOL (Register R0, Bit D0

to Bit D5) and RINVOL (Register R1, Bit D0 to Bit D5) bits. By

default the volume is independently adjustable for both right

and left line inputs. However, if the LRINBOTH or RLINBOTH

bit is programmed, both LINVOL and RINVOL are loaded with

the same value. The programmer can also set the LINMUTE

(Register R0, Bit D7) and RINMUTE (Register R1, Bit D7) bits

to mute the line input signal to the ADC.

The high impedance, low capacitance monaural microphone

input pin (MICIN, shown in Figure 3 ) has two gain stages and a

microphone bias level (MICBIAS) that is internally biased to the

VMID voltage level by way of a voltage divider between AVDD

and AGND. The microphone input signal can be connected to

the internal ADC and, if desired, routed directly to the outputs

via the sidetone path by using the SIDETONE bit (Register R4,

Bit D5).

Page 5

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

ADC

OR

SIDETONE

INTERNAL CIRCUITRY

MICIN

AVDD

VMID

AGND

R

EXT

10kΩ

50kΩ

0dB/20dB/40dB

GAIN BOOST

LINE OUTPUT

AND

HEADPHONE

OUTPUT

AVDD

VMID

AGND

BYPASS

SIDETONE

DACSEL

LINE

INPUT

MICROPHONE

INPUT

DAC

OUTPUT

INTERNAL CIRCUITRY

RHPOUT

or

LHPOUT

DAC/

SIDETONE/

BYPASS

AVDD

VMID

AGND

+

–

INTERNAL CIRCUITRY

selected level of attenuation occurs after the initial microphone

signal amplification from the microphone first and second stage

gains.

Line and Headphone Outputs

The DAC outputs, the microphone (the sidetone path), and the

line inputs (the bypass path) are summed at an output mixer

(see Figure 4). This output signal is then applied to both the stereo line outputs and stereo headphone outputs.

Figure 3. Microphone Input to ADC

The first gain stage is composed of a low noise operational

amplifier set to an inverting configuration with integrated

50 kΩ feedback and 10 kΩ input resistors. The default microphone input signal gain is 14 dB. An external resistor (R

be connected in series with the MICIN pin to reduce the firststage gain of the microphone input signal to as low as 0 dB by

using the following equation:

Microphone Input Gain = 50 kΩ/(10 kΩ + R

EXT

)

The second-stage gain of the microphone signal path is derived

from the internal microphone boost circuitry. The available settings are 0 dB, 20 dB, and 40 dB and are controlled by the

MICBOOST (Register R4, Bit D0) and MICBOOST2 (Register

R4, Bit D8) bits. To achieve 20 dB of secondary gain boost, the

programmer can select either MICBOOST or MICBOOST2. To

achieve 40 dB of secondary microphone signal gain, the programmer must select both MICBOOST and MICBOOST2.

The MUTEMIC bit (Register R4, Bit D1) mutes the microphone

input signal to the ADC.

When using either the line or microphone inputs, the maximum

full-scale input to the ADC is 1.0 V rms when AVDD = 3.3 V.

Do not apply an input voltage larger than full-scale to avoid

overloading the ADC, which causes distortion of sound and

deterioration of audio quality. For best sound quality in both

microphone and line inputs, gain should be carefully configured

so that the ADC receives a signal equal to its full-scale. This

maximizes the signal-to-noise ratio for best total audio quality.

EXT

) can

Figure 4. Output Signal Chain

The codec has a set of efficient headphone amplifier outputs,

LHPOUT and RHPOUT, that are able to drive 16 Ω or 32 Ω

headphones (shown in Figure 5).

Bypass and Sidetone Paths to Output

The line and microphone inputs can be routed and mixed

directly to the output terminals by programming the SIDETONE (Register R4, Bit D5) and BYPASS (Register R4, Bit D3)

registers. In both modes, the analog input signal is routed

directly to the output terminals and is not digitally converted.

The bypass signal at the output mixer is the same level as the

output of the PGA associated with each line input.

The sidetone signal at the output mixer can be attenuated from

–6 dB to –15 dB in steps of –3 dB by configuring the SIDEATT

(Register R4, Bit D6 and Bit D7) control register bits. The

Figure 5. Headphone Output

Like the line inputs, the LHPOUT and RHPOUT volumes, by

default, are independently adjusted by setting the LHPVOL

(Register R2, Bit D0 to Bit D6) and RHPVOL (Register R3, Bit

D0 to Bit D6) bits of the headphone output control registers.

The headphone outputs can be muted by writing codes less than

0110000 to the LHPVOL and RHPVOL bits.

Rev. A | Page 5 of 36 | March 2010

Page 6

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

1234 NXX XXN12

LEFT CHANNEL

3

RIGHT CHANNEL

1/

f

S

X = DON’T CARE.

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

LEFT CHANNEL RIGHT CHANNEL

1/

f

S

X = DON’T CARE.

XNX

32 1 XXN4 4321

The programmer can simultaneously load the volume control of

both channels by writing to the LRHPBOTH (Register R2, Bit

D8) and RLHPBOTH (Register R3, Bit D8) bits of the left- or

right-channel DAC volume registers.

The maximum output level of the headphone outputs is

1.0 V rms when AVDD and HPVDD = 3.3 V. To suppress audible pops and clicks, the headphone and line outputs are held at

the VMID dc voltage level when the device is set to standby

mode or when the headphone outputs are muted.

The stereo line outputs of the codec, the LOUT and ROUT pins,

can drive a load impedance of 10 kΩ and 50 pF. The line output

signal levels are not adjustable at the output mixer, which has a

fixed gain of 0 dB. The maximum output level of the line outputs is 1.0 V rms when AVDD = 3.3 V.

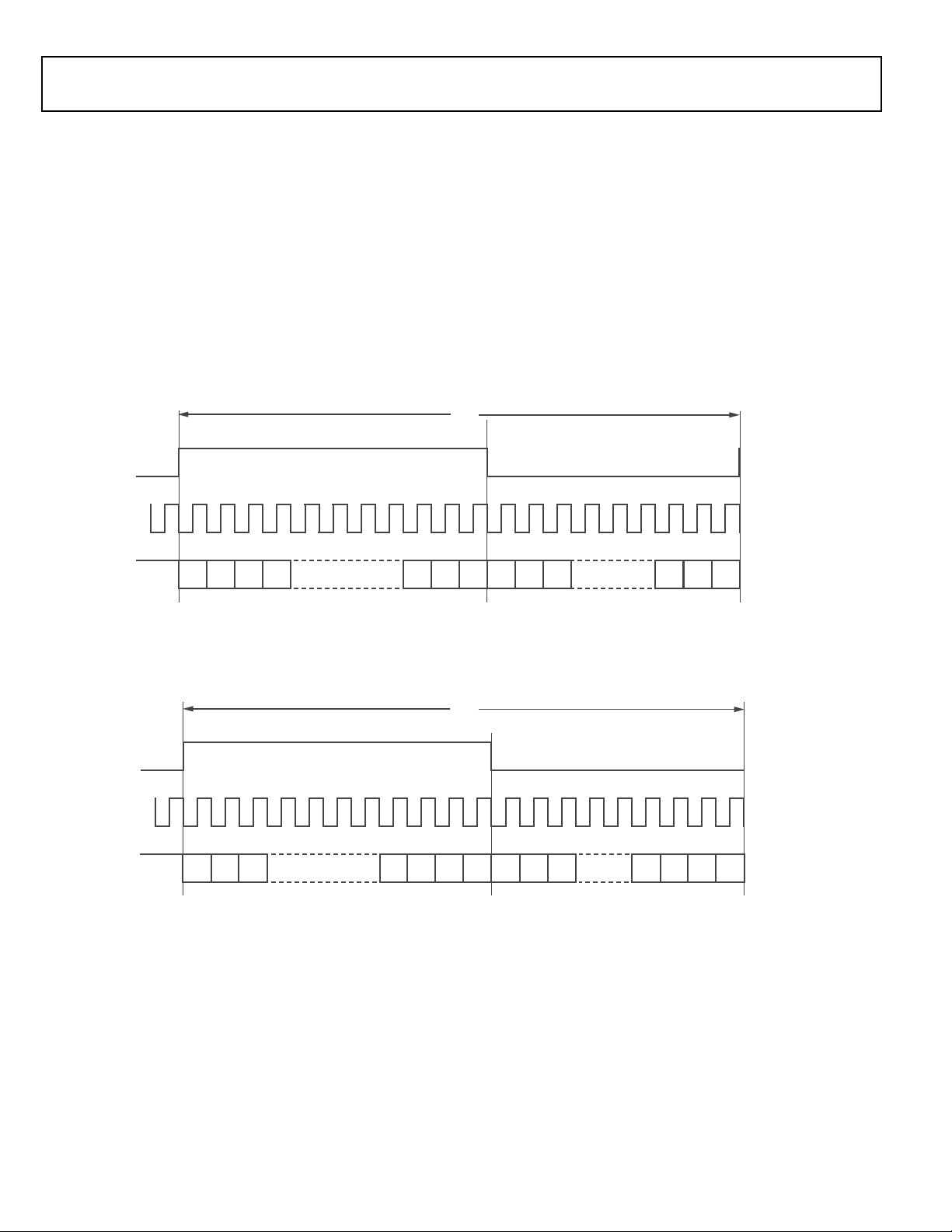

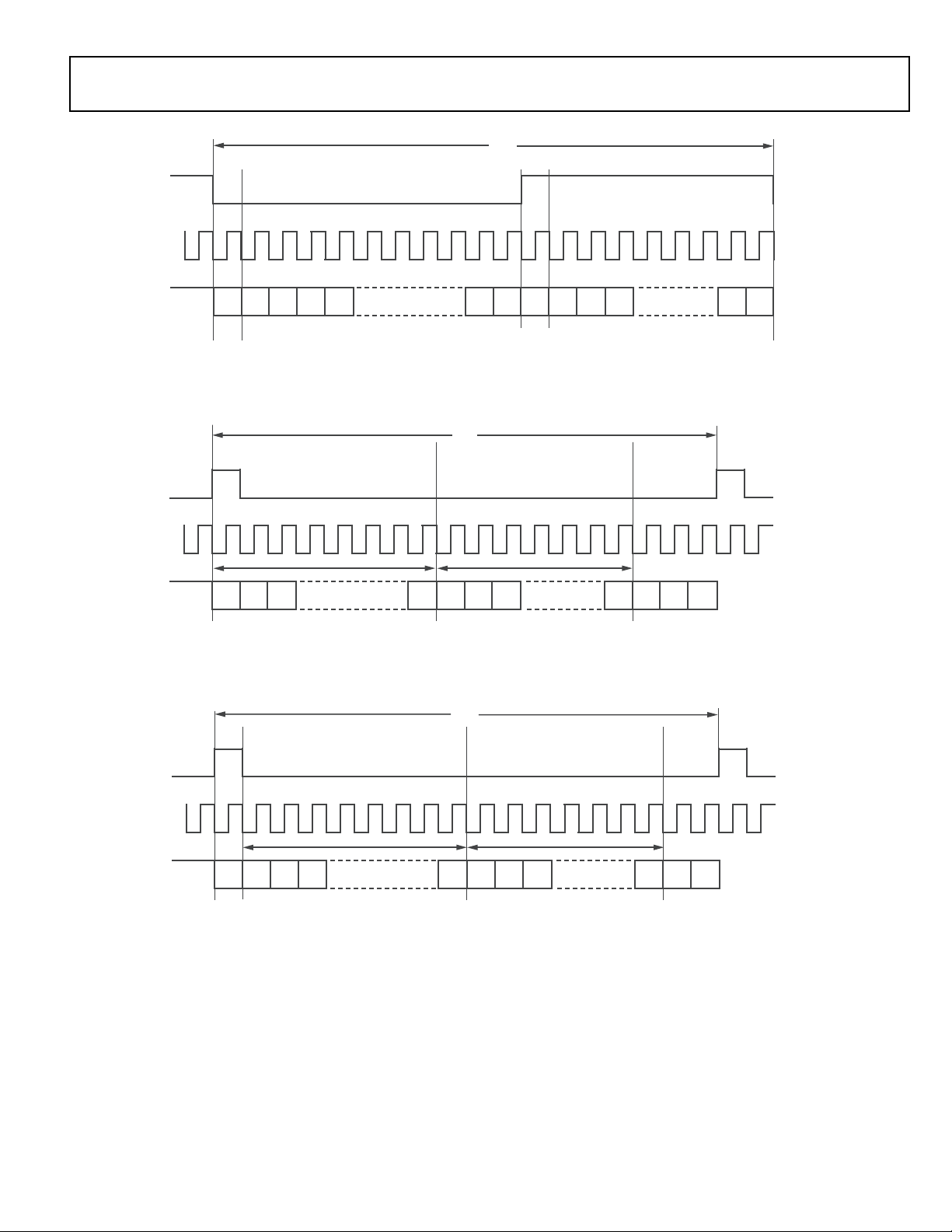

DIGITAL AUDIO INTERFACE

The digital audio input can support the following digital audio

communication protocols: right-justified mode, left-justified

2

mode, I

through Figure 10 on Page 7.

The mode selection is performed by writing to the FORMAT

bits of the digital audio interface register (Register R7, Bit D1

and Bit D0). All modes are MSB first and operate with data of 16

to 32 bits.

S mode, and frame sync mode. See Figure 6 on Page 6

Figure 6. Left-Justified Audio Input Mode

Figure 7. Right-Justified Audio Input Mode

Rev. A | Page 6 of 36 | March 2010

Page 7

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

1234X XN

LEFT CHANNEL RIGHT CHANNEL

1/

f

S

X = DON’T CARE.

NX123X

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

LEFT CHANNEL RIGHT CHANNEL

1/

f

S

X = DON’T CARE.

231

123N

XXXN

ADCLRC/

DACLRC

CODEC_BCLK

ADCDAT/

DACDAT

LEFT CHANNEL RIGHT CHANNEL

1/

f

S

X = DON’T CARE.

231X

123N

XXN

Figure 8. I2S Audio Input Mode

Figure 9. Frame Sync/PCM Mode Audio Input (Submode 1) [Bit LRP = 0]

Figure 10. Frame Sync/PCM Mode Audio Input (Submode 2) [Bit LRP = 1]

Rev. A | Page 7 of 36 | March 2010

Page 8

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Recording Mode

The digital audio interface sends the ADC digital filter data to

the ADCDAT output pin for recording. The ADCDAT data

stream multiplexes the left- and right-channel audio data in the

time domain. The ADCLRC clock signal separates left- and

right-channel digital audio frames on the ADCDAT lines.

The CODEC_BCLK signal clocks the digital audio data within

the frames. The CODEC_BCLK signal is either an input or an

output depending on whether the codec is in master or slave

mode. During a recording operation, ADCDAT and ADCLRC

must be synchronous to the CODEC_BCLK signal to avoid data

corruption.

Playback Mode

The digital audio interface receives data on the DACDAT input

pin for playback. The digital audio data stream on the DACDAT

pin is time-domain-multiplexed left and right channel audio

data. The DACLRC clock signal separates left and right channel

digital audio frames on the DACDAT lines.

The CODEC_BCLK signal clocks the digital audio data within

the frames. The CODEC_BCLK signal is either an input or an

output depending on whether the codec is in master or slave

mode. During a playback operation, DACDAT and DACLRC

must be synchronous to the CODEC_BCLK signal to avoid data

corruption.

Digital Audio Data Sampling Rate

To accommodate a wide variety of commonly used DAC and

ADC sampling rates, the codec allows for two modes of operation, normal and USB, selected by the USB bit (Register R8,

Bit D0).

The sampling rate is generated as a fixed divider from the

CODEC_MCLK signal. Because all audio processing references

the CODEC_MCLK signal, corruption of this signal w ill cor rupt

the quality of the audio at the codec output. The ADCLRC/

ADCDAT/CODEC_BCLK or DACLRC/DACDAT/

CODEC_BCLK signals must be synchronized with

CODEC_MCLK in the digital audio interface circuit.

CODEC_MCLK must be faster or equal to the CODEC_BCLK

frequency to guarantee that no data is lost during data synchronization. The CODEC_BCLK frequency should be greater than

the sampling rate × word length × 2. Ensuring that the

CODEC_BCLK frequency is greater than this, guarantees that

all valid data bits are captured by the digital audio interface circuitry. For example, if a 32 kHz digital audio sampling rate with

a 32-bit word length is desired, CODEC_BCLK = 2.048 MHz.

Rev. A | Page 8 of 36 | March 2010

Page 9

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

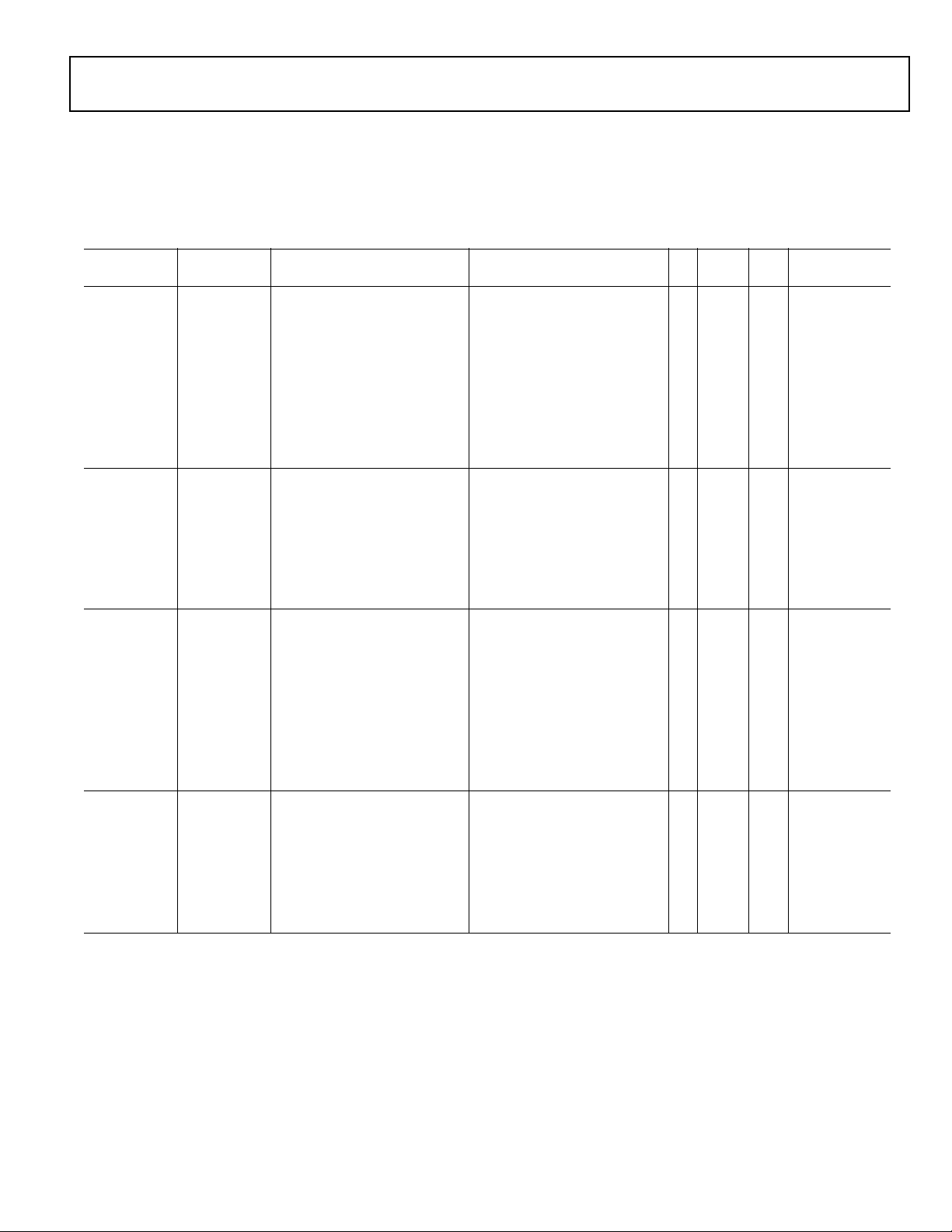

Normal Mode

In normal mode, the codec supports digital audio sampling

rates from 8 kHz to 96 kHz. Normal mode supports 256 × f

384 × f

based clocks. To select the desired sampling rate, the

S

and

S

programmer must set the appropriate sampling rate register in

Table 1. Sampling Rate Lookup Table, Normal Mode (USB Disabled)

the SR control bits (Register R8, Bit D2 to Bit D5) and match

this selection to the core clock frequency that is pulsed on the

CODEC_MCLK pin. See Table 1 for sampling rates in

normal mode.

CODEC_MCLK

(CLKDIV2 = 0)

CODEC_MCLK

(CLKDIV2 = 1)

ADC Sampling Rate

(ADCLRC)

DAC Sampling Rate

(DACLRC)

USB SR [3:0] BOSR CODEC_BCLK

(MS = 1)

1

12.288 MHz 24.576 MHz 8 kHz (CODEC_MCLK/1536) 8 kHz (CODEC_MCLK/1536) 0 0011 0 CODEC_MCLK/4

8 kHz (CODEC_MCLK/1536) 48 kHz (CODEC_MCLK/256) 0 0010 0 CODEC_MCLK/4

12 kHz (CODEC_MCLK/1024) 12 kHz (CODEC_MCLK/1024) 0 0100 0 CODEC_MCLK/4

16 kHz (CODEC_MCLK/768) 16 kHz (CODEC_MCLK/768) 0 0101 0 CODEC_MCLK/4

24 kHz (CODEC_MCLK/512) 24 kHz (CODEC_MCLK/512) 0 1110 0 CODEC_MCLK/4

32 kHz (CODEC_MCLK/384) 32 kHz (CODEC_MCLK/384) 0 0110 0 CODEC_MCLK/4

48 kHz (CODEC_MCLK/256) 8 kHz (CODEC_MCLK/1536) 0 0001 0 CODEC_MCLK/4

48 kHz (CODEC_MCLK/256) 48 kHz (CODEC_MCLK/256) 0 0000 0 CODEC_MCLK/4

96 kHz (CODEC_MCLK/128) 96 kHz (CODEC_MCLK/128) 0 0111 0 CODEC_MCLK/2

11.2896 MHz 22.5792 MHz 8.0182 kHz (CODEC_MCLK/1408) 8.0182 kHz (CODEC_MCLK/1408) 0 1011 0 CODEC_MCLK/4

8.0182 kHz (CODEC_MCLK/1408) 44.1 kHz (CODEC_MCLK/256) 0 1010 0 CODEC_MCLK/4

11.025 kHz (CODEC_MCLK/1024) 11.025 kHz (CODEC_MCLK/1024) 0 1100 0 CODEC_MCLK/4

22.05 kHz (CODEC_MCLK/512) 22.05 kHz (CODEC_MCLK/512) 0 1101 0 CODEC_MCLK/4

44.1 kHz (CODEC_MCLK/256) 8.0182 kHz (CODEC_MCLK/1408) 0 1001 0 CODEC_MCLK/4

44.1 kHz (CODEC_MCLK/256) 44.1 kHz (CODEC_MCLK/256) 0 1000 0 CODEC_MCLK/4

88.2 kHz (CODEC_MCLK/128) 88.2 kHz (CODEC_MCLK/128) 0 1111 0 CODEC_MCLK/2

18.432 MHz 36.864 MHz 8 kHz (CODEC_MCLK/2304) 8 kHz (CODEC_MCLK/2304) 0 0011 1 CODEC_MCLK/6

8 kHz (CODEC_MCLK/2304) 48 kHz (CODEC_MCLK/384) 0 0010 1 CODEC_MCLK/6

12 kHz (CODEC_MCLK/1536) 12 kHz (CODEC_MCLK/1536) 0 0100 1 CODEC_MCLK/6

16 kHz (CODEC_MCLK/1152) 16 kHz (CODEC_MCLK/1152) 0 0101 1 CODEC_MCLK/6

24 kHz (CODEC_MCLK/768) 24 kHz (CODEC_MCLK/768) 0 1110 1 CODEC_MCLK/6

32 kHz (CODEC_MCLK/576) 32 kHz (CODEC_MCLK/576) 0 0110 1 CODEC_MCLK/6

48 kHz (CODEC_MCLK/384) 48 kHz (CODEC_MCLK/384) 0 0000 1 CODEC_MCLK/6

48 kHz (CODEC_MCLK/384) 8 kHz (CODEC_MCLK/2304) 0 0001 1 CODEC_MCLK/6

96 kHz (CODEC_MCLK/192) 96 kHz (CODEC_MCLK/192) 0 0111 1 CODEC_MCLK/3

16.9344 MHz 33.8688 MHz 8.0182 kHz (CODEC_MCLK/2112) 8.0182 kHz (CODEC_MCLK/2112) 0 1011 1 CODEC_MCLK/6

8.0182 kHz (CODEC_MCLK/2112) 44.1 kHz (CODEC_MCLK/384) 0 1010 1 CODEC_MCLK/6

11.025 kHz (CODEC_MCLK/1536) 11.025 kHz (CODEC_MCLK/1536) 0 1100 1 CODEC_MCLK/6

22.05 kHz (CODEC_MCLK/768) 22.05 kHz (CODEC_MCLK/768) 0 1101 1 CODEC_MCLK/6

44.1 kHz (CODEC_MCLK/384) 8.0182 kHz (CODEC_MCLK/2112) 0 1001 1 CODEC_MCLK/6

44.1 kHz (CODEC_MCLK/384) 44.1 kHz (CODEC_MCLK/384) 0 1000 1 CODEC_MCLK/6

88.2 kHz (CODEC_MCLK/192) 88.2 kHz (CODEC_MCLK/192) 0 1111 1 CODEC_MCLK/3

1

CODEC_BCLK frequency is for master mode and slave right-justified mode only.

Rev. A | Page 9 of 36 | March 2010

Page 10

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

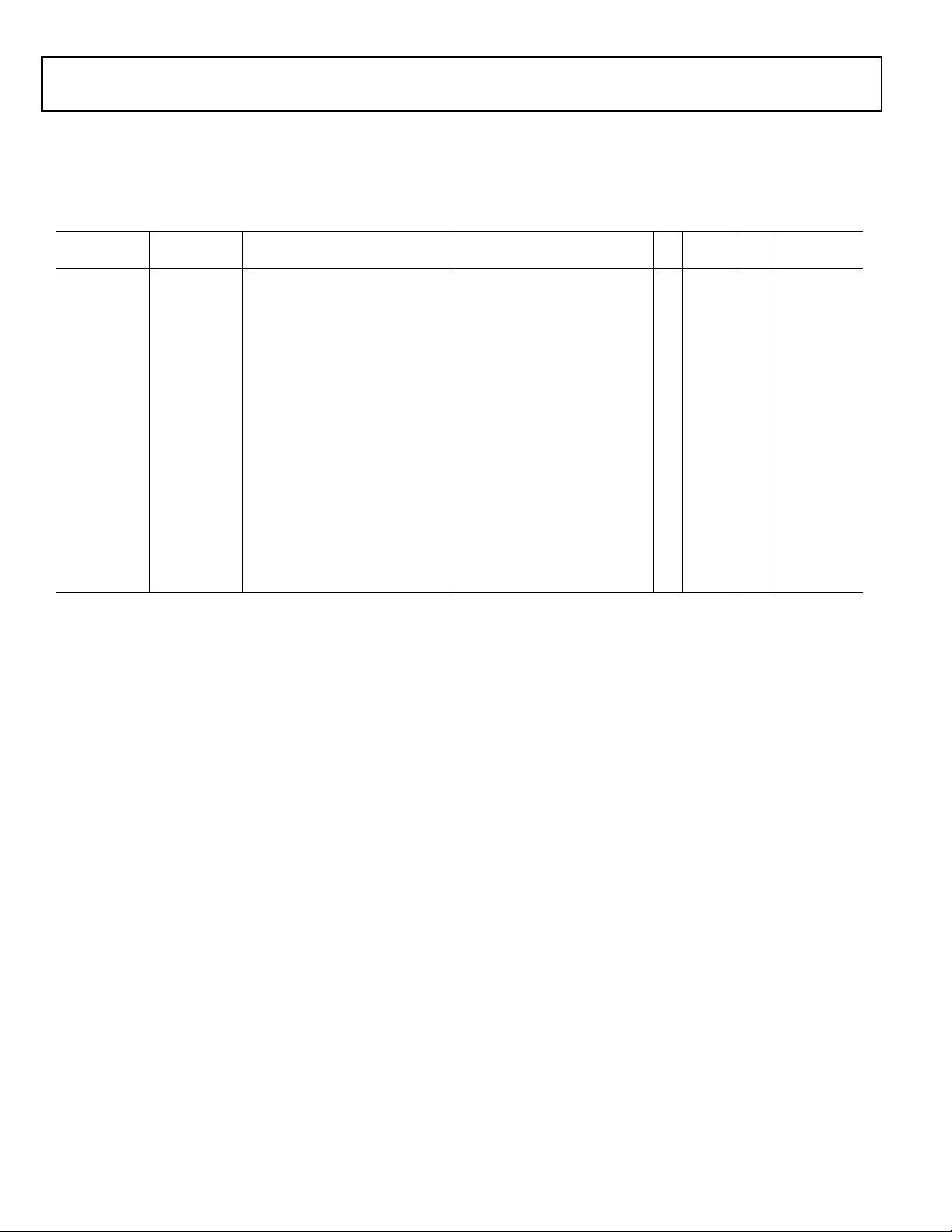

USB Mode

In USB mode, the codec supports digital audio sampling rates

from 8 kHz to 96 kHz. USB mode is enabled on the codec

to support the common universal serial bus (USB) clock rate of

12 MHz, or to support 24 MHz if the CLKDIV2 control register

bit is activated. The programmer must set the appropriate sampling rate in the SR control bits (Register R8, Bit D2 to Bit D5).

See Table 2 for sampling rates in USB mode.

Table 2. Sampling Rate Lookup Table, USB Mode (USB Enabled)

CODEC_MCLK

(CLKDIV2 = 0)

12.000 MHz 24.000 MHz 8 kHz (CODEC_MCLK/1500) 8 kHz (CODEC_MCLK/1500) 1 0011 0 CODEC_MCLK

1

CODEC_BCLK frequency is for master mode and slave right-justified mode only.

CODEC_MCLK

(CLKDIV2 = 1)

ADC Sampling Rate

(ADCLRC)

8 kHz (CODEC_MCLK/1500) 48 kHz (CODEC_MCLK/250) 1 0010 0 CODEC_MCLK

8.0214 kHz (CODEC_MCLK/1496) 8.0214 kHz (CODEC_MCLK/1496) 1 1011 1 CODEC_MCLK

8.0214 kHz (CODEC_MCLK/1496) 44.118 kHz (CODEC_MCLK/272) 1 1010 1 CODEC_MCLK

11.0259 kHz (CODEC_MCLK/1088) 11.0259 kHz (CODEC_MCLK/1088) 1 1100 1 CODEC_MCLK

12 kHz (CODEC_MCLK/1000) 12 kHz (CODEC_MCLK/1000) 1 1000 0 CODEC_MCLK

16 kHz (CODEC_MCLK/750) 16 kHz (CODEC_MCLK/750) 1 1010 0 CODEC_MCLK

22.0588 kHz (CODEC_MCLK/544) 22.0588 kHz (CODEC_MCLK/544) 1 1101 1 CODEC_MCLK

24 kHz (CODEC_MCLK/500) 24 kHz (CODEC_MCLK/500) 1 1110 0 CODEC_MCLK

32 kHz (CODEC_MCLK/375) 32 kHz (CODEC_MCLK/375) 1 0110 0 CODEC_MCLK

44.118 kHz (CODEC_MCLK/272) 8.0214 kHz (CODEC_MCLK/1496) 1 1001 1 CODEC_MCLK

44.118 kHz (CODEC_MCLK/272) 44.118 kHz (CODEC_MCLK/272) 1 1000 1 CODEC_MCLK

48 kHz (CODEC_MCLK/250) 8 kHz (CODEC_MCLK/1500) 1 0001 0 CODEC_MCLK

48 kHz (CODEC_MCLK/250) 48 kHz (CODEC_MCLK/250) 1 0000 0 CODEC_MCLK

88.235 kHz (CODEC_MCLK/136) 88.235 kHz (CODEC_MCLK/136) 1 1111 1 CODEC_MCLK

96 kHz (CODEC_MCLK/125) 96 kHz (CODEC_MCLK/125) 1 0111 0 CODEC_MCLK

DAC Sampling Rate

(DACLRC)

USB SR [3:0] BOSR CODEC_BCLK

(MS = 1)

1

Rev. A | Page 10 of 36 | March 2010

Page 11

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

B15

B14

CSB

CSCL

CSDA

B0B01B02B03B04B05B06B07B08B09B10B11B12B13

REGISTER MAP

ADDRESS

REGISTER

DATA

P981 – 7981 – 7981 – 7

S

CSDA

CSCL

START ADDR R/W ACK ACKSUBADDRESS ACK STOP

DATA

WRITE

SEQUENCE

READ

SEQUENCE

SA1A7 A0 A(S) A(S) SB15 B9 0

01

0P

0... A1A7 A0 A(S)... B0 B8B7 A(M) A(M)...

B0B7 P...

......

DEVICE

ADDRESS

DEVICE

ADDRESS

REGISTER

ADDRESS

SA1A7 A0 A(S) A(S) A(S)B15 B9 B8

0

... ...

DEVICE

ADDRESS

REGISTER

ADDRESS

REGISTER

DATA

(SLAVE DRIVE)

REGISTER

DATA

S/P = START/STOP BIT.

A0 = I

2

C R/W BIT.

A(S) = ACKNOWLEDGE BY SLAVE.

A(M) = ACKNOWLEDGE BY MASTER.

A(M) = ACKNOWLEDGE BY MASTER (INVERSION).

SOFTWARE CONTROL INTERFACE

The software control interface provides access to the

programmer-selectable control registers and can operate with a

2-wire (TWI) or 3-wire (SPI) interface, depending on the setting

of the CMODE pin. If the CMODE pin is set to 0, the 2-wire

interface is selected; if 1, the 3-wire interface is selected.

Within each control register is a control data-word consisting of

16 bits, MSB first. Bit B15 to Bit B9 are the register map address,

and Bit B8 to Bit B0 are register data for the associated register

map.

Figure 11. Codec SPI Serial Interface

When 2-wire (TWI) mode is selected, CSDA generates the serial

control data-word; CSCL clocks the serial data; and CSB determines the TWI device address. If the CSB pin is set to 0, the

address selected is 0011010; if 1, the address is 0011011.

When 3-wire (SPI) mode is selected, CSDA generates the control data-word, CSCL clocks the control data-word into the

codec, and CSB latches in the control data-word.

Figure 12. Codec TWI Serial Interface

Figure 13. Codec TWI Write and Read Sequences

Rev. A | Page 11 of 36 | March 2010

Page 12

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

CODEC PIN DESCRIPTIONS

Table 3 shows the signals added to the ADSP-BF52xC processor

for the embedded codec. Please refer to the published

ADSP-BF52x data sheet for descriptions of other signals for the

processor.

Table 3. Codec Pin Descriptions

Pin Name Type Function Pull-Up/Down

Codec

CODEC_CLKOUT O Codec Clock Output None

CODEC_BCLK I/O Codec Digital Audio Bit Clock Internal Pull-down

DACDAT I Codec Digital Audio Data (DAC) Input None

DACLRC I/O Codec DAC Sample Rate Left/Right Clock Internal Pull-down

ADCDAT O Codec ADC Digital Audio Data Output None

ADCLRC I/O Codec ADC Sample Rate Left/Right Clock Internal Pull-down

CMODE I Codec Control Interface Selection Internal Pull-up

CSB I Codec Chip Select Interface Address Selection Internal Pull-up

CSDA I/O Codec Data Input None

CSCL I/O Codec Data Clock None

XTI/CODEC_MCLK I Codec Crystal Input/ Clock Input None

XTO O Codec Crystal Output None

LHPOUT O Codec Left Channel Headphone Output (Analog Output) None

RHPOUT O Codec Right Channel Headphone Output (Analog Output) None

LOUT O Codec Left Channel Line Output (Analog Output) None

ROUT O Codec Right Channel Line Output (Analog Output) None

VMID O Codec Mid-rail Reference Decoupling Point (Analog Output) None

MICBIAS O Codec Electret Microphone Bias (Analog Output) None

MICIN I Codec Microphone Input; (Analog Input, AC Coupled) None

RLINEIN I Codec Right Channel Line Input (Analog Input, AC Coupled) None

LLINEIN I Codec Left Channel Line Input (Analog Input, AC Coupled) None

AVDD P Codec Analog V

DD

AGND P Codec Analog Ground N/A

CVDD P Codec Digital V

HPVDD P Codec Analog Headphone V

DD

DD

HPGND P Codec Headphone Ground N/A

1

To conserve power, the pull-up/pull-down is only present when the control register interface is active (= 0).

N/A

N/A

N/A

1

1

1

1

1

Rev. A | Page 12 of 36 | March 2010

Page 13

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

10 K

AVDD

SPI

ADSP-BF52XC

CODEC

RHPOUT

VMID

CODEC_CLKOUT

LOUT

+

LHPOUT

+

AVDD

AGND

AVDD

ROUT

+

+

+

RLINEIN

MICBIAS

DACLRC

DACDAT

ADCLRC

ADCDAT

LLINEIN

MICIN

R

MIC

CODEC_BCLK

TFSx

DTxPRI

RFSx

DRxPRI

RSCLKx

+

10 F

10 F

1 F

1 F

220 F

220 F

0.1 F

0.1 F

47 K

47 K

47 K

47 K

100

100

100

XTO

XTI/CODEC_MCLK

X

1

C

P

C

P

680

47 K

+

HPVDD

HPGND

HPVDD

10 F

0.1 F

+

CSDA

CSB

CSCL

CMODE

BLACKFIN

PROCESSOR

SDA

SCL

SPISELx

MOSI

SCK

+

1 F

100

K

10

M

220 pF

+

1 F

100

K

10

M

220 pF

Figure 14 on Page 13 and Figure 15 on Page 14 describe alterna-

tive external connections for SPI or TWI control of the

ADSP-BF52xC codec. The figures are the same except for the

shaded area in each.

Figure 14. Recommended Application Circuit Using SPI Control

Rev. A | Page 13 of 36 | March 2010

Page 14

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

10 K

10 K

AVDD

AVDD

TWI

RR

SEE VERSION 2.1 OF

THE I2C SPECIFICATION

FOR THE PROPER

RESISTOR VALUE.

ADSP-BF52XC

CODEC

RHPOUT

VMID

CODEC_CLKOUT

LOUT

+

LHPOUT

+

AVDD

AGND

AVDD

ROUT

+

+

+

RLINEIN

MICBIAS

DACLRC

DACDAT

ADCLRC

ADCDAT

LLINEIN

MICIN

R

MIC

CODEC_BCLK

TFSx

DTxPRI

RFSx

DRxPRI

RSCLKx

+

10 F

10 F

1 F

1 F

220 F

220 F

0.1 F

0.1 F

47 K

47 K

47 K

47 K

100

100

100

XTO

XTI/CODEC_MCLK

X

1

C

P

C

P

680

47 K

+

1 F

100

K

10

M

220 pF

+

HPVDD

HPGND

HPVDD

10 F

0.1 F

+

CSDA

CSB

CSCL

CMODE

BLACKFIN

PROCESSOR

SDA

SCL

SPISELx

MOSI

SCK

+

1 F

100

K

10

M

220 pF

Figure 15. Recommended Application Circuit Using TWI Control

Rev. A | Page 14 of 36 | March 2010

Page 15

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

REGISTER DETAILS

Register Address B8 B7 B6 B5 B4 B3 B2 B1 B0

Register 0 Left-Channel ADC

Input Volume on Page 16

Register 1 Right-Channel ADC

Input Volume on Page 17

Register 2 Left-Channel DAC

Volume on Page 17

Register 3 Right-Channel DAC

Volume on Page 18

Register 4 Analog Audio Path

on Page 18

Register 5 Digital Audio Path

on Page 19

Register 6 Power Management

on Page 19

Register 7 Digital Audio I/F on

Page 20

Register 8 Sampling Rate on

Page 20

Register 9 Active on Page 20 0x09 0 0 0 0 0 0 0 0 ACTIVE

Register 10 Software Reset on

Page 20

0x00 LRINBOTH LINMUTE 0 LINVOL

Default = 010010111

0x01 RLINBOTH RINMUTE 0 RINVOL

Default = 010010111

0x02 LRHPBOTH LZCEN LHPVOL

Default = 001111001

0x03 RLHPBOTH RZCEN RHPVOL

Default = 001111001

0x04 MICBOOST2 SIDEATT[1:0] SIDETONE DACSEL BYPASS INSEL MUTEMIC MICBOOST

Default = 000001010

0x05 0 0 0 0 HPOR DACMU DEEMPH[1:0] ADC HPD

Default = 000001000

0x06 0 POWEROFF CLKOUTPD OSCPD OUTPD DACPD ADCPD MICPD LINEINPD

Default = 010011111

0x07 0 BCLKINV MS LRSWAP LRP WL[1:0] FORMAT[1:0]

Default = 000001010

0x08 0 CLKODIV2 CLKDIV2 SR[3:0] BOSR USB

Default = 000000000

Default = 000000000

0x0F RESET

Default = 000000000

Figure 16. Register Mapping

Rev. A | Page 15 of 36 | March 2010

Page 16

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

BIT DESCRIPTIONS

Table 4 through Table 14 on Page 20 describe each bit in the

control registers.

Table 4. Register 0 Left-Channel ADC Input Volume

Bit Name Bits Description Settings

LRINBOTH B8 Left-to-right line input ADC

data load control

LINMUTE B7 Left-channel input mute 0 = disable mute

LINVOL B[5:0] Left-channel PGA volume control 00 0000 = –34.5 dB

0 = disable simultaneous loading of left-channel

ADC data to right-channel register (default)

1 = enable simultaneous loading of left-channel

ADC data to right-channel register

1 = enable mute on data path to ADC (default)

… 1.5 dB step up

01 0111 = 0 dB (default)

… 1.5 dB step up

01 1111 = 12 dB

10 0000 = 13.5 dB

10 0001 = 15 dB

10 0010 = 16.5 dB

10 0011 = 18 dB

10 0100 = 19.5 dB

10 0101 = 21 dB

10 0110 = 22.5 dB

10 0111 = 24 dB

10 1000 = 25.5 dB

10 1001 = 27 dB

10 1010 = 28.5 dB

10 1011 = 30 dB

10 1100 = 31.5 dB

10 1101 = 33 dB

11 1111 to 10 1101 = 33 dB

Rev. A | Page 16 of 36 | March 2010

Page 17

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Table 5. Register 1 Right-Channel ADC Input Volume

Bit Name Bits Description Settings

RLINBOTH B8 Right-to-left line input ADC

data load control

RINMUTE B7 Right-channel input mute 0 = disable mute

RINVOL B[5:0] Right-channel PGA volume control 00 0000 = –34.5 dB

0 = disable simultaneous loading of right-channel

ADC data to left-channel register (default)

1 = enable simultaneous loading of right-channel

ADC data to left-channel register

1 = enable mute on data path to ADC (default)

… 1.5 dB step up

01 0111 = 0 dB (default)

… 1.5 dB step up

01 1111 = 12 dB

10 0000 = 13.5 dB

10 0001 = 15 dB

10 0010 = 16.5 dB

10 0011 = 18 dB

10 0100 = 19.5 dB

10 0101 = 21 dB

10 0110 = 22.5 dB

10 0111 = 24 dB

10 1000 = 25.5 dB

10 1001 = 27 dB

10 1010 = 28.5 dB

10 1011 = 30 dB

10 1100 = 31.5 dB

10 1101 = 33 dB

11 1111 to 10 1101 = 33 dB

Table 6. Register 2 Left-Channel DAC Volume

Bit Name Bits Description Settings

LRHPBOTH B8 Left-to-right headphone volume

load control

LZCEN B7 Left-channel zero cross detect enable 0 = disable (default)

LHPVOL B[6:0] Left-channel headphone volume control 000 0000 to 010 1111 = mute

Rev. A | Page 17 of 36 | March 2010

0 = disable simultaneous loading of left-channel

headphone volume data to right-channel register (default)

1 = enable simultaneous loading of left-channel

headphone volume data to right-channel register

1 = enable

011 0000 = –73 dB

…

111 1001 = 0 dB (default)

… 1 dB steps up to

111 1111 = +6 dB

Page 18

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Table 7. Register 3 Right-Channel DAC Volume

Bit Name Bits Description Settings

RLHPBOTH B8 Right-to-left headphone volume load control 0 = disable simultaneous loading of right-channel

headphone volume data to left-channel register (default)

1 = enable simultaneous loading of right-channel

headphone volume data to left-channel register

RZCEN B7 Right-channel zero cross detect enable 0 = disable (default)

1 = enable

RHPVOL [6:0] B[6:0] Right-channel headphone volume control 000 0000 to 010 1111 = mute

011 0000 = –73 dB

…

111 1001 = 0 dB (default)

… 1 dB steps up to

111 1111 = +6 dB

Table 8. Register 4 Analog Audio Path

Bit Name Bits Description Settings

MICBOOST2 B8 Additional microphone amplifier gain booster control 0 = 0 dB (default)

1 = 20 dB

SIDEATT[1:0] B[7:6] Microphone sidetone gain control 00 = –6 dB (default)

01 = –9 dB

10 = –12 dB

11 = –15 dB

SIDETONE B5 Sidetone enable. Allow attenuated microphone

signal to be mixed at device output terminal

0 = sidetone disable (default)

1 = sidetone enable

DACSEL B4 DAC select—allow DAC output to be

mixed at device output terminal

BYPASS B3 Bypass select—allow line input signal to be mixed

at device output terminal

INSEL B2 Line input or microphone input select to ADC 0 = line input select to ADC (default)

MUTEMIC B1 Microphone mute control to ADC 0 = mute on data path to ADC disable

MICBOOST B0 Primary microphone amplifier gain booster control 0 = 0 dB (default)

0 = do not select DAC (default)

1 = select DAC

0 = bypass disable

1 = bypass enable (default)

1 = microphone input select to ADC

1 = mute on data path to ADC enable (default)

1 = 20 dB

Rev. A | Page 18 of 36 | March 2010

Page 19

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Table 9. Register 5 Digital Audio Path

Bit Name Bits Description Settings

HPOR B4 Store dc offset when high-pass filter is disabled 0 = clear offset (default)

1 = store offset

DACMU B3 DAC digital mute 0 = no mute (signal active)

1 = mute (default)

DEEMPH[1:0] B[2:1] De-emphasis control 00 = no de-emphasis (default)

01 = 32 kHz sampling rate

10 = 44.1 kHz sampling rate

11 = 48 kHz sampling rate

ADCHPD B0 ADC high-pass filter control 0 = ADC high-pass filter enable (default)

1 = ADC high-pass filter disable

Table 10. Register 6 Power Management

Bit Name Bits Description Settings

POWEROFF B7 Whole chip power-down control 0 = power-up

1 = power-down (default)

CLKOUTPD B6 Clock output power-down control 0 = power-up (default)

1 = power-down

OSCPD B5 Crystal power-down control 0 = power-up (default)

1 = power-down

OUTPD B4 Output power-down control 0 = power-up

1 = power-down (default)

DACPD B3 DAC power-down control 0 = power-up

1 = power-down (default)

ADCPD B2 ADC power-down control 0 = power-up

1 = power-down (default)

MICPD B1 Microphone input power-down control 0 = power-up

1 = power-down (default)

LINEINPD B0 Line input power-down control 0 = power-up

1 = power-down (default)

Rev. A | Page 19 of 36 | March 2010

Page 20

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Table 11. Register 7 Digital Audio I/F

Bit Name Bits Description Settings

BCLKINV B7 CODEC_BCLK inversion control 0 = CODEC_BCLK not inverted (default)

1 = CODEC_BCLK inverted

MS B6 Master mode enable 0 = enable slave mode (default)

1 = enable master mode

LRSWAP B5 Swap DAC data control 0 = output left- and right-channel data as normal (default)

1 = swap left- and right-channel DAC data in audio interface

LRP B4 Polarity control for clocks in right-justified,

left-justified, and I

2

S modes

WL [1:0] B[3:2] Data-word length control 00 = 16 bits

FORMAT [1:0] B[1:0] Digital audio input format control 00 = right justified

0 = normal DACLRC and ADCLRC (default),

or processor Submode 1

1 = invert DACLRC and ADCLRC polarity, or processor Submode 2

01 = 20 bits

10 = 24 bits (default)

11 = 32 bits

01 = left justified

2

S mode (default)

10 = I

11 = processor mode

Table 12. Register 8 Sampling Rate

Bit Name Bits Description Settings

CLKODIV2 B7 CODEC_CLKOUT divider select 0 = CODEC_CLKOUT is codec clock (default)

1 = CODEC_CLKOUT is codec clock divided by 2

CLKDIV2 B6 Codec clock divide select 0 = codec clock is CODEC_MCLK (default)

1= codec clock is CODEC_MCLK divided by 2

SR [3:0] B[5:2] Clock setting condition See Table 1 on Page 9 and Table 2 on Page 10

BOSR B1 Base oversampling rate USB mode:

0 = support for 250 × f

1 = support for 272 × f

based clock (default)

S

based clock

S

Normal mode:

0 = support for 256 × f

1 = support for 384 × f

based clock (default)

S

based clock

S

USB B0 USB mode select 0 = normal mode enable (default)

1 = USB mode enable

Table 13. Register 9 Active

Bit Name Bit Description Settings

ACTIVE B0 Digital core activation control 0 = disable digital core (default)

1 = activate digital core

Table 14. Register 10 Software Reset

Bit Name Bit Description Settings

RESET [8:0] B[8:0] Write all 0s to this register to set all registers to their default settings.

0 = reset (default)

Other data written to this register has no effect.

Rev. A | Page 20 of 36 | March 2010

Page 21

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

SPECIFICATIONS

T

= 25°C, AVDD = VDDEXT = 3.3 V, HPVDD = 3.3 V,

Ambient

1 kHz signal, f

unless otherwise noted.

OPERATING CONDITIONS

See operating conditions in the published ADSP-BF52xC

data sheet.

Parameter Conditions Min Typical Max Unit

AVD D

HPVDD 1.8 3.3 3.6 V

1

Note that AVDD must equal HPVDD.

CODEC ELECTRICAL CHARACTERISTICS

Parameter Conditions Min Typical Max Unit

Line Input

Input Signal Level (0 dB) AVDD/3.3 V(rms)

Input Impedance PGA gain = 0 dB 200 kΩ

Input Capacitance 10 pF

Signal-to-Noise Ratio (A-Weighted) PGA gain = 0 dB, AVDD = 3.3 V 82 87 dB

Total Harmonic Distortion (THD) –1 dBFS input, AVDD = 3.3 V –80 –84 dB

Channel Separation

Programmable Gain –34.5 0 +33.5 dB

Gain Step 1.5 dB

Mute Attenuation –80 dB

Microphone Input

Input Signal Level 1V(rms)

Signal-to-Noise Ratio (A-Weighted) Microphone gain = 0 dB (R

Total Harmonic Distortion –1 dBFS input, 0 dB gain, AVDD = 3.3 V –75 dB

Power Supply Rejection Ratio 50 dB

Mute Attenuation 80 dB

Input Resistance 10 kΩ

Input Capacitance 10 pF

Microphone Bias

Bias Voltage 0.75 × AVDD V

Bias Current Source 3mA

Noise in the Signal Bandwidth 20 Hz to 20 kHz 40 nV/√Hz

= 48 kHz, PGA gain = 0 dB, 24-bit audio data,

S

1

PGA gain = +33 dB 10 kΩ

PGA gain = –34.5 dB 480 kΩ

PGA gain = 0 dB, AVDD = 1.8 V 84 dB

–1 dBFS input, AVDD = 1.8 V –71 –60 dB

1

–1 dBFS input, 0 dB gain, AVDD = 1.8 V –65 dB

1.8 3.3 3.6 V

80 dB

= 40 kΩ)85dB

SOURCE

Rev. A | Page 21 of 36 | March 2010

Page 22

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Parameter Conditions Min Typical Max Unit

Line Output

DAC –1 dBFS input DAC + line output

Full-Scale Output AVDD/3.3 V(rms)

Signal-to-Noise Ratio (A-Weighted) AVDD = 3.3 V 90 95 dB

AVDD = 1.8 V 85 88 dB

THD + N AVDD = 3.3 V –80 –70 dB

AVDD = 1.8 V –80 –70 dB

Power Supply Rejection Ratio 50 dB

Channel Separation 80 dB

Headphone Output

Full-Scale Output Voltage AVDD/3.3 V(rms)

Maximum Output Power R

Signal-to-Noise Ratio (A-Weighted) AVDD = 3.3 V 90 94 dB

THD + N HPOUT = 10 mW –65 dB

Power Supply Rejection Ratio 50 dB

Mute Attenuation 80 dB

LIne Input To Line Output

Full-Scale Output Voltage AVDD/3.3 V(rms)

Signal-to-Noise Ratio (A-Weighted) AVDD = 3.3 V 92 dB

Total Harmonic Distortion AVDD = 3.3 V –80 dB

Power Supply Rejection 50 dB

Microphone Input To Headphone Output

Full-Scale Output Voltage AVDD/3.3 V(rms)

Signal-to-Noise Ratio (A-Weighted) AVDD = 3.3 V 94 dB

Power Supply Rejection Ratio 50 dB

Programmable Attenuation 6 15 dB

Gain Step 3dB

Mute Attenuation 80 dB

1

Guaranteed but not tested.

= 32 Ω 30 mW

L

= 16 Ω 60 mW

R

L

AVDD = 1.8 V 80 85 dB

HPOUT = 20 mW –60 dB

AVDD = 1.8 V 86 dB

AVDD = 1.8 V –80 dB

AVDD = 1.8 V 88 dB

Rev. A | Page 22 of 36 | March 2010

Page 23

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

n.nvvvvvv.x

tppZccc

B

ADSP-BF 527KBCZ 6C2X

a

yyww country_of_origin

ABSOLUTE MAXIMUM RATINGS

See absolute maximum ratings in the published ADSP-BF52x

processor data sheet.

ESD SENSITIVITY

ESD (electrostatic discharge) sensitive device.

Charged devices and circuit boards can discharge

without detection. Although this product features

patented or proprietary protection circuitry, damage

may occur on devices subjected to high energy ESD.

Therefore, proper ESD precautions should be taken to

avoid performance degradation or loss of functionality.

PACKAGE INFORMATION

The information presented in Figure 17 and Table 15 provides

details about the package branding for the ADSP-BF52xC processor. For a complete listing of product availability, see

Ordering Guide on Page 36.

Figure 17. Product Information on Package

Table 15. Package Brand Information

Brand Key Field Description

t Temperature Range

pp Package Type

Z Lead Free Option

ccc See Ordering Guide

vvvvvv.x Assembly Lot Code

n.n Silicon Revision

yyww Date Code

Rev. A | Page 23 of 36 | March 2010

Page 24

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

POWER CONSUMPTION

These current consumption values are for the codec alone.

Please refer to the published ADSP-BF52x processor data sheet

for the additional current consumption of the Blackfin

processor.

Table 16. Power Consumption

Mode

(1.8V) (3.3V)

1

POWEROFF

CLKOUTPD

OSCPD

OUTPD

DACPD

ADCPD

MICPD

LINEINPD

AVDD HPVDD V

AVDD HPVDD V

DDEXT

Record and Playback 00000000 7.4 1.5 6.3 14.8 2.0 12.0 mA

Playback Only

Oscillator Enabled 00000111 3.1 1.30 3.0 4.7 2.0 6.1 mA

External Clock 01100111 2.9 1.2 3.0 4.7 2.0 6.1 mA

Record Only

Line Oscillator 00011010 2.4 N/A 3.7 4.3 N/A 7.4 mA

Line Clock 00111010 2.5 N/A 3.8 4.3 N/A 7.4 mA

Microphone 1 00011001 3.6 N/A 1.9 9.4 N/A 3.6 mA

Microphone 2 00111001 3.6 N/A 1.8 9.4 N/A 3.6 mA

Sidetone

(Microphone-to-Headphone Output)

Internally Generated Clock 00001101 2.3 1.0 2.0 7.9 2.0 4.0 mA

External Clock 00101101 2.3 1.0 2.0 7.9 2.0 4.0 mA

Analog Bypass

(Line Input or Line Output)

Internally Generated Line 00001110 0.9 1.0 2.0 1.8 2.0 4.0 mA

External Line 00101110 0.9 1.0 2.0 1.8 2.0 4.0 mA

Power-Down

Clock Stopped 11111111 3.1 6.3 3.8 9.4 6.3 12.3 μA

1

V

here refers to the total of the codec's DCVDD and DBVDD signals and does not include VDDExt supplies in the Blackfin device.

DDEXT

DDEXT

1

Unit

Rev. A | Page 24 of 36 | March 2010

Page 25

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

CSCL

CSDA

t

RT

t

SCH

t

PL

t

DS

t

PH

t

DH

t

FT

t

SCS

t

HCS

TIMING SPECIFICATIONS

TWI Timing

Table 17. TWI Timing

Parameter Test Conditions

t

SCS

t

SCH

t

PH

t

PL

f

SCL

t

DS

t

DH

t

RT

t

FT

t

HCS

1

AVDD, HPVDD, V

Start condition setup time 600 ns

Start condition hold time 600 ns

CSCL pulse width high 600 ns

CSCL pulse width low 1.3 μs

CSCL frequency 0526kHz

Data setup time 100 ns

Data hold time 900 ns

CSDA and CSCL rise time 300 ns

CSDA and CSCL fall time 300 ns

Stop condition setup time 600 ns

= 3.3 V, AGND = 0 V, TA = +25°C, Slave Mode, fS = 48 kHz, XTI/CODEC_MCLK = 256 × fS unless otherwise stated.

DDEXT

1

Min Max Unit

Figure 18. TWI Timing

Rev. A | Page 25 of 36 | March 2010

Page 26

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

CSB

CSCL

CSDA

t

CSL

t

CSH

t

DHO

t

CSS

t

DSU

t

SCS

t

SCL

t

SCH

SPI Timing

Table 18. SPI Timing

Parameter Test Conditions1Min Max Unit

CSDA to CSCL setup time 20 ns

t

DSU

t

DHO

t

SCH

t

SCL

t

SCS

t

CSS

t

CSH

t

CSL

t

PS

1

AVDD, HPVDD, V

CSCL to CSDA hold time 20 ns

CSCL pulse width high 20 ns

CSCL pulse width low 20 ns

CSCL rising edge to CSB rising edge 60 ns

CSB rising to CSCL rising 20 ns

CSB pulse width high 20 ns

CSB pulse width low 20 ns

Pulse width of spikes to be suppressed 0 5 ns

= 3.3 V, AGND = 0 V, TA = +25°C, Slave Mode, fS = 48 kHz, XTI/CODEC_MCLK = 256 × fS unless otherwise stated.

DDEXT

Figure 19. SPI Timing

Rev. A | Page 26 of 36 | March 2010

Page 27

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

CODEC_BCLK

DACLRC/

ADCLRC

DACDAT

ADCDAT

t

BCL

t

DS

t

LRSU

t

LRH

t

BCH

t

BCY

t

DD

t

DH

Digital Audio Interface Slave Mode Timing

Table 19. Digital Audio Interface Slave Mode Timing

Parameter Test Conditions1Min Max Unit

t

DS

t

DH

t

LRSU

t

LRH

t

DD

t

BCH

t

BCL

t

BCY

1

AVDD, HPVDD, V

DACDAT setup time from CODEC_BCLK rising edge 10 ns

DACDAT hold time from CODEC_BCLK rising edge 10 ns

ADCLRC/DACLRC setup time to CODEC_BCLK rising edge 10 ns

ADCLRC/DACLRC hold time to CODEC_BCLK rising edge 10 ns

ADCDAT propagation delay from CODEC_BCLK falling edge (external load of 70 pF) 30 ns

CODEC_BCLK pulse width high 25 ns

CODEC_BCLK pulse width low 25 ns

CODEC_BCLK cycle time 50 ns

= 3.3 V, AGND = 0 V, TA = +25°C, Slave Mode, fS = 48 kHz, XTI/CODEC_MCLK = 256 × fS unless otherwise stated.

DDEXT

Figure 20. Digital Audio Interface Slave Mode Timing

Rev. A | Page 27 of 36 | March 2010

Page 28

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

CODEC_BCLK

DACLRC/

ADCLRC

DACDAT

ADCDAT

t

DDA

t

DST

t

DHT

t

DL

Digital Audio Interface Master Mode Timing

Table 20. Digital Audio Interface Master Mode Timing

Parameter Test Conditions1Min Max Unit

t

DST

t

DHT

t

DL

t

DDA

t

BCLKR

t

BCLKF

t

BCLKDS

1

AVDD, HPVDD, V

DACDAT setup time to CODEC_BCLK rising edge 30 ns

DACDAT hold time to CODEC_BCLK rising edge 10 ns

ADCLRC/DACLRC propagation delay from CODEC_BCLK falling edge 10 ns

ADCDAT propagation delay from CODEC_BCLK falling edge 10 ns

CODEC_BCLK rising time (10 pF load) 10 ns

CODEC_BCLK falling time (10 pF load) 10 ns

CODEC_BCLK duty cycle (normal and USB mode) 45:55 55:45

= 3.3 V, AGND = 0 V, TA = +25°C, Slave Mode, fS = 48 kHz, XTI/CODEC_MCLK = 256 × fS unless otherwise stated.

DDEXT

Figure 21. Digital Audio Interface Master Mode Timing

Rev. A | Page 28 of 36 | March 2010

Page 29

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

t

COPDIV2

t

COP

CODE C_MCLK/ XT I

CODE C_CLKO UT

CODE C_CLKO UT/ 2

t

XTIH

t

XTIL

t

XTIY

System Clock Timing

Table 21. System Clock Timing

Parameter Test Conditions1Min Max Unit

t

XTIY

t

MCLKDS

t

XTIH

t

XTIL

t

COP

t

COPDIV2

1

AVDD, HPVDD, V

XTI/CODEC_MCLK system clock cycle time 72 ns

XTI/CODEC_MCLK duty cycle 40:60 60:40

XTI/CODEC_MCLK system clock pulse width high 32 ns

XTI/CODEC_MCLK system clock pulse width low 32 ns

CODEC_CLKOUT propagation delay from XTI/CODEC_MCLK falling edge 20 ns

CLKODIV2 propagation delay from XTI/CODEC_MCLK falling edge 20 ns

= 3.3 V, AGND = 0 V, TA = +25°C, Slave Mode, fS = 48 kHz, XTI/CODEC_MCLK = 256 × fS unless otherwise stated.

DDEXT

Figure 22. System (CODEC_MCLK) Clock Timing

Rev. A | Page 29 of 36 | March 2010

Page 30

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

FREQUENCY (fS)

MAGNITUDE (dB)

0 0.25

0

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0.75 1.00 1.250.50 1.50 2.001.75

FREQUENCY (fS)

MAGNITUDE (dB)

0 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40 0.45 0.50

−0.05

−0.04

−0.03

−0.02

−0.01

0

0.01

0.02

0.03

0.04

0.05

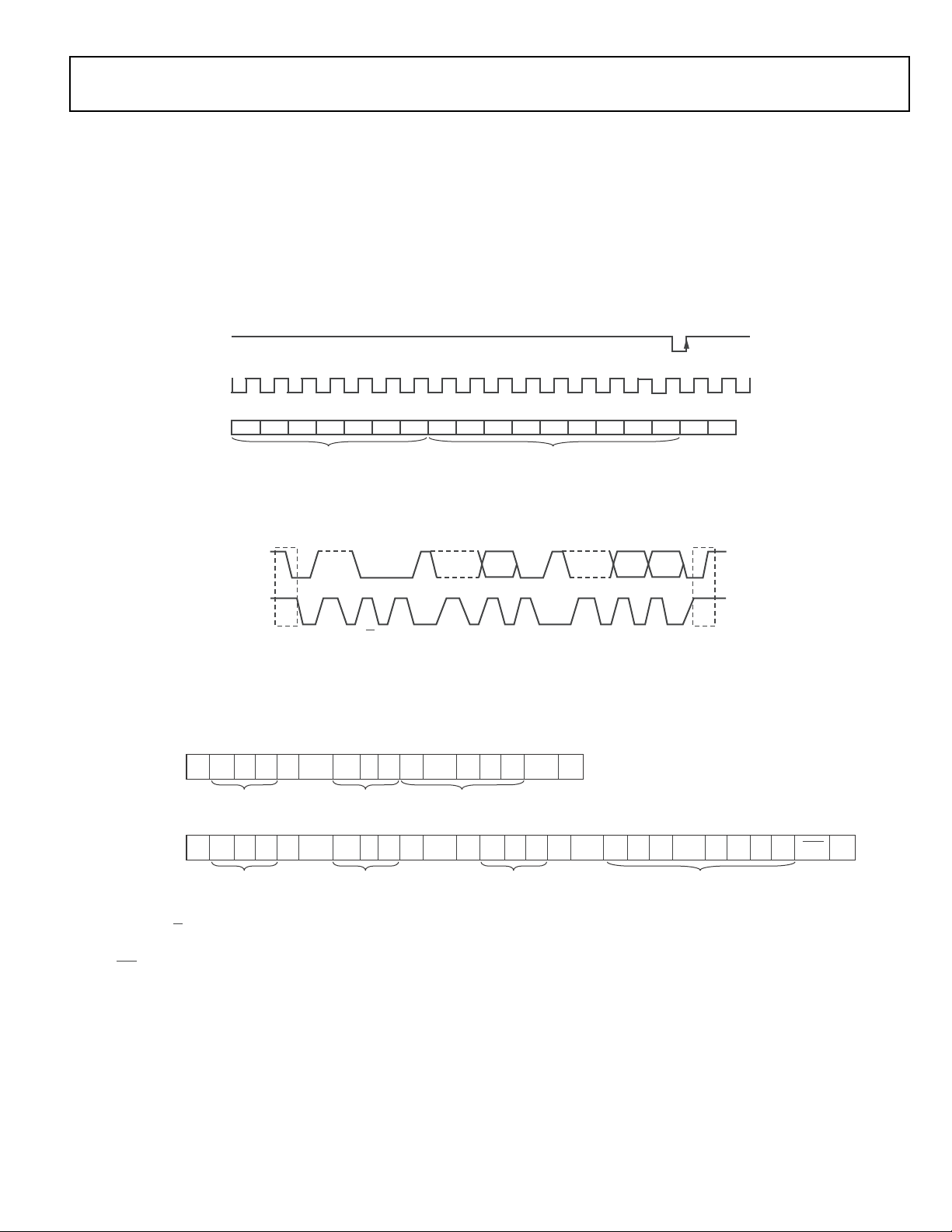

Digital Filter Characteristics

Table 22. Digital Filter Characteristics

Parameter Conditions Min Typical Max Unit

ADC FILTER

Pass Band ±0.04 dB 0 0.445 × fSHz

–6 dB 0.5 × f

Pass Band Ripple ±0.04 dB

Stop Band 0.555 × f

Stop Band Attenuation f > 0.567 × f

S

–61 dB

S

High-Pass Filter Corner Frequency –3 dB 3.7 Hz

–0.5 dB 10.4 Hz

–0.1 dB 21.6 Hz

DAC FILTER

Pass Band ±0.04 dB 0 0.445 × f

–6 dB 0.5 × f

Pass Band Ripple ±0.04 dB

Stop Band 0.555 × f

Stop Band Attenuation f > 0.565 × f

S

–61 dB

S

Codec Clock Tolerance

Frequency Range 8.0 13.8 MHz

Jitter Tolerance 50 pS

S

S

S

Hz

Hz

Hz

Hz

Hz

CONVERTER FILTER RESPONSE

Figure 23. ADC Digital Filter Frequency Response, Sampling Rate = 48 kHz

Figure 24. ADC Digital Filter Ripple, Sampling Rate = 48 kHz

Rev. A | Page 30 of 36 | March 2010

Page 31

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

FREQUENCY (fS)

MAGNITUDE (dB)

0 0.25

0

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0.75 1.00 1.250.50 1.50 2.001.75

FREQUENCY (fS)

MAGNITUDE (dB)

0 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40 0.45 0.50

−0.05

−0.04

−0.03

−0.02

−0.01

0

0.01

0.02

0.03

0.04

0.05

FREQUENCY (kHz)

MAGNITUDE (dB)

0481216

−10

−9

−8

−7

−6

−5

−4

−3

−2

−1

0

FREQUENCY (kHz)

MAGNITUDE (dB)

0 4 12 20816

−10

−9

−8

−7

−6

−5

−4

−3

−2

−1

0

FREQUENCY (kHz)

MAGNITUDE (dB)

0 4 12 2081624

−10

−9

−8

−7

−6

−5

−4

−3

−2

−1

0

FREQUENCY (kHz)

MAGNITUDE (dB)

04 12816

−0.4

−0.3

−0.2

−0.1

0

0.1

0.2

0.3

0.4

Figure 25. DAC Digital Filter Frequency Response, Sampling Rate = 48 kHz

Figure 26. DAC Digital Filter Ripple, Sampling Rate = 48 kHz

DIGITAL DE-EMPHASIS

Figure 28. De-Emphasis Frequency Response, Sampling Rate = 44.1 kHz

Figure 29. De-Emphasis Frequency Response, Sampling Rate = 48 kHz

Figure 27. De-Emphasis Frequency Response, Sampling Rate = 32 kHz

Rev. A | Page 31 of 36 | March 2010

Figure 30. De-Emphasis Error, Sampling Rate = 32 kHz

Page 32

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

FREQUENCY (kHz)

MAGNITUDE (dB)

0 4 12 20816

−0.4

−0.3

−0.2

−0.1

0

0.1

0.2

0.3

0.4

FREQUENCY (kHz)

MAGNITUDE (dB)

0 4 12 2081624

−0.4

−0.3

−0.2

−0.1

0

0.1

0.2

0.3

0.4

289-BALL CSP_BGA BALL ASSIGNMENT

Signals added or changed to the ADSP-BF52xC processor for

the embedded codec are shown in Table 23 and Table 24. Please

refer to the published ADSP-BF52x processor data sheet for

descriptions of additional signals for the processor.

Table 23. 289-Ball CSP_BGA Ball Assignment

(Alphabetically)

Signal Ball No. Signal Ball No.

ADCDAT A16 HPGND G17

1

Figure 31. De-Emphasis Error, Sampling Rate = 44.1 kHz

ADCLRC A15 HPVDD G16

AGND H22 LHPOUT B20

1

AVD D J22

LLINEIN E23

CMODE E22 LOUT F22

CODEC_BCLK A19 MICBIAS H23

CODEC_CLKOUT D22 MICIN J23

CSB D23 RHPOUT B21

CSCL B23 RLINEIN F23

CSDA C23 ROUT G22

1

CVDD H17

VMID G23

DACDAT A18 XTI/CODEC_MCLK A22

DACLRC A17 XTO A21

1

For ADSP-BF52x processor (without internal codec) compatibility,

connect this ball to V

DDEXT

.

Figure 32. De-Emphasis Error, Sampling Rate = 48 kHz

Table 24. 289-Ball CSP_BGA Ball Assignment

(Numerically)

Ball No. Signal Ball No. Signal

A15 ADCLRC E22 CMODE

A16 ADCDAT E23 LLINEIN

A17 DACLRC F22 LOUT

A18 DACDAT F23 RLINEIN

A19 CODEC_BCLK G16

A21 XTO G17 HPGND

A22 XTI/CODEC_MCLK G22 ROUT

B20 LHPOUT G23 VMID

B21 RHPOUT H17

B23 CSCL H22 AGND

C23 CSDA H23 MICBIAS

D22 CODEC_CLKOUT J22

D23 CSB J23 MICIN

1

For ADSP-BF52x processor (without internal codec) compatibility,

connect this ball to V

Rev. A | Page 32 of 36 | March 2010

DDEXT

1

HPVDD

1

CVDD

1

AVD D

.

Page 33

TOP VIEW

A1 BALL

PAD CORNER

3456789 1011121314151612 17 18 19 20 21 22 23

M

B

C

D

E

F

G

H

J

K

L

N

R

T

A

U

V

W

Y

AA

AB

AC

P

KEY:

V

DDINT

GND

V

DDEXT

I/O V

DDMEM

AGND

HPGND

AVDD

CODEC I/O

BALLS THAT HAVE CHANGED USAGE ON THE

ADSP-BF522C/523C/524C/525C/526C/527C:

HPVDD

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

Figure 33 shows the top view of the ADSP-BF52xC processor

ball configuration.

Figure 33. ADSP-BF52xC Processor Ball Configuration (Top View)

Rev. A | Page 33 of 36 | March 2010

Page 34

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

BOTTOM VIEW

A1 BALL

PAD CORNER

345678910111213141516 1217181920212223

M

B

C

D

E

F

G

H

J

K

L

N

R

T

A

U

V

W

Y

AA

AB

AC

P

KEY:

V

DDINT

GND

V

DDEXT

I/O V

DDMEM

AGND

HPGND

AVDD

CODEC I/O

BALLS THAT HAVE CHANGED USAGE ON THE

ADSP-BF522C/523C/524C/525C/526C/527C:

HPVDD

Figure 34 shows the bottom view of the ADSP-BF52xC proces-

sor ball configuration.

Figure 34. ADSP-BF52xC Processor Ball Configuration (Bottom View)

Rev. A | Page 34 of 36 | March 2010

Page 35

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

NOTES

1. DIMENSIONS ARE IN MILLIMETERS.

2. COMPLIES WITH JEDEC REGISTERED OUTLINE

MO-195, VARIATION AJ AND EXCEPTION TO PACKAGE HEIGHT

AND BALL HEIGHT.

3. MINIMUM BALL HEIGHT 0.20

CL

CL

0.5 BSC

BALL

PITCH

11.00 BSC SQ

TOP VIEW

A1 BALL

PAD CORNER

12.00 BSC SQ

SIDE VIEW

DETAIL A

DETAIL A

SEATING PLANE

0.35

0.30

0.25

BALL DIAMETER

0.08 MAX

COPLANARITY

0.20 MIN

BOTTOM VIEW

A1 BALL

PAD CORNER

M

B

C

D

E

F

G

H

J

K

L

N

R

T

A

345678910111213141516 12

1.40

1.26

1.11

17181920212223

U

V

W

Y

AA

AB

AC

P

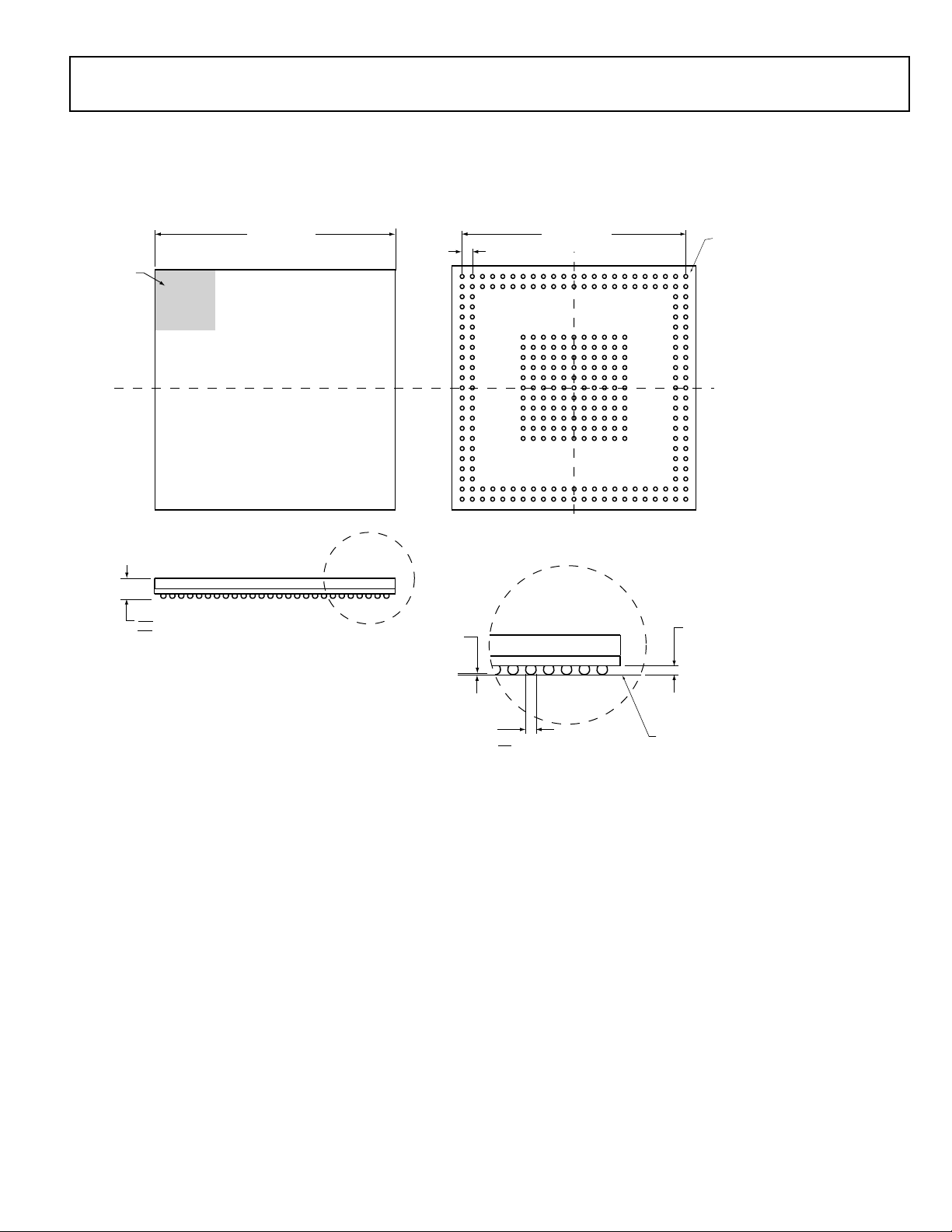

OUTLINE DIMENSIONS

Dimensions in Figure 35, 289-Ball CSP_BGA (BC-289-2) are

shown in millimeters.

Figure 35. 289-Ball CSP_BGA (BC-289-2)

Rev. A | Page 35 of 36 | March 2010

Page 36

ADSP-BF522C/ADSP-BF523C/ADSP-BF524C/ADSP-BF525C/ADSP-BF526C/ADSP-BF527C

ORDERING GUIDE

Model

1

Temperature

Range2

Instruction

Rate (Max) Package Description

Package

Option

ADSP-BF522KBCZ-3C2 0°C to +70°C 300 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF522KBCZ-4C2 0°C to +70°C 400 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF523KBCZ-5C2 0°C to +70°C 533 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF523KBCZ-6C2 0°C to +70°C 600 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF524KBCZ-3C2 0°C to + 70°C 300 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF524KBCZ-4C2 0°C to + 70°C 400 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF525KBCZ-5C2 0°C to +70°C 533 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF525KBCZ-6C2 0°C to +70°C 600 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF526KBCZ-3C2 0°C to +70°C 300 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF526KBCZ-4C2 0°C to +70°C 400 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF527KBCZ-5C2 0°C to +70°C 533 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

ADSP-BF527KBCZ-6C2 0°C to +70°C 600 MHz 289-Ball Chip Scale Package Ball Grid Array (CSP_BGA) BC-289-2

1

Z = RoHS Compliant Part.

2

Referenced temperature is ambient temperature. The ambient temperature is not a specification. Please see Operating Conditions on Page 21 for junction temperature (TJ)

specification which is the only temperature specification.

©2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06876-0-3/10(A)

Rev. A | Page 36 of 36 | March 2010

Loading...

Loading...