Preliminary

ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

Analog Devices, Inc.

Digital Signal Processor Division

One Technology Way

Norwood, Mass. 02062-9106

Preliminary Revision 0, 2003

Part Number:

82-000640-01

Preliminary

Copyright Information

© 03 Analog Devices, Inc., ALL RIGHTS RESERVED. This document

may not be reproduced in any form without prior, express written consent

from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, EZ-ICE, EZ-LAB, SHARC, the SHARC logo,

TigerSHARC, the TigerSHARC logo, VisualDSP, and the VisualDSP

logo are registered trademarks of Analog Devices, Inc.

Apex-ICE, Blackfin, the Blackfin logo, CROSSCORE, the CROSSCORE

logo, EZ-KIT Lite, ICEPAC, Mountain-ICE, SHARCPAC, Summit-ICE, Trek-ICE, VisualDSP++ and the VisualDSP++ logo are

trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

CONTENTS

Preliminary

CONTENTS

PREFACE

Purpose ...................................................................................... xxxiii

Instruction Set Enhancements ............................................... xxxiii

For more Information about Analog Products ............................. xxxiv

For Technical or Customer Support ............................................ xxxv

What’s New in this Manual ......................................................... xxxv

Related Documents .................................................................... xxxvi

Conventions ............................................................................. xxxvii

INTRODUCTION

Overview—Why Fixed-Point DSP? ............................................... 1-1

ADSP-2199x Design Advantages ................................................... 1-2

ADSP-2199x Architecture Overview .............................................. 1-6

DSP Core Architecture ............................................................ 1-9

DSP Peripherals Architecture ................................................. 1-11

Memory Architecture ............................................................ 1-12

Internal (On-chip) Memory .............................................. 1-13

ADSP-2199x Mixed Signal DSP Controller iii

Hardware Reference

CONTENTS

Preliminary

External (Off-chip) Memory ............................................. 1-14

Interrupts ............................................................................. 1-16

DMA Controller ................................................................... 1-16

DSP Serial Port (SPORT) ..................................................... 1-17

Serial Peripheral Interface (SPI) Port ...................................... 1-18

Controller Area Network (CAN) Module ............................... 1-18

Analog To Digital Conversion System .................................... 1-19

PWM Generation Unit ......................................................... 1-20

Auxiliary PWM Generation Unit ........................................... 1-20

Encoder Interface Unit .......................................................... 1-21

Flag I/O (FIO) Peripheral Unit ............................................. 1-22

Low-Power Operation ........................................................... 1-22

Clock Signals ........................................................................ 1-23

Booting Modes ..................................................................... 1-23

JTAG Port ............................................................................ 1-24

Development Tools ..................................................................... 1-24

Differences from Previous DSPs .................................................. 1-27

Computational Units and Data Register File .......................... 1-27

Arithmetic Status (ASTAT) Register Latency .......................... 1-27

Norm and Exp Instruction Execution .................................... 1-27

Shifter Result (SR) Register as Multiplier Dual Accumulator .. 1-28

Shifter Exponent (SE) Register is not Memory Accessible ....... 1-28

Conditions (SWCOND) and Condition Code (CCODE) Register .

1-29

Unified Memory Space .......................................................... 1-30

iv ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Data Memory Page (DMPG1 and DMPG2) Registers ............ 1-30

Data Address Generator (DAG) Addressing Modes ................. 1-31

Base Registers for Circular Buffers .......................................... 1-31

Program Sequencer, Instruction Pipeline, and Stacks .............. 1-32

Conditional Execution (Difference in Flag Input Support) ...... 1-32

Execution Latencies (Different for JUMP Instructions) ........... 1-33

COMPUTATIONAL UNITS

Overview ...................................................................................... 2-1

Using Data Formats ...................................................................... 2-4

Binary String ........................................................................... 2-5

Unsigned ................................................................................. 2-5

Signed Numbers: Two’s Complement ....................................... 2-5

Signed Fractional Representation: 1.15 .................................... 2-5

ALU Data Types ...................................................................... 2-6

Multiplier Data Types .............................................................. 2-7

Shifter Data Types ................................................................... 2-8

Arithmetic Formats Summary .................................................. 2-8

Setting Computational Modes ..................................................... 2-10

Latching ALU Result Overflow Status .................................... 2-10

Saturating ALU Results on Overflow ...................................... 2-11

Using Multiplier Integer and Fractional Formats .................... 2-11

Rounding Multiplier Results .................................................. 2-13

Unbiased Rounding .......................................................... 2-14

Biased Rounding ............................................................... 2-15

ADSP-2199x Mixed Signal DSP Controller v

Hardware Reference

CONTENTS

Preliminary

Using Computational Status ....................................................... 2-16

Arithmetic Logic Unit (ALU) ...................................................... 2-17

ALU Operation ..................................................................... 2-17

ALU Status Flags ................................................................... 2-18

ALU Instruction Summary .................................................... 2-19

ALU Data Flow Details ......................................................... 2-21

ALU Division Support Features ............................................. 2-24

Multiply—Accumulator (Multiplier) ........................................... 2-29

Multiplier Operation ............................................................. 2-29

Placing Multiplier Results in MR or SR Registers .............. 2-31

Clearing, Rounding, or Saturating Multiplier Results ......... 2-32

Multiplier Status Flags ........................................................... 2-33

Saturating Multiplier Results on Overflow ............................. 2-33

Multiplier Instruction Summary ............................................ 2-35

Multiplier Data Flow Details ................................................. 2-37

Barrel-Shifter (Shifter) ................................................................ 2-39

Shifter Operations ................................................................. 2-39

Derive Block Exponent ..................................................... 2-41

Immediate Shifts .............................................................. 2-42

Denormalize ..................................................................... 2-45

Normalize, Single-Precision Input ..................................... 2-47

Normalize, ALU Result Overflow ...................................... 2-48

Normalize, Double-Precision Input ................................... 2-50

Shifter Status Flags ................................................................ 2-53

vi ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Shifter Instruction Summary .................................................. 2-54

Shifter Data Flow Details ....................................................... 2-55

Data Register File ........................................................................ 2-61

Secondary (Alternate) Data Registers ........................................... 2-63

Multifunction Computations ...................................................... 2-64

PROGRAM SEQUENCER

Overview ...................................................................................... 3-1

Instruction Pipeline ...................................................................... 3-7

Instruction Cache ....................................................................... 3-10

Using the Cache .................................................................... 3-13

Optimizing Cache Usage ....................................................... 3-13

Branches and Sequencing ............................................................ 3-15

Indirect Jump Page (IJPG) Register ........................................ 3-18

Conditional Branches ............................................................ 3-18

Delayed Branches .................................................................. 3-19

Loops and Sequencing ................................................................. 3-23

Managing Loop Stacks ........................................................... 3-26

Restrictions on Ending Loops ................................................ 3-26

Interrupts and Sequencing ........................................................... 3-26

Stacks and Sequencing ................................................................ 3-32

Conditional Sequencing .............................................................. 3-37

Sequencer Instruction Summary .................................................. 3-40

ADSP-2199x Mixed Signal DSP Controller vii

Hardware Reference

CONTENTS

Preliminary

MEMORY

Overview ...................................................................................... 4-1

Internal Address and Data Buses .............................................. 4-6

External Address and Data Buses ............................................. 4-7

Internal Data Bus Exchange .................................................... 4-8

ADSP-2199x Memory Organization ........................................... 4-11

Shadow Write FIFO .............................................................. 4-16

Data Move Instruction Summary ................................................ 4-17

DATA ADDRESS GENERATORS

Overview ...................................................................................... 5-1

Setting DAG Modes ..................................................................... 5-4

Secondary (Alternate) DAG Registers ...................................... 5-4

Bit-Reverse Addressing Mode .................................................. 5-6

DAG Page Registers (DMPGx) ................................................ 5-7

Using DAG Status ........................................................................ 5-8

DAG Operations .......................................................................... 5-9

Addressing with DAGs ............................................................ 5-9

Addressing Circular Buffers ................................................... 5-12

Addressing with Bit-Reversed Addresses ................................. 5-16

Modifying DAG Registers ..................................................... 5-20

DAG Register Transfer Restrictions ............................................. 5-20

DAG Instruction Summary ......................................................... 5-22

viii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

I/O PROCESSOR

Overview ...................................................................................... 6-1

Descriptor-Based DMA Transfers ............................................. 6-5

Autobuffer-Based DMA Transfers ............................................ 6-8

Interrupts from DMA Transfers ............................................... 6-9

Setting Peripheral DMA Modes ................................................... 6-10

MemDMA DMA Settings ...................................................... 6-14

Serial Port DMA Settings ....................................................... 6-15

SPI Port DMA Settings .......................................................... 6-16

Working with Peripheral DMA Modes ......................................... 6-17

Using MemDMA DMA ......................................................... 6-17

Using Serial Port (SPORT) DMA .......................................... 6-18

Descriptor-Based SPORT DMA ........................................ 6-18

Autobuffer-Based SPORT DMA ........................................ 6-19

SPORT DMA Data Packed/Unpacked Enable ................... 6-20

Using Serial Peripheral Interface (SPI) Port DMA ................... 6-21

SPI DMA in Master Mode ................................................ 6-21

SPI DMA in Slave Mode ................................................... 6-23

SPI DMA Errors ............................................................... 6-25

Boot Mode DMA Transfers ......................................................... 6-27

Code Example: Internal Memory DMA ....................................... 6-28

EXTERNAL PORT

Overview ...................................................................................... 7-1

ADSP-2199x Mixed Signal DSP Controller ix

Hardware Reference

CONTENTS

Preliminary

Setting External Port Modes .......................................................... 7-3

Memory Bank and Memory Space Settings .............................. 7-3

External Bus Settings ............................................................... 7-5

Bus Master Settings ................................................................. 7-7

Boot Memory Space Settings ................................................... 7-7

Working with External Port Modes ............................................... 7-8

Using Memory Bank/Space Waitstates Modes .......................... 7-9

Using Memory Bank/Space Clock Modes .............................. 7-10

Using External Memory Banks and Pages ............................... 7-11

Using Memory Access Status ................................................. 7-11

Using Bus Master Modes ....................................................... 7-12

Using Boot Memory Space .................................................... 7-14

Reading from Boot Memory ............................................. 7-14

Writing to Boot Memory .................................................. 7-15

Interfacing to External Memory .................................................. 7-15

Data Alignment—Logical versus Physical Address .................. 7-15

Memory Interface Pins .......................................................... 7-20

Memory Interface Timing ..................................................... 7-24

Code Example: BMS Runtime Access .......................................... 7-28

SERIAL PORT

Overview ...................................................................................... 8-1

SPORT Operation .................................................................. 8-6

SPORT Disable ...................................................................... 8-7

Setting SPORT Modes .................................................................. 8-8

x ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Transmit and Receive Configuration Registers (SP_TCR, SP_RCR)

8-10

Register Writes and Effect Latency ......................................... 8-16

Transmit and Receive Data Buffers (SP_TX, SP_RX) ............. 8-17

Clock and Frame Sync Frequencies ........................................ 8-18

Maximum Clock Rate Restrictions .................................... 8-20

Frame Sync and Clock Example ......................................... 8-20

Data Word Formats ............................................................... 8-20

Word Length .................................................................... 8-21

Endian Format .................................................................. 8-21

Data Type ......................................................................... 8-21

Companding ..................................................................... 8-22

Clock Signal Options ............................................................ 8-22

Frame Sync Options .............................................................. 8-23

Framed versus Unframed ................................................... 8-23

Internal versus External Frame Syncs ................................. 8-25

Active Low versus Active High Frame Syncs ....................... 8-26

Sampling Edge for Data and Frame Syncs .......................... 8-26

Early versus Late Frame Syncs (Normal and Alternate Timing) 8-27

Data-Independent Transmit Frame Sync ............................ 8-29

Multichannel Operation ........................................................ 8-29

Frame Syncs in Multichannel Mode ................................... 8-32

Multichannel Frame Delay ................................................ 8-33

Window Size ..................................................................... 8-33

Window Offset ................................................................. 8-33

ADSP-2199x Mixed Signal DSP Controller xi

Hardware Reference

CONTENTS

Preliminary

Other Multichannel Fields in SP_TCR, SP_RCR .............. 8-34

Channel Selection Registers .............................................. 8-35

Multichannel Enable ......................................................... 8-36

Multichannel DMA Data Packing ..................................... 8-36

Multichannel Mode Example ............................................ 8-37

Moving Data Between SPORTS and Memory ............................. 8-38

SPORT DMA Autobuffer Mode Example .............................. 8-39

SPORT Descriptor-Based DMA Example .............................. 8-40

Support for Standard Protocols ................................................... 8-42

2X Clock Recovery Control ................................................... 8-43

SPORT Pin/Line Terminations ................................................... 8-43

Timing Examples ........................................................................ 8-43

SERIAL PERIPHERAL INTERFACE (SPI) PORT

Overview ...................................................................................... 9-1

Interface Signals ........................................................................... 9-4

Serial Peripheral Interface Clock Signal (SCK) ......................... 9-5

Serial Peripheral Interface Slave Select Input Signal (SPISS) ..... 9-5

Master Out Slave In (MOSI) ................................................... 9-6

Master In Slave Out (MISO) ................................................... 9-6

Interrupt Behavior .................................................................. 9-7

SPI Registers ................................................................................ 9-8

SPI Baud Rate (SPIBAUD) Register ....................................... 9-8

SPI Control (SPICTL) Register ............................................... 9-9

SPI Flag (SPIFLG) Register ................................................... 9-11

xii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Slave-Select Inputs ............................................................ 9-13

Use of FLS Bits in SPIFLG for Multiple-Slave SPI Systems 9-13

SPI Status (SPIST) Register ................................................... 9-15

Transmit Data Buffer (TDBR) Register .................................. 9-17

Receive Data Buffer (RDBR) Register .................................... 9-17

Data Shift (SFDR) Register ................................................... 9-18

Register Mapping .................................................................. 9-18

SPI Transfer Formats ................................................................... 9-19

SPI General Operation ................................................................ 9-22

Clock Signals ........................................................................ 9-23

Master Mode Operation ........................................................ 9-24

Transfer Initiation from Master (Transfer Modes) ................... 9-26

Slave Mode Operation ....................................................... 9-26

Slave Ready for a Transfer .................................................. 9-28

Error Signals and Flags ................................................................ 9-28

Mode-Fault Error (MODF) ................................................... 9-28

Transmission Error (TXE) Bit ................................................ 9-30

Reception Error (RBSY) Bit ................................................... 9-30

Transmit Collision Error (TXCOL) Bit .................................. 9-30

Beginning and Ending of an SPI Transfer .................................... 9-31

DMA .......................................................................................... 9-32

TIMER

Overview .................................................................................... 10-1

Pulsewidth Modulation (PWMOUT) Mode ........................... 10-7

ADSP-2199x Mixed Signal DSP Controller xiii

Hardware Reference

CONTENTS

Preliminary

PWM Waveform Generation ............................................ 10-8

Single-Pulse Generation .................................................. 10-11

Pulsewidth Count and Capture (WDTH_CAP) Mode ......... 10-11

External Event Watchdog (EXT_CLK) Mode ...................... 10-14

Code Examples ......................................................................... 10-14

Timer Example Steps .......................................................... 10-15

Timer0 Initialization Routine .............................................. 10-18

Timer Interrupt Routine ..................................................... 10-20

JTAG TEST-EMULATION PORT

Overview .................................................................................... 11-1

JTAG Test Access Port ................................................................ 11-2

INSTRUCTION Register ........................................................... 11-3

BYPASS Register ........................................................................ 11-4

BOUNDARY Register ................................................................ 11-4

IDCODE Register ...................................................................... 11-4

References .................................................................................. 11-5

SYSTEM DESIGN

Overview .................................................................................... 12-1

Pin Descriptions ......................................................................... 12-1

Recommendations for Unused Pins ....................................... 12-5

Pin States at Reset ....................................................................... 12-6

Resetting the Processor (“Hard Reset”) ...................................... 12-10

Resetting the Processor (“Soft Reset”) ........................................ 12-11

xiv ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Booting the Processor (“Boot Loading”) .................................... 12-13

Booting Modes .................................................................... 12-13

Boot from External 8-Bit Memory (EPROM) over EMI ... 12-13

Execute from External 8-Bit Memory .............................. 12-14

Execute from External 16-Bit Memory ............................ 12-14

Boot from SPI0 with < 4k bits ......................................... 12-14

Boot from SPI0 with > 4k bits ......................................... 12-15

Bootstream Format .............................................................. 12-15

Managing DSP Clocks .............................................................. 12-21

Phase Locked Loop (PLL) ......................................................... 12-23

Clock Generation (CKGEN) Module ........................................ 12-25

Overview of CKGEN Functionality ..................................... 12-25

Hardware Reset Generation ................................................. 12-26

Software Reset Logic ............................................................ 12-27

Clock Generation & PLL Control ........................................ 12-28

Lock Counter ...................................................................... 12-31

Powerdown Control/Modes ....................................................... 12-32

Idle Mode ........................................................................... 12-32

Powerdown Core Mode ....................................................... 12-33

Powerdown Core/Peripherals Mode ...................................... 12-33

Powerdown All Mode .......................................................... 12-34

Register Configurations ............................................................. 12-35

Working with External Bus Masters ........................................... 12-36

Recommended Reading ............................................................. 12-40

ADSP-2199x Mixed Signal DSP Controller xv

Hardware Reference

CONTENTS

Preliminary

PERIPHERAL INTERRUPT CONTROLLER

Overview .................................................................................... 13-1

ADSP-2199x PERIPHERAL INTERRUPT CONTROLLER ...... 13-2

GENERAL OPERATION .......................................................... 13-3

REGISTERS .............................................................................. 13-5

WATCHDOG TIMER

Overview .................................................................................... 14-1

General Operation ...................................................................... 14-1

Registers ..................................................................................... 14-3

POWER ON RESET

Overview .................................................................................... 15-1

ENCODER INTERFACE UNIT

Overview .................................................................................... 16-1

Encoder Loop Timer .................................................................. 16-4

Encoder Interface Structure & Operation .................................... 16-5

Introduction ......................................................................... 16-5

Programmable Input Noise Filtering of Encoder Signals ......... 16-5

Encoder Counter Direction ................................................... 16-9

Alternative Frequency and Direction Inputs ......................... 16-10

Encoder Counter Reset ....................................................... 16-10

Registration Inputs & Software Zero Marker ....................... 16-12

Single North Marker Mode ................................................. 16-14

xvi ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Encoder Error Checking ...................................................... 16-14

EIU Input Pin Status ........................................................... 16-14

Interrupts ............................................................................ 16-15

32-bit Register Accesses ....................................................... 16-15

Encoder Event Timer ................................................................ 16-17

Introduction & Overview .................................................... 16-17

Latching Data from the EET ............................................... 16-18

EET Status Register ............................................................. 16-20

EIU/EET Registers ................................................................... 16-21

Inputs/Outputs ......................................................................... 16-27

AUXILIARY PWM GENERATION UNIT

Overview .................................................................................... 17-1

Independent Mode ...................................................................... 17-2

Offset Mode ............................................................................... 17-4

Operation Features ...................................................................... 17-5

AUXTRIP Shutdown .................................................................. 17-6

AUXSYNC Operation ................................................................. 17-7

Registers ..................................................................................... 17-8

PWM GENERATION UNIT

OVERVIEW ............................................................................... 18-1

GENERAL OPERATION ..................................................... 18-7

FUNCTIONAL DESCRIPTION .......................................... 18-8

Three-Phase Timing & Dead Time Insertion Unit ............. 18-8

ADSP-2199x Mixed Signal DSP Controller xvii

Hardware Reference

CONTENTS

PWM Switching Frequency, PWMTM Register ................. 18-8

PWM Switching Dead Time, PWMDT Register ............... 18-9

PWM Operating Mode, PWMCTRL & PWMSTAT Registers ..

18-10

PWM Duty Cycles, PWMCHA, PWMCHB, PWMCHC Registers

18-12

Special Consideration for PWM Operation in Over-Modulation

18-16

PWM Timer Operation .................................................. 18-19

Effective PWM Accuracy ................................................ 18-20

Switched Reluctance Mode ............................................. 18-21

Output Control Unit ...................................................... 18-21

Crossover Feature ........................................................... 18-22

Preliminary

Output Enable Function ................................................. 18-22

Brushless DC Motor (Electronically Commutated Motor) Control

18-23

GATE DRIVE UNIT ......................................................... 18-25

High Frequency Chopping .............................................. 18-25

PWM Polarity Control, PWMPOL Pin ........................... 18-26

Output Control Feature Precedence ................................ 18-27

Switched Reluctance Mode ............................................. 18-27

PWMSYNC Operation ................................................... 18-31

Internal PWMSYNC generation ..................................... 18-31

External PWMSYNC operation ...................................... 18-31

PWM Shutdown & Interrupt Control Unit ..................... 18-32

xviii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Registers ................................................................................... 18-33

ANALOG TO DIGITAL CONVERTER SYSTEM

Overview .................................................................................... 19-1

ADC Inputs ................................................................................ 19-2

Analog to Digital Converter and Input Structure ......................... 19-2

ADC Control Module ................................................................. 19-6

ADC Clock ........................................................................... 19-6

ADC Data Formats ............................................................... 19-7

Convert Start Trigger ............................................................. 19-8

ADC Time Counters ............................................................. 19-9

Conversion Modes ............................................................... 19-10

Simultaneous Sampling Mode ......................................... 19-11

Latch Mode .................................................................... 19-12

Offset Calibration Mode ................................................. 19-12

DMA Single Channel Acquisition Mode .......................... 19-13

DMA Dual Channel Acquisition Mode ........................... 19-14

DMA Quad Channel Acquisition Mode .......................... 19-14

DMA Octal Channel Acquisition Mode ........................... 19-15

DMA Operation Overview .................................................. 19-15

Voltage Reference ...................................................................... 19-16

Registers ................................................................................... 19-17

FLAG I/O (FIO) PERIPHERAL UNIT

Overview .................................................................................... 20-1

ADSP-2199x Mixed Signal DSP Controller xix

Hardware Reference

CONTENTS

Preliminary

Operation of the FIO Block ........................................................ 20-3

Flag Register ......................................................................... 20-3

Flag as Output ...................................................................... 20-3

Flag as Input ......................................................................... 20-4

Interrupt Outputs ................................................................. 20-4

Flag Wake-up output ............................................................ 20-5

FIO Lines as PWM Shutdown Sources. ................................. 20-5

FIO Lines as SPI Slave Select Lines ........................................ 20-6

Configuration Registers ......................................................... 20-6

Flag Configuration Registers ................................................. 20-7

FIO Direction Control (DIR) Register .............................. 20-8

Flag Control (FLAGC and FLAGS) Registers .................... 20-8

Flag Interrupt Mask (MASKAC, MASKAS, MASKBC, and

MASKBS) Registers ....................................................... 20-8

FIO Polarity Control (POLAR) Register ........................... 20-9

FIO Edge/Level Sensitivity Control (EDGE and BOTH) Registers

20-10

Power-Down Modes ............................................................ 20-10

Idle Mode ...................................................................... 20-11

Power-Down Core Mode ................................................ 20-11

Power-Down Core/Peripherals Mode ............................... 20-12

Power-Down All Mode ................................................... 20-13

Reset State .......................................................................... 20-13

Registers ................................................................................... 20-14

xx ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

CONTROLLER AREA NETWORK (CAN) MODULE

Overview .................................................................................... 21-1

CAN Module Registers ............................................................... 21-4

Master Control Register (CANMCR) ..................................... 21-4

CCR CAN Configuration Mode Request ........................... 21-4

CSR CAN Suspend Mode Request .................................... 21-5

SMR Sleep Mode Request ................................................. 21-6

WBA Wake Up on CAN Bus Activity ................................ 21-6

TxPrio Transmit Priority by message identifier

(if implemented) ............................................................ 21-6

ABO Auto Bus On ............................................................ 21-6

DNM Device Net Mode (if implemented) ......................... 21-7

SRS Software Reset ........................................................... 21-7

Global Status Register (CANGSR) ......................................... 21-8

Rec Receive Mode ............................................................. 21-9

Trm Transmit Mode .......................................................... 21-9

MBptr Mail Box Pointer ................................................... 21-9

CCA CAN Configuration Mode Acknowledge ................... 21-9

CSA CAN Suspend Mode Acknowledge ............................ 21-9

SMA Sleep Mode Acknowledge ....................................... 21-10

EBO CAN Error Bus Off Mode ...................................... 21-10

EP CAN Error Passive Mode ........................................... 21-10

WR CAN Receive Warning Flag ...................................... 21-10

WT CAN Transmit Warning Flag .................................... 21-10

ADSP-2199x Mixed Signal DSP Controller xxi

Hardware Reference

CONTENTS

Preliminary

CAN Configuration Registers ................................................... 21-11

Bit Configuration Register 0 (CANBCR0) ........................... 21-12

Bit Configuration Register 1 (CANBCR1) ........................... 21-13

CAN Configuration Register (CANCNF) ............................ 21-13

TEST Enable for the special functions ............................ 21-14

MRB Mode Read Back ................................................... 21-14

MAA Mode Auto Acknowledge ....................................... 21-15

DIL Disable CAN Internal Loop ..................................... 21-15

DTO Disable CAN TX Output ...................................... 21-15

DRI Disable CAN RX Input ........................................... 21-15

DEC Disable CAN Error Counter .................................. 21-15

Version Code Register (CANVERSION) ............................. 21-16

CAN Error Counter Register (CANCEC) ............................ 21-16

Interrupt Register (CANINTR) ........................................... 21-17

Rx Serial Input from CAN Bus Line (from Transceiver) ... 21-18

TX Serial Output to CAN Bus Line (to Transceiver) ........ 21-18

SMACK Sleep Mode Acknowledge .................................. 21-19

GIRQ Global Interrupt Output ...................................... 21-19

MBTIF Mailbox Transmit Interrupt Output ................... 21-19

MBRIF Mailbox Receive Interrupt Output ..................... 21-19

Data Storage ............................................................................. 21-20

Mailbox Layout ................................................................... 21-21

Mailbox Area ...................................................................... 21-23

Mailbox Types .................................................................... 21-24

xxii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Mailbox Control Logic .............................................................. 21-24

Mailbox Configuration (CANMC / CANMD) ..................... 21-24

Receive Logic ...................................................................... 21-26

Acceptance Filter / Data Acceptance Filter ............................ 21-27

Acceptance Mask Register .................................................... 21-29

FDF Filtering on Data Field (if enabled) .......................... 21-30

FMD Full Mask Data Field ............................................. 21-30

AMIDE Acceptance Mask Identifier Extension ................ 21-31

BaseId Base Identifier ...................................................... 21-31

ExtId Extended Identifier ................................................ 21-31

DFM Data Field Mask .................................................... 21-31

Receive Control Registers .................................................... 21-31

Receive Message Pending Register (CANRMP) ................ 21-31

Receive Message Lost Register (CANRML) ...................... 21-32

Overwrite Protection / Single Shot Transmission Register

(CANOPSS) ................................................................ 21-32

Transmit Logic ................................................................ 21-33

Retransmission ................................................................ 21-34

Single Shot Transmission ................................................. 21-35

Transmit Priority defined by Mailbox Number ................. 21-35

Transmit Control Registers .............................................. 21-35

Transmission Request Set Register (CANTRS) ................. 21-36

Transmission Request Reset Register (CANTRR) ............. 21-36

Abort Acknowledge Register (CANAA) ............................ 21-38

Transmission Acknowledge Register (CANTA) ................. 21-39

ADSP-2199x Mixed Signal DSP Controller xxiii

Hardware Reference

CONTENTS

Preliminary

Temporary Mailbox Disable Feature (CANMBTD) ......... 21-39

Remote Frame Handling Register (CANRFH) ................. 21-41

Mailbox Interrupts .............................................................. 21-43

Mailbox Interrupt Mask Register (CANMBIM) .............. 21-43

Mailbox Transmit Interrupt Flag Register (CANMBTIF) . 21-44

Mailbox Receive Interrupt Flag Register (CANMBRIF) ... 21-45

Global Interrupt ................................................................. 21-46

ADI Access Denied Interrupt .......................................... 21-46

EXTI External Trigger Output Interrupt ......................... 21-46

UCE Universal Counter Event ........................................ 21-47

RMLI Receive Message Lost Interrupt ............................. 21-47

AAI Abort Acknowledge Interrupt .................................. 21-47

UIAI Access to Unimplemented Address Interrupt ........... 21-48

WUI Wake Up Interrupt ................................................ 21-48

BOI Bus-Off Interrupt ................................................... 21-48

EPI Error-Passive Interrupt ............................................. 21-48

EWRI Error Warning Receive Interrupt .......................... 21-49

EWTI Error Warning Transmit Interrupt ........................ 21-49

Global Interrupt Logic .................................................... 21-49

Global Interrupt Mask Register (CANGIM) .................... 21-50

Global Interrupt Status Register (CANGIS) .................... 21-50

Global Interrupt Flag Register (CANGIF) ....................... 21-51

Universal Counter Module .............................................. 21-53

UCEN Universal Counter Enable ............................... 21-53

xxiv ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

UCCT Universal Counter CAN Trigger ....................... 21-53

UCRC Universal Counter Reload / Clear ..................... 21-54

UCCNF Universal Counter Mode ............................... 21-54

Event Counter Modes ................................................. 21-55

Time Stamp Counter Mode ............................................. 21-56

Error Status Register (CANESR) ..................................... 21-57

FER Form Error Flag ...................................................... 21-57

BEF Bit Error Flag .......................................................... 21-57

SA1 Stuck at dominant Error .......................................... 21-58

CRCE CRC Error ........................................................... 21-58

SER Stuff Error ............................................................... 21-58

ACKE Acknowledge Error ............................................... 21-58

Programmable Warning Limit for REC and TEC ............. 21-58

ADSP-2199X DSP CORE REGISTERS

Overview .................................................................................... 22-1

Core Registers Summary ........................................................ 22-2

Register Load Latencies ......................................................... 22-4

Core Status Registers ................................................................... 22-7

Arithmetic Status (ASTAT) Register ....................................... 22-7

Mode Status (MSTAT) Register ............................................. 22-8

System Status (SSTAT) Register ........................................... 22-10

Computational Unit Registers ................................................... 22-11

Data Register File (Dreg) Registers ....................................... 22-11

ALU X- & Y-Input (AX0, AX1, AY0, AY1) Registers ............ 22-12

ADSP-2199x Mixed Signal DSP Controller xxv

Hardware Reference

CONTENTS

Preliminary

ALU Results (AR) Register .................................................. 22-12

ALU Feedback (AF) Register ............................................... 22-12

Multiplier X- & Y-Input (MX0, MX1, MY0, MY1) Registers 22-12

Multiplier Results (MR2, MR1, MR0) Registers .................. 22-13

Shifter Input (SI) Register ................................................... 22-13

Shifter Exponent (SE) & Block Exponent (SB) Registers ...... 22-13

Shifter Results (SR2, SR1, SR0) Registers ............................ 22-13

Program Sequencer Registers ..................................................... 22-14

Interrupt Mask (IMASK) & Latch (IRPTL) Registers .......... 22-15

Interrupt Control (ICNTL) Register .................................... 22-16

Indirect Jump Page (IJPG) Register ..................................... 22-16

PC Stack Page (STACKP) and

PC Stack Address (STACKA) Registers ............................. 22-17

Loop Stack Page (LPSTACKP) and

Loop Stack Address (LPSTACKA) Register ....................... 22-17

Counter (CNTR) Register ................................................... 22-18

Condition Code (CCODE) Register .................................... 22-18

Cache Control (CACTL) Register ....................................... 22-20

Data Address Generator Registers .............................................. 22-20

Index (Ix) Registers ............................................................. 22-21

Modify (Mx) Registers ........................................................ 22-21

Length and Base (Lx,Bx) Register ........................................ 22-21

Data Memory Page (DMPGx) Registers ............................... 22-22

Memory Interface Registers ....................................................... 22-22

PM Bus Exchange (PX) Register .......................................... 22-22

xxvi ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

I/O Memory Page (IOPG) Register ...................................... 22-22

Register & Bit #Defines File (def219x.h) ................................... 22-23

ADSP-2199X DSP I/O REGISTERS

Overview .................................................................................... 23-1

I/O Processor (Memory Mapped) Registers .................................. 23-2

Clock and System Control Registers .......................................... 23-11

PLL Control (PLLCTL) Register ......................................... 23-11

PLL Lock Counter (LOCKCNT) Register ............................ 23-12

Software Reset (SWRST) Register ...................................... 23-13

Next System Configuration (NXTSCR) Register .................. 23-14

System Configuration (SYSCR) Register .............................. 23-15

DMA Controller Registers ......................................................... 23-16

DMA, MemDMA Channel Write Pointer (DMACW_PTR) Register

23-16

DMA, MemDMA Channel Write Configuration (DMACW_CFG)

Register ............................................................................ 23-17

DMA, MemDMA Channel Write Start Page (DMACW_SRP) Register

23-19

DMA, MemDMA Channel Write Start Address (DMACW_SRA)

Register ............................................................................ 23-19

DMA, MemDMA Channel Write Count (DMACW_CNT) Register

23-19

DMA, MemDMA Channel Write Chain Pointer (DMACW_CP)

Register ............................................................................ 23-20

DMA, MemDMA Channel Write Chain Pointer Ready

(DMACW_CPR) Register ................................................ 23-20

ADSP-2199x Mixed Signal DSP Controller xxvii

Hardware Reference

CONTENTS

Preliminary

DMA, MemDMA Channel Write Interrupt (DMACW_IRQ) Register

23-20

DMA, MemDMA Channel Read Pointer (DMACR_PTR) Register

23-21

DMA, MemDMA Channel Read Configuration (DMACR_CFG)

Register ............................................................................ 23-21

DMA, MemDMA Channel Read Start Page (DMACR_SRP) Register

23-22

DMA, MemDMA Channel Read Start Address (DMACR_SRA)

Register ............................................................................ 23-22

DMA, MemDMA Channel Read Count (DMACR_CNT) Register

23-22

DMA, MemDMA Channel Read Chain Pointer (DMACR_CP) Register

23-23

DMA, MemDMA Channel Read Chain Pointer Ready (DMACR_CPR)

Register ............................................................................ 23-23

DMA, MemDMA Channel Read Interrupt (DMACR_IRQ) Register

23-23

SPORT Registers ...................................................................... 23-24

SPORT Transmit Configuration (SP_TCR) Register ............ 23-24

SPORT Receive Configuration (SP_RCR) Register .............. 23-28

SPORT Transmit Data (SP_TX) Register ............................ 23-29

SPORT Receive Data (SP_RX) Register ............................... 23-29

SPORT Transmit (SP_TSCKDIV) and (SP_RSCKDIV) Serial Clock

Divider Registers ............................................................. 23-30

SPORT Transmit (SP_TFSDIV) and Receive (SP_RFSDIV) Frame

Sync Divider Registers ...................................................... 23-31

SPORT Status (SP_STATR) Register ................................... 23-31

xxviii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

SPORT Multi-Channel Transmit Select (SP_MTCSx) Registers 23-33

SPORT Multi-Channel Receive Select (SP_MRCSx) Registers 23-34

SPORT Multi-Channel Configuration (SP_MCMCx) Registers 23-35

SPORT DMA Receive Pointer (SPDR_PTR) Register .......... 23-39

SPORT Receive DMA Configuration (SPDR_CFG) Register 23-39

SPORT Receive DMA Start Page (SPDR_SRP) Register ....... 23-41

SPORT Receive DMA Start Address (SPDR_SRA) Register .. 23-41

SPORT Receive DMA Count (SPDR_CNT) Register .......... 23-42

SPORT Receive DMA Chain Pointer (SPDR_CP) Register .. 23-42

SPORT Receive DMA Chain Pointer Ready (SPDR_CPR)

Register ............................................................................ 23-43

SPORT Receive DMA Interrupt (SPxDR_IRQ) Register ...... 23-43

SPORT Transmit DMA Pointer (SPDT_PTR) Register ........ 23-44

SPORT Transmit DMA Configuration (SPDT_CFG) Register 23-44

SPORT Transmit DMA Start Address (SPDT_SRA) Register 23-45

SPORT Transmit DMA Start Page (SPDT_SRP) Register .... 23-45

SPORT Transmit DMA Count (SPDT_CNT) Register ........ 23-46

SPORT Transmit DMA Chain Pointer (SPDT_CP) Register 23-46

SPORT Transmit DMA Chain Pointer Ready (SPDT_CPR)

Register ............................................................................ 23-47

SPORT Transmit DMA Interrupt (SPDT_IRQ) Register ..... 23-47

Serial Peripheral Interface Registers ............................................ 23-48

SPI Control (SPICTL) Register ............................................ 23-48

SPI Flag (SPIFLG) Register ................................................. 23-51

SPI Status (SPIST) Register ................................................. 23-52

ADSP-2199x Mixed Signal DSP Controller xxix

Hardware Reference

CONTENTS

Preliminary

SPI Transmit Buffer (TDBR) Register ................................. 23-54

Receive Buffer, SPI (RDBR) Register ................................... 23-54

Receive Data Buffer Shadow, SPI (RDBRS) Register ............ 23-55

SPI Baud Rate (SPIBAUD) Register .................................... 23-55

SPI DMA Current Pointer (SPID_PTR) Register ................. 23-55

SPI DMA Configuration (SPID_CFG) Register ................... 23-56

SPI DMA Start Page (SPID_SRP) Register .......................... 23-58

SPI DMA Start Address (SPID_SRA) Register ..................... 23-58

SPI DMA Word Count (SPID_CNT) Register .................... 23-58

SPI DMA Next Chain Pointer (SPID_CP) Register ............. 23-58

SPI DMA Chain Pointer Ready (SPID_CPR) Register ......... 23-59

SPI DMA Interrupt (SPID_IRQ) Register ........................... 23-59

Timer Registers ........................................................................ 23-59

Timer Global Status and Control (T_GSRx) Registers ......... 23-60

Timer Configuration (T_CFGRx) Registers ......................... 23-62

Timer Counter, low word (T_CNTLx) and high word (T_CNTHx)

Registers .......................................................................... 23-63

Timer Period, low word (T_PRDLx) and high word (T_PRDHx)

Registers .......................................................................... 23-65

Timer Width, low word (T_WLRx) and high word (T_WHRx) Register

23-66

External Memory Interface Registers ......................................... 23-68

External Memory Interface Control/Status (E_STAT) Register 23-68

External Memory Interface Control (EMICTL) Register ...... 23-69

Boot Memory Select Control (BMSCTL) Register ............... 23-70

xxx ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

CONTENTS

Preliminary

Memory Select Control (MSxCTL) Registers ....................... 23-72

I/O Memory Select Control (IOMSCTL) Register .............. 23-73

External Port Status (EMISTAT) Register ............................. 23-73

Memory Page (MEMPGx) Registers ..................................... 23-75

NUMERIC FORMATS

Overview .................................................................................... 24-1

Un/Signed: Two’s-Complement Format ....................................... 24-1

Integer or Fractional .................................................................... 24-2

Binary Multiplication .................................................................. 24-4

Fractional Mode and Integer Mode ........................................ 24-5

Block Floating-Point Format ....................................................... 24-6

INDEX

ADSP-2199x Mixed Signal DSP Controller xxxi

Hardware Reference

Preliminary

-xxxii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

Preface

Preliminary

PREFACE

Purpose

The ADSP-2199x Mixed Signal DSP Controller Hardware Reference pro-

vides architectural information on the ADSP-2199x family of DSP

products and the ADSP-219x modified Harvard architecture Digital Signal Processor (DSP) core. The architectural descriptions cover functional

blocks, buses, and ports, including all the features and processes they

support.

Instruction Set Enhancements

The ADSP-2199x provides near source code compatibility with the previous family members, easing the process of porting code. All computational

instructions (but not all registers) from previous ADSP-2100 family DSPs

ADSP-2199x Mixed Signal DSP Controller xxxiii

Hardware Reference

For more Information about Analog Products

Preliminary

are available in the ADSP-2199x. New instructions, control registers, or

other facilities, required to support the new feature set of the ADSP-219x

core are:

• Program flow control differences (pipeline execution and changes

to looping)

• Memory accessing differences (DAG support and memory map)

• Peripheral I/O differences (additional ports and added DMA

functionality)

For programming information, see the ADSP-219x DSP Instruction Set

Reference.

For more Information about Analog

Products

Analog Devices is online on the internet at http://www.analog.com. Our

Web pages provide information on the company and products, including

access to technical information and documentation, product overviews,

and product announcements.

You may also obtain additional information about Analog Devices and its

products in any of the following ways:

Visit our World Wide Web site at www.analog.com

• FAX questions or requests for information to 1(781)461-3010.

• Access the DSP Division File Transfer Protocol (FTP) site at

ftp.analog.com or ftp 137.71.23.21 or ftp://ftp.analog.com.

xxxiv ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

ftp

Preliminary

For Technical or Customer Support

You can reach our Customer Support group in the following ways:

E-mail questions to MixedSignalDSP@analog.com or

dsp.europe@analog.com (European customer support)

• Telex questions to 924491, TWX:710/394-6577

• Cable questions to ANALOG NORWOODMASS

• Contact your local ADI sales office or an authorized ADI

distributor

• Send questions by mail to:

Analog Devices, Inc.

DSP Division

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

Preface

What’s New in this Manual

This is the first edition of the Mixed Signal DSP Controller Hardware Reference. Summaries of changes between editions will start with the next

edition.

ADSP-2199x Mixed Signal DSP Controller xxxv

Hardware Reference

Related Documents

Preliminary

Related Documents

For more information about Analog Devices DSPs and development

products, see the following documents:

• ADSP-2199x Mixed Signal DSP Data Sheet

• ADSP-219x DSP Instruction Set Reference

• VisualDSP++ User’s Guide for ADSP-21xx Family DSPs

• C Compiler and Library Manual for ADSP-219x Family DSPs

• Assembler and Preprocessor Manual for ADSP-219x Family DSPs

• Linker and Utilities Manual for ADSP-219x Family DSPs

• Getting Started Guide for ADSP-219x Family DSPs

All the manuals are included in the software distribution CD-ROM. To

access these manuals, use the Help Topics command in the VisualDSP++

environment’s Help menu and select the Online Manuals. From this Help

topic, you can open any of the manuals, which are in Adobe Acrobat PDF

format.

xxxvi ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

Preliminary

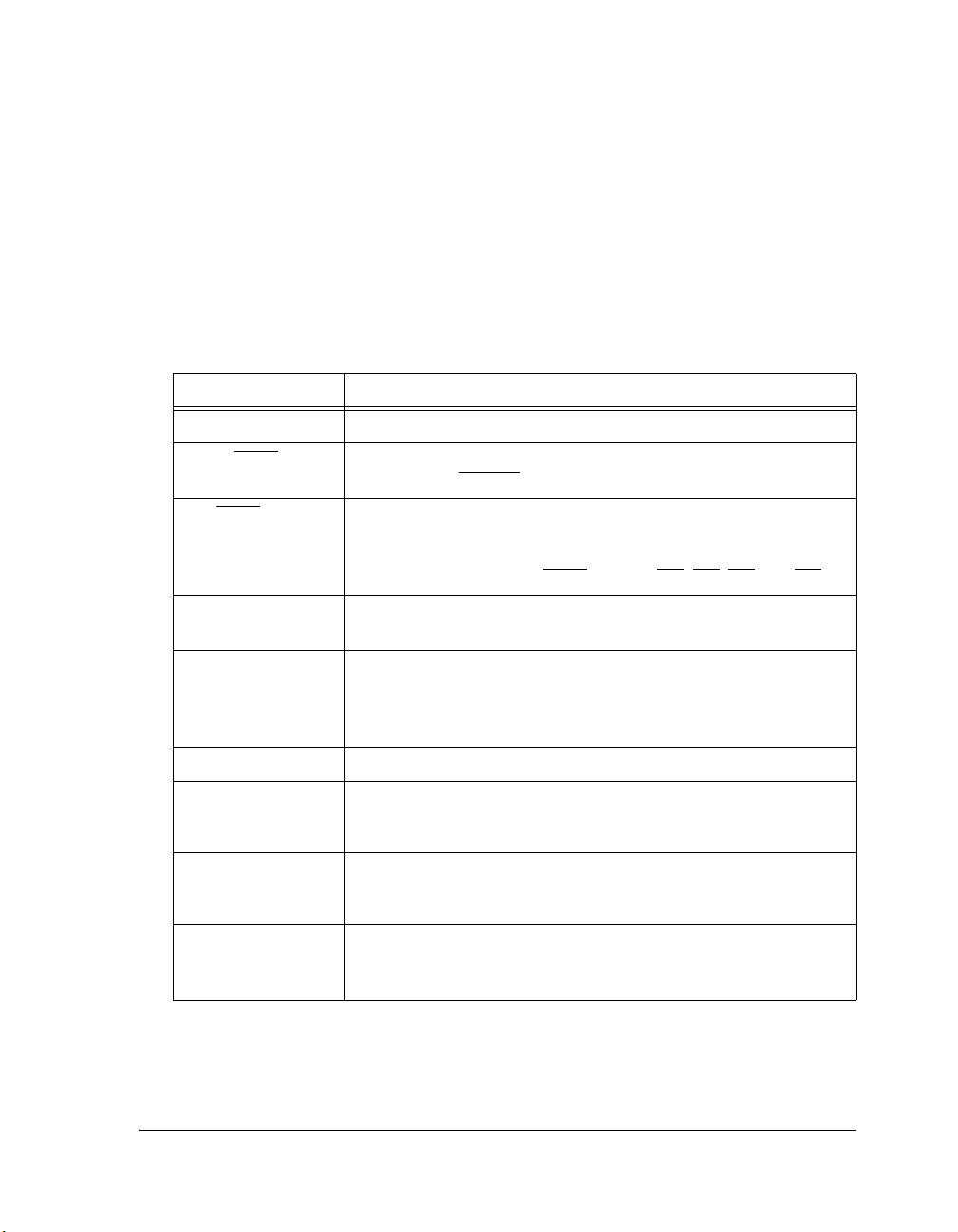

Conventions

The following are conventions that apply to all chapters. Note that additional conventions, which apply only to specific chapters, appear

throughout this document.

Table -1. Notation Conventions

Example Description

AX0, SR, PX Register names appear in UPPERCASE and keyword font

TMR0E, RESET Pin names appear in UPPERCASE and keyword font; active low signals

appear with an OVERBAR.

DRx, MS3-0 Register and pin names in the text may refer to groups of registers or

pins. When a lowercase “x” appears in a register name (e.g., DRx), that

indicates a set of registers (e.g.,

shown with a hyphen (e.g., MS3-0 indicates MS3, MS2, MS1, and MS0).

DR0, DR1, and DR2). A range also may be

Preface

If, Do/Until Assembler instructions (mnemonics) appear in Mixed-case and keyword

font

[this, that]

|this, that|

0xabcd, b#1111 A 0x prefix indicates hexadecimal; a b# prefix indicates binary

L

[

Click Here In the online version of this document, a cross reference acts as a hyper-

Assembler instruction syntax summaries show optional items two ways.

When the items are optional and none is required, the list is shown

enclosed in square brackets, []. When the choices are optional, but one

is required, the list is shown enclosed in vertical bars, ||.

A note, providing information of special interest or identifying a related

DSP topic.

A caution, providing information on critical design or programming

issues that influence operation of the DSP.

text link to the item being referenced. Click on blue references (Table,

Figure, or section names) to jump to the location.

ADSP-2199x Mixed Signal DSP Controller xxxvii

Hardware Reference

Conventions

Preliminary

xxxviii ADSP-2199x Mixed Signal DSP Controller

Hardware Reference

Introduction

Preliminary

1 INTRODUCTION

Overview—Why Fixed-Point DSP?

A digital signal processor’s data format determines its ability to handle signals of differing precision, dynamic range, and signal-to-noise ratios.

Because 16-bit, fixed-point DSP math is required for certain DSP coding

algorithms, using a 16-bit, fixed-point DSP can provide all the features

needed for certain algorithm and software development efforts. Also, a

narrower bus width (16-bit as opposed to 32- or 64-bit wide) leads to

reduced power consumption and other design savings. The extent to

which this is true depends on the fixed-point processor’s architecture.

High-level language programmability, large address spaces, and wide

dynamic range allow system development time to be spent on algorithms

and signal processing concerns, rather than assembly language coding,

code paging, and error handling. The ADSP-2199x DSP is a highly integrated, 16-bit fixed-point DSP that provides many of these design

advantages.

ADSP-2199x Mixed Signal DSP Controller Hardware Reference 1-1

ADSP-2199x Design Advantages

Preliminary

ADSP-2199x Design Advantages

The ADSP-2199x family DSPs are mixed-signal DSP controllers based on

the ADSP-219x DSP core, suitable for a variety of high-performance

industrial motor control and signal processing applications that require

the combination of a high-performance DSP and the mixed-signal integration of embedded control peripherals such as analog to digital

conversion with communications interfaces such as CAN and SPI.

The ADSP-2199x integrates the 160 MIPS, fixed point ADSP-219x family base architecture with a serial port, an SPI compatible port, a DMA

controller, three programmable timers, general purpose Programmable

Flag pins, extensive interrupt capabilities, on-chip program and data

memory spaces, and a complete set of embedded control peripherals that

permits fast motor control and signal processing in a highly integrated

environment.

The ADSP-219x architecture balances a high-performance processor core

with high performance buses (PM, DM, DMA). In the core, every computational instruction can execute in a single cycle. The buses and

instruction cache provide rapid, unimpeded data flow to the core to maintain the execution rate.

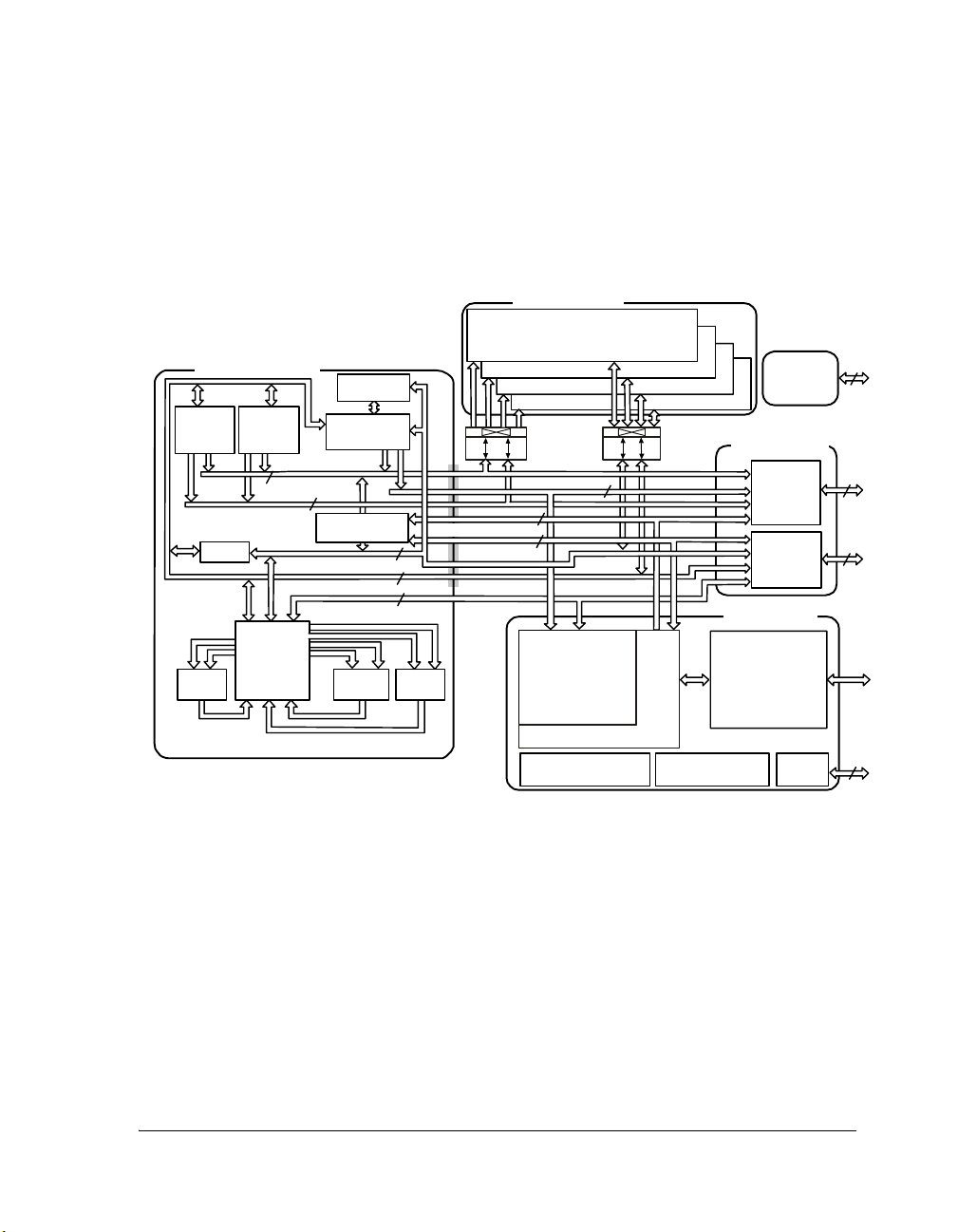

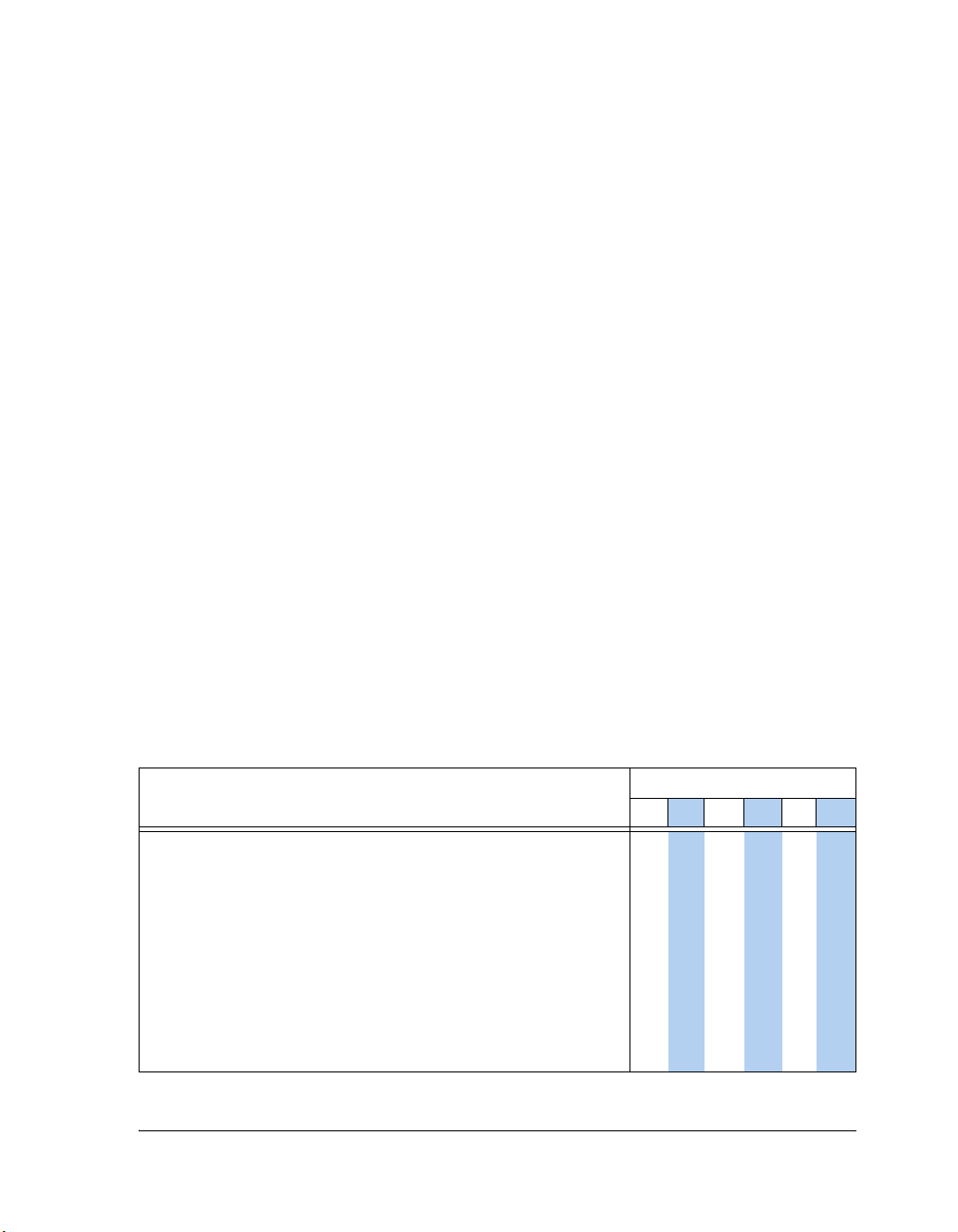

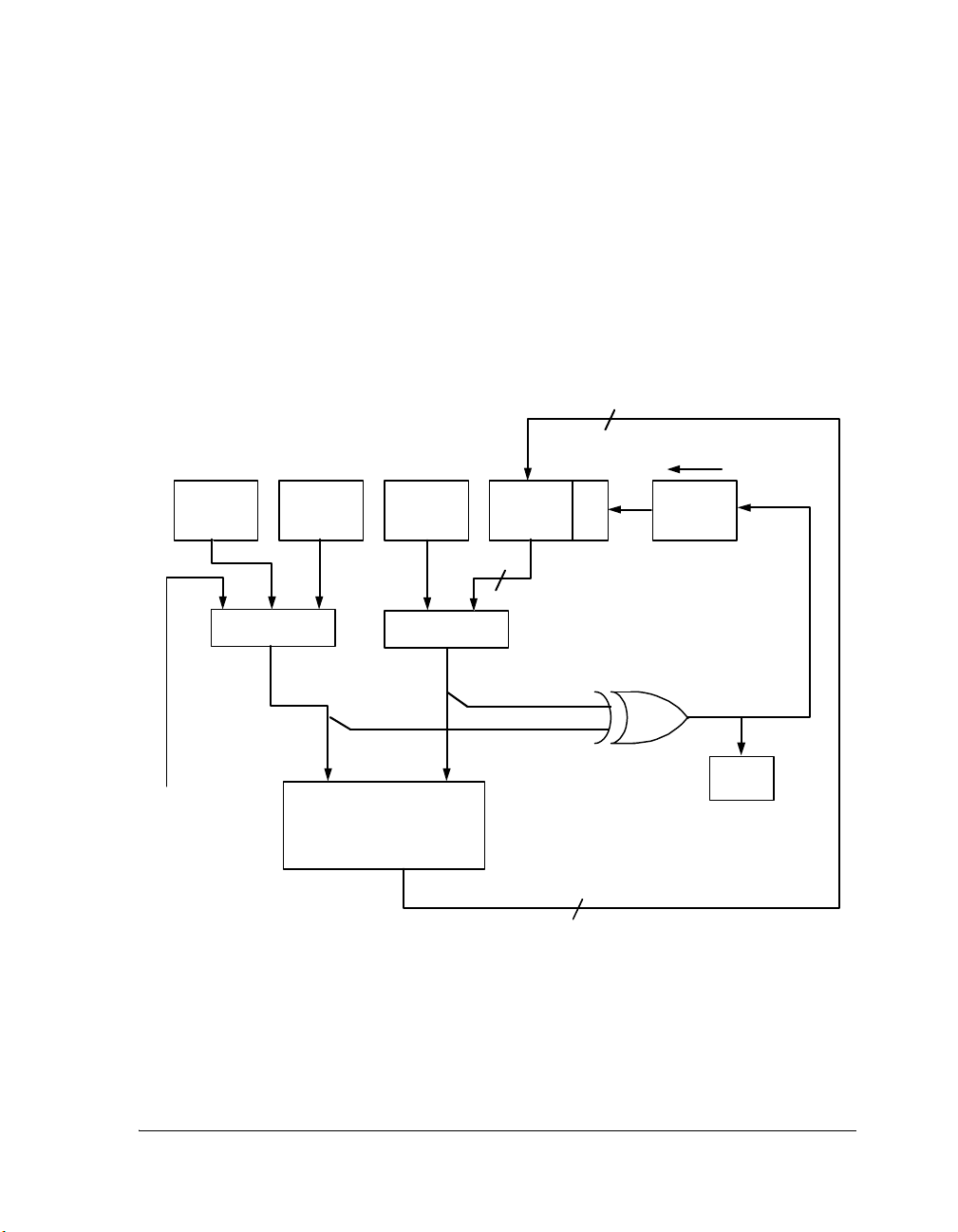

Figure 1-2 on page 1-7 shows a detailed block diagram of the processor,

illustrating the following architectural features:

• Computation units—multiplier, ALU, shifter, and data register file

• Program sequencer with related instruction cache, interval timer,

and Data Address Generators (DAG1 and DAG2)

• Dual-blocked SRAM

• External ports for interfacing to off-chip memory, peripherals, and

hosts

1-2 ADSP-2199x Mixed Signal DSP Controller Hardware Reference

Introduction

Preliminary

• Communications ports such as a serial port (SPORT), serial

peripheral interface (SPI) port, and a CAN Module (ADSP-21992

only)

• Mixed signal and embedded control peripherals such as analog to

digital conversion, Encoder Interface Unit, PWM Generator, etc.,

that permit fast motor control and signal processing in a highly

integrated environment.

• JTAG Test Access Port for board test and emulation

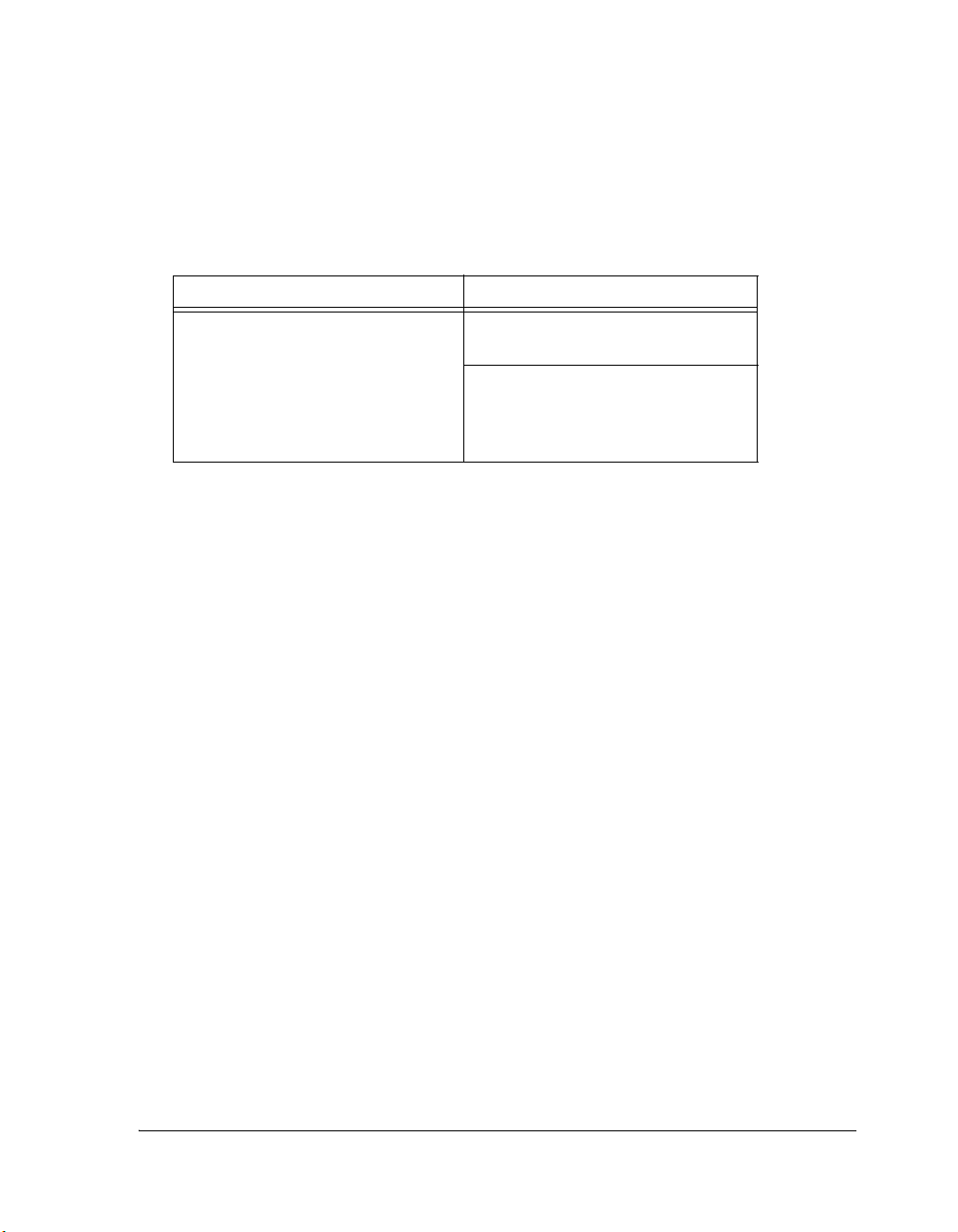

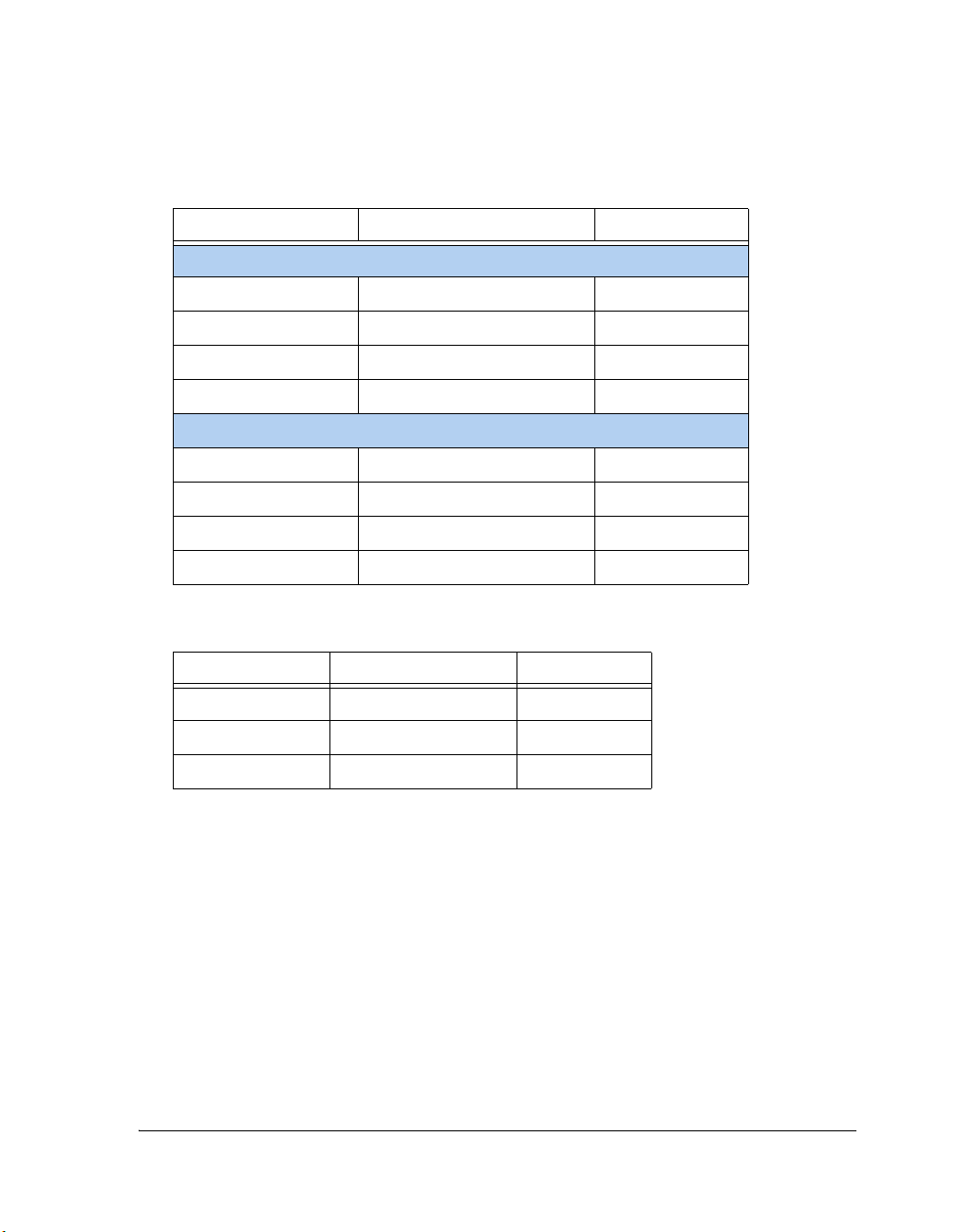

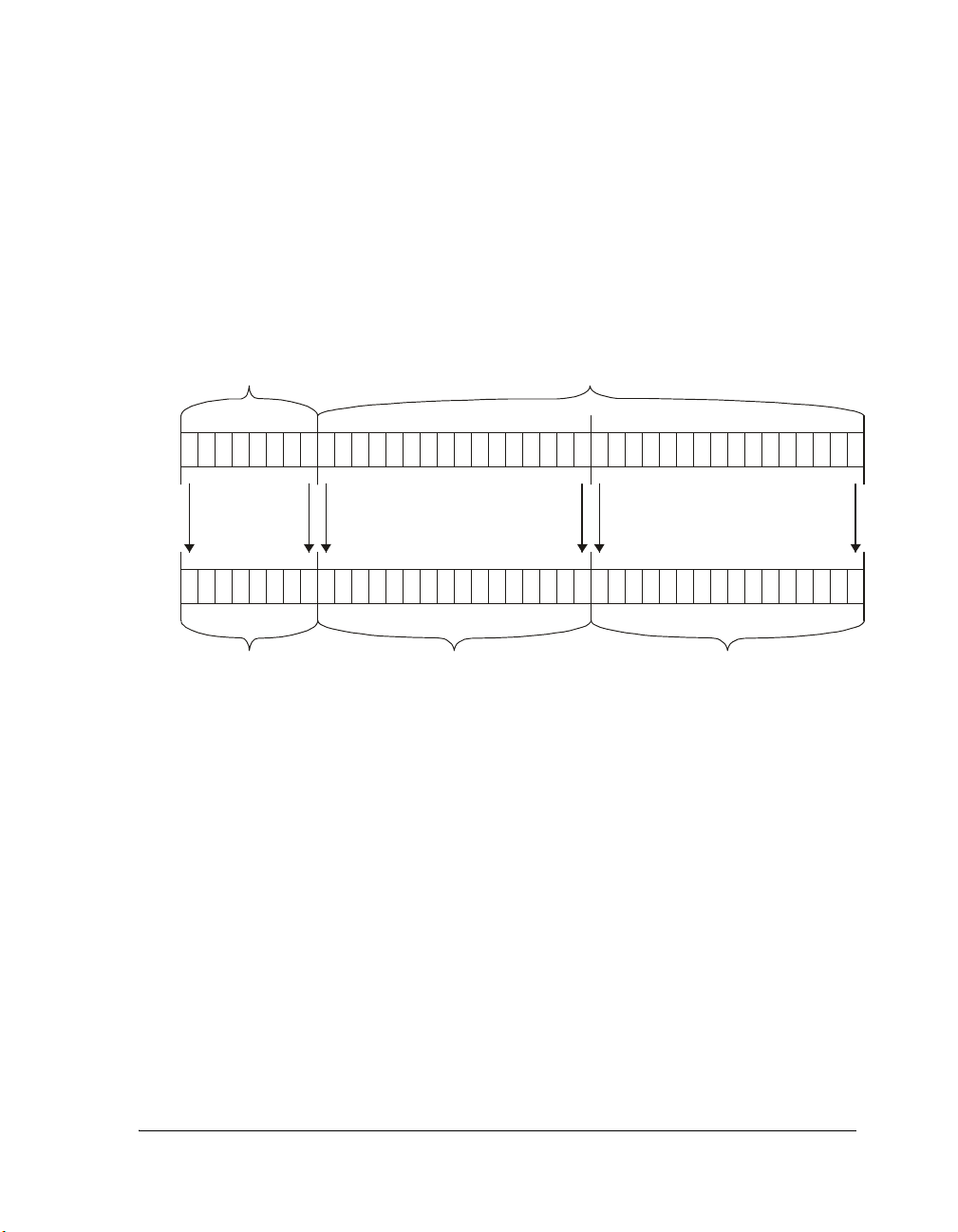

Figure 1-1 on page 1-4 also shows the three on-chip buses of the

ADSP-2199x: the Program Memory (PM) bus, Data Memory (DM) bus,

and Direct Memory Accessing (DMA) bus. The PM bus provides access to

either instructions or data. During a single cycle, these buses let the processor access two data operands (one from PM and one from DM), and

access an instruction (from the cache).

ADSP-2199x Mixed Signal DSP Controller Hardware Reference 1-3

ADSP-2199x Design Advantages

Preliminary

The buses connect to the ADSP-2199x’s external port, which provides the

processor’s interface to external memory, I/O memory-mapped, and boot

memory. The external port performs bus arbitration and supplies control

signals to shared, global memory and I/O devices.

CLOCK

GENERATOR / PLL

JTA G

TEST &

EMULA TION

PWM

GENERATION

UNIT

I/O

BUS

I/O REGISTERS

ENCODER

INTE RFAC E

UNIT

(A ND EE T )

160 MHZ

ADSP-219X

DS P

AUXILIARY

PWM

UNIT

FLAG

I/O

DMRAM

(BLOCK 1)

SPI

WATCHDOG

TIMER

PMR OM

(BLOCK 2)

SPO RT

INTERRUPT

CONTROLLER

PM R AM

(BLO CK 0)

(SEE NOTE2) (SEE NOTE 2) (SEE NOTE 2)

PM ADDRESS/DATA

DM ADDRE SS/DATA

TIMER 0

TIMER 1

TIMER 2

(I CN TL )

EXT ERN AL

MEMORY

INTE RFAC E

(EMI)

CONTROLLER

(S EE N OT E 1 )

ADDRESS

DATA

CONTROL

AR EA

NETWORK

(CAN)

AD C

CONTROL

POR

MEMORYDMA

CONTROLLER

PIPELINE

FLASH ADC

VREF

NOTES:

1. THE CONTROLLER AREA NETWORK (CAN) APPLIES O NLY TO THE ADSP-21992.

2. REFER TO THEMEMORY CHAPTER FOR SIZES OF THE MEMORY BLOCKS.

Figure 1-1. ADSP-2199x DSP Block Diagram

1-4 ADSP-2199x Mixed Signal DSP Controller Hardware Reference

Introduction

Preliminary

Further, the ADSP-2199x addresses the five central requirements for

DSPs:

• Fast, flexible arithmetic computation units

Fast, Flexible Arithmetic. The ADSP-2199x family DSPs execute

all computational instructions in a single cycle. They provide both

fast cycle times and a complete set of arithmetic operations.

• Unconstrained data flow to and from the computation units

Unconstrained Data Flow. The ADSP-2199x has a modified Harvard architecture combined with a data register file. In every cycle,

the DSP can:

— Read two values from memory or write one value to

memory

— Complete one computation

— Write up to three values back to the register file

• Extended precision and dynamic range in the computation units

40-Bit Extended Precision. The DSP handles 16-bit integer and

fractional formats (two’s-complement and unsigned). The processors carry extended precision through result registers in their

computation units, limiting intermediate data truncation errors.

• Dual address generators with circular buffering support

Dual Address Generators. The DSP has two data address generators (DAGs) that provide immediate or indirect (pre- and

post-modify) addressing. Modulus and bit-reverse operations are

supported with memory page constraints on data buffer placement

only.

ADSP-2199x Mixed Signal DSP Controller Hardware Reference 1-5

ADSP-2199x Architecture Overview

Preliminary

• Efficient program sequencing

Efficient Program Sequencing. In addition to zero-overhead loops,

the DSP supports quick setup and exit for loops. Loops are both

nestable (eight levels in hardware) and interruptable. The processors support both delayed and non-delayed branches.

ADSP-2199x Architecture Overview

The ADSP-2199x Family DSPs are mixed-signal DSP controllers based

on the ADSP-219x DSP core, suitable for a variety of high-performance

industrial motor control and signal processing applications that require

the combination of a high-performance DSP and the mixed-signal integration of embedded control peripherals These DSPs provide a complete

system-on-a-chip, integrating a large, high-speed SRAM and I/O periph-

1-6 ADSP-2199x Mixed Signal DSP Controller Hardware Reference

Introduction

Preliminary

erals supported by a dedicated DMA bus. The following sections

summarize the features of each functional block in the ADSP-2199x architecture, which appears in Figure 1-1 on page 1-4.

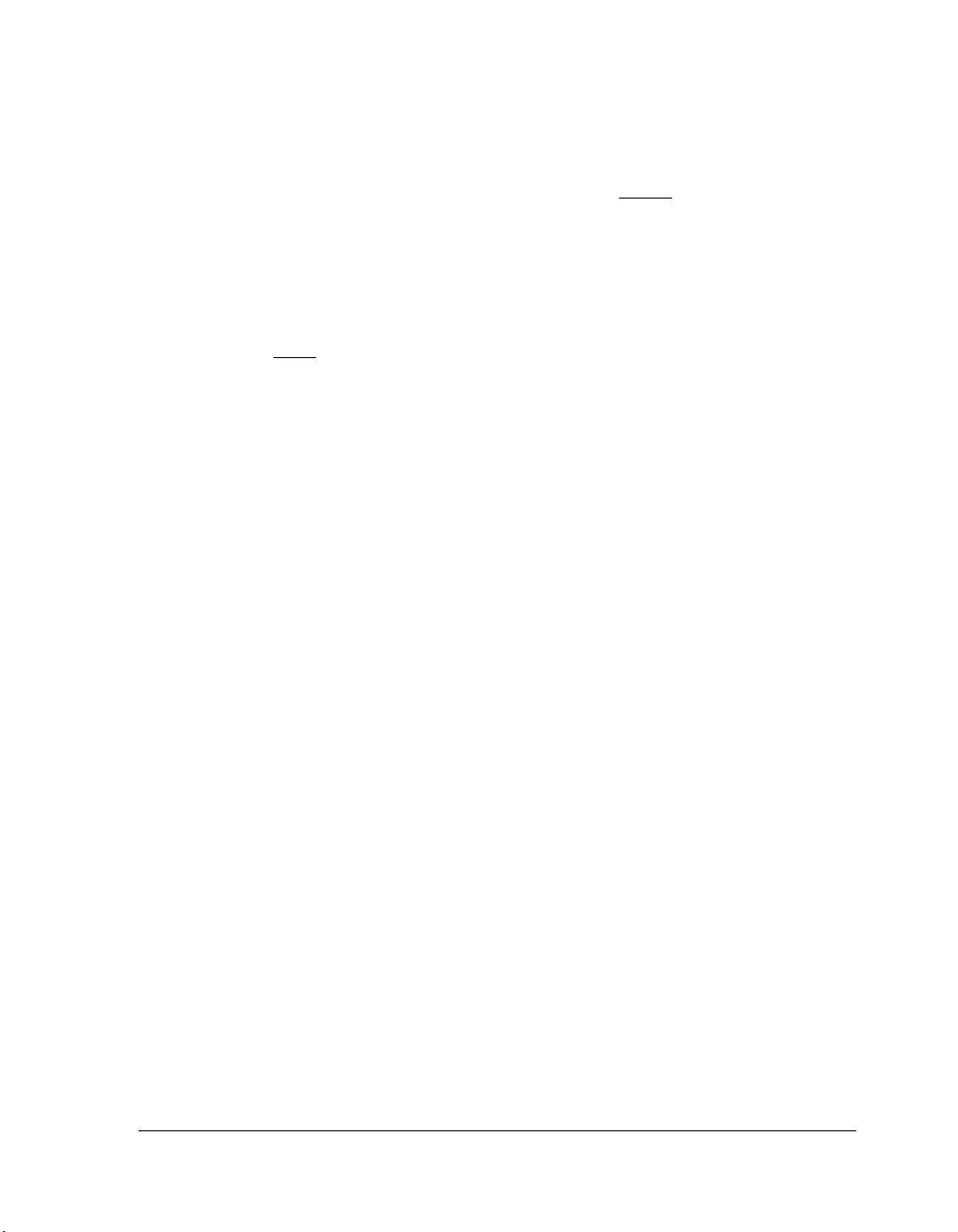

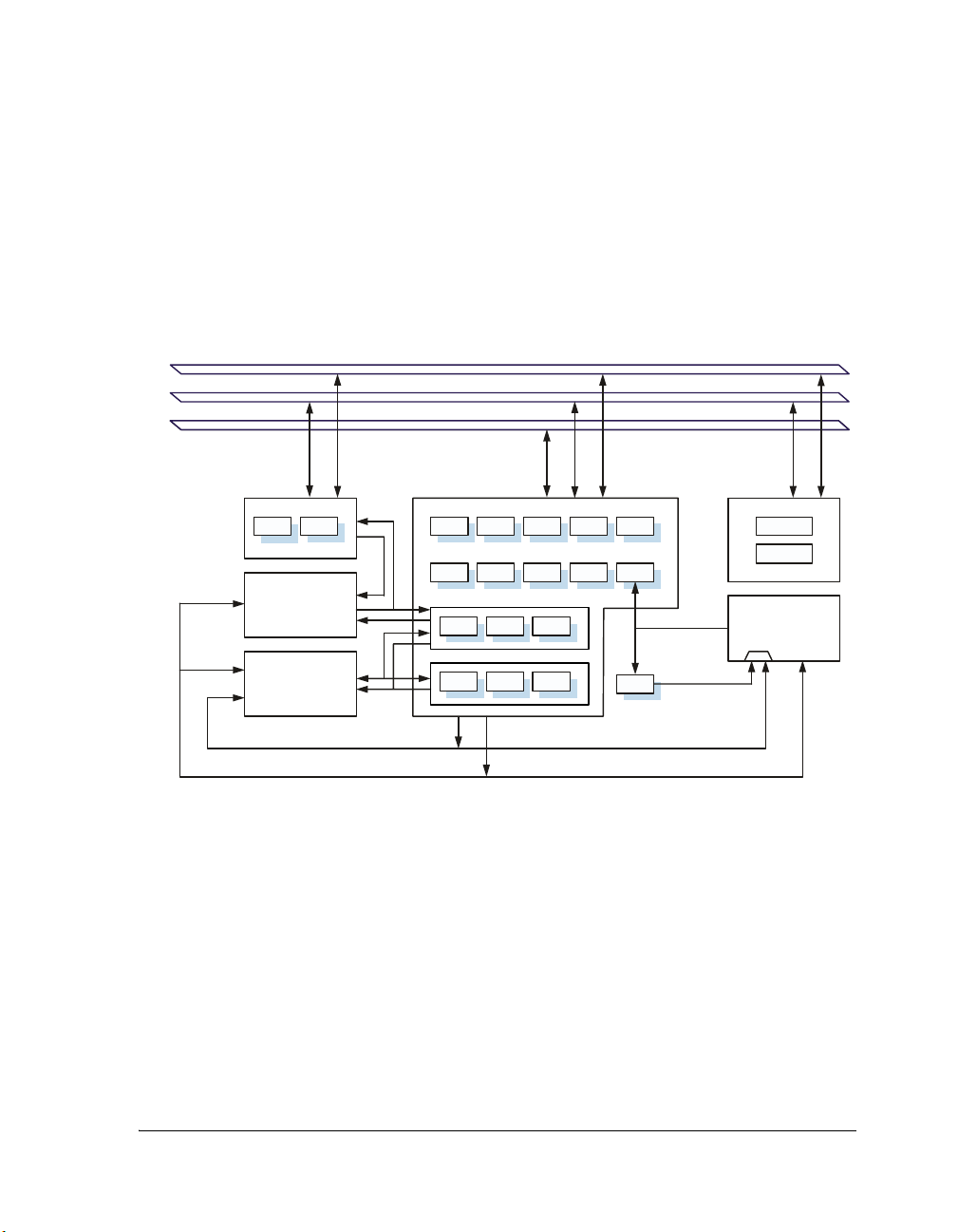

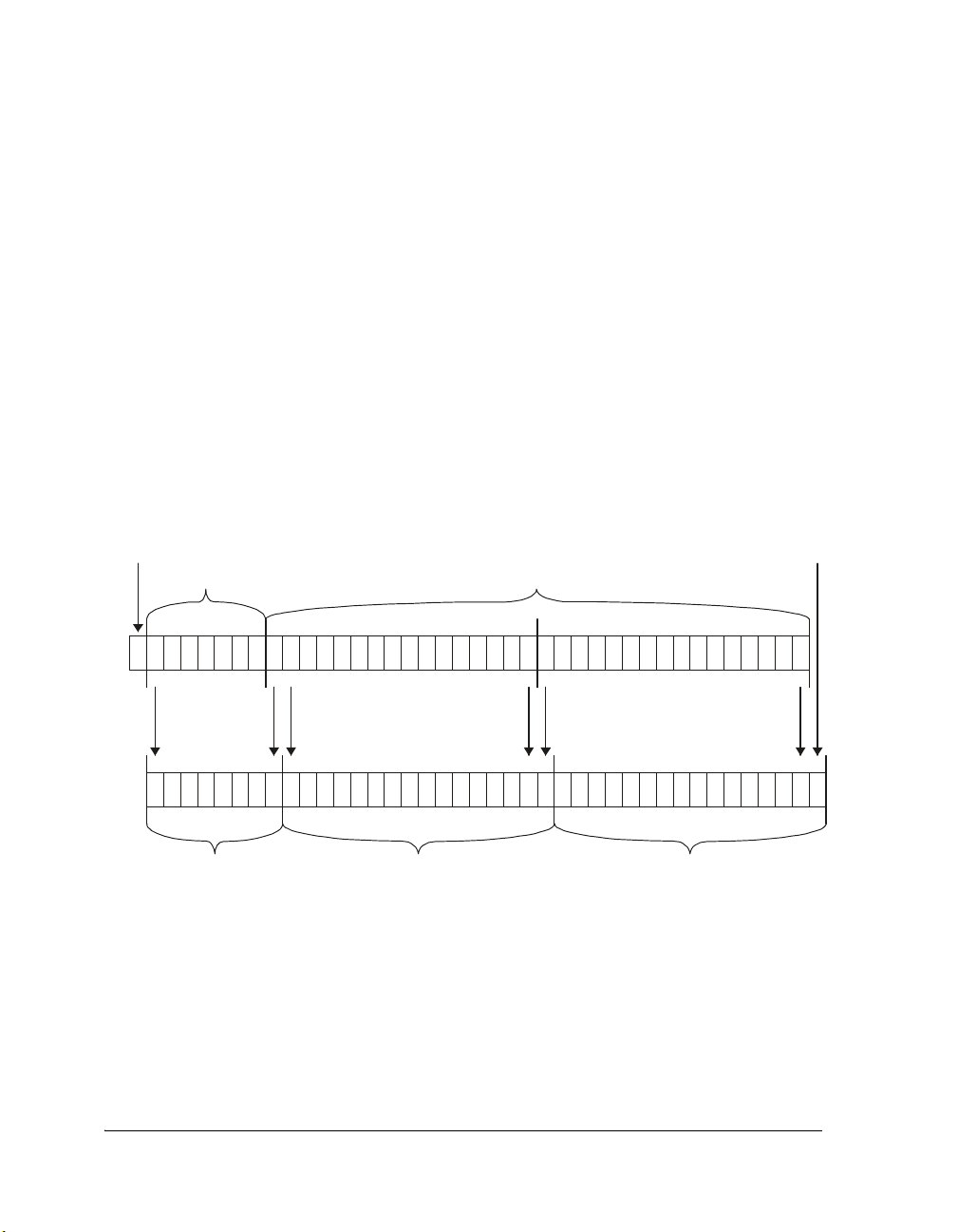

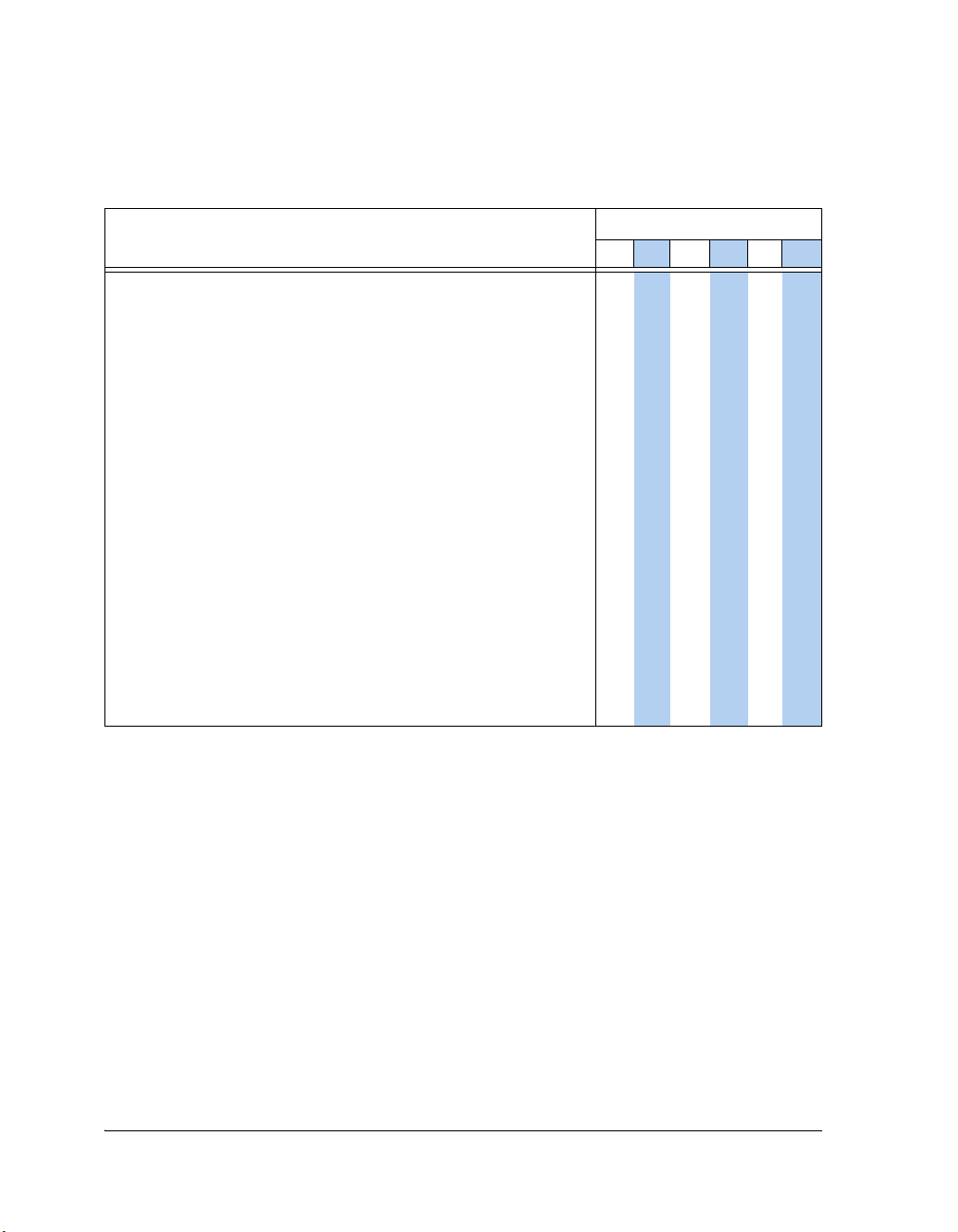

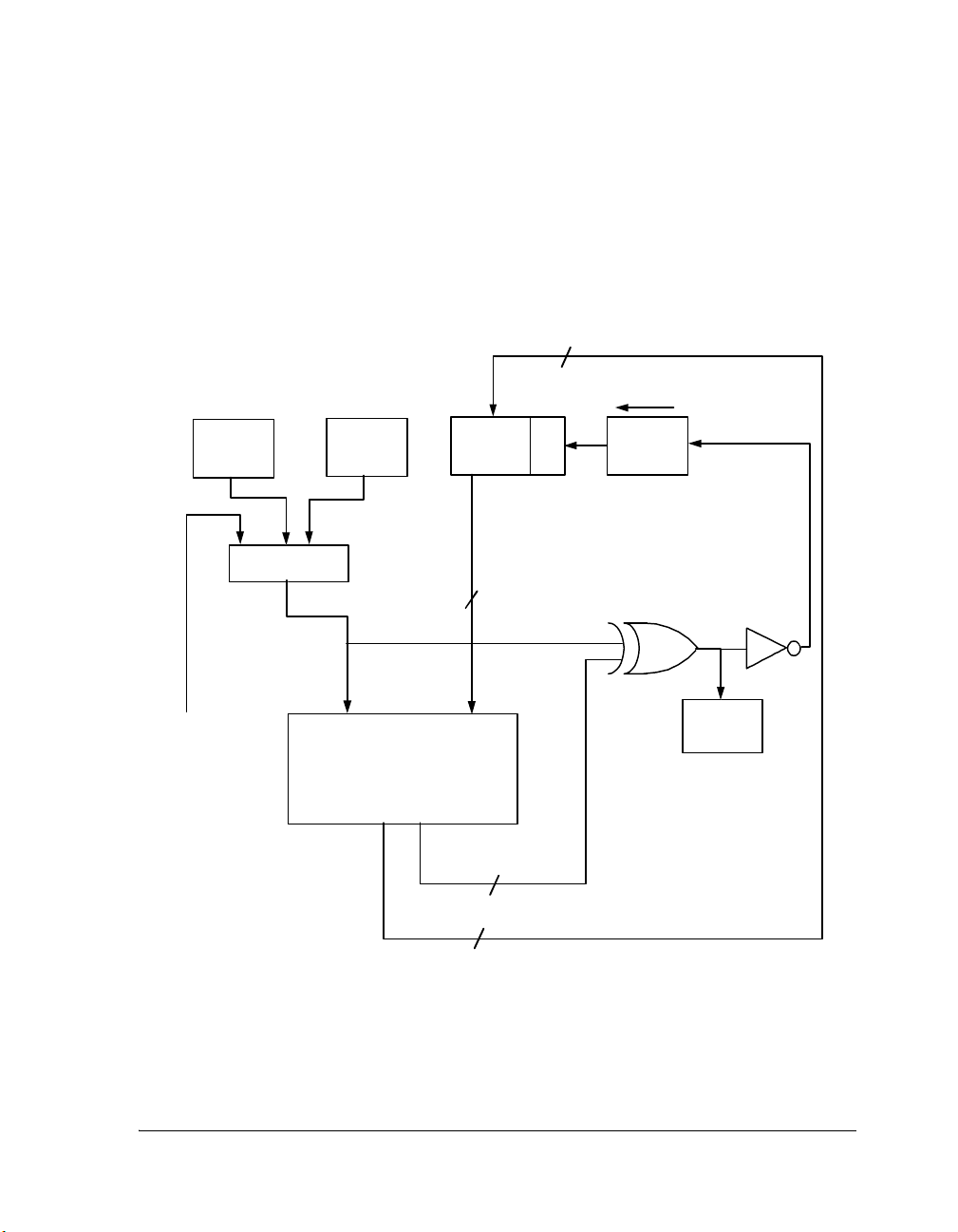

ADSP-219X DSP CORE

PX

DAG2

4X4X16

INPUT

REGIST ERS

RESULT

REGIST ERS

16 X 16-BIT

DAG1

4X4X16

DM ADDRESS BUS

DATA

REGISTER

FILE

MULT

PM ADDRESS BUS

24

24

PM DATA BUS

CACHE

64 X 24-BIT

PROGRAM

SEQUENCER

DMA CONNECT

DM DATA BUS

I/O DATA

BARREL

SHIFTER

Figure 1-2. DSP Core

24

16

16

DMA ADDRESS

ALU

INTERNAL MEMORY

FOUR INDEPENDENT BLOCKS

24 B IT

ADDRESS

ADDRESS

DMA DATA

24 BIT

16 BIT

ADDRESS

ADDRESS

I/O ADDRESS

24

24

I/O REGISTERS

(MEMORY-MAPPED)

CONTROL

STATUS

BUFFERS

DMA CONTROLLER

SYSTEM INTERRUPT

CONTROLLER

16 BI T

0

K

1

C

K

O

2

C

DATA

DATA

18

L

B

DATA

DATA

PROGRAMMABLE

FLAGS (16)

K

O

3

L

C

B

O

L

B

I/O PROCESSOR

PERIPHERALS

COMMUNICATIONS

JTAG

K

TEST AND

C

O

EMULA TION

L

B

EXTERNAL PORT

ADDR BUS

MUX

DATA BUS

MUX

EMBEDDED

CONTROL

AND

PORTS

TIMERS

6

22

16

3

(3)

The ADSP-2199x combines the ADSP-219x family base architecture

(three computational units, two data address generators, and a program

sequencer) with an Analog to Digital Converter, Encoder Interface Unit,

PWM generator, a CAN Module (ADSP-21992 only) a serial port, an

SPI-compatible port, a DMA controller, three programmable timers, general-purpose Programmable Flag pins, extensive interrupt capabilities, and

on-chip program and data memory blocks.

ADSP-2199x Mixed Signal DSP Controller Hardware Reference 1-7

ADSP-2199x Architecture Overview

Preliminary

The ADSP-2199x architecture is code compatible with ADSP-218x family

DSPs. Though the architectures are compatible, the ADSP-2199x architecture has a number of enhancements over the ADSP-218x architecture.

The enhancements to computational units, data address generators, and

program sequencer make the ADSP-2199x more flexible and even easier

to program than the ADSP-218x DSPs.

Indirect addressing options provide addressing flexibility—pre-modify

with no update, pre- and post-modify by an immediate 8-bit, two’s-complement value and base address registers for easier implementation of

circular buffering.

The ADSP-2199x DSPs integrate various amounts of on-chip memory.

Please refer to “ADSP-2199x Memory Organization” in Chapter 4, Mem-

ory for the memory configuration for each device in the ADSP-2199x

family of DSPs. Power-down circuitry is also provided to meet the low

power needs of battery operated portable equipment.

The ADSP-2199x’s flexible architecture and comprehensive instruction

set support multiple operations in parallel. For example, in one processor

cycle, the ADSP-2199x can:

• Generate an address for the next instruction fetch

• Fetch the next instruction

• Perform one or two data moves

• Update one or two data address pointers

• Perform a computational operation

These operations take place while the processor continues to:

• Receive and transmit data through the serial port

• Receive or transmit data over the SPI port

• Access external memory through the external memory interface

1-8 ADSP-2199x Mixed Signal DSP Controller Hardware Reference

Introduction

Preliminary

• Decrement the timers

• Operate the embedded control peripherals (ADC, PWM, EIU, etc.

DSP Core Architecture

The ADSP-219x instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every

single-word instruction can be executed in a single processor cycle. The

ADSP-219x assembly language uses an algebraic syntax for ease of coding

and readability. A comprehensive set of development tools supports program development.

Figure 1-2 on page 1-7 shows the architecture of the ADSP-219x core. It

contains three independent computational units: the ALU, the multiplier/accumulator, and the shifter. The computational units process 16-bit

data from the register file and have provisions to support multiprecision

computations. The ALU performs a standard set of arithmetic and logic

operations; division primitives also are supported. The multiplier performs single-cycle multiply, multiply/add, and multiply/subtract

operations. The multiplier has two 40-bit accumulators, which help with

overflow. The shifter performs logical and arithmetic shifts, normalization, denormalization, and derive exponent operations. The shifter can

efficiently implement numeric format control, including multiword and

block floating-point representations.

Register-usage rules influence placement of input and results within the

computational units. For most operations, the computational units’ data

registers act as a data register file, permitting any input or result register to

provide input to any unit for a computation. For feedback operations, the

computational units let the output (result) of any unit be input to any

unit on the next cycle. For conditional or multifunction instructions,