初步技术数据http://www.elecfans.com 电子发烧友

初步技术数据 ADSP-21535

概要

300 MHz 高性能 Blackfin DSP 内核

2 个 16 位 MAC,2 个 40 位 ALU,2 个 40 位累加器,

4 个 8 位视频 ALU,以及 1 个 40 位移位器

RISC 式寄存器和指令模型,编程简单,编译环境友好

先进的调试、跟踪和性能监视

V

内核电压

范围 0.9-1.5V,带有动态功率管理

DD

3.3V I/O

商业外壳温度范围 0ºC-85ºC

工业外壳温度范围(200MHz)-40ºC-105ºC

260 引脚 PBGA 封装

存储器

4GB 统一寻址范围

308KB 片内存储器:

16KB 指令 SRAM/Cache

32KB 数据 SRAM/Cache

4KB 存放中间结果的 SRAM

256KB 全速、低延迟 SRAM

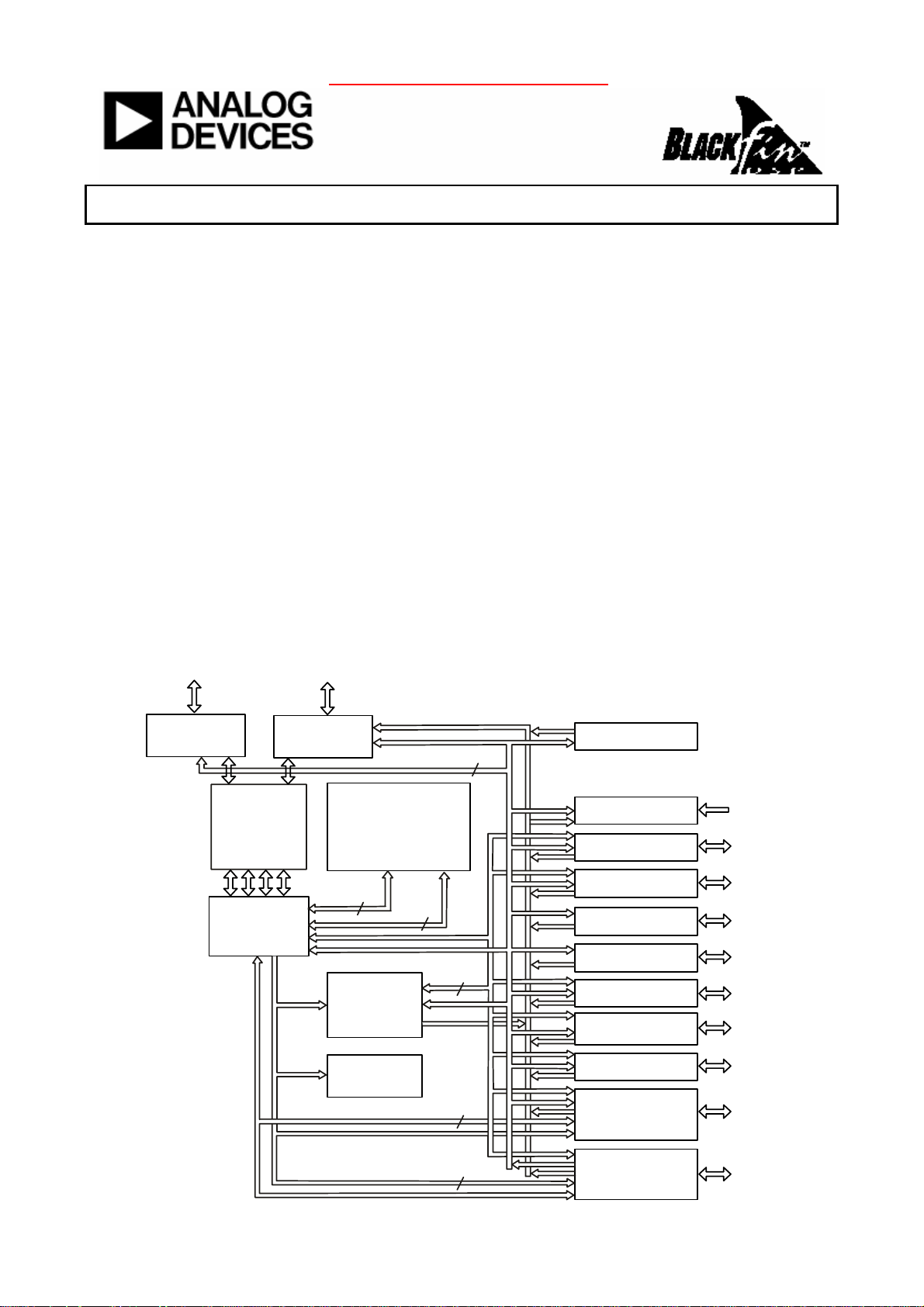

功能框图

存储器 DMA 控制器

存储器管理单元提供存储器保护

无硬件要求的外部存储控制器

支持同步 SDRAM

支持异步 SRAM、Flash、ROM

外设

32 位、33MHz、3.3V、版本 2.2 兼容的主/从 PCI 总线接口

集成的 USB 1.1 兼容的设备接口

2 个 UART,其中一个支持 IrDA

2 个 SPI 兼容接口

2 个全双工同步串行接口(SPORT)

4 个定时/计数器,其中 3 个支持 PWM

16 个双向可编程标志 I/O 引脚

“看门狗”定时器

实时时钟

1x-31x 倍频的片内 PLL

JTAG TEST AND

EMULATION

52K BYTES

L1 SRAM/CACHE

SYSTEM BUS

INTERFACE UNIT

BLACKFIN

CORE

INTERRUPT

CONTROLLER/

TIMER

256K BYTES L2 SRAM

64

DMA

CONTROLLER

BOOT ROM

32

32

32

32

32

WATCHDOG TIMER

REAL TIME CLOCK

UART PORT 0

IRDA®

UART PORT 1

TIMER0, TIMER1,

TIMER2

PROGRAMMABLE

FLAGS

USB INTERFACE

SERIAL PORTS (2)

SPI PORTS (2)

PCI BUS INTERFACE

EXTERNAL PORT

FLASH

SDRAM CONTROL

-1-

初步技术数据

ADSP-21535

说明

本数据手册提供的是关于 ADSP-21535 Blackfin DSP

的初步信息。

概述

ADSP-21535 是 Blackfin DSP 系列产品的成员之一,

由 AD 公司和 Intel 公司共同开发,采用了 Micro Signal

Architecture (MSA)。这种体系结构将艺术级的 dual-MAC

DSP 引擎,简洁的 RISC 式微处理器指令集的优点,以及

单指令多数据(SIMD)多媒体能力结合起来,形成了一套独

特的指令集结构。

通过集成业界领先和丰富的系统外设及存储器,

Blackfin DSP 系列成为下一代需要将 RISC 式编程、多媒体

支持和前沿的信号处理等集成在片内的 DSP 的选择平台。

便携式低功耗结构

同其它数字信号处理器相比,Blackfin DSP 系列具有

世界领先的低功耗和性能。Blackfin DSP 采用低功耗和低

电压的设计方法,具有动态功率管理的特点,即通过改变

工作电压和频率来降低总功耗。与仅改变工作频率相比,

既改变电压又改变频率能够使总功耗减少 1/3。对于便携式

应用来说,这相当于延长了电池的寿命。

系统集成

对下一代的数字通信和便携式的 Internat 应用来说,

ADSP-21535 是一个高度集成的片上系统解决方案。通过

将工业标准接口与高性能的数字信号处理内核相结合,用

户可以快速开发出节省成本的解决方案,而无需昂贵的外

部组件。ADSP-21535 系统外设包括 UARTs、SPIs、SPORTs、

定时器、实时时钟、可编程标志、看门狗定时器,以及用

于无缝外设扩展的 USB 和 PCI 总线。

ADSP-21535 外设

ADSP-21535 包含丰富的外设,它们通过不同的高速

宽带内总线与内核相连,使系统不但配置灵活而且有极好

的性能(见第 1 页的功能框图)。基本的外设用于一些通用

的功能,如 UARTs、带有 PWM(脉冲宽度调制器)和脉

冲测量能力的定时器、通用的 I/O 标志引脚、一个实时时

钟和一个看门狗定时器。这些外设满足了典型系统的各种

需求,并且通过它们增强了系统的扩充能力。除了这些通

用的外设,ADSP-21535 还包含有用于各种音频和 modem

CODEC 功能的高速串行端口,用于灵活地管理来自片内

外设和外部信源的中断事件处理器,以及可根据不同的应

用来配置系统的性能和功耗的功率管理控制功能。

在许多系统设计中,用户可以用很少或根本不用其它

逻辑电路就可以扩充片内的外设,这是由于 ADSP-21535

提供给用户的一些外设接口符合工业标准总线。这些接口

包括一个 32 位、33MHz、V2.2兼容的 PCI 总线、SPI 串行

扩展端口和一个 USB 设备端口。这使得在不同的应用中为

连接各种各样的外设而进行系统设计的复杂性已经降到最

小了。

除可编程标志引脚、实时时钟和定时器外,所有其它

的外设都有一个灵活的 DMA 结构和一个独立的 DMA 通

道。片内还有一个独立的存储器 DMA 通道,专用于在 DSP

的不同存储空间(包括外部的 SDRAM 和异步存储器)、内

部的 Level 1 和 Level 2 SRAM 和 PCI 存储空间之间的数据

传输。片内的多条 32 位总线能以 133MHz 的速度运行,这

样提供了足够的带宽以保证处理器内核能够跟得上片内的

和片外的外设。

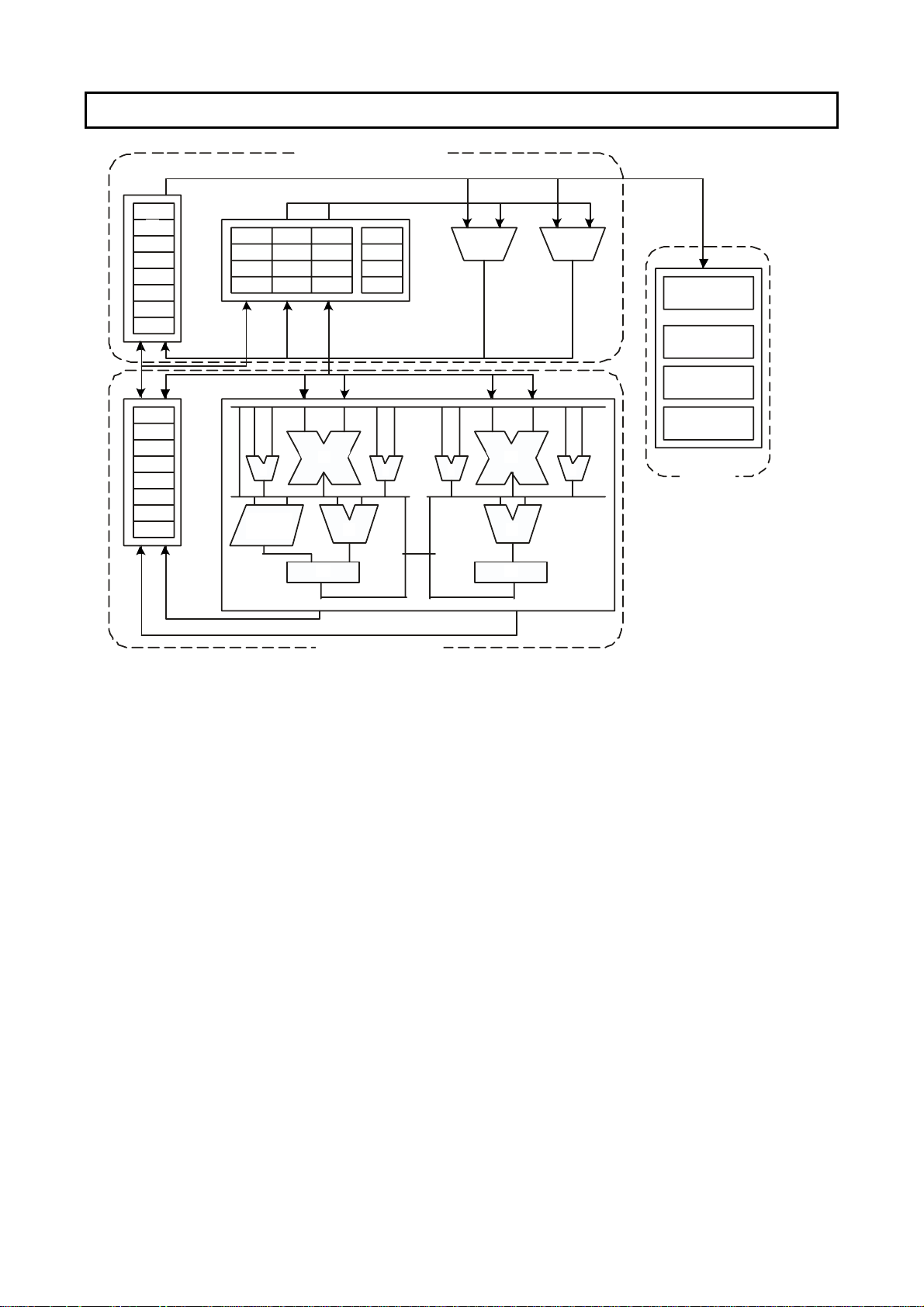

Blackfin DSP 内核

如图 1 所示,Blackfin DSP 内核包含 2 个乘法器/累加

器(MAC),2 个 40 位的 ALU,4 个视频 ALU 和 1 个移位

器。ALU 处理来自寄存器组的 8 位、16 位或者

每个时钟周期,每个 MAC 都完成一次 16 位乘 16 位的乘

法,并同累加器相加得到一个 40 位宽度、8 位扩展精度的

结果。

ALU 执行一套标准的算术和逻辑运算。片内有 2 个

ALU,因此可完成 16 或 32 位数据的运算,这样的灵活性

可以满足信号处理各种应用的需求。2 个 32 位输入寄存器

中的每一个都可以看作 2 个 16 位的寄存器,因此,每一个

ALU 都能够非常灵活地完成单独的 16 位算术运算。把寄

存器看作一对 16 位操作数,在一个指令周期可以完成双

16 位或单 32 位运算。进一步使用第二个 ALU,可以方便

地完成 4 个 16 位运算,从而加速每个周期的吞吐量。

功能强大的扩展 40 位移位器可以完成数据的移位、循

环移位、标准化、提取和存储等操作。

运算单元的数据来自于多端口的 16 乘 16 位或 8乘 32

位的寄存器组。

功能强大的程序控制器控制着指令执行的顺序,包括

取指和译码。程序控制器支持条件跳转、子程序调用和零

耗循环。一个循环缓冲器存储当前的指令,节省了指令存

储器的访问时间。

2 套数据地址产生器(DAG)为同时从存储器中存取双

操作数提供地址。它们共享一个寄存器组,这个寄存器组

由 4 套 32 位的索引、修改、长度和基址寄存器组成。另外

的 8 个 32 位寄存器提供用于指向变量和堆栈位置的指针。

Blackfin DSP 采用改进的哈佛结构和分级的存储器结

构。Level1(L1)存储器一般以全速运行,没有或只有很少的

延迟。Level2(L2)存储器同其它的片内或片外存储器一样,

需要花费多个处理器周期来访问。在 Ll 级,指令存储器只

存放指令。2 个数据存储器用于存放数据,专用的临时数

据存储器存放堆栈和局部变量。L2 级存储器采用统一的存

储空间,可以存放指令和数据。

此外,L1 指令存储器和 L1 数据存储器可以配置成静

态 RAM(SRAM)或者 CACHE。存储器管理单元(MMU)提

供存储器保护功能,对运行于内核上的独立的任务,可保

护系统寄存器免于意外的存取。

这种体系结构提供了 3 种运行模式:用户模式、管理

员模式和仿真模式。用户模式限制对某些系统资源的访问,

因此提供了一个受保护的软件环境;而管理员模式对系统

和内核资源的访问不受限制。

2002 年 6 月

32 位数据。

-2-

初步技术数据

2002 年 6 月 ADSP-21535

ADDRESSARITHMETIC UNIT

SP

FP

P5

P4

P3

P2

P1

P0

I3

L3

B3

I2

L2

B2

I1

L1

B1

I0

L0

B0

M3

M2

M1

M0

DAG0 DAG1

SEQUENCER

ALIGN

DECODE

R7

R6

R5

R4

R3

R2

R1

R0

BARREL

SHIFTER

16 16

88 8 8

40 40

A0 A1

DATA ARI THMETIC UNI T

图 1. Blackfin DSP 内核

Blackfin DSP 指令系统经过优化,16 位操作码组成了

最常用的指令,这使得编译后的代码密度非常高。复杂 DSP

指令采用 32 位操作码,体现了多功能指令的全部特征。

Blackfin DSP 支持有限的并发能力,即 1 个 32 位的指令可

以和 2 个 16 位指令并发执行,使编程人员在单指令周期中

使用尽可能多的内核资源。

Blackfin DSP 汇编语言使用易于编程和可读性强的代

数语法,而且在和 C 编译器的链接上进行了优化,给程序

员提供了快速有效的软件环境。

存储器结构

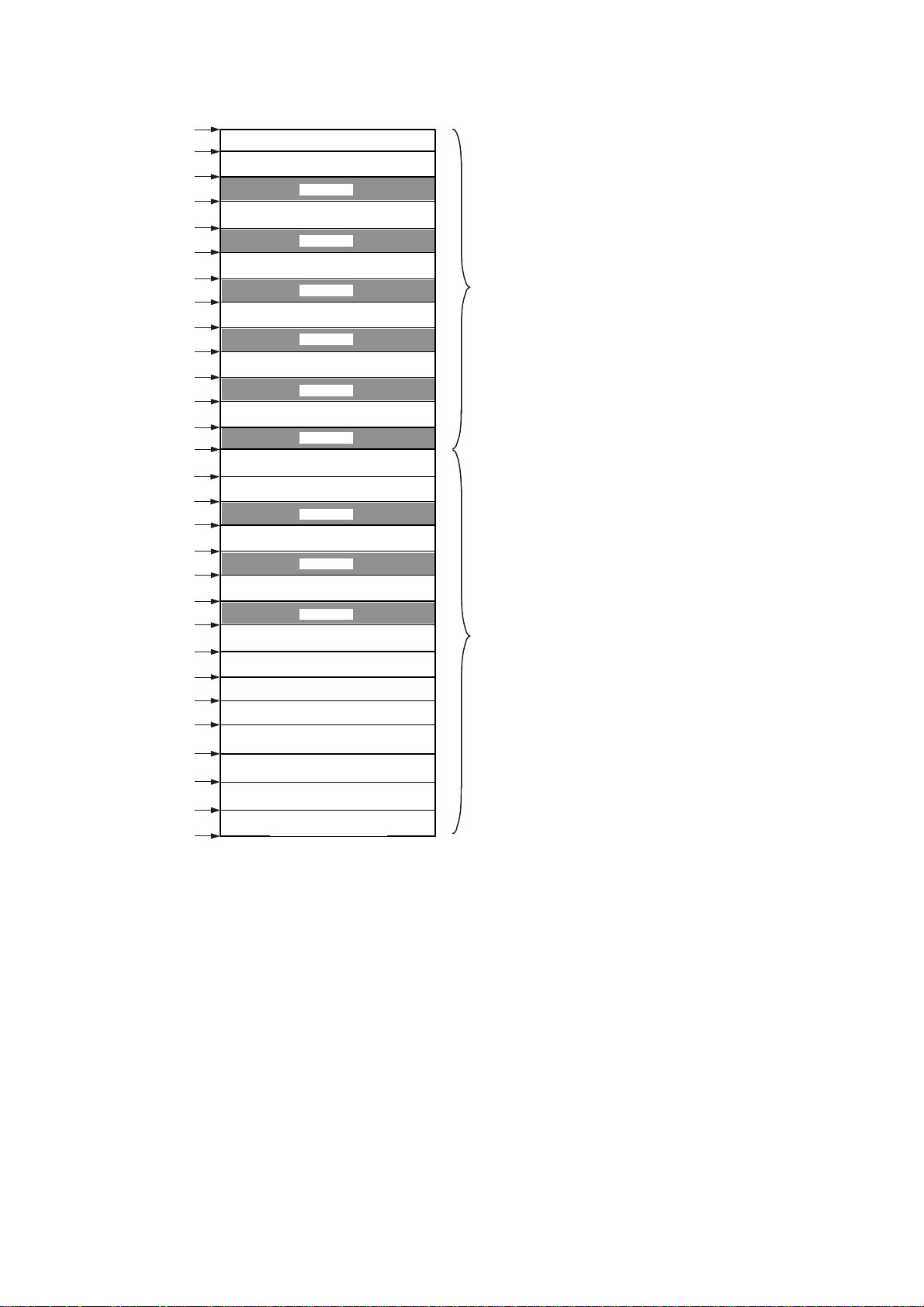

ADSP-21535 把存储器视为一个统一的 4GB 的地址空

间,使用 32 位地址。所有的资源,包括内部存储器、外部

存储器、PCI 地址空间和 I/O 控制寄存器,都占据公共地

址空间的各自独立的部分。此地址空间的各部分存储器按

分级结构排列,以提供高的性能价格比。一些非常快速、

低延迟的存储器(如 CACHE 或 SRAM)的位置非常接近

处理器,而更大的低成本、低性能的存储器远离处理器。

参见图 2。

L1存储器是 Blackfin DSP内核中性能最高的最重要的

存储器。L2 存储器性能稍低,提供额外的空间。最后,通

过外部总线接口单元(EBIU),片外存储器可以由 SDRAM、

FLASH 和 SRAM 进行扩展,可以访问超过 768MB 的物理

存储器。

LO OP BUFFER

CONTROL

UNIT

存储器的 DMA 控制器提供高带宽的数据传输能力。

它能够在内部的 L1/L2存储器和外部存储器空间(包括 PCI

存储空间)之间执行代码或数据的块传输。

内部(片内)存储器

ADSP-21535 有 4

块片内存储器,提供到内核的高带

宽的访问。

第 1 块是 16KB 的 L1 指令存储器,可配置成 4 路组联

合的 CACHE,也可配置成 SRAM,它以处理器的最快速

度访问。

第 2块片内存储器是由 2 块 16KB 组成的 L1 数据存储

器。每个 L1 数据存储器都能配置成单路或双路组联合的

CACHE 或者 SRAM,同样被内核以最快速度访问。

第 3 块存储器模块是一个 4KB 的临时数据 RAM,它

和 L1 存储器有相同的运行速度,但是只能作为数据 SRAM

(不能配置为 CACHE,也不能通过 DMA 访问)。

第 4 块片内存储器是 256KB 的高速 L2 SRAM,同样

以内核全带宽运行,和 L1 存储器相比,延迟稍长。L2 存

储器是一个统一的指令和数据存储器,能够根据系统设计

要求同时存放代码和数据。

Blackfin DSP 内核有一个专用的低延迟 64 位宽的数据

通道进入 L2 SRAM 存储器。例如,在内核 300MHz 频率

下,通过此接口的峰值数据传输率达到每秒 2.4GB。

-3-

初步技术数据

ADSP-21535

0XFFFF FFFF

0XFFE0 0000

0XFFC0 0000

0XFFB0 1000

0XFFB0 0000

0XFFA0 4000

0XFFA0 0000

0XFF90 4000

0XFF90 0000

0XFF80 4000

0XFF80 0000

0XF003 FFFF

0XF000 0000

0XEF00 0000

0XEEFF FFFC

0XEEFF FF00

0XEEFE FFFF

0XEEFE 0000

0XE7FF FFFF

0XE000 0000

0X2FFF FFFF

0X2C00 0000

0X2800 0000

0X2400 0000

0X2000 0000

0X1800 0000

0X1000 0000

0X0800 0000

0X0000 0000

1

THE ADDRESSES SHOWN FOR THE SDRAM BANKS REFLECT A FULLY

POPULATED SDRAM ARRAY WITH 512M BYTES OF MEMORY. IF ANY BANK

CONTAINS LESS THAN 128M BYTES OF MEMORY, THAT BANK WOULD

EXTEND ONLY TO THE LENGTH OF THE REAL MEMORY SYSTEMS, AND TH E

END ADDRESS WOULD BECOME THE START ADDRESS OF THE NEXT BANK.

THIS WOULD CONTINUE FOR ALL FOUR BANKS, WITH ANY REMAINING SPACE

BETWEEN THE END OF MEMORY BANK 3 AND THE BEGINNING OF ASYNC

MEMORY BANK 0, AT ADDRESS 0X2000 0000, TREATED AS RESERVED

ADDRESS SPACE.

CORE MMR REGISTERS (2M BYTE)

SYSTEM MMR REGISTERS(2M BYTE)

RESERVED

SCRATCHPAD SRAM (4K BYTE)

RESERVED

INSTRUCTION SRAM (16K BYTE)

RESERVED

DATA BANK B SRAM (16K BYTE)

RESERVED

DATA BANK A SRAM (16K BYTE)

RESERVED

L2 SRAM MEMORY ( 256K BYTE)

RESERVED

PCI CONFIG SPACE PORT (4 BYTE)

PCI CONFIG REGISTERS (64K BYTE)

RESERVED

PCI IO SPACE (64K BYTE)

RESERVED

PCI MEMORY SPACE (128M BYTE)

RESERVED

ASYNC MEMORY BANK 3 (64M BYTE)

ASYNC MEMORY BANK 2 (64M BYTE)

ASYNC MEMORY BANK 1 (64M BYTE)

ASYNC MEMORY BANK 0 (64M BYTE)

SDRAM MEMORY BANK 3

(16M BYTE - 128M BYTE)

SDRAM MEMORY BANK 2

(16M BYTE - 128M BYTE)

SDRAM MEMORY BANK 1

(16M BYTE - 128M BYTE)

SDRAM MEMORY BANK 0

(16M BYTE - 128M BYTE)

1

1

1

1

图 2. 内部/外部存储器映射

外部(片外)存储器

外部存储器通过外部总线接口单元(EBIU)进行访问。

此接口可与最多 4 个同步 DRAM(SDRAM),或与最多 4

个异步存储器设备(包括 FLASH、EPROM、ROM、SRAM

和存储器映射 I/O 设备)直接连接。

PC133 兼容的 SDRAM 控制器可以被编程并有与最多

4 个 bank 的 SDRAM 接口,每个 bank 的容量在 16MB 到

128MB 之间,提供给系统最多达 512MB 的 SDRAM 空间。

每个 bank 空间都是可独立编程的,无论大小及其位置是否

相同,相邻的 bank 地址都是连续的。这样就允许灵活地配

置和升级系统的存储器,并且允许内核把所有的 SDRAM

视为一个简单、连续的物理地址空间。

异步存储器的控制器也能够通过编程控制多达 4 个

bank 的时序参数灵活的各种异步存储设备。无论使用设备

的大小如何,每个 bank 的空间都占据 64MB。这样,只有

P

A

M

装满 4 个 64MB 的存储器时地址空间才能连续。

Y

R

O

PCI

M

E

M

PCI 总线定义了 3 个独立的地址空间,这些地址空间

L

A

N

通过 ADSP-21535 存储空间的窗口进行访问。它们分别是

R

E

T

PCI 存储器、PCI I/O 和 PCI 配置空间。

N

I

此外,PCI 接口可以有两种配置方法。其一,本处理

器用作系统中的控制

CPU,PCI 接口用作与它相接的 PCI

桥;其二,系统中另有一个 CPU 作为主机,本 ADSP-21535

用作 PCI 总线上的智能 I/O 设备。

当 ADSP-21535 作为系统控制器时,它通过映射窗口

来查看 PCI 地址空间,并且能初始化系统中的所有设备,

维持环境的拓扑映射。

PCI存储区域是出现在 PCI总线上的 4GB的存储空间,

可用来映射总线上的存储器 I/O 设备。ADSP-21535 使用存

储空间中的一个 128MB 窗口来查看 PCI 存储空间。同时使

P

A

用一个基地址寄存器,在 4GB PCI 存储空间中定位窗口的

M

Y

R

起始位置,而在处理器地址空间中这个窗口的地址保持不

O

M

E

变。

M

L

A

N

PCI I/O 区域也是 4GB 空间。然而,对于 I/O 映射地址,

R

E

T

大多数系统和 I/O 设备只使用这个空间的一个 64KB 子集。

X

E

ADSP-21535 用一个基地址寄存器把一个 64KB 的窗口实

现于这个空间,虽然可以定位于 PCI I/O 地址空间的任何

地方,但是这个窗口在处理器地址空间处于固定位置。

PCI 配置空间是一个有限的地址空间,用于系统列举

和初始化,在处理器与 PCI 设备之间这是一种低性能的通

信模式。ADSP-21535 提供一个单值窗口,在 PCI 配置空

间中的任何地址都可存取一个数据的值。这个窗口是固定

的,写操作时接收这个数据的地址和的值,而读操作时把

这个值返回到同一地址。

I/O 存储器空间

Blackfin DSP 没有定义独立的 I/O 空间。所有的资源都

被映射到统一的 32 位地址空间。片上 I/O 设备的控制寄存

器被映射到靠近 4GB

地址空间顶端的存储器映射寄存器

(MMR)地址范围内。这个地址空间又被划分为 2 个部分,

一部分包含完成所有内核功能的控制 MMR,另一部分包

含用于设置和控制内核以外的片内外设的寄存器。内核

MMR 仅在管理员模式下可被内核访问,对于片内外设和

通过 PCI 总线访问的外部设备,内核 MMR 都被保留起来。

系统 MMR 在管理员模式下可被内核访问,而且根据所需

的系统保护模式,系统 MMR 可对其它设备可见或保留。

引导

ADSP-21535 包括一个小的引导内核,用于配置的适

当的外设。如果 ADSP-21535 被配置为从引导 ROM 存储

2002 年 6 月

-4-

初步技术数据

2002 年 6 月 ADSP-21535

器引导,那么 DSP 从片内引导 ROM 开始执行。若需要更

多信息,请看第 12 页的引导模式。

事件处理

ADSP-21535 的事件控制器处理到达处理器的所有的

同步和异步事件。ADSP-21535 事件处理支持嵌套和优先

级。嵌套允许同时激活多个事件的服务程序。优先级保证

高优先级事件的响应可以抢占较低优先级事件的响应。控

制器支持 5 种类型的事件:

1. 仿真:仿真事件使处理器进入仿真模式,允许通过

JT AG接口命令和控制处理器。

2. 复位:此事件使处理器复位。

3. 不可屏蔽中断(NMI):NMI 事件可以由软件“看门狗”

定时器或者处理器的 NMI 输入信号产生的。NMI 事件

经常用作断电指示,有序地进行系统关闭工作。

4. 异常:异常是与程序执行同步发生的事件,即指令执

行完之前可能会产生异常。例如数据对准违规、未定

义指令等情况都将导致异常。

5. 中断:中断是与程序执行异步发生的事件,由定时器、

外设、输入引脚等引起。

每个事件都有一个相应的保存返回地址的寄存器和一

个相应的从事件返回指令。一个事件被触发后,处理器当

前状态被保存在管理员堆栈内。

ADSP-21535 事件控制器包括 2 个部分,内核事件控

制器(CEC)和系统中断控制器(SIC)。内核事件控制器和系

统中断控制器协同工作来确定优先级和控制所有系统事

件。从概念上讲,来自外设的中断进入到 SIC,然后被直

接发送到 CEC 的通用中断中处理。

内核事件控制器(CEC)

除专用中断和异常事件外,CEC还支持 9 个通用中断

(IVG15-7)。这些通用中断中,推荐将优先级最低的 2 个中

断(IVG15-14)留作软件中断,剩下的 7 个优先级中断分别

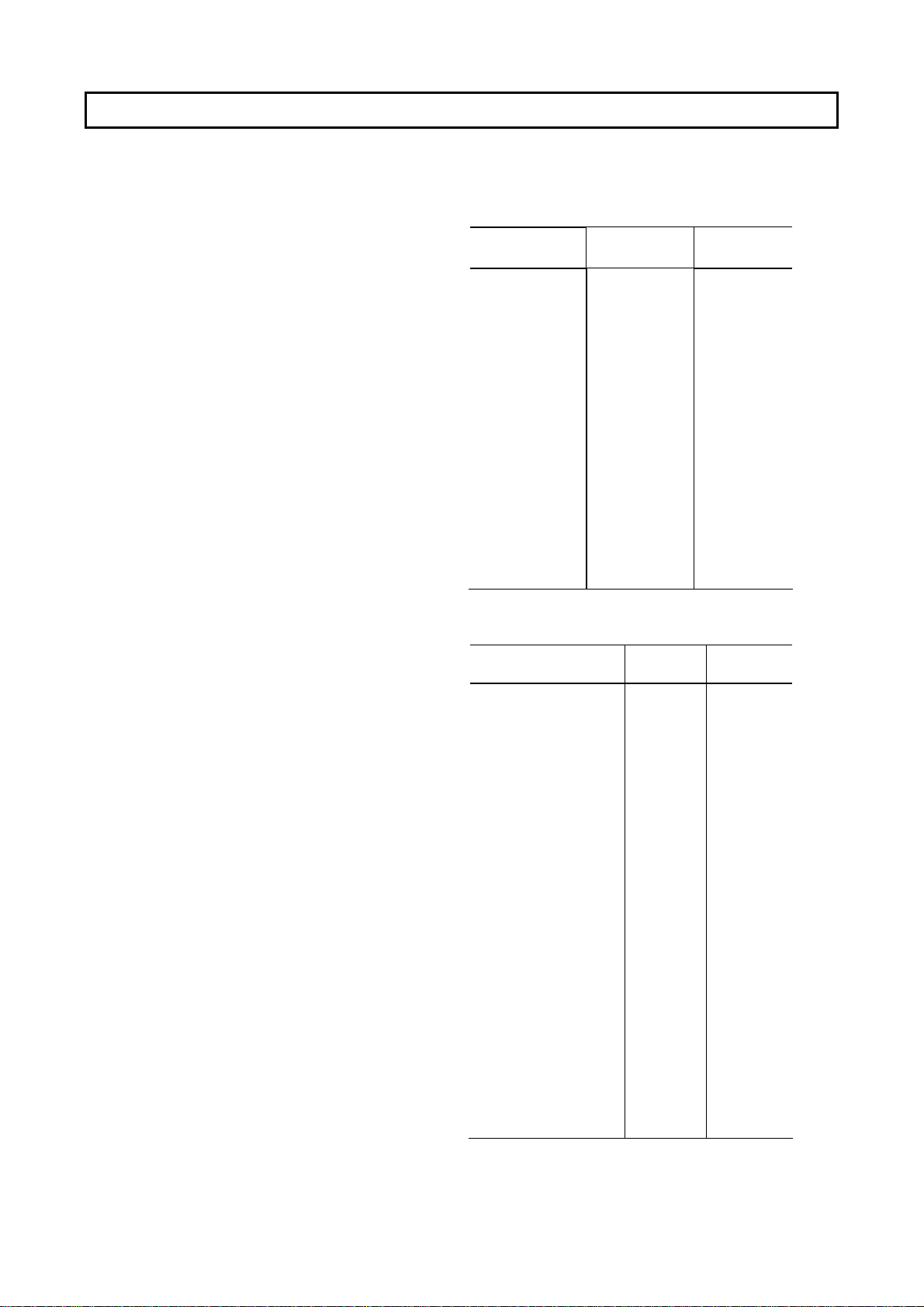

用于 ADSP-21535 的外设。表 1 描述了 CEC 的事件、事件

向量表(EVT)的名称及优先权。

系统中断控制器(SIC)

系统中断控制器为来自不同外设的中断源提供至 CEC

通用中断输入的映射和路由。尽管 ADSP-21535 提供了默

认的映射,用户仍可以通过改写中断设置寄存器(IAR)的

值,来改变中断事件的映射和优先权。表 2 描述了 SIC 的

中断源和至 CEC 的默认映射。

事件控制

ADSP-21535 为用户提供了非常灵活的机制来控制事

件的处理。在 CEC 中,有 3 个寄存器用于调整和控制事件。

如下所示,它们中的每个寄存器都是 16 位宽度,每一位都

代表一种特殊的事件分类:

表 1. 内核事件控制器(CEC)

优先权

(0 为最高)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

表 2. 系统中断控制器(SIC)

外设中断事件

实时时钟

保留

USB 2 IVG7

PCI 中断

SPORT 0 Rx DMA 4 IVG8

SPORT 0 Tx DMA 5 IVG8

SPORT 1 Rx DMA 6 IVG8

SPORT 1 Tx DMA 7 IVG8

SPI 0 DMA 8 IVG9

SPI 1 DMA 9 IVG9

UART 0 Rx 10 IVG10

UART 0 Tx 11 IVG10

UART 1 Rx 12 IVG10

UART 1 Tx 13 IVG10

定时器 0

定时器 1

定时器 2

GPIO 中断 A

GPIO 中断 B

存储器 DMA

软件看门狗定时器

保留

软件中断 1

软件中断 2

1. CEC 中断锁存寄存器(ILAT):ILAT 寄存器用于指示事

件已被锁存。处理器锁存事件后相应的位置 1,事件被

事件类 EVT 入口

仿真/测试

复位

不可屏蔽

异常

全局使能

硬件错误

内核定时器

通用中断 7

通用中断 8

通用中断 9

通用中断 10

通用中断 11

通用中断 12

通用中断 13

通用中断 14

通用中断 15

外设中断

ID

0 IVG7

1 -

3 IVG7

14 IVG11

15 IVG11

16 IVG11

17 IVG12

18 IVG12

19 IVG13

20 IVG13

26-21 27 IVG14

28 IVG15

EMU

RST

NMI

EVX

IVHW

IVTMR

IVG7

IVG8

IVG9

IVG10

IVG11

IVG12

IVG13

IVG14

IVG15

默认映射

-5-

初步技术数据

ADSP-21535

系统接受后该位清 0。该寄存器被控制器自动刷新,但

仅在管理员模式下可读。

2. CEC 中断屏蔽寄存器(IMASK):IMASK 寄存器控制发

生的事件是否被屏蔽。当 IMASK 寄存器的相应位置 1

时,事件不被屏蔽,发生后由系统处理。该位清 0 将

屏蔽事件,即使该事件已被锁存在 ILAT 寄存器中,

处理器也不会处理该事件。在管理员模式下,该寄存

器可以被读写。(注:通用中断可以通过 STI 和 CLI

指令设置为全局使能和禁止。)

3. CEC 中断等待寄存器(IPEND):IPEND 寄存器跟踪所

有嵌套的事件。IPEND 寄存器中的相应位置 1 表示事

件当前处于活动状态或嵌套在某一级。该寄存器被控

制器自动刷新,但是在管理员模式下才能读取。

SIC 使用 3 个 32 位中断控制和状态寄存器,来进一步

控制事件的处理。每个寄存器都包含与表 2 所示的每个外

设中断相对应的位。

1. SIC 中断屏蔽寄存器(SIC_IMASK):此寄存器控制每

个外设中断事件是否被屏蔽。当寄存器的相应位置 1

时,事件不被屏蔽,发生后由系统处理。该位清 0 将

屏蔽外设事件,使之不被处理。

2. SIC 中断状态寄存器(SIC_ISTAT):由于多个外设可以

映射到同一事件,该寄存器允许软件设置哪个外设事

件源触发该中断。相应位置 1 表明外设发出了中断,

为 0 则表明外设未发出事件。

3. SIC 中断唤醒使能寄存器(SIC_IWR):通过使能该寄存

器中的相应位,当事件发生而处理器处于掉电模式时,

每个外设都可唤醒处理器。(更多信息,请见第 9 页动

态功率管理。)

由于多个中断源可以映射到同一个通用中断,因此该

中断输入引脚上可能同时出现多个脉冲,这可以发生在对

一个已检测到的中断处理之前或之中。IPEND寄存器的内

容由 SIC 监控,以检查中断是否得到确认。

当一个中断上升沿被检测到(检测需要 2 个处理器时

钟周期),ILAT 寄存器的相应位被置 1。当 IPEND 寄存器

的任一位被置 1 时,该位被清 0。IPEND 的这位表示该事

件已进入处理器流水线。此时,CEC将在下一个事件到来

时识别其上升沿,并将这一事件排入队列。从通用中断的

上升沿到 IPEND 寄存器的输出置 1,最小的延迟为 3 个处

理器时钟周期;然而,由于内部的活动和处理器的模式不

同,延迟可能更长。

DMA 控制器

ADSP-21535 有多个独立的 DMA 控制器,能够以最小

的 DSP 内核开销完成自动的数据传输。DMA 传输可以发

生在 ADSP-21535 的内部存储器和任一有 DMA 能力的外

设之间。此外,DMA 传输也可以在任一有 DMA 能力的外

设和已连接到外部存储器接口(包括 SDRAM 控制器、异

步存储器控制器和 PCI 总线接口)的外部设备之间完成。

有 DMA 传输能力的外设包括 SPORT、SPI 端口、UART

和 USB 端口。每个独立的有 DMA 能力的外设至少有一个

专用 DMA 通道。PCI 的 DMA 传输由存储器的 DMA 通道

来完成。

为了描述每个 DMA 序列,DMA 控制器使用一套名为

描述子块的参数。当需要后继的 DMA 序列时,这些描述

子块被链接或串接起来,这样,一个 DMA 序列的完成能

够自动初始化并启动下一个序列。为能访问整个

ADSP-21535 的地址空间,原地址和目标地址描述子块采

用了全 32 位地址的基指针。

除专用外设的 DMA 通道以外,在 ADSP-21535 的不

同存储器之间有一个独立的存储器 DMA 通道。这使得任

意的存储器(包括片内 L2 存储器、外部 SDRAM、ROM、

SRAM 和 FLASH)与 PCI 地址空间之间的数据块传输成为

可能,几乎不需处理器干预。

外部存储器控制

ADSP-21535 的外部总线接口单元(EBIU),为各种工

业标准的存储器设备提供一个高性能、无需附加硬件的接

口。该控制器由两部分组成:第一部分是用于连接工业标

准的同步 DRAM 设备和 DIMM 的 SDRAM 控制器,第二

部分是用于与各种存储设备接口的异步存储控制器。

PC133 SDRAM 控制器

SDRAM 控制器能以

的工业标准 SDRAM 或 DIMM 接口。每个 bank 可以配置

为 16MB 至 128MB 的存储器,完全符合 PC133 SDRAM 标

准。

即使不同的 bank 使用不同大小的存储器,控制器也能

把所有 bank 管理成一个连续的地址空间,以便处理器将它

视为单一地址空间。这使初始配置的系统设计在将来便于

用类似的或不同的存储器进行升级。

一套可编程的时序参数用于配置 SDRAM bank,可以

支持更低速的存储设备。存储器 bank 可以配置成最高性能

和带宽的 32 位宽度或者低成本的 16 位宽度设备。

所有 4 个 bank 使用相同的 SDRAM 控制信号和独立的

bank 选通信号,为大多数的系统配置提供了一个完整的无

缝接口。

异步控制器

异步存储器控制器提供与多达 4 个 bank 的存储器或

I/O 设备的可配置的接口。每个 bank 都可以用不同的时序

参数独立编程,使之与各种存储设备(包括 SRAM、ROM

和 FLASH EPROM)及与标准存储器控制线接口的 I/O 设

备相连接。每个 bank 在处理器地址空间中都占据一个

64MB 的窗口,但如果每个 bank 容量不满 64MB 就不能组

成一个连续的地址空间。这些 bank 也可以配置为低成本和

功耗的 16 位总线宽度或高性能的 32 位总线宽度,以简化

与各种存储器和 I/O 设备的接口。

PCI 接口

ADSP-21535 提供一个 33MHz,3.3V,32 位,PCI 版

本 2.2 兼容的无需其它硬件的逻辑和硬件接口。该 PCI 接

f 的速度,与多达 4 个 bank

SCLK

2002 年 6 月

-6-

初步技术数据

2002 年 6 月 ADSP-21535

口设计为 3 伏的信号环境,在存储器内核和片上外设及外

部 PCI 总线之间提供了一个总线桥接功能。ADSP-21535

的 PCI 接口支持如下 2 种 PCI 功能:

仍然保持供电和时钟。RTC 提供了数个可编程的中断选择

(包括以时、分、秒计数中断,可编程跑表倒数计数中断,

或者已编程的警报时钟中断)。

1. 主机到 PCI 桥功能,从 PCI目标设备来看,ADSP-21535

的资源(处理器内核、片内和片外存储器、存储器 DMA

控制器)提供了必要的硬件部件,来仿真 PC 主机的

PCI 接口。

2. PCI 目标功能,基于 ADSP-21535 的智能外设可以容

易地与版本 2.2 兼容的 PCI 总线接口。

PCI 主机功能

用作 PCI 主机时,ADSP-21535 提供必要的 PCI 主机

(平台)功能,以支持和控制各种流行的 PCI I/O 设备(如

以太网控制器、总线桥等)。

注意,Blackfin DSP 体系结构中只定义了存储器空间

(没有 I/O 或配置地址空间)。PCI 的 3 个地址空间(存储

器、I/O 和配置空间)都被映射到 ADSP-21535 的统一的

32 位存储空间中。由于 PCI 存储器空间与 ADSP-21535 存

储器地址空间大小相同,所以使用一个加窗的方法,在

ADSP-21535地址空间中采用独立的窗口用来访问 3 个 PCI

地址空间。基地址寄存器用于定位这些窗口,以便能够访

问 PCI 地址空间中的任何区域,而它们在 ADSP-21535 处

理器地址空间内却保持固定位置。

对于欲查看 ADSP-21535 资源的 PCI 总线设备,提供

了几个映射寄存器,以使在 PCI 地址空间中查看这些资源

成为可能。ADSP-21535 的外部存储器空间、片内 L2 和某

些 I/O MMR 可以被选择使能,用作 PCI 总线设备的目标地

址空间,用于 PCI 存储器操作。

PCI 目标功能

用作为一个 PCI 目标设备时,PCI 主机处理器在列举

PCI 总线系统时,可配置 ADSP-21535 子系统。一经配置,

该子系统就成为一个智能的 I/O 设备。被配置为目标设备

后,PCI 控制器使用存储器 DMA 控制器来完成 PCI 主机

要求的 DMA 传输。

USB 设备

ADSP-21535 提供一个 USB1.1 兼容的设备类型接口,

支持直接与主机系统相连接。USB 内核接口提供一个灵活

的多达 8 个终端的可编程环境。每个终端都能支持所有

USB 数据传输类型(包括控制、批量、中断和等时)。每

个终端都为传输数据提供了存储器映射的缓冲器。

ADSP-21535 USB 端口有一个专用的用于最小化处理器轮

询开销的 DMA 控制器和仅当传输完成时才向 CPU 发出异

步请求的中断输入。

实时时钟

ADSP-21535 的实时时钟(RTC)提供了一个具有当前时

间、跑表和报警等功能的稳定的数字表。该 RTC 的时钟采

用 ADSP-21535 外部的 32.768KHz 晶振,RTC 有专用的电

源引脚,以使得当处理器其它部分处于低功耗状态时 RTC

32.768KHz 的输入时钟频率通过分频器成为 1Hz 信

号。具有计数功能的定时器包括 4 个计数器:一个 6 位的

秒计数器、一个 6 位的分计数器、一个 5 位的小时计数器

和一个 8 位的日计数器。

报警功能启动后,当定时器的输出和报警控制寄存器

中给定值相等时,报警功能会产生一个中断。报警分为 2

类:第一类是时间报警;第二类是日期加时间报警。

跑表功能从一个已编程的值起以 1 分钟分辨率倒数计

数。当跑表功能启动且计数器下溢出时,便产生中断。

同其它外设一样,RTC 能在产生任何中断之前把

ADSP-21535 处理器从低功耗状态唤醒。

用外部元件连接 RTC 的引脚 XTALI 和 XTALO,如 图

3 所示。

XTAL1

X1

C1 C2

SUGGESTEDCOMPONENTS:

ECLIPTEK EC38J (THROUGH-HOLE PACKAGE)

EPSON MC405 12 pF LOAD (SURFACE MOUNT PACKAGE)

C1 = 22 pF

C2 = 22 pF

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1.

CONTACT CRYSTAL MANUFACTURER FOR DETAILS. C1 AND C2

SPECIFICATIONS ASSUME BOARD TRACE CAPACITANCE OF 3 pF.

XTAL0

推荐元件:

ECLIPTEK EC38J(通孔封装)

EPSON MC-405 12.5pF LOAD(表贴封装)

C1=22pF

C2=22pF

注意:C1 与 C2 专用于推荐的晶振 X1

联系晶振制造商索取 C1 和 C2 的详细资料

规格假定板上线路容值为 3pF

图 3. RTC 的外部元件

“看门狗”定时器

ADSP-21535 包含一个 32 位定时器,可用于执行软件

的“看门狗”功能。软件“看门狗”可以提高系统的可靠

性,如果在软件复位前定时器溢出,软件“看门狗”通过

产生一个硬件复位、不可屏蔽中断(NMI)或通用中断来强迫

处理器进入一个已知状态。程序员初始化定时器计数值,

使能相应的中断,然后启动定时器。随后,软件必须在计

数器从给定值计数到 0 前重新装载计数器。这样防止系统

停留在未知状态。在未知状态下,软件由于外部噪声或者

软件错误等停止运行后,通常将定时器复位。

复位后,软件可以通过查询定时控制寄存器的一个状

态位来确定“看门狗”是否为硬件复位的来源,该位仅当

-7-

初步技术数据

ADSP-21535

“看门狗”产生复位时置 1。

定时器的时钟采用系统时钟(SCLK),以最高频率

f 运行。

SCLK

定时器

ADSP-21535 有 4 个可编程定时器。3 个通用定时器都

连有外部引脚,可以用作脉冲宽度调制器(PWM)或定 时

器输出,也可以用作定时器的输入时钟或测量外部事件的

脉冲宽度的输入。3 个通用定时器中的每一个都能够独立

地编程用作 PWM、内部或外部时钟驱动的定时或者脉冲

宽度计数器。

通用定时器单元可以与 UART 联合使用,进行串行通

道数据流的脉冲宽度的测量,提供自动的波特率检测功能。

通用定时器能够向处理器内核发出中断,为同步、处

理器时钟、或外部信号的计数值提供周期性事件。

除 3 个通用可编程定时器外,ADSP-21535 还提供了

第 4 个定时器。这个额外的定时器由内部处理器时钟

(CCLK)驱动,一般用作系统标记时钟,用以产生操作系统

的周期性中断。

串行口(SPORT)

ADSP-21535 提供 2 个完整的同步串行端口(SPORT0

和 SPORT1)来完成串行和多处理器的通信工作。SPORT

有以下特点:

1. 双向操作:每个 SPORT 都有独立的发送和接收引脚。

2. 缓冲的(8-deep)发送和接收端口:每个端口都有一

个数据寄存器,用以同其它 DSP 部件间进行双向数据

传输;多个移位寄存器用于数据寄存器内数据的移位。

3. 时钟:每个发送或接收端口或者使用外部串行时钟,

或者使用自己产生的频率范围为 (

f /2) Hz 的时钟。

到(

SCLK

f /131070) Hz

SCLK

缓冲区之后,每个发送和接收端口都能产生一个中断。

9. 多通道能力:每个 SPORT 支持 128 通道,并兼容

H.100、H.110、MVIP-90 和 HMVIP 标准。

串行外设接口(SPI)

ADSP-21535 有 2 个 SPI 兼容的端口,能够与多个

兼容的设备通信。

SPI 接口使用 3 个引脚传输数据:2 个数据引脚(主输

出-从输入 MOSIx 和主输入-从输出 MISOx)和 1 个时钟引

脚(串行时钟 SCKx);2 个 SPI 片选输入引脚(

可使其它 SPI 设备选择 DSP;14 个 SPI 片选输出引脚

(SPIxSEL7-1)使 DSP 能够选择其它 SPI 设备。这些 SPI

引脚也可以被重新配置为可编程标志引脚。通过这些引脚,

SPI 端口提供了全双工的同步串行接口,支持主从模式和

多主环境。

每个 SPI 的波特率和时钟的相位/极性都是可编程的

(见图 4),而且每个 SPI 都集成有一个 DMA 控制器,可

配置为发送或接收数据流。SPI 的 DMA 控制器在任意给定

时间,只能进行单向存取。

f

SPI

时钟率

=

SPIBAUD

×

2

SCLK

图 4. SPI 时钟率计算

在传输过程中,SPI 端口从 2 个串行数据引脚进行串

行数据移入和移出,同时完成发送和接收工作。串行时钟

引脚使 2 条串行数据引脚上的数据移位和采样同步。

在主模式下,DSP 采用如下的顺序来设置和初始化 SPI

传输:

1. 使能和配置 SPI 端口(数据大小和传输格式)。

2. 用 SPIxSELy 输出引脚(可重新配置为可编程标志引

脚),选择从目标 SPI。

2002 年 6 月

SPI

SPISSx

)

4. 字长:每个 SPORT 都支持 3 到 16 位长度的串行数据

字,以最高有效位在前或最低有效位在前的格式传送。

5. 帧:每个发送和接收端口在无论每个数据字有无帧同

步信号的情况下都能运行。帧同步信号能够从内部或

者外部产生,可以高有效或低有效,要求 2 个脉冲宽

度,可以前或后帧同步。

6. 硬件压扩:每个 SPORT 都能根据 ITU 推荐的 G.711

标准完成 A 律和 µ 律压扩。对 SPORT 的发送和/或接

收通道都能进行压扩,而且没有额外的延迟。

7. 单时钟周期开销的 DMA 操作:每个 SPORT 都可以自

动发送和接收多个缓冲区的数据信息。DSP 能够链接

或串接 SPORT 和存储器之间的多个 DMA 序列。串接

后的 DMA,通过建立串接的描述子块,能够进行动态

的分配和更新。

8. 中断:完成数据传输或者通过 DMA 传输完整个数据

3. 在 DSP 存储空间(仅在 DMA 模式下是可选择的)中,

定义一个或多个的 TCBs。

4. 使能 SPI DMA 引擎并指定传输方向。

5. 读写 SPI 端口接收或发送的缓冲数据(仅在非 DMA

模式下)。

SCKx引脚为同时移出 MOSIx 上的数据和移入 MISOx

上的数据产生编程时钟脉冲。仅在 DMA 模式下,SPI DMA

的字计数器从 1 变为 0 时,才停止传输。

在从模式下,DSP 采用如下的顺序来设置 SPI 端口接

收主 SPI 设备发送来的数据:

1. 使能和配置 SPI

(数据大小和传输格式)匹配。

2. 在 DSP 存储空间内定义和产生一个接收 TCB,在数据

传输结束时(仅在 DMA 模式下是可选的)时产出中

-8-

的从端口,与主 SPI 设备的运行参数

初步技术数据

D

2002 年 6 月 ADSP-21535

断。

3. 使能 SPI DMA 以接收数据(仅在 DMA 模式下是可选

的)。

4. 当接收到

引脚)的 SPI 片选信号后,在适当的 SPI SCKx 边沿,

开始接收来自主 SPI 设备的数据。

仅在 DMA 模式下,SPI DMA 的字计数器从 1 变为 0

时,才停止传输。此时若有下一个命令 TCB 在等待,DSP

将继续传输。

从模式的发送操作与此类似,但 DSP 指定的发送数据

的数据缓冲区、产生和放弃对发送 TCB 的控制、及开始填

充 SPI 端口的数据缓冲区都不相同。如果 SPI 控制器在数

据发送时没有准备好,它将发送一个“0”字。

UART 端口

ADSP-21535 提供 2 个全双工的通用异步接收/发送

(UART)端口(UART0 和 UART1),与 PC 标准的 UART 完

全兼容。UART 端口为其它外设或主机提供了一个简化的

UART 接口,支持全双工、有 DMA 能力的异步串行数据

传输。每个 UART 端口支持 5 至 8 个数据位、1 或 2 个停

止位和无校验/奇校验/偶校验位的支持。UART 端口支持以

下 2 种模式的操作:

1. PIO(编程 I/O):处理器通过读/写 I/O 映射的

或 UARX 寄存器,发送或接收数据。在发送和接收时,

数据都是双缓冲的。

2. DMA(直接存储器访问):DMA 控制器传输发送和接

收数据。这就减少了与存储器传输数据所需的中断的

数量和频率。每个 UART 都有 2 个专用的 DMA 通道,

一个用于发送,一个用于接收。这些 DMA 通道的优

先权低于大多数 DMA 通道,因为其使用率相对较低。

每个 UART 端口的波特率(见图 5)、串行数据格式、

错误代码的产生和状态、及中断均可编程:

1. 支持位速率每秒从(

位。

2. 支持每帧7至12位的数据格式。

3. 发送和接收操作都可被配置为能产生可屏蔽中断。

这里D=1 to 65536

同通用定时器联合使用可进行自动波特率检测。

UART0的功能被进一步扩展,能支持IrDA串行红外物

理层连接规范(SIR)协议

输入引脚(可重新配置为可编程标志

SPISSx

f /1048576)到(

SCLK

f

SCLK

UART

图 5. UART 时钟频率计算

时钟频率

=

×

16

UATX

f /16)

SCLK

可编程标志(PFX)

ADSP-21535 有 16 个双向的通用可编程 I/O 引脚

(PF15-0)。这些引脚还有专用的功能,用于时钟倍频选择、

SROM 引导模式和 SPI 端口操作。详见第 8 页的串行外设

接口(SPI)和第 11 页的时钟信号。每一个可编程引脚都

能通过操作下面的的标志控制寄存器、标志状态寄存器和

标志中断寄存器被独立控制:

1. 标志方向控制寄存器—规定每个独立的PFx引脚的方

向,用作输入或输出。

2. 标志控制和状态寄存器—ADSP-21535使用一种“写1

设置”和“写1清除”的机制控制每个标志的设置,而

不是常用的软件读-修改-写操作。这种机制能够在不

影响其它标志的情况下,一个处理器周期内完成对这

些标志进行任意组合地设置或清除。两个寄存器用于

此工作,一个用来设置标志,另一个用来清除标志。

通过软件读标志位状态寄存器,可以查看标志的状态。

3. 标志中断屏蔽寄存器—2 个标志中断屏蔽寄存器允许

每个独立的 PFx 引脚为处理器提供中断。与用于设置

和清除标志的 2 个标志控制寄存器类似,一个标志屏

蔽寄存器通过设置相应的位来使能中断功能,另一个

标志屏蔽寄存器通过清除相应的位来禁止中断功能。

PFx 引脚定义为输入时,能够设置为产生硬件中断;

定义为输出时,能够设置为产生软件中断。

4. 标志中断敏感寄存器—

规定每个 PFx 引脚是电平还是边沿敏感,如果是边沿

敏感,还规定是仅上升沿敏感,还是信号的上升沿和

下降沿都很敏感。一个寄存器选择敏感类型,另一个

寄存器选择边沿敏感的敏感边沿。

动态功率管理

ADSP-21535 提供 4 种运行模式,每种模式有不同的

性能/功耗特性。动态功率管理用适当的外部电源调节能力

来动态地改变处理器内核供电电压,进一步降低功耗。控

制每一个 ADSP-21535 外设的时钟也能降低功耗。表 3 概

要列出了每种模式下的功率设置。

全速运行模式—最高性能

在全速模式下,PLL 被使能,且不被旁路,因此提供

最高运行频率。这是获得最高性能的正常执行状态。处理

器内核和所有使能的外设都以全速运行。

活动运行模式—中等功率节省

在此模式下,PLL 被使能,但被旁路。输入时钟(CLKIN)

用于为处理器内核(CCLK)和外设(SCLK)产生时钟。由于

PLL 被旁路,CCLK 以 CLKIN 一半的频率运行,此时可节

省大量的功率。此模式下,PLL 倍频率可以通过设置 PLL

控制寄存器(PLL_CTL)中的 SSEL 域改变。

在活动运行模式下,系统支持对适当配置的 L1 存储器

进行 DMA 访问。

2 个标志中断敏感寄存器用于

-9-

初步技术数据

ADSP-21535

休眠运行模式-高功率节省

休眠运行模式通过关闭处理器内核(CCLK)的时钟

脉冲来降低功耗,然而PLL和系统时钟(SCLK)仍在运行。

任何中断,一般通过外部事件或RTC活动,将唤醒处理器。

此模式下任何中断到来时,处理器都会检查PLL控制寄存

器(PLL_CTL)中旁路位(BYPASS)的值。如果旁路位被关

闭,处理器将切换到全速运行模式。如果旁路位使能,处

理器将切换到活动运行模式。休眠模式时,系统DMA不支

持对L1存储器的访问。

深度休眠运行模式—最大功率节省

通过关闭处理器内核(CCLK)和所有同步系统

(SCLK)的时钟,深度休眠运行模式将获得最大的功率节

省。异步系统,如 RTC,仍将运行但将不能访问内部资源

或外部存储器。这种掉电模式只能通过复位中断(

或由 RTC 产生的异步中断退出。此模式下

处理器会检查 BYPASS 引脚的值。如果旁路被关闭,处理

器将切换到全速运行模式。如果旁路使能,处理器将切换

到活动运行模式。此模式下 RTC 产生的异步中断有效时,

处理器将切换到全速运行模式,而不管 BYPASS引脚的值。

DEEPSLEEP 引脚的输出在此模式下有效。

表 3. 运行模式功率设置

模式

全速 使能 否 使能 使能

活动 使能 是 使能 使能

休眠 使能 是或否 禁用 使能

深度休眠 禁用

PLL

RESET

有效时,

RESET

PLL 旁路 内核时钟(CCLK) 系统时钟(SCLK)

-

模式转换

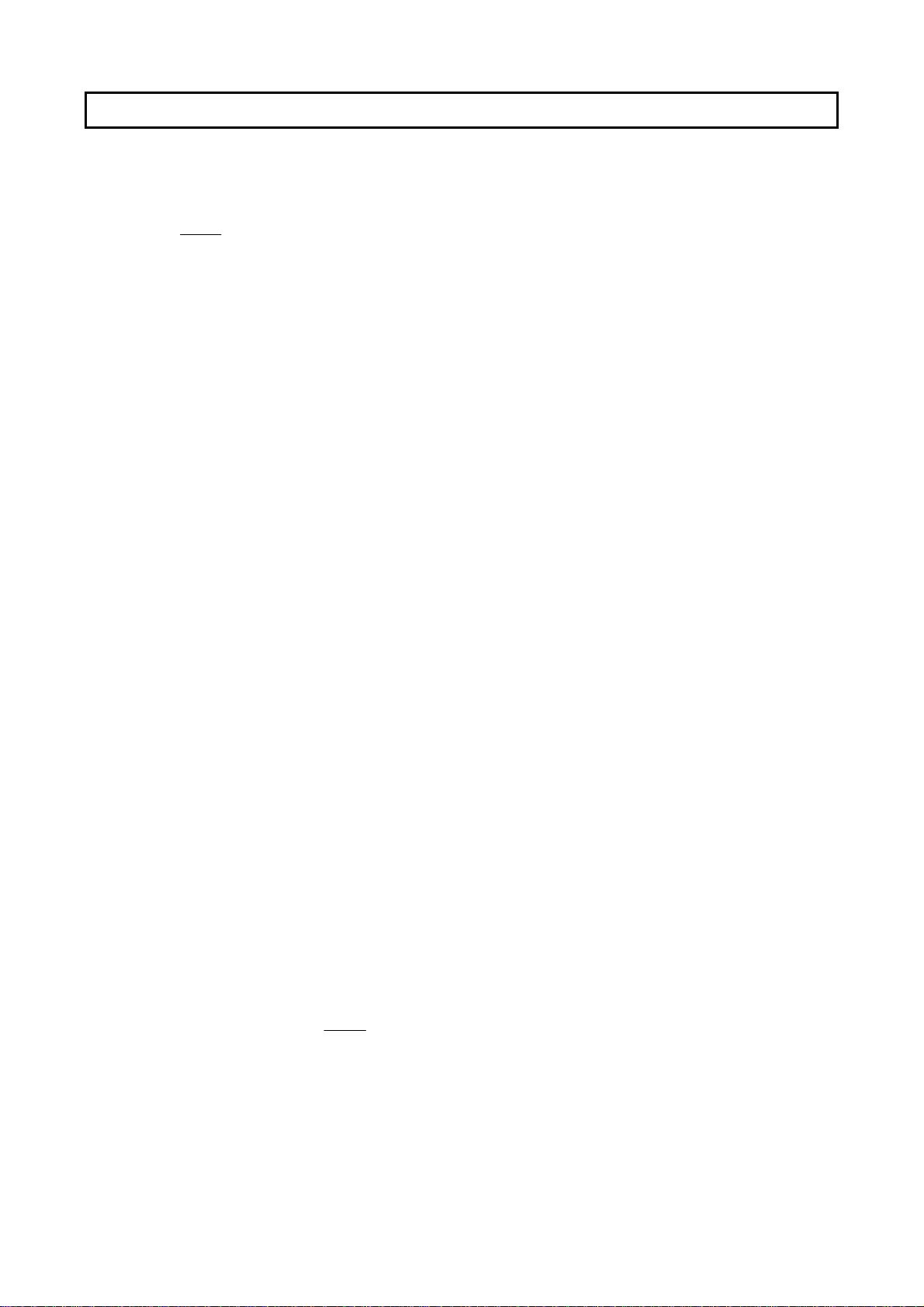

图 6 给出了可用的模式转换,这些模式转换或者通过

本节描述的中断事件完成,或通过对 PLLCTL 寄存器赋值

并执行 PLL 指令来完成。

此指令序列在中断禁用时将处理器切换到一种已知的

空闲状态。注意在此状态下所有的 DMA 活动都被禁用。

功率节省

如表 4 所示,ADSP-21535 支持 5 种不同的电源范围。

使用多个电源范围在与工业标准和惯例兼容的同时,可获

得最大的灵活性。通过将 ADSP-21535 内部逻辑隔离为独

立的电源,同 PLL、RTC、PCI 和其它 I/O 分离,处理器能

够使用动态功率管理,而不影响 PLL、RTC 或其它 I/O 设

)

备。

处理器的功耗主要是处理器时钟和工作电压的平方的

函数。例如,降低 25%的时钟频率就能降低 25%的功耗,

而降低 25%的电压可以降低 40%以上的功耗。此外,这些

功率节省是加性的,如果时钟频率和电源都降低,功耗将

会更显著地降低。

禁用 禁用

2002 年 6 月

-10-

初步技术数据

2002 年 6 月 ADSP-21535

SLEEP

STOPCK=1 &

PDWN=0

PDWN=1

WAK E UP &

BYPASS=1

BYPASS=0 & PLL_OFF=0 &

STOPCK=0 & PDWN=0

ACTIVE

MSEL= NEW & PLL _OF F=0 &

BYPASS=1

RTC_WAKEUP

BYPASS=1 & STOPCK =0 &

PDWN=0

P

D

E

E

P

E

E

L

S

HARDWARE

RESET

RESET

图6. 模式转换

表4. 电源范围

电源范围 VDD范围

V

所有内部逻辑(除PLL和RTC)

模拟PLL内部逻辑

RTC内部逻辑和晶体I/O

PCI I/O V

所有其它I/O

DDINT

V

DDPLL

V

DDRTC

DDPCIEXT

V

DDEXT

动态功率管理允许处理器的输入电压(V

钟频率(

f )动态可控。

CLK

如上所述,功耗节省可用下面的模型:

DDINT

)和时

举一个当频率和电压都降低时动态功率管理如何显著

节省功率的例子。如果频率从标称值降到50MHZ,同时电

压从标称值降到1.2V,此时,处理器的功耗只有标称频率

和电压下大约10%的功耗。

这里

功耗因子=

是标称内核时钟频率(300MHZ)

f

cclknom

是降低的内核时钟频率

f

cclkred

V

DDINTNOM

V

DDINTRED

VVff ×

DDINTNOMDDINTREDcclknomcclkred

是标称内部供给电压(1.5V)

是降低的内部供给电压

2

)/()/(

外设功率控制

ADSP-21535 通过动态管理每个外设的时钟输入提供

额外功率控制能力。下面列出的每个外设的时钟都可以通

过适当设置外设时钟使能寄存器 PLL_IOCK 的外设控制位

进行使能或禁止。外设时钟使能寄存器允许独立控制下列

每个外设:

1. PCI

2. EBIU 控制器

WA KEU P &

BYPASS=0

PDWN=1

MSEL=N EW & PLL_OFF=0 &

BYPASS=0

FULL-ON

STOPCK=1 &

PDWN=0

-11-

初步技术数据

ADSP-21535

3. 可编程标志

4. MEMDMA 控制器

5. SPORT 0

6. SPORT 1

7. SPI 0

8. SPI 1

9. UART 0

10.UART 1

11.TIMER 0,TIMER 1,TIMER 2

12.USB CLK

时钟信号

ADSP-21535 使用来自外部晶振的正弦输入,或经过

缓冲整形的时钟。

如果使用缓冲整形的时钟,此外部时钟应连到 DSP 的

CLKIN 引脚。在正常运行时,CLKIN 输入不能停止、改变、

或低于指定的频率。这个时钟信号应是 TTL 兼容信号。DSP

提供了用户编程的 1x 到 31x 的输入时钟倍频,即外部到内

部(DSP 内核)的时钟比率。MSEL6-0、BYPASS 和 DF

引脚决定复位时 PLL 倍频因子。运行时,倍频因子可用软

件控制。如图 7 所示的上拉和下拉电阻的组合设置了一个

6:1 的内核时钟比,即如果输入 25MHZ 的时钟将产生

150MHZ 的内核时钟。其它时钟倍频因子的设置,请参看

ADSP-21535 DSP Hardware Reference。

外设时钟通过 CLKOUT_SCLK0 引脚提供。

CLKIN CLKOUT

V

DD

V

DD

MSEL0

(PF0)

MSEL1

(PF1)

MSEL2

(PF2)

MSEL3

(PF3)

ADSP-21535

所有片上外设都以设定好的系统时钟(SCLK)速度运

行。此系统时钟频率可通过SSEL编程。运行时,通过写PLL

控制寄存器(PLL_CTL)中 的 SSEL域可以软件控制系统时

钟频率。SSEL的编程值规定了内核时钟频率(CCLK)和

系统时钟的分频比率。表5给出了系统时钟比率。

表5. 系统时钟比率

信号 比率

名称

分频 频率比率示例

(MHz)

CCLK/

SSEL-0 SCLK CCLK SCLK

00

01

10

11

2:1

2.5:1

3:1

4:1

266

275

300

300

系统时钟最高频率是

f 。注意分频比率必须选

SCLK

择,使之能将系统时钟频率限制到最大值

SSEL1-0值通过采样可编程标志输入引脚(PF9-8)来决定。

SSEL的值可以通过写PLL控制寄存器(PLL_CTL)来动态

改变,请参看ADSP-21535 DSP Hardware Reference。

引导模式

复位后,ADSP-21535有三种机制自动载入内部L2存储

器。第四种模式从外部存储器执行,绕过引导程序。

表6. 引导模式

BMODE2–0

000

001

010

011

100-111

说明

从外部16位存储器执行

(旁路引导ROM)

由8位Flash引导

由SPI0串行ROM引导(8位地址范

围)

由SPI0串行ROM引导(16位地址

范围)

保留

上电复位或软件复位后,处理器采样复位配置寄存器

的BMODE脚,执行以下引导模式:

2002 年 6 月

133

110

100

75

f 。复位后

SCLK

RESET

SOURCE

MSEL4

(PF4)

MSEL5

(PF5)

MSEL6

(PF6)

DF (PF7)

BYPASS

RESET

图7. 时钟比率示例

THE PULL-UP/PULLDOWN RESISTORS ON

THE MSEL, DF, AND

BYPASS PINS SELECT

THECORECLOCK

RATIO.

HERE, THE SELECTION

(6:1) AND 25MHz INPUT

CLOCK PRODUCE A

150MHz CORE CLOCK.

1. 从外部16位存储器执行—从16位紧缩地址0x2000000开

始执行,此模式跳过引导ROM。

2. 从外部8位Flash引导—位于引导ROM存储空间的8位

Flash引导程序通过异步存储器Bank0设置。所有的设置

参数都适合最慢的设备。(3个周期的保持时间;15个周

期的R/W访问时间;4个周期的建立时间。)

3. 从SPI串行EEPROM引导(8位寻址)—SPI0用PF10输出

引脚选择一个SPI EPROM设备,在地址0x00开始读数

据,将之存入L2存储器的起始部分。必须使用一个8位

寻址的SPI兼容EPROM。

-12-

初步技术数据

2002 年 6 月 ADSP-21535

4. 由SPI串行EEPROM引导(16位寻址)—SPI0用PF10输

出引脚选择一个SPI EPROM设备,从地址0x0000开始读

数据,将之存入L2存储器的起始部分。必须使用一个16

位寻址的SPI兼容EPROM。

无论上述何种引导模式,从存储器设备首先要读入一

个四个字节的值。这个值用来指定之后要被读到 L2 存储器

起始部分的字节数。一但这些字节装载完成,处理器跳到

L2 存储器空间起始位置并开始执行。

此外,软件代码可以设置复位配置寄存器,使软件复

位时跳过正常的引导顺序,处理器直接从 L2 存储空间的起

始部分开始执行。

为扩充上述引导模式,ADSP-21535提供了一个辅助的

软件加载器以加入其它的引导功能。辅助的加载器提供的

引导能力能够从16位Flash、快 速 Flash及可变的波特率等引

导。

指令集描述

Blackfin DSP 系列汇编语言指令集使用易于编程和可

读性强的代数语法,采用专门调整的灵活的高密度编码的

指令,这些指令被编译后只占用非常小的存储空间。指令

集还提供了体现 ADSP-21535 全部特点的多功能指令,以

使在一个时钟周期内能够使用尽可能多的处理器内核资

源。除许多微控制器上常见的功能外,指令集编译 C 和 C++

源代码时效率非常高。此外,指令集还支持用户(算法/

应用代码)和管理员(O/S 内核,设备驱动,调试器,ISRs)

两种运行模式,允许对 DSP 内核资源的多级访问。

汇编语言结合了处理器独特的体系结构,具有以下优

点:

1.无缝集成DSP/CPU特征,对8位和16位操作进行了优化。

2.超级流水线并发加载/

周期支持两个16位MAC或4个8位ALU+两个加载/存储

+两个指针更新。

3. 所有的寄存器、I/O、和存储器被映射成为统一4GB存

储空间,提供了一个简化编程模式。

4. 微控制器特征,如任意位和位域操作,插入和提取;

对8位、16位和32位数据类型上的整数操作;独立的用

户和内核堆栈指针。

5. 代码密度增强,包括混合的16和32位指令(无模式转

换和代码分离)。常用指令以16位编码。

开发工具

ADI 公司提供一套完整的 ADSP-21535 软硬件开发工

具,包括仿真器和 Visual DSP++

对 ADSP-21535 实现全仿真,还支持对其它 ADI 的 JTAG

DSPs 芯片的仿真。

利用 Vis ua l DS P+ +项目管理环境,程序员可以开发和

调试应用程序。这个环境包括一个基于代数语法的易于使

存储的改进哈佛体系结构,每个

TM

开发环境。仿真器能够

用的汇编器,一个归档器(库和库建立工具),一个链接器,

一个加载器,一个精确到时钟周期、指令级的模拟器,一

个 C/C++编译器和一个包括 DSP 和数学函数的 C/C++运行

库。这些工具的最重要特点是 C/C++代码的有效性。编译

器能有效地将 C/C++代码转换为 Blackfin DSP 的汇编代

码。Blackfin DSP 体系结构的特点也提高了 C/C++代码的

编译效率。

Visual DSP++调试器有许多重要的功能。绘图功能非

常灵活,增强了数据的可视化能力。这种用户数据的图形

化显示使程序员能快速确定一个算法的性能。随着算法复

杂性的增加,这个功能对与设计者开发进度的重要性也不

断提高。统计性能分析功能使程序员可以在不干扰处理器

运行的情况下访问处理器。这一 Vis ua l DS P+ +独特的功能

使程序员能以被动方式获取重要代码的执行尺度而不中断

程序的实时特性。从本质上讲,开发者可以快速而有效的

找出软件的瓶颈所在。通过使用性能分析工具,程序员可

以将注意力集中到影响程序性能的区域并采取相应纠正措

施。

用 Visual DSP++调试器调试 C/C++和汇编程序时,程

序员能够:

1. 查看混合的C/C++和汇编代码(交叉资源和目标信息)

2. 插入断点

3. 根据寄存器、存储器和堆栈设置条件断点

4. 跟踪指令执行

5. 对执行的程序进行线性或统计性能分析

6. 对存储器进行Fill、Dump和绘图操作

7. 执行源程序级调试

8. 创建用户调试窗口

Visual DSP++ IDE 能够让程序员定义和管理 DSP 软件

开发环境。它的对话框和属性页可以让程序员配置和管理

所有的开发工具,包括 Visual DSP++编辑器里的语法高亮

颜色。这些功能允许程序员:

1. 控制开发工具如何处理输入和产生输出

2. 维护与命令行操作一一对应的操作

Visual DSP++内核(VDK)提供进度和资源管理功能,

能够根据存储器地址和 DSP 程序时序约束进行裁剪,能使

工程师在开发新程序时提高编程效率,不用从头写起。

VDK 的特征包括线程,Critical 和 Unscheduled region,

Semaphores,事件和设备标志。VDK 同时也支持优先级的、

抢占的、协作和时间片的方法。此外,VDK 是可裁剪的。

如果应用程序不使用某种功能,可以将支持此功能的代码

从目标系统中清除。

因为 VDK 是一个库,开发者可以决定是否使用它。

VDK 已被集成到了 Visual DSP++开发环境中,也可以通过

标准的命令行工具使用。当使用 VDK 调试一个程序时,

开发环境帮助开发者解决许多易犯的错误同时帮助管理系

统资源,自动配置许多 VDK 基础目标的阶段,并可视化

-13-

初步技术数据

ADSP-21535

系统状态。

ADI公司的 DSP 仿真器使用 IEEE 1149.1 JTAG测试访

问端口,在仿真时监视和控制目标板上的 DSP 处理器。仿

真器提供全速仿真,允许查看和修改存储器、寄存器和处

理器堆栈。使用处理器 JTAG 接口可确保进行不干扰处理

器运行的在电路仿真——仿真器不会影响目标系统的装载

和定时。

除 ADI 公司提供软硬件开发工具外,第三方也提供了

许多支持 Blankfin DSP 系列的工具。硬件工具包括

ADSP-21535 EZ-KIT LITE

TM

评估/开发卡,软件工具包括

DSP 库、实时操作系统和方框图设计工具等。

设计仿真器兼容的 DSP 目标板

ADI公司的仿真器是每个 DSP 开发者都需要的测试和

调试软硬件系统的工具。ADSP-21535 提供了一个 IEEE

1149.1 JTAG 测试访问端口(TAP)。通过此 TAP,仿真器

能够访问 DSP 的内部,允许开发者装载代码,设置断点,

观察变量和存储器,检查寄存器。在发送数据和命令时 DSP

必须暂停,但当仿真器完成此次操作,DSP 系统就可以全

速运行,不影响系统的定时时序。

由图 8 可见,插座上有两组信号。一组是仿真用的标

准 JTAG 信号 TMS,TCK,TDI,TDO,TRST 和 EMU。

另一组是可选用的辅助 JTAG 信号 BTMS,BTCK,BTDI

和 BTRST,用于板级(边界扫描)的测试。

当仿真器不与目标板连接时,应如图 9 所示将跳线跨

接在 BTMS,BTCK,BTRST,和 BTDI 引脚上。这将使

JT AG 信号保持正确状态从而使 DSP 自由运行。当与仿真

器连接时,应移去所有的跳线。

JTAG仿真插头

图 10 详细给出了 14 个引脚目标端的 JTAG 仿真插头

的尺寸。图 11 所示的是应给目标板上插座的保留区域。保

留区域可使仿真插头合适地插在目标板上。

GND

KEY (NO PIN)

BTMS

12

34

56

2002 年 6 月

EMU

GND

TMS

要使用这些仿真器,用户目标板上必须设计有 AD 的

JTAG DSP 接口和仿真插座。

目标板仿真插座

仿真器与 AD 的 JTAG DSP的接口是一个 14 个引脚的

插座,如图 8 所示。用户必须在目标板上提供这个与仿真

器通讯的接口。接口由标准的双排 0.025″的方型直立引脚

组成, 0.1″× 0.1″的间隔,0.235″的最小直立高度。

引脚 3 这个重要的位置用来防止将仿真头插反,目标板上

的这个引脚必须切断。

而且,插座周围的空隙(长、宽和高)也必须考虑。

长和宽至少要分别留出 0.15″和 0.10″的空隙,高度的空

隙要能够插拔仿真器的插头。

GND

12

34

KEY (NO PIN)

56

BTMS

78

BTCK

910

BTRST

EMU

GND

TMS

TCK

TRST

BTCK

BTRST

BTDI

GND

78

910

9

11 12

13 14

TOP VIEW

TCK

TRST

TDI

TDO

图 9. 无局部边界扫描的 JTAG 目标板插座

目标板上地保留区域不应放任何元器件(芯片、电阻、

电容等)。图上尺寸以0.025"方型直立引脚的中心为参考

点。

0.64"

11 12

BTDI

13 14

GND

TDI

TDO

0.88"

0.24"

图10. JTAG插头尺寸

TOP VIEW

图 8. AD DSP JTAG 目标板插座

-14-

初步技术数据

2002 年 6 月 ADSP-21535

0.10"

0.15"

图11. JTAG插头保留区域

设计仿真电路信息

关于目标板的设计问题包括:单处理器连接,多处理

器扫描链,信号缓冲,信号端接,仿真器逻辑等,详见

EE-68:Analog Device JTAG Emulation Technical Refence

(请到 AD网站 WWW.ANALOG.COM使用“EE-68”搜索)。

此文档随仿真器的改进而更新。

补充信息

本数据手册为ADSP-21535的体系结构和功能提供了

一个总体概览。关于Blankfin DSP系列内核体系结构和指令

集的详细信息,请参考ADSP-21535 Hardware Reference和

Blackfin DSP Family Instruction Set Reference。

-15-

初步技术数据

ADSP-21535

引脚描述

ADSP-21535 的引脚定义列于表 7。下列引脚是异步的:

ARDY、 PF15–0、 USB_CLK、 NMI、 TRST、 RESET、

PCI_CLK、XT ALI、XTALO。

表 7. 引脚描述

引脚 类型 功能

ADDR25–2 O/T

DATA31–01

/SDQM3–0

ABE

ARDY

AOE

ARE

AWE

1

0-AMS3

1,2

I/O/T

O/T

O/T

I

O/T

O

O

CLKOUT/SCLK1 O

SCLK0 O

SCKE O/T

SA10 O/T

SRAS

SCAS

SWE

TMR02

TMR12

TMR22

PF15/

SPI1SEL7

PF14/

SPI0SEL7

PF13/

SPI1SEL6

PF12/

SPI0SEL6

PF11/

SPI1SEL5

PF10/

SPI0SEL5

PF9/

SPI1SEL4

PF8/

SPI0SEL4

PF7/

SPI1SEL3

PF6/

SPI0SEL3

PF5/

SPI1SEL2

PF4/

SPI0SEL2

0-SMS3

2

2

2

2

2

2

/SSEL13

/SSEL03

/DF3

/MSEL63

/MSEL53

/MSEL43

O/T

O/T

O/T

O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O

I/O

I/O

I/O

I/O

I/O

外部地址总线

外部数据总线

异步存储器字节使能,SDRAM 数据屏蔽

异步存储器片选

异步存储器确认信号

异步存储器输出使能

异步存储器读使能

异步存储器写使能

SDRAM 时钟输出引脚,频率和定时同 SCLK0,用于减小 SCLK0 上的容性

负载,连接到 SDRAM 的 CK 引脚

SDRAM 时钟输出引脚 0,系统时钟频率开关,连接到 SDRAM 的 CK 引脚

SDRAM 时钟使能引脚。连接到 SDRAM 的 CKE 引脚

SDRAM A10 引脚,SDRAM 接口利用它保持在主机总线请求时对 SDRAM

器件的控制,连接到 SDRAM 的 A10 引脚

SDRAM 行地址选通引脚。接 SDRAM 的 RAS 引脚

SDRAM 列地址选择引脚。接 SDRAM 的 CAS 引脚

SDRAM 写使能引脚。接 SDRAM 的 WE 或 W 缓冲引脚

配置 SDRAM 的外部存储器 bank 选择引脚,接 SDRAM 的片选引脚

定时器 0 引脚,PWMOUT 模式下用作输出,WIDTH_CNT 和 EXT_CLK 模

式下用作输入

定时器 1 引脚,PWMOUT 模式下用作输出,WIDTH_CNT 和 EXT_CLK 模

式下用作输入

定时器 2 引脚,PWMOUT 模式下用作输出,WIDTH_CNT 和 EXT_CLK 模

式下用作输入

可编程标志引脚,SPI 输出选择引脚

可编程标志引脚,SPI 输出选择引脚

可编程标志引脚,SPI 输出选择引脚

可编程标志引脚,SPI 输出选择引脚

可编程标志引脚,SPI 输出选择引脚

可编程标志引脚,SPI 输出选择引脚(SPI 引导时使用)

可编程标志引脚,SPI 输出选择引脚,复位时采样,以确定内核时钟与系统

时钟之比

可编程标志引脚,SPI 输出选择引脚,复位时采样,以确定内核时钟与系统

时钟之比

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL。DF=1 时将高频率输入时钟除以 2;DF=0 时,输入时钟直通到

PLL 鉴相器

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

下列符号出现在表 7 的“类型”一栏中:I = Input、O =

Output、T = Three-State、P = Power、G = Ground。

2002 年 6 月

-16-

初步技术数据

2002 年 6 月 ADSP-21535

PF3/

SPI1SEL1

PF2/

SPI0SEL1

PF1/

SPISS1

PF0/

SPISS0

RSLCK02

RFS02

DR03

TSCLK02

TFS02

DT0 O

RSCLK12

RFS12

DR13

TSCLK12

TFS12

DT1 O

MOSI02

MISO02

SCK04

MOSI12

MISO12

SCK14

RX03

TX0 O

RX13

TX1 O

USB_CLK4

XVER_DATA4

DPLS4

DMNS4

TXDPLS O

TXDMNS O

TXEN

SUSPEND O

NMI4

TCK2

TDO O/T

TDI2

TMS2

/MSEL33

/MSEL23

/MSEL13

/MSEL03

I/O

I/O

I/O

I/O

I/O/T

I/O/T

I

I/O/T

I/O/T

I/O/T

I/O/T

I

I/O/T

I/O/T

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

O

I

I

I

I

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

可编程标志引脚,SPI 输出选择引脚,硬件复位时采样以确定配置状态,用

于配置 PLL,选择 CK 对 CLKIN 的比率

SPORT0 串行时钟接收

SPORT0 帧同步接收

SPORT0 串行数据接收

SPORT0 串行时钟发送

SPORT0 帧同步发送

SPORT0 串行数据发送

SPORT1 串行时钟接收

SPORT1 帧同步接收

SPORT1 串行数据接收

SPORT1 串行时钟发送

SPORT1 帧同步发送

SPORT1 串行数据发送

SPI0 主输出从输入引脚,发送来自主设备的输出数据和接收去往从设备的输

入数据

SPI0 主输入从输出引脚,发送来自从设备的输出数据和接收去往主设备的输

入数据

SPI0 时钟线,主设备输出时钟,从设备输入时钟

SPI1 主输出从输入引脚,发送来自主设备的输出数据和接收去往从设备的输

入数据

SPI1 主输入从输出引脚,发送来自从设备的输出数据和接收去往主设备的输

入数据

SPI1 时钟线,主设备输出时钟,从设备输入时钟

UART0 接收

UART0 发送

UART1 接收

UART1 发送

USB 时钟

单端接收 USB 收发器到 USBD 模块的数据输出

差分 D+接收 USB 收发器到 USBD 模块的数据输出

差分 D-接收 USB 收发器到 USBD 模块的数据输出

从 USBD 模块到 USB 收发器发送 D+

从 USBD 模块到 USB 收发器发送 D从 USBD 模块到 USB 收发器发送使能

从 USBD 模块到 USB 收发器暂停模式使能输出,该信号也能被路由至系统

内部,以支持低功耗运行

不可屏蔽中断

JT AG时钟

JT AG串行数据输出

JT AG串行数据输入

测试模式选择

-17-

初步技术数据

ADSP-21535

4

TRST

RESET

CLKIN1 I

BYPASS I

DEEPSLEEP O

BMODE2-0 I

PCI_AD31-02

2

0-PCI_CBE3

2

PCI_FRAME

PCI_IRDY

PCI_TRDY

2

2

PCI_DEVSEL2

2

PCI_STOP

PCI_PERR

2

PCI_PAR2

2

PCI_REQ

PCI_SERR

PCI_RST

PCI_GNT

PCI_IDSEL

PCI_LOCK

2

2

2

2

2

PCI_CLK4

2

PCI_INTA

PCI_INTB

PCI_INTC

PCI_INTD

2

2

2

XTALI I

XTALO O

EMU

V

DDPLL

V

DDRTC

V

DDEXT

DDPCIEXT

DDINT

V

V

GND G

1

引脚有逻辑电平保持电路,防止输入内部浮置。

2

如果不用,引脚上拉。

3

如果不用,引脚上拉或下拉。

4

如果不用,引脚下拉。

I

I

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

I/O/T

O

I/O/T

I/O/T

I

I

I

I

I/O/T

I

I

I

O

P

P

P

P

P

JT AG复位

低电平至少 10 CLKIN 周期,硬件复位开始;上电复位最小脉冲宽度 40μS

时钟输入

专用模式引脚,可永久与

V

DD

或

连接,旁路片内 PLL

V

SS

表明 Blackfin DSP 内核处于深度休眠运行模式

专用模式引脚,可永久与

V

DD

或

连接,配置硬件或软件复位后的引导模

V

SS

式

PCI 地址和数据总线

PCI 字节使能

PCI 帧信号,表明 PCI 交易的开始和结束,被 PCI 启动方使用

PCI 启动方准备好信号

PCI 目标准备好信号

PCI 设备选择信号,PCI 交易目标用该信号的有效声明交易

PCI 停止信号

PCI 奇偶校验错误信号

PCI 奇偶校验信号

PCI 请求信号,用于请求使用 PCI 总线

PCI 系统错误信号,在系统板上要求上拉

PCI 复位信号

PCI 允许信号,用于允许访问 PCI 总线

PCI 初始化设备选择信号,PCI 配置传输期间选择不同的目标设备

PCI 锁定信号,用于锁定一个目标或整个 PCI 总线,供要锁定的主机用

PCI 时钟

PCI 总线的 PCI 中断 A 线;当 ADSP-21535 作为一个设备时,发出此中断信

号给系统处理器;当 ADSP-21535 作为系统处理器时监视此引脚

PCI 中断 B 线,当 ADSP-21535 作为系统处理器时监视此引脚

PCI 中断 C 线,当 ADSP-21535 作为系统处理器时监视此引脚

PCI 中断 D 线,当 ADSP-21535 作为系统处理器时监视此引脚

实时时钟晶振输入。

实时时钟晶振输出。

仿真器确认,漏极开路,必须连接到 ADSP-21535 仿真器与目标板相接的仿

真插座

PLL 电源(1.5V 标称)

实时时钟电源(3.3V 标称)

I/O(PCI 除外)电源(3.3V 标称)

PCI I/O 电源(3.3V 标称)

内部电源(1.5V 标称)

地

2002 年 6 月

-18-

初步技术数据

2002 年 6 月 ADSP-21535

ADSP-21535 —— 技术规格

推荐操作条件

参数1 K级参数

V

DDINT

V

DDEXT

V

DDPLL

V

DDRTC

V

DDPCIEXT

VIH

VIL

V

IHPCI

V

ILPCI

T

CASE

1

规格有改动不另行通知。

2

适用于输入和双向引脚,PCI 除外。

3

适用于PCI输入和双向引脚:PCI_AD31–0,

PCI_STOP

PCI_INTA

内部(内核)供电电压

外部(I/O)供电电压

PLL 电源电压

实时时钟电源电压

PCI I/O 电源电压

高电平输入电压2,@V

低电平输入电压2,@V

高电平输入电压

低电平输入电压3,@V

外壳工作温度

,

PCI_PERR

,

PCI_INTB, PCI_INTC

DDEXT

DDEXT

3

,@V

DDEXT

DDINT

, PCI_PAR,

,

=max

=min

=max

=min

PCI_SERR

PCI_INTD

电气特性

参数1

VOH

VOL

V

OHPCI

V

OLPCI

IIH

IIL

I

OZH

I

OZL

CIN

高电平输出电压

低电平输出电压

高电平输出电压

PCI

PCI

低电平输出电压

高电平输入电流

低电平输入电流

三态漏电流

三态漏电流

输入电容

2

2

3

3

4

4

5

5

6,7

1

规格有改动不另行通知

2

适用于输入和双向引脚,PCI 除外。

3

适用于PCI 输入和双向引脚:PCI_AD31–0,

PCI_DEVSEL,

4

用于输入引脚。

5

用于三态引脚。

6

用于所有信号引脚。

7

保证但未测试。

PCI_STOP

,

PCI_PERR

测试条件 最小

@ V

I

OH

@ V

I

OL

@ V

I

OH

@ V

I

OL

@ V

V

IN

@ V

V

IN

@ V

V

IN

@ V

V

IN

f = 1 MHz,

T

CASE

V

IN

, PCI_PAR,

DDEXT

= –0.5 mA

DDEXT

= 2.0 mA

DDEXT

= –0.5 mA

DDEXT

= 1.5mA

DDEXT

= VDD max

DDEXT

= 0 V

DDEXT

= V

DD

DDEXT

= 0 V

= 25°C,

= 2.5 V

最小 标称 最大 单位

0.86 1.5 1.575 V

2.5 3.3 3.45 V

1.425 1.5 1.575 V

2.60 3.3 3.45 V

3.15 3.3 3.45 V

2.0 V

-0.3 0.6 V

0.5V

V

DDPCIEXT

-0.5 0.3 V

0 85 ºC

,

0-PCI_CBE3

,

PCI_RST, PCI_GNT

PCI_FRAME

,

PCI_IRDY

,

PCI_IDSEL

。

=min,

2.4

=min,

=min,

0.9 V

DDPCIEXT

=min,

=max,

=max,

= max,

TBD µA

max

= max,

TBD µA

TBD pF

,

0-PCI_CBE3

PCI_FRAME

,

PCI_REQ

PCI_SERR

,

,

PCI_RST

PCI_IRDY

+0.5 V

DDEXT

+0.5 V

DDPCIEXT

V

DDPCIEXT

,

PCI_TRDY

,

PCI_LOCK

, PCI_DEVSEL,

最大

0.4

DDPCIEXT

0.1 V

TBD

TBD

,

PCI_TRDY

,

PCI_INTA

。

, PCI_CLK,

单位

V

V

V

V

µA

µA

,

-19-

初步技术数据

ADSP-21535

2002 年 6 月

绝对最大额定值

内部(内核)供电电压(V

外部(I/O)供电电压(V

DDINT

DDEXT

输入电压………………………-0.5V 到 V

输出电压漂移…………………-0.5V 到 V

负载电容………………………………………………200pF

内核时钟频率………………………………………300MHz

外设时钟频率(SCLK)………………………………133MHz

储存温度范围……………………………-65ºC 到 150ºC

管脚温度(5 秒)……………………………………185ºC

1

过载大于上述值时芯片会受到永久性损坏。以上只是过载额定值,芯片在超出

上述条件下的工作情况没有给出。在最大额定值条件下持续工作可能影响芯片

的可靠性。

ESD 灵敏度

注意

ESD(静电放电)灵敏器件。静电容易在人体或测试设备上积累高达 4000V 且放

电不宜察觉。虽然

ADSP-21535 有 ESD 保护电路,但当芯片受到高能静电放电时可能

会受到永久性破坏。因此,采用适当的

失。

)1……-0.3V 到 1.8V

)……-0.3V 到 4.0V

DDEXT

DDEXT

+0.5V

+0.5V

ESD 保护措施,以防止芯片性能降低和功能损

时序规格

表 8 和表 9 描述了 ADSP-21535 时钟的时序规格。注意选择 MSEL 和 SSEL 的比率使之不要超出最大内核时钟和系统

时钟工作频率,参照绝对最大额定值表。表

表 8. 内核与系统时钟需要

参数 说明 最大 最小 单位

t

CCLK1.5

t

CCLK1.4

t

CCLK1.3

t

CCLK1.2

t

CCLK1.1

t

CCLK1.0

t

CCLK0.9

f

CCLKNN

t

SCLK

f

SCLK

内核周期(V

内核周期(V

内核周期(V

内核周期(V

内核周期(V

内核周期(V

内核周期(V

内核时钟频率:t

=1.5V-5%)

DDINT

=1.4V-5%)

DDINT

=1.3V-5%)

DDINT

=1.2V-5%)

DDINT

=1.1V-5%)

DDINT

=1.0V-5%)

DDINT

=0.9V-5%)

DDINT

CCLKNN

系统时钟周期 最大(7.5 或 t

系统时钟频率

9 描述了锁相环工作条件。

3.3 TBD ns

TBD TBD ns

TBD TBD ns

TBD TBD ns

TBD TBD ns

TBD TBD ns

TBD TBD ns

1/t

CCLKNN

×2)

ns

1/t

Hz

CCLKNN

Hz

SCLK

表 9. 锁相环工作条件

参数 最小 一般 最大 单位

工作电压

抖动,上升沿到上升沿(每个输出)

抖动,下降沿到上升沿(每个输出)

偏斜,上升沿到上升沿(任意两个输出)

压控振荡器(VCO)频率

V

引入的抖动

DDPLL

1.425 1.5 1.575 V

120 ps

60 ps

120 ps

40 400 MHz

1 ps/mV

-20-

初步技术数据

2002 年 6 月 ADSP-21535

时钟和复位时序

表

10 和图 12 描述了时钟和复位操作。在上述绝对最大额定值的工作条件下,CLKIN 和时钟倍频器的选择必须使内

/外设时钟不超过 300/133MHz。

核

表 10. 时钟和复位时序

参数 说明 最小 最大 单位

时序要求

t

CKIN

t

CKINL

t

CKINH

t

WRST

t

PFD

t

MSD

t

MSS

t

MSH

CLKIN

CLKIN

CLKIN

RESET

从

从

RESET

RESET

周期

脉冲低电平

脉冲高电平

有效低电平脉宽

RESET

RESET

有效到 PFx I/O 终止的延迟

有效到 MSELx 和 DF 有效的延迟

1

1

2

失效前 MSELx/DF/BYPASS 建立稳定

失效后 MSELx/DF/BYPASS 保持稳定

3

4

5

开关特性

t

SCLKD

t

SCLK

1

用于旁路模式和非旁路模式.

2

用于上电顺序已完成情况。在上电时且当复位有效,处理器内部锁相环需要不超过 2000 个 CLKIN 周期,假定电源稳定

供给和

3

从这一点,MSELx 和 DF 值开始稳定到一个有效状态。

4

MSELx 和 DF 值可以从这一点变化,但值必须有效。

5

MSELx 和 DF 值必须从这时保持,直到持续时间结束。

6

下图按 t

从 CLKIN 到 CLKOUT 的延迟

6

周期

CLKOUT

CLKIN(不包括外部时钟振荡器的启动时间)。

和 t

CKIN

×2 比率显示,但比率可以有很多可编程的选择。参照 ADSP-21535 Hardware Reference。

SCLK

30.0 100.0 ns

10.0 ns

10.0 ns

11

×t

CKIN

ns

TBD ns

TBD ns

TBD ns

TBD ns

TBD TBD ns

7.5 ns

CLKIN

RESET

MSEL6–0

BYPASS

DF

CLKOUT

t

CKINL

t

CKIN

t

CKINH

t

PFD

t

MSD

t

WRST

t

MSS

t

SCLKD

图 12. 时钟和复位时序

t

MSH

t

SCLK

-21-

初步技术数据

−

−

ADSP-21535

2002 年 6 月

可编程标志周期时序

11 和图 13 描述了可编程标志操作。

表

表 11. 可编程标志周期时序

参数 说明

开关特性

t

t

DFO

HFO

相对于 SCLK 的标志输出延迟

SCLK

时序要求

t

HFI

SCLK

PF (OUTPUT)

PF (INPUT)

标志输出保持为异步

高后的标志输出维持

t

DFO

FLAG INPUT

t

HFIxS

FLAG

OUTPUT

Min Max

6 ns

TBD TBD ns

3 ns

t

DFO

图 13. 可编程标志周期时序

定时器 PWM_OUT 周期时序

12 和图 14 描述了定时器计数满操作。

表

输入信号在宽度捕获模式(width capture mode)下是异步的,且有一个 TBD MHz 的绝对最大输入频率。

表 12. 定时器 PWM_OUT 周期时序

参数 说明 最小 最大 单位

开关特性

t

HTO

1

t

的最小时间是一个周期,t

HTO

定时器脉宽输出

1

的最大时间为(

HTO

7.5

32

12

)个周期。

(

32

)个周期

12

ns

单位

SCLK

t

HTO

PWM_OUT

图 14. 定时器 PWM_OUT 周期时序

-22-

初步技术数据

2002 年 6 月 ADSP-21535

异步存储器写周期时序

表 13. 异步存储器写周期时序

参数 说明 最小 最大 单位

时序要求

t

SARDY

t

HARDY

t

DDAT

t

ENDAT

开关特性

tDO

tHO

1

输出引脚包括

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

2CYCLES

前 ARDY 建立

后 ARDY 保持

后 DATA31-0 关闭

后 DATA31-0 打开

后输出延迟

后输出保持

0-AMS3

SETUP

,

0-ABE3

PROGRAMMED READ

1

1

,ADDR25-2,DATA31-0,

ACCESS

EXTENDED

ACCESS 2 CYCLES

1CYCLE

5.5 ns

0.0 ns

6.0 ns

1.0 ns

6.0 ns

0.8 ns

AOE

HOLD

1CYCLE

,

AWE

。

AMSx

ABE1–0

ADDR19–1

DATA15–0

AWE

ARDY

t

DO

t

ENDAT

BE, ADDRESS

WRITE DATA

t

SARDY

t

HARDY

图 15. 异步存储器写周期时序

t

HO

t

DDAT

-23-

初步技术数据

ADSP-21535

2002 年 6 月

异步存储器读周期时序

表 14. 异步存储读周期时序

参数 说明 最小 最大 单位

时序要求

t

SDAT

t

HDAT

t

SARDY

t

HARDY

开关特性

tDO

tHO

1

输出引脚包括

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

0-AMS3

前 DATA31-0 建立

后 DATA31-0 保持

前 ARDY 建立

后 ARDY 保持

后输出延迟

后输出保持

,

1

1

,ADDR25-2,

0-ABE3

AOE

,

2.1 ns

0.8 ns

5.5 ns

0.0 ns

6.0 ns

0.8 ns

。

ARE

CLKOUT

AMSx

SETUP

2CYCLES

t

DO

PROGRAMMED READ ACCESS

4CYCLES

ACCESS EXTENDED

3CYCLES

HOLD

1CYCLE

t

HO

ABE1–0

ADDR19–1

DATA15–0

AOE

ARE

ARDY

t

DO

t

SARDY

图 16. 异步存储器读周期时序

BE, ADDRESS

t

HARDY

t

SDAT

READ

t

HARDY

t

HDAT

-24-

初步技术数据

2002 年 6 月 ADSP-21535

SDRAM 接口时序

表 15. SDRAM 接口时序

参数 说明 最小 最大 单位

时序要求

t

SSDAT

t

HSDAT

开关特性

t

SCLK

t

SCLKH

t

SCLKL

t

DCAD

t

HCAD

t

DSDAT

t

ENSDAT

1

命令引脚包括:

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

CLKOUT

SRAS

SCLK0/

SCLK1

DATA

(IN)

DATA

(OUT)

CMND

ADDR

(OUT)

前 DATA 建立

后 DATA 保持

周期

高电平宽度

低电平宽度

后命令、地址和数据延迟

后命令、地址和数据保持

后 DATA31-0 关闭

后 DATA31-0 使能

,

1

SCAS

,

,SDQM,

SWE

t

SSDAT

t

DCAD

t

ENSDAT

t

DCAD

NOTE 1: COMMAND = SRAS, SCAS, SWE, SDQM, SMS, SAIO, SCKE.

1

1

SMS

t

SCLK

t

图 17. SDRAM 接口时序

2.1 ns

0.8 ns

7.5 ns

TBD ns

TBD ns

6.0 ns

0.8 ns

6.0 ns

1.0 ns

,SA10,SCKE。

t

SCLKH

t

HSDAT

t

HCAD

SCLKL

t

t

HCAD

DSDAT

-25-

初步技术数据

ADSP-21535

2002 年 6 月

串行口

表 16. 串行口—外部时钟

参数 说明 最小 最大 单位

时序要求

t

SFSE

t

HFSE

t

SDRE

t

HDRE

t

SCLKW

t

SCLK

1

以采样边沿为参考

TCLK/RCLK

TCLK/RCLK

前接收数据建立

RCLK

后接收数据保持

RCLK

TCLK/RCLK

TCLK/RCLK

前 TFS/RFS 建立

后 TFS/RFS 保持

1

1

宽度

周期

1

1

3.0 ns

3.0 ns

3.0 ns

3.0 ns

4.5 ns

15.0 ns

表 17. 串行口—内部时钟

参数 说明 最小 最大 单位

时序要求

t

SFSI

t

HFSI

t

SDRI

t

HDRI

1

以采样边沿为参考

TCLK/RCLK

TCLK/RCLK

前接受数据建立

RCLK

后接受数据保持

RCLK

前 TFS/RFS 建立

后 TFS/RFS 保持

1

1

1

1

7.0 ns

2.0 ns

7.0 ns

4.0 ns

表 18. 串行口—内部或外部时钟

参数 说明 最小 最大 单位

开关特性

t

DFSE

t

HOFSE

1

以驱动边沿为参考

后 RFS 延迟(内部产生的 RFS)

RCLK

后 RFS 保持(内部产生的 RFS)

RCLK

1

1

10.0 ns

6.0 ns

表 19. 串行口—外部时钟

参数 说明 最小 最大 单位

开关特性

t

DFSE

t

HOFSE

t

DDTE

t

HDTE

1

以驱动边沿为参考

TCLK

后 TFS 延迟(内部产生的 TFS)

后 TFS 保持(内部产生的 TFS)

TCLK

TCLK

后发送数据延迟

TCLK

后发送数据保持

1

1

1

10.0 ns

6.0 ns

10.0 ns

6.0 ns

表 20. 串行口—内部时钟

参数 说明 最小 最大 单位

开关特性

t

DFS1

t

HOFS1

t

DDT1

t

HDT1

t

SCLKIW

1

以驱动边沿为参考

后 TFS 延迟(内部产生的 TFS)

TCLK

后 TFS 保持(内部产生的 TFS)

TCLK

后发送数据延迟

TCLK

TCLK

后发送数据保持

TCLK/RCLK

宽度

1

1

1

4.0 ns

0.0 ns

4.0 ns

0.0 ns

4.5 ns

-26-

初步技术数据

2002 年 6 月 ADSP-21535

表 21. 串行口—使能和三态

参数 说明 最小 最大 单位

开关特性

t

DTENE

t

DDTTE

t

DTENI

t

DDTTI

1

以驱动边沿为参考

DATA RECEIVE— INTERNAL CLOCK DATA RECEIVE— EXTERNAL CLOCK

DRIVE EDGE SAMPLE EDGE

RCLK

t

HOFSE

RFS

DR

外部 TCLK 的数据使能延迟

外部 TCLK 的数据关闭延迟

1

1

内部 TCLK 的数据使能延迟

内部 TCLK 的数据关闭延迟

t

SCLKIW

t

DFSE

NOTE: EITHER THE RISING EDGE OR FALLING EDGE OF RCLK, TCLK CAN BE USED AS THE ACTIVE SAMPLING EDGE.

t

t

SFSI

SDRI

1

t

HFSI

t

HDRI

5.0 ns

12.0 ns

2.0 ns

5.0 ns

RCLK

RFS

DR

DRIVE EDGE SAMPLE EDGE

t

HOFSE

t

DFSE

t

SCLKW

t

SFSE

t

SDRE

t

HFSE

t

HDRE

TCLK

TFS

DT

TCLK (EXT)

TFS(“LATE”, EXT)

DT

TCLK (INT)

TFS(“LATE”, INT)

DATA TRANSMIT — INTERNAL CLOCK

DRIVE EDGE SAMPLE EDGE

t

SCLKIW

TCLK

t

t

HOFSI

t

HDTI

DRIVE EDGE DRIVE EDGE

DRIVE EDGE

DFSI

NOTE: EITHER THE RISING EDGE OR FALLING EDGE OF RCLK OR T CLK CAN BE USED AS THE ACTIVE SAMPLING EDGE.

t

DDTEN

t

DDTIN

t

DDTI

t

SFSI

t

HFSI

TFS

DT

TCLK/RCLK

TCLK/RCLK

DRIVE EDGE SAMPLE EDGE

t

t

HDTE

DRIVE EDGE

DATA TRANSMIT — EXTERNAL CLOCK

t

SCLKW

t

HOFSE

t

DDTTE

DFSE

t

DDTTI

t

DDTE

t

SFSE

t

HFSE

DT

图 18. 串行口

-27-

初步技术数据

ADSP-21535

2002 年 6 月

串行外设接口(SPI)口—主时序

22 和图 19 描述 SPI 端口主操作。

表

表 22. 串行外设接口(SPI)口—主时序

参数 说明 最小 最大 单位

时序要求

t

SSPID

t

HSPID

开关特性

t

SDSCIM

t

SPICHM

t

SPICLM

t

SPICLK

t

HDSM

t

SPITDM

t

DDSPID

t

HDSPID

数据输入有效到 SCLK 边沿(数据输入建立)

采样边沿到数据输入无效

SCLK

SPIxSEL

低到第一个 SCLK 边沿(x=0 或 1)

串行时钟高电平时间

串行时钟低电平时间

串行时钟周期

最后 SCLK 边沿到

SPIxSEL

高(x=0 或 1)

序列传输延迟

边沿到数据输出有效(数据输出延迟)

SCLK

边沿到数据输出无效(数据输出保持)

SCLK

1.6 ns

1.6 ns

ns

2t

SCLK

2t

ns

SCLK

2t

ns

SCLK

4t

ns

SCLK

2t

ns

SCLK

2t

ns

SCLK

0 6 ns

0 5 ns

SPIXSEL

(OUTPUT)

(X = 0 OR 1)

SCK

(CPOL = 0)

(OUTPUT)

t

SDSCIM

t

SPICHMtSPICLM

t

SPICLK

t

HDSM

t

SPITDM

SCK

(CPOL = 1)

(OUTPUT)

MOSI

(OUTPUT)

CPHA=1

MISO

(INPUT)

MOSI

(OUTPUT)

CPHA=0

MISO

(INPUT)

t

SSPID

t

SPICLM

t

SSPID

MSB

VALID

t

SPICHM

t

HDSPID

VALID

t

SSPID

LSB

t

HDSPID

LSBMSB

MSB

VALID

t

HSPID

t

DDSPID

t

HSPID

t

DDSPID

图 19. 串行外设接口(SPI)端口—主时序

LSB

VALID

LSBMSB

t

HSPID

-28-

初步技术数据

2002 年 6 月 ADSP-21535

串行外设接口(SPI)端口—从时序

表

23 和图 20 描述了 SPI 端口从操作。

表 23. 串行外设接口(SPI)端口—从时序

参数 说明 最小 最大 单位

时序要求

t

SPICHS

t

SPICLS

t

SPICLK

t

HDS

t

SPITDS

t

SDSCI

t

SSPID

t

HSPID

开关特性

t

DSOE

t

DSDHI

t

DDSPID

t

HDSPID

SPISS

(INPUT)

串行时钟高电平时间

串行时钟低电平时间

串行时钟周期

最后一个 SPICLK 边沿到

SPISS

无效

序列传输延迟

有效到第一个 SCLK 边沿

SPISS

数据输入有效到 SCLK 边沿(数据输入建立)

采样边沿到数据输入无效

SCLK

有效到数据输出启动

SPISS

无效到数据高阻抗

SPISS

边沿到数据输出有效(数据输出延时)

SCLK

边沿到数据输出无效(数据输出保持)

SCLK

2t

ns

SCLK

2t

ns

SCLK

4t

ns

SCLK

2t

ns

SCLK

2t

ns

SCLK

2t

ns

SCLK

1.6 ns

1.6 ns

0 6 ns

0 6 ns

0 5 ns

0 5 ns

(CPOL = 0)

(INPUT)

SCK

(CPOL = 1)

(INPUT)

MISO

(OUTPUT)

CPHA=1

MOSI

(INPUT)

MISO

(OUTPUT)

CPHA=0

MOSI

(INPUT)

SCK

t

DSOE

t

DSOE

t

SDSCI

t

SSPID

t

SPICHStSPICLS

t

SPICLS

t

DDSPID

VALID

t

MSB

VALID

MSB

MSB

DDSPID

t

SPICHS

t

HSPID

t

HDSPID

t

SSPID

t

DDSPID

VALID

t

LSB

t

SSPID

图 20. 串行外设接口(SPI)端口—从时序

SPICLK

LSB

VALID

t

HSPID

LSB

t

DSDHI

t

HDS

t

DSDHI

LSBMSB

t

HSPID

t

SPITDS

-29-

初步技术数据

ADSP-21535

2002 年 6 月

通用串行收发器(UART)端口—接收和发送时序

21 描述了 UART 端口接收和发送操作,最大波特率是 SCLK/16。如图 21 所示,在产生内部 UART 中断和外部数

图

据操作之间有一些延迟。这些延迟同

SCLK

(SAMPLE

CLOCK)

RXD

RECEIVE

INTERNAL

UART RECEIVE

INTERRUPT

START

TXD

AS DATA

INTERNAL

WRITE N TO

BUFFER

TRANS MIT

UART TRANSMIT

INTERRUPT

UART 数据传输率相比可以忽略。

DATA(5–8)

DATA(5–8)

STOP

UART R ECEIVE BIT S ET BY DATA

STOP; CLEARED BY FIFO READ

STOP (1–2)

UART TRANSMIT B IT SET BY PROGRAM;

CLEARED B Y WRITE TO TRANSMIT

图 21. UART 端口—接收和发送时序

-30-

初步技术数据

2002 年 6 月 ADSP-21535

JTAG测试和仿真端口时序

表

24 和图 22 描述 JTAG 端口的操作。

表 24. JTAG 端口时序

参数 说明 最小 最大 单位

时序参数

t

TCK

t

STAP

t

HTAP

t

SSYS

t

HSYS

t

TRSTW

周期

TCK

高电平前 TDI 和 TMS 建立

TCK

高电平后 TDI 和 TMS 保持

TCK

低电平前系统输入建立

TCK

低电平后系统输入保持

TCK

TRST

脉冲宽度

2

1

1

开关特性

t

DTDO

t

DSYS

1

系统输入=DATA31-0, ADDR25-2, ARDY, TMR2-0, PF15-0, RSCLK0, RFS0, DR0, TSCLK0, TFS0, RSCLK1, RFS1, DR1,

低电平后 TDO 延迟

TCK

低电平后系统输出延迟

TCK

3

TSCLK1, TFS1,MOSI0, MISO0, SCK0, MOSI1, MISO1, SCK1, RX0, RX1, TSB_CLK, XVER_DATA, DPLS, DMNS, NMI,

, BYPASS, BMODE2-0,PCI_AD31-0,

RESET

,

SCAS

,

,

PCI_PERR

PCI_INTB, PCI_INTC

SWE

PCI_STOP

PCI_INTA

2

50 MHz max。

3

System Outputs=DATA31-0, ADDR25-2,

,

SRAS

, PCI_PAR,

,

,

PCI_SERR

,

PCI_INTD

/SDQM3-0,

ABE

,TMR2-0, PF15-0, RSCLK0, RFS0, TSCLK0, TFS0, DT0, RSCLK1, RFS1, TSCLK1, TFS1,

0-SMS3

PCI_RST

。

AOE

DT1, MOSI0, MISO0, SCK0, MOSI1, MISO1, SCK1,TX0, TX1, TXDPLS, TXDMNS,

PCI_AD31-0,

PCI_PAR,

PCI_REQ

,

,

0-PCI_CBE3

PCI_SERR

PCI_FRAME, PCI_IRDY

,

PCI_RST

,

PCI_INTA

t

TCK

,

20 ns

4 ns

4 ns

4 ns

5 ns

4 ns

4 ns

0 5 ns

,

0-PCI_CBE3

PCI_FRAME

,

ARE

,

PCI_TRDY

。

EMU

,

PCI_GNT

,

PCI_IRDY

,

PCI_IDSEL

,

, CLKOUT/SCLK1, SCLK0, SCKE, SA10,

AWE

,PCI_DEVSEL,

,

PCI_TRDY

,

PCI_LOCK

, SUSPEND, DEEPSLEEP,

TXEN

PCI_STOP

, PCI_DEVSEL,

, PCI_CLK,

,

PCI_PERR

,

TCK

TMS

TDI

TDO

SYSTEM

INPUTS

SYSTEM

OUTPUTS

功耗

总功耗有两部分,一部分是内部电路(

t

DTDO

t

t

STAP

DSYS

t

HTAP

图 22. JTAG 端口时序

P

)的功耗,

INT

t

SSYS

t

HSYS

另一部分是内部输出驱动(

P

)的开关功耗。表 25 给出

EXT

了内部电路的功耗。内部功耗取决于内部指令执行序列和

-31-

初步技术数据

ADSP-21535

2002 年 6 月

相关的数据操作。表 26 列出了取得表 25 给出值的条件。

表 25. 内部功耗

参数 测试条件 典型值(V

I

t

DDHIGH

I

t

DDTYP

I

t

DDLOW

I

t

DDSYS

I

t

DDEFR

I

DDACTIVE

I

DDSLEEP

I

DDDEEPSLEEP

1

25ºC TBD TBD mA

25ºC TBD TBD mA

25ºC TBD TBD mA

典型 IDD数据指定为标称的 V

,25ºC TBD TBD mA

CCLKMIN

,25ºC TBD TBD mA

CCLKMIN

,25ºC TBD TBD mA

CCLKMIN

,25ºC TBD TBD mA

CCLKMIN

,25ºC TBD TBD mA

CCLKMIN

和典型处理参数。最大 IDD在典型值的 TBD%范围内。

DDINT

=1.5V)1 典型值(V

DDINT

=1.0V)1 单位

DDINT

表 26. 内部功耗条件

参数 模式

1

I

DDHIGH

1

I

DDTYP

1

I

DDLOW

2

I

DDSYS

3

I

DDEFR

I

DDACTIVE

I

DDSLEEP

I

DDDEEPSLEEP

1

TBD 指令混合。

2

3

每周期 TBD 指令混合和系统 DMA。

执行增强全速率(EFR)GSM 算法,从 L1/L2 存储器和 Cache 取指令和数据。

全速 使能 使能 使能

全速 使能 使能 使能

全速 使能 使能 使能

全速 使能 使能 使能

全速 使能 使能 使能 算法有关

活动 使能/旁路 使能 使能

休眠 使能 关闭 使能

深度休眠 关闭 关闭 关闭

PLL CCLK SCLK

总功耗的外部元件部分由输出引脚的开关引起,其大

小取决于

1

. 每周期开关的输出引脚个数(O)

2

. 最大开关频率(f)

3

. 负载电容(C)

4

. 电压摆动(V

)

DDEXT

外部元件功耗用下式计算

= O × C × V

P

EXT

DD

× f

频率 f 包括驱动负载变为高电平之后又回到低电平。

DATA31-0 引脚处于 SDRAM 突发模式下能以 1/(2

例如:

×t

)的最大速率驱动高电平和低电平。

SCLK

注意,引起最坏 P

P

不同。最大

全部

0 时。同时注意,对于一个应用实例,100%,甚至 50%

不能发生在所有的输出引脚由全部 1 变为

INT

的条件和引起最坏 P

EXT

的输出同时开关是不常见的。

环境条件

ADSP-21535 提供 260 引脚的 PBGA 封装。

ADSP-21535

不超出范围,可以使用气流源。T

T

=外壳温度(在封装顶面测量)

CASE

功耗 W(此值取决于具体应用)

PD=

规定了外壳温度(T

= T

T

CASE

AMB

CASE

用下式计算

CASE

+( PD × θ

单位

TBD

TBD

TBD

TBD

TBD

TBD

TBD

的的条件

INT

)。为保证 T

)

CA

CASE

这种情况下的典型功耗应当用加上一个典型内部功耗

的公式计算。

P

TOTAL

= P

EXT

+ ( I

DD

× V

DDINT

)

-32-

初步技术数据

2002 年 6 月 ADSP-21535

表 27 是气流每分钟线性英尺的 3 个例子。

表 27. 气流

线性 Ft/Min

θ

(ºC/W)

CA

ADSP-21535 260 –Lead PBGA 的引脚

28 按信号名称列出了 PBGA 的引脚,表 29 给出了

表

PBGA 引脚的按序号排列。

表 28. 260 引脚 PBGA 排列表(按字母顺序排列)

信号 引脚 #

/SDQM0

ABE0

/SDQM1

ABE1

/SDQM2

ABE2

/SDQM3

ABE3

ADDR2 A06

ADDR3 B06

ADDR4 D06

ADDR5 C06

ADDR6 A05

ADDR7 B05

ADDR8 A04

ADDR9 C05

ADDR10 D05

ADDR11 B04

ADDR12 A01

ADDR13 C04

ADDR14 D04

ADDR15 A03

ADDR16 B03

ADDR17 A02

ADDR18 C03

ADDR19 D03

ADDR20 B02

ADDR21 C02

ADDR22 E03

ADDR23 C01

ADDR24 F03

ADDR25 D02

AMS0

AMS1

AMS2

AMS3

AOE

ARDY R01

ARE

AWE

BMODE0 B14

BMODE1 A14

BMODE2 B13

BYPASS C12

CLKIN1 D09

CLKOUT/SCLK1 H01

DATA0 N02

0 200 400

TBD TBD TBD

E02

B01

G03

H07

F02

D01

H03

G02

E01

F01

G01

N02

DATA1 M03

DATA2 T01

DATA3 P02

DATA4 N03

DATA5 R02

DATA6 P03

DATA7 U01

DATA8 U02

DATA9 T02

DATA10 V02

DATA11 V03

DATA12 R04

DATA13 U03

DATA14 T03

DATA15 T04

DATA16 U04

DATA17 V04

DATA18 V05

DATA19 R05

DATA20 T05

DATA21 U05

DATA22 V06

DATA23 R06

DATA24 U06

DATA25 T06

DATA26 V07

DATA27 V08

DATA28 U07

DATA29 R07

DATA30 T07

DATA31 V09

DMNS D08

DPLS C09

DR0 V14

DR1 U15

DT0 R14

DT1 V17

EMU

GND C13

GND H02

GND H08

GND H10

GND H11

GND J07

GND J08

GND J09

GND J10

GND J11

GND J12

GND K02

GND K07

GND K08

GND K09

GND K10

GND K11

GND K12

GND L07

GND L08

GND L09

A13

-33-

初步技术数据

ADSP-21535

GND L10

GND L11

GND M07

GND M09

GND M10

MISO0 T16

MISO1 U18

MOSI0 U16

MOSI1 T17

N/C A18

N/C R03

N/C V01

N/C V18

NMI B11

PCI_AD0 E17

PCI_AD1 E18

PCI_AD2 G16

PCI_AD3 F17

PCI_AD4 F18

PCI_AD5 G18

PCI_AD6 G17

PCI_AD7 H18

PCI_AD8 J18

PCI_AD9 H17

PCI_AD10 K18

PCI_AD11 H16

PCI_AD12 L18

PCI_AD13 J17

PCI_AD14 M18

PCI_AD15 K17

PCI_AD16 J16

PCI_AD17 K16

PCI_AD18 N18

PCI_AD19 P18

PCI_AD20 L17

PCI_AD21 L16

PCI_AD22 R18

PCI_AD23 T18

PCI_AD24 M17

PCI_AD25 M16

PCI_AD26 N17

PCI_AD27 P17

PCI_AD28 P15

PCI_AD29 N16

PCI_AD30 R17

PCI_AD31 P16

PCI_CBE0

PCI_CBE1

PCI_CBE2

PCI_CBE3

PCI_CLK D14

PCI_DEVSEL C16

PCI_FRAME

PCI_GNT

PCI_IDSEL

PCI_INTA

PCI_INTB

F16

F15

E16

D17

C17

C18

B18

C14

B15

PCI_INTC

PCI_INTD

PCI_IRDY

PCI_LOCK

PCI_PAR C15

PCI_PERR

PCI_REQ

PCI_RST

PCI_SERR

PCI_STOP

PCI_TRDY

PF0 U08

/

SPISS0

/MSEL0

PF1 R08

/

SPISS1

/MSEL1

PF2 T08

/

SPI0SEL1

MSEL2

PF3 V10

/

SPI1SEL1

/MSEL3

PF4 U09

/

SPI0SEL2

/MSEL4

PF5 R09

/

SPI1SEL2

/MSEL5

PF6 T09

/

SPI0SEL3

/MSEL6

PF7 R11

/

SPI1SEL3

/DF

PF8 T11

/

SPI0SEL4

/SSEL0

PF9 U11

/

SPI1SEL4

/SSEL1

PF10 V12

/

SPI0SEL5

PF11 T12

/

SPI1SEL5

PF12 R12

/

SPI0SEL6

PF13 U12

/

SPI1SEL6

PF14 V13

/

SPI0SEL7

PF15 T13

/

SPI1SEL7

A15

D13

E15

A16

D15

D16

D18

B16

A17

B17

2002 年 6 月

-34-

初步技术数据

2002 年 6 月 ADSP-21535

RESET

B09

RFS0 U13

RFS1 V16

RSCLK0 R13

RSCLK1 U14

RX0 A07

RX1 B08

SA10 M01

SCAS

L03

SCK0 U17

SCK1 R16

SCKE L01

SCLK0 K01

SLEEP D12

SMS0

SMS1

SMS2

SMS3

SRAS

M02

P01

N01

K03

L02

SUSPEND A11

SWE

J03

TCK D10

TDI C11

TDO D11

TFS0 T14

TFS1 R15

TMR0 B07

TMR1 C07

TMR2 D07

TMS A12

TRST

B12

TSCLK0 V15

TSCLK1 T15

TX0 A08

TX1 C08

TXDMNS G10

TXDPLS B10

TXEN

C10

USB_CLK G07

V

E04

DDEXT

V

G04

DDEXT

V

G08

DDEXT

V

J01

DDEXT

V

J02

DDEXT

V

J04

DDEXT

V

K04

DDEXT

V

L04

DDEXT

V

M04

DDEXT

V

P04

DDEXT

V

F04

DDINT

V

G11

DDINT

V

G12

DDINT

V

G15

DDINT

V

H04

DDINT

V

H09

DDINT

V

H12

DDINT

V

L12

DDINT

V

M08

DDINT

V

M11

DDINT

V

M12

DDINT

V

N04

DDINT

V

N15

DDINT

V

V

V

V

V

V

V

V

V

H15

DDPCIEXT

J15

DDPCIEXT

K15

DDPCIEXT

L15

DDPCIEXT

M15

DDPCIEXT

G09

DDPLL

U10

DDRTC

A10

SSPLL

V11

SSRTC

XTALI R10

XTALO T10

XVER_DATA A09

-35-

初步技术数据

ADSP-21535

表 29. 260 –Lead PBGA 排列表(按引脚序号排列)

引脚# 信号

A01 ADDR12

A02 ADDR17

A03 ADDR15

A04 ADDR8

A05 ADDR6

A06 ADDR2

A07 RX0

A08 TX0

A09 XVER_DATA

A10 V

SSPLL

A11 SUSPEND

A12 TMS

A13

EMU

A14 BMODE1

A15

A16

A17

PCI_INTC

PCI_LOCK

PCI_STOP

A18 N/C

B01

ABE1

/SDQM1

B02 ADDR20

B03 ADDR16

B04 ADDR11

B05 ADDR7

B06 ADDR3

B07 TM R0

B08 RX1

B09

RESET

B10 TXDPLS

B11 NMI

B12

TRST

B13 BMODE2

B14 BMODE0

B15

B16

B17

B18

PCI_INTB

PCI_SERR

PCI_TRDY

PCI_IDSEL

C01 ADDR23

C02 ADDR21

C03 ADDR18

C04 ADDR13

C05 ADDR9

C06 ADDR5

C07 TMR1

C08 TX1

C09 DPLS

C10

TXEN

C11 TDI

C12 BYPASS

C13 GND

C14

PCI_INTA

C15 PCI_PAR

C16 PCI_DEVSE

C17

C18

D01

PCI_FRAME

PCI_GNT

AMS1

D02 ADDR25

D03 ADDR19

D04 ADDR14

D05 ADDR10

D06 ADDR4

D07 TMR2

D08 DMNS

D09 CLKIN1

D10 TCK

D11 TDO

D12 SLEEP

D13

PCI_INTD

D14 PCI_CLK

D15

D16

D17

D18

E01

E02

PCI_PERR

PCI_REQ

PCI_CBE3

PCI_RST

AOE

/SDQM0

ABED

E03 ADDR22

E04 V

E15

E16

DDEXT

PCI_IRDY

PCI_CBE2

E17 PCI_AD0

E18 PCI_AD1

F01

F02

ARE

AMS0

F03 ADDR24

F04 V

F15

F16

DDINT

PCI_CBE1

PCI_CBE0

F17 PCI_AD3

F18 PCI_AD4

G01

G02

G03

G04 V

AWE

AMS3

ABE2

DDEXT

/SDQM2

G07 USB_CLK

G08 V

G09 V

DDEXT

DDPLL

G10 TXDMNS

G11 V

G12 V

G15 V

DDINT

DDINT

DDINT

G16 PCI_AD2

G17 PCI_AD6

G18 PCI_AD5

H01 CLKOUT/SCLK1

H02 GND

H03

H04 V

H07

AMS2

DDINT

ABE3

/SDQM3

H08 GND

H09 VDDINT

H10 GND

H11 GND

H12 V

H15 V

DDINT

DDPCIEXT

H16 PCI_AD11

H17 PCI_AD9

H18 PCI_AD7

J01 V

J02 V

J03

J04 V

DDEXT

DDEXT

SWE

DDEXT

2002 年 6 月

-36-

初步技术数据

2002 年 6 月 ADSP-21535

J07 GND

J08 GND

J09 GND

J10 GND

J11 GND

J12 GND

J15 V

DDPCIEXT

J16 PCI_AD16

J17 PCI_AD13

J18 PCI_AD8

K01 SCLK0

K02 GND

K03

K04 V

SMS3

DDEXT

K07 GND

K08 GND

K09 GND

K10 GND

K11 GND

K12 GND

K15 V

DDPCIEXT

K16 PCI_AD17

K17 PCI_AD15

K18 PCI_AD10

L01 SCKE

L02

L03

L04 V

SRAS

SCAS

DDEXT

L07 GND

L08 GND

L09 GND

L10 GND

L11 GND

L12 V

L15 V

DDINT

DDPCIEXT

L16 PCI_AD21

L17 PCI_AD20

L18 PCI_AD12

M01 SA10

M02

SMS0

M03 DATA1

M04 V

DDEXT

M07 GND

M08 V

DDINT

M09 GND

M10 GND

M11 V

M12 V

M15 V

DDINT

DDINT

DDPCIEXT

M16 PCI_AD25

M17 PCI_AD24

M18 PCI_AD14

N01

SMS2

N02 DATA0

N03 DATA4

N04 V

N15 V

DDINT

DDINT

N16 PCI_AD29

N17 PCI_AD26

N18 PCI_AD18

P01

SMS1

P02 DATA3

P03 DATA6

P04 V

DDEXT

P15 PCI_AD28

P16 PCI_AD31

P17 PCI_AD27

P18 PCI_AD19

R01 ARDY

R02 DATA5

R03 N/C

R04 DATA12

R05 DATA19

R06 DATA23

R07 DATA29

R08 PF1

/

SPISS1

/MSEL1

R09 PF5

/