Ultralow Noise, LDO XFET Voltage

www.BDTIC.com/ADI

References with Current Sink and Source

FEATURES

Ultralow noise (0.1 Hz to 10 Hz)

ADR440: 1 μV p-p

ADR441: 1.2 μV p-p

ADR443: 1.4 μV p-p

ADR444: 1.8 μV p-p

ADR445: 2.25 μV p-p

Superb temperature coefficient

A grade: 10 ppm/°C

B grade: 3 ppm/°C

Low dropout operation: 500 mV

Input range: (V

High output source and sink current

+10 mA and −5 mA, respectively

Wide temperature range: −40°C to +125°C

APPLICATIONS

Precision data acquisition systems

High resolution data converters

Battery-powered instrumentation

Portable medical instruments

Industrial process control systems

Precision instruments

Optical control circuits

+ 500 mV) to 18 V

OUT

ADR440/ADR441/ADR443/ADR444/ADR445

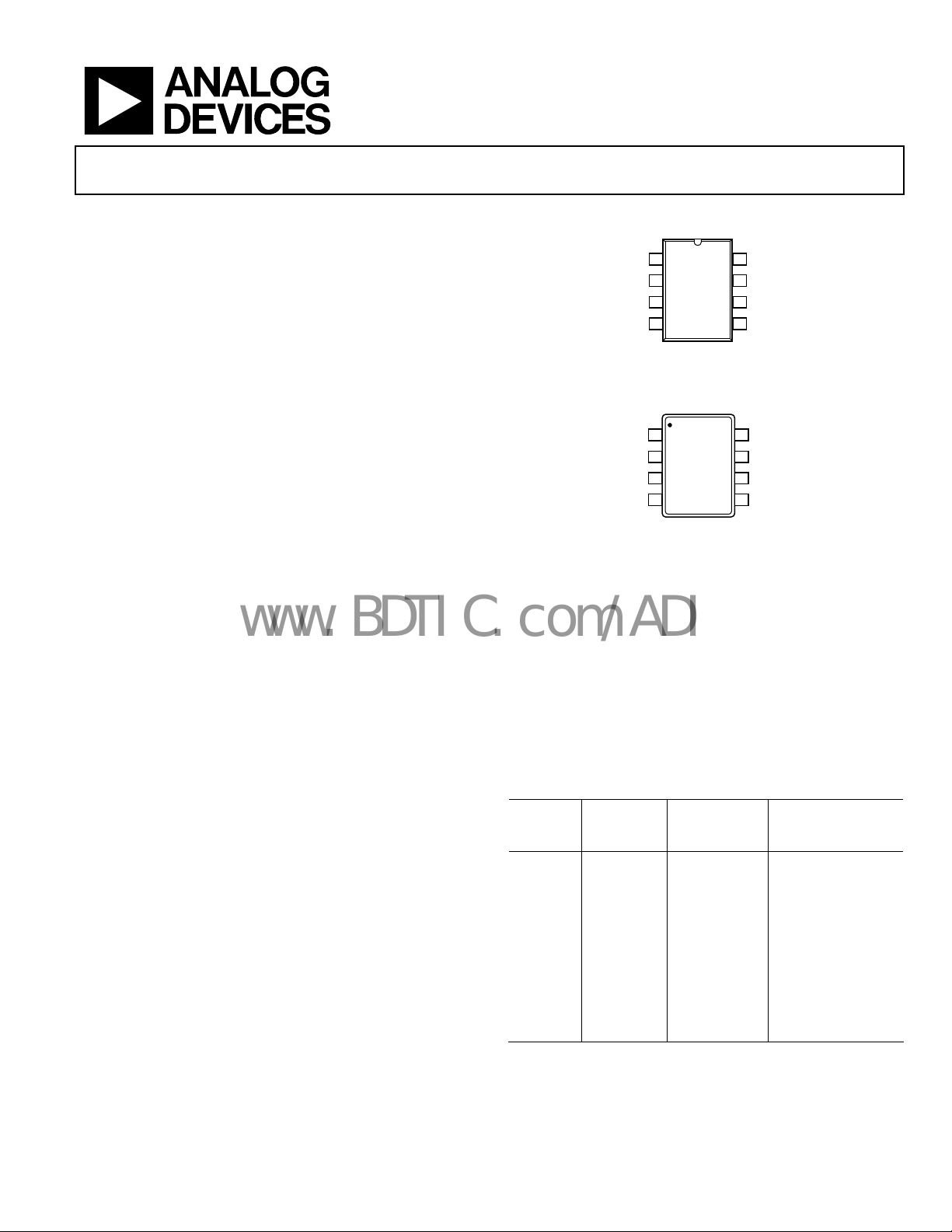

PIN CONFIGURATIONS

ADR440/

TP

1

ADR441/

ADR443/

V

2

IN

ADR444/

NC

3

ADR445

TOP VIEW

4

GND

(Not to Scale)

NOTES

1. NC = NO CONNECT

2. TP = TEST PIN (DO NOT CONNECT)

Figure 1. 8-Lead SOIC_N (R-Suffix)

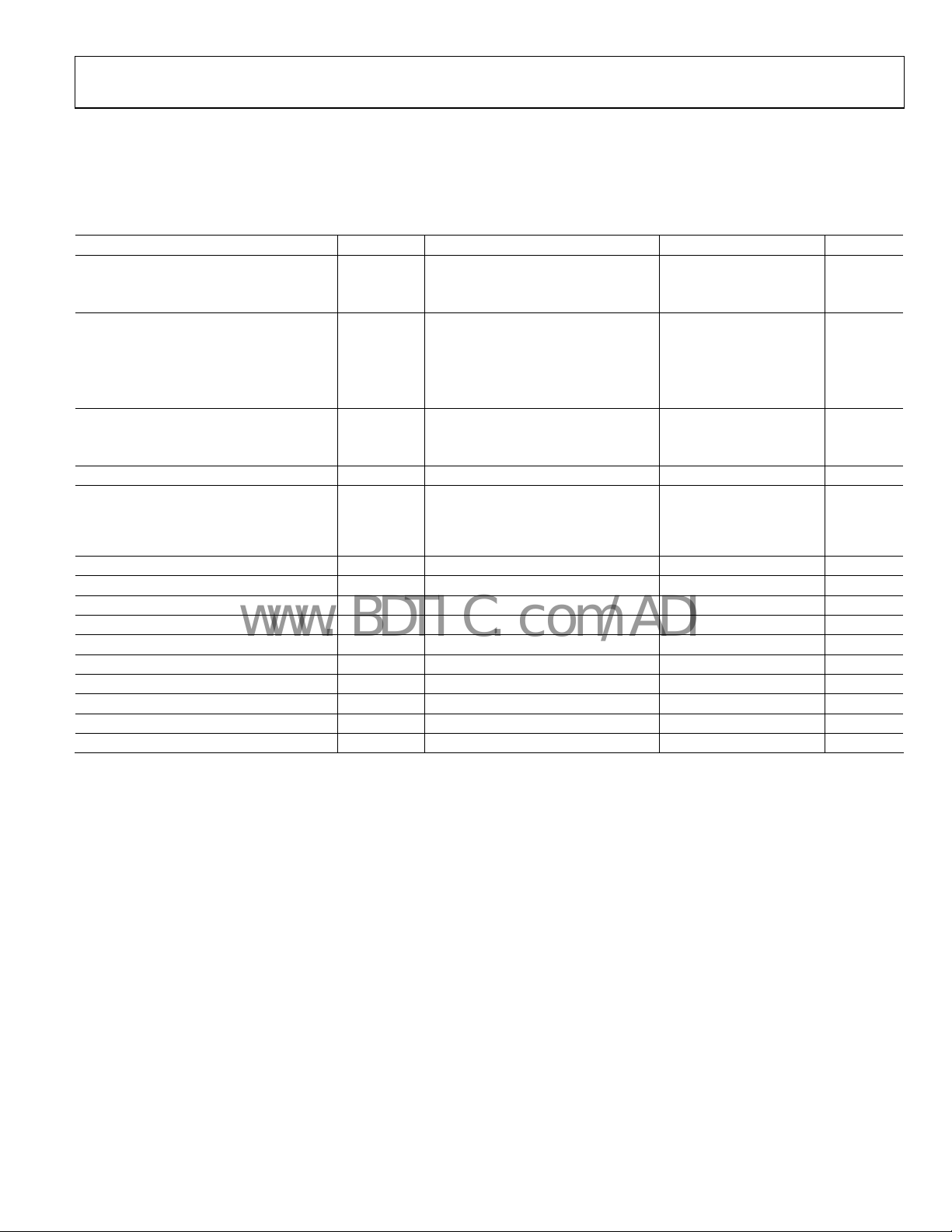

ADR440/

1

TP

ADR441/

ADR443/

2

V

IN

ADR444/

NC

3

ADR445

GND

NOTES

1. NC = NO CONNECT

2. TP = TEST PIN (DO NOT CONNECT)

Figure 2. 8-Lead MSOP (RM-Suffix)

TOP VIEW

4

(Not to Scale)

TP

8

NC

7

6

V

OUT

5

TRIM

05428-001

8

TP

7

NC

V

6

OUT

TRIM

5

05428-002

GENERAL DESCRIPTION

The ADR44x series is a family of XFET® voltage references

featuring ultralow noise, high accuracy, and low temperature

drift performance. Using Analog Devices, Inc., patented

temperature drift curvature correction and XFET (eXtra

implanted junction FET) technology, voltage change vs.

temperature nonlinearity in the ADR44x is greatly minimized.

The XFET references offer better noise performance than

ried Zener references, and XFET references operate off

bu

low supply voltage headroom (0.5 V). This combination of

features makes the ADR44x family ideally suited for precision

signal conversion applications in high-end data acquisition

systems, optical networks, and medical applications.

The ADR44x family has the capability to source up to 10 mA of

o

utput current and sink up to −5 mA. It also comes with a trim

terminal to adjust the output voltage over a 0.5% range without

compromising performance.

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Offered in two electrical grades, the ADR44x family is available in 8-lead MSOP and narrow SOIC packages. All versions

are specified over the extended industrial temperature range of

−40°C to +125°C.

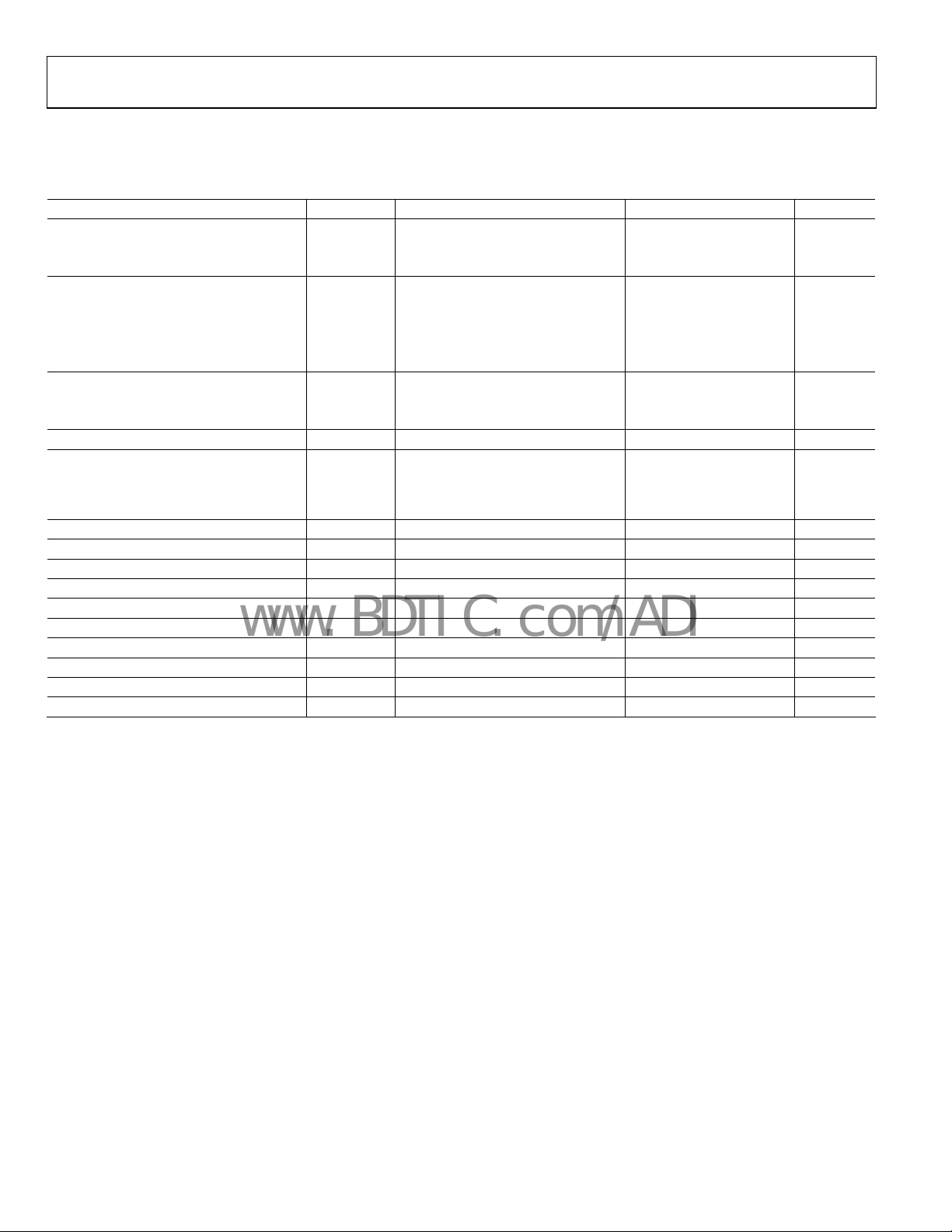

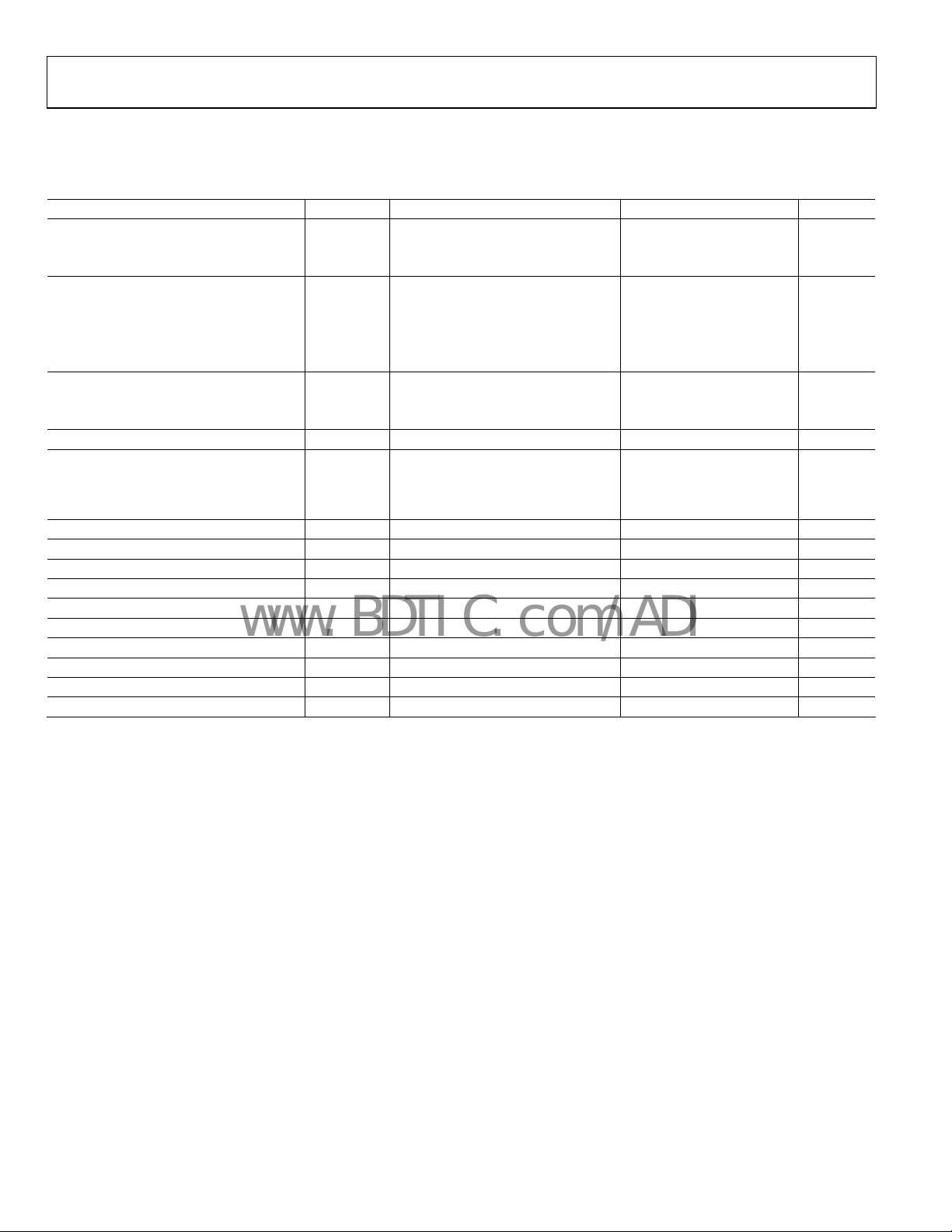

Table 1. Selection Guide

Model

Output

oltage

V

(V)

Initial

Accuracy

(mV)

Temperature

Coefficient

(ppm/°C)

ADR440A 2.048 ±3 10

ADR440B 2.048 ±1 3

ADR441A 2.500 ±3 10

ADR441B 2.500 ±1 3

ADR443A 3.000 ±4 10

ADR443B 3.000 ±1.2 3

ADR444A 4.096 ±5 10

ADR444B 4.096 ±1.6 3

ADR445A 5.000 ±6 10

ADR445B 5.000 ±2 3

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2005–2008 Analog Devices, Inc. All rights reserved.

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

Pin Configurations ........................................................................... 1

General Description......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

ADR440 Electrical Characteristics............................................. 3

ADR441 Electrical Characteristics............................................. 4

ADR443 Electrical Characteristics............................................. 5

ADR444 Electrical Characteristics............................................. 6

ADR445 Electrical Characteristics............................................. 7

Absolute Maximum Ratings............................................................ 8

Thermal Resistance ...................................................................... 8

ESD Caution.................................................................................. 8

Typical Performance Characteristics ............................................. 9

Theory of Operation ...................................................................... 14

Power Dissipation Considerations ........................................... 14

Basic Voltage Reference Connections ..................................... 14

Noise Performance ..................................................................... 14

Tur n -O n Tim e ............................................................................ 14

Applications Information.............................................................. 15

Output Adjustment.................................................................... 15

Bipolar Outputs .......................................................................... 15

Negative Reference ..................................................................... 15

Programmable Voltage Source ................................................. 16

Programmable Current Source ................................................ 16

High Voltage Floating Current Source.................................... 16

Precision Output Regulator (Boosted Reference).................. 17

Outline Dimensions ....................................................................... 18

Ordering Guide .......................................................................... 19

REVISION HISTORY

3/08—Rev. B to Rev. C

Changes to Table 8............................................................................ 8

Change to Figure 11 ....................................................................... 10

Changes to Figure 36...................................................................... 15

Changes to Figure 39...................................................................... 16

Changes to Figure 41...................................................................... 17

Updated Outline Dimensions....................................................... 18

8/07—Rev. A to Rev. B

Change to Table 2, Ripple Rejection Ratio Specification ............ 3

Change to Table 3, Ripple Rejection Ratio Specification ............ 4

Change to Table 4, Ripple Rejection Ratio Specification ............ 5

Change to Table 5, Ripple Rejection Ratio Specification ............ 6

Change to Table 6, Ripple Rejection Ratio Specification ............ 7

9/06—Rev. 0 to Rev. A

Updated Format.................................................................. Universal

Changes to Features ..........................................................................1

Changes to Pin Configurations .......................................................1

Changes to Specifications Section...................................................3

Changes to Figure 4 and Figure 5....................................................9

Inserted Figure 6 and Figure 7.........................................................9

Changes to Figure 15...................................................................... 11

Changes to Power Dissipation Considerations Section ............ 14

Changes to Figure 35 and Figure 36............................................. 15

Changes to Figure 38 and Table 9................................................. 16

Updated Outline Dimensions....................................................... 18

Changes to Ordering Guide.......................................................... 19

10/05—Revision 0: Initial Version

Rev. C | Page 2 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

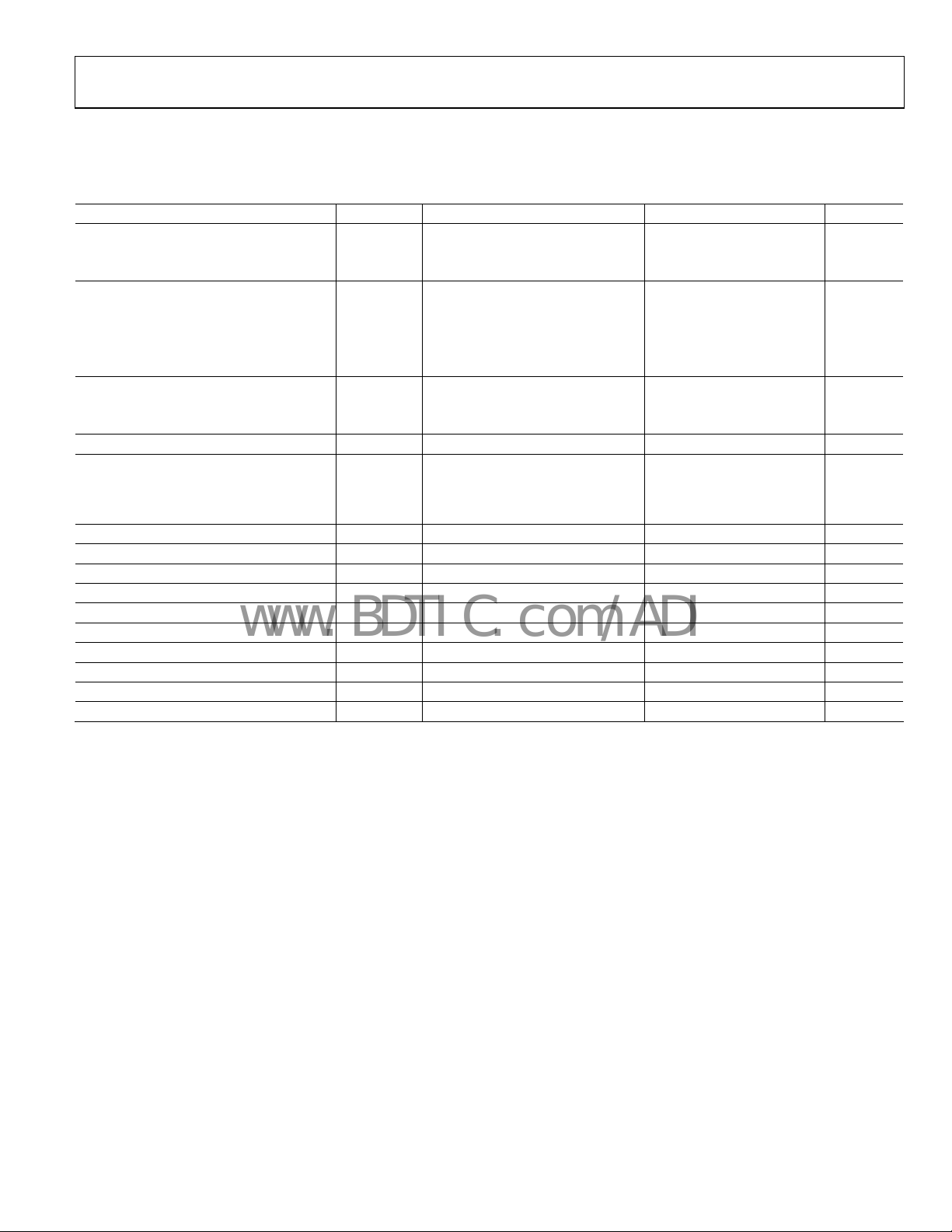

SPECIFICATIONS

ADR440 ELECTRICAL CHARACTERISTICS

VIN = 3 V to 18 V, TA = 25°C, CIN = C

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

A Grade

B Grade

INITIAL ACCURACY V

A Grade

0.15 %

B Grade 1 mV

0.05 %

TEMPERATURE DRIFT TCV

A Grade −40°C < TA < +125°C 2 10 ppm/°C

B Grade −40°C < TA < +125°C 1 3 ppm/°C

LINE REGULATION ΔVO/ΔV

LOAD REGULATION ΔVO/ΔI

ΔVO/ΔI

QUIESCENT CURRENT I

VOLTAGE NOISE eN p-p 0.1 Hz to 10 Hz 1 μV p-p

VOLTAGE NOISE DENSITY e

TURN-ON SETTLING TIME t

LONG-TERM STABILITY

1

OUTPUT VOLTAGE HYSTERESIS V

RIPPLE REJECTION RATIO RRR fIN = 1 kHz −80 dB

SHORT CIRCUIT TO GND I

SUPPLY VOLTAGE OPERATING RANGE V

SUPPLY VOLTAGE HEADROOM VIN − V

1

The long-term stability specification is noncumulative. The drift in the subsequent 1000-hour period is significantly lower than in the first 1000-hour period.

= 0.1 µF, unless otherwise noted.

OUT

O

OERR

O

LOAD

2.045 2.048 2.051 V

2.047 2.048 2.049 V

3 mV

−40°C < TA < +125°C −20 +10 +20 ppm/V

IN

I

= 0 mA to 10 mA, VIN = 3.5 V,

LOAD

−40°C < T

I

LOAD

= 0 mA to −5 mA, VIN = 3.5 V,

LOAD

−40°C < T

IN

V

SC

N

R

O

O_HYS

IN

O

No load, −40°C < TA < +125°C 3 3.75 mA

1 kHz 45 nV/√Hz

10 μs

1000 hours 50 ppm

70 ppm

27 mA

3 18 V

500 mV

< +125°C

A

< +125°C

A

−50 +50 ppm/mA

−50 +50 ppm/mA

Rev. C | Page 3 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ADR441 ELECTRICAL CHARACTERISTICS

VIN = 3 V to 18 V, TA = 25°C, CIN = C

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

A Grade

B Grade

INITIAL ACCURACY V

A Grade

0.12 %

B Grade 1 mV

0.04 %

TEMPERATURE DRIFT TCV

A Grade −40°C < TA < +125°C 2 10 ppm/°C

B Grade −40°C < TA < +125°C 1 3 ppm/°C

LINE REGULATION ΔVO/ΔV

LOAD REGULATION ΔVO/ΔI

ΔVO/ΔI

QUIESCENT CURRENT I

VOLTAGE NOISE eN p-p 0.1 Hz to 10 Hz 1.2 μV p-p

VOLTAGE NOISE DENSITY e

TURN-ON SETTLING TIME t

LONG-TERM STABILITY

1

OUTPUT VOLTAGE HYSTERESIS V

RIPPLE REJECTION RATIO RRR fIN = 1 kHz −80 dB

SHORT CIRCUIT TO GND I

SUPPLY VOLTAGE OPERATING RANGE V

SUPPLY VOLTAGE HEADROOM VIN − V

1

The long-term stability specification is noncumulative. The drift in subsequent 1000-hour period is significantly lower than in the first 1000-hour period.

= 0.1 µF, unless otherwise noted.

OUT

O

OERR

O

LOAD

2.497 2.500 2.503 V

2.499 2.500 2.501 V

3 mV

−40°C < TA < +125°C 10 20 ppm/V

IN

I

= 0 mA to 10 mA, VIN = 4 V,

LOAD

−40°C < T

I

LOAD

= 0 mA to −5 mA, VIN = 4 V,

LOAD

−40°C < T

IN

V

SC

N

R

O

O_HYS

IN

O

No load, −40°C < TA < +125°C 3 3.75 mA

1 kHz 48 nV/√Hz

10 μs

1000 hours 50 ppm

70 ppm

27 mA

3 18 V

500 mV

< +125°C

A

< +125°C

A

−50 +50 ppm/mA

−50 +50 ppm/mA

Rev. C | Page 4 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ADR443 ELECTRICAL CHARACTERISTICS

VIN = 3.5 V to 18 V, TA = 25°C, CIN = C

Table 4.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

A Grade

B Grade

INITIAL ACCURACY V

A Grade

0.13 %

B Grade 1.2 mV

0.04 %

TEMPERATURE DRIFT TCV

A Grade −40°C < TA < +125°C 2 10 ppm/°C

B Grade −40°C < TA < +125°C 1 3 ppm/°C

LINE REGULATION ΔVO/ΔV

LOAD REGULATION ΔVO/ΔI

ΔVO/ΔI

QUIESCENT CURRENT I

VOLTAGE NOISE eN p-p 0.1 Hz to 10 Hz 1.4 μV p-p

VOLTAGE NOISE DENSITY e

TURN-ON SETTLING TIME t

LONG-TERM STABILITY

1

OUTPUT VOLTAGE HYSTERESIS V

RIPPLE REJECTION RATIO RRR fIN = 1 kHz −80 dB

SHORT CIRCUIT TO GND I

SUPPLY VOLTAGE OPERATING RANGE V

SUPPLY VOLTAGE HEADROOM VIN − V

1

The long-term stability specification is noncumulative. The drift in the subsequent 1000-hour period is significantly lower than in the first 1000-hour period.

= 0.1 µF, unless otherwise noted.

OUT

O

OERR

O

LOAD

2.996 3.000 3.004 V

2.9988 3.000 3.0012 V

4 mV

−40°C < TA < +125°C 10 20 ppm/V

IN

I

= 0 mA to 10 mA, VIN = 5 V,

LOAD

−40°C < T

I

LOAD

= 0 mA to −5 mA, VIN = 5 V,

LOAD

−40°C < T

IN

V

SC

N

R

O

O_HYS

IN

O

No load, −40°C < TA < +125°C 3 3.75 mA

1 kHz 57.6 nV/√Hz

10 μs

1000 hours 50 ppm

70 ppm

27 mA

3.5 18 V

500 mV

< +125°C

A

< +125°C

A

−50 +50 ppm/mA

−50 +50 ppm/mA

Rev. C | Page 5 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ADR444 ELECTRICAL CHARACTERISTICS

VIN = 4.6 V to 18 V, TA = 25°C, CIN = C

Table 5.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

A Grade

B Grade

INITIAL ACCURACY V

A Grade

0.13 %

B Grade 1.6 mV

0.04 %

TEMPERATURE DRIFT TCV

A Grade −40°C < TA < +125°C 2 10 ppm/°C

B Grade −40°C < TA < +125°C 1 3 ppm/°C

LINE REGULATION ΔVO/ΔV

LOAD REGULATION ΔVO/ΔI

ΔVO/ΔI

QUIESCENT CURRENT I

VOLTAGE NOISE eN p-p 0.1 Hz to 10 Hz 1.8 μV p-p

VOLTAGE NOISE DENSITY e

TURN-ON SETTLING TIME t

LONG-TERM STABILITY

1

OUTPUT VOLTAGE HYSTERESIS V

RIPPLE REJECTION RATIO RRR fIN = 1 kHz −80 dB

SHORT CIRCUIT TO GND I

SUPPLY VOLTAGE OPERATING RANGE V

SUPPLY VOLTAGE HEADROOM VIN − V

1

The long-term stability specification is noncumulative. The drift in the subsequent 1000-hour period is significantly lower than in the first 1000-hour period.

= 0.1 µF, unless otherwise noted.

OUT

O

OERR

O

4.091 4.096 4.101 V

4.0944 4.096 4.0976 V

5 mV

−40°C < TA < +125°C 10 20 ppm/V

IN

I

LOAD

= 0 mA to 10 mA, VIN = 5.5 V,

LOAD

−40°C < T

I

LOAD

= 0 mA to −5 mA, VIN = 5.5 V,

LOAD

−40°C < T

IN

V

SC

N

R

O

O_HYS

IN

O

No load, −40°C < TA < +125°C 3 3.75 mA

1 kHz 78.6 nV/√Hz

10 μs

1000 hours 50 ppm

70 ppm

27 mA

4.6 18 V

500 mV

< +125°C

A

< +125°C

A

−50 +50 ppm/mA

−50 +50 ppm/mA

Rev. C | Page 6 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ADR445 ELECTRICAL CHARACTERISTICS

VIN = 5.5 V to 18 V, TA = 25°C, CIN = C

Table 6.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE V

A Grade

B Grade

INITIAL ACCURACY V

A Grade

0.12 %

B Grade 2 mV

0.04 %

TEMPERATURE DRIFT TCV

A Grade −40°C < TA < +125°C 2 10 ppm/°C

B Grade −40°C < TA < +125°C 1 3 ppm/°C

LINE REGULATION ΔVO/ΔV

LOAD REGULATION ΔVO/ΔI

ΔVO/ΔI

QUIESCENT CURRENT I

VOLTAGE NOISE eN p-p 0.1 Hz to 10 Hz 2.25 μV p-p

VOLTAGE NOISE DENSITY e

TURN-ON SETTLING TIME t

LONG-TERM STABILITY

1

OUTPUT VOLTAGE HYSTERESIS V

RIPPLE REJECTION RATIO RRR fIN = 1 kHz –80 dB

SHORT CIRCUIT TO GND I

SUPPLY VOLTAGE OPERATING RANGE V

SUPPLY VOLTAGE HEADROOM VIN − V

1

The long-term stability specification is noncumulative. The drift in the subsequent 1000-hour period is significantly lower than in the first 1000-hour period.

= 0.1 µF, unless otherwise noted.

OUT

O

OERR

O

LOAD

4.994 5.000 5.006 V

4.998 5.000 5.002 V

6 mV

−40°C < TA < +125°C 10 20 ppm/V

IN

I

= 0 mA to 10 mA, VIN = 6.5 V,

LOAD

−40°C < T

I

LOAD

= 0 mA to −5 mA, VIN = 6.5 V,

LOAD

−40°C < T

IN

V

SC

N

R

O

O_HYS

IN

O

No load, −40°C < TA < +125°C 3 3.75 mA

1 kHz 90 nV/√Hz

10 μs

1000 hours 50 ppm

70 ppm

27 mA

5.5 18 V

500 mV

< +125°C

A

< +125°C

A

−50 +50 ppm/mA

−50 +50 ppm/mA

Rev. C | Page 7 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 7.

Parameter Rating

Supply Voltage 20 V

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature, Soldering (60 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 8. Thermal Resistance

Package Type θ

8-Lead SOIC (R-Suffix) 130 43 °C/W

8-Lead MSOP (RM-Suffix) 132.5 43.9 °C/W

θ

JA

Unit

JC

ESD CAUTION

Rev. C | Page 8 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

T

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 7 V, TA = 25°C, CIN = C

2.051

= 0.1 µF, unless otherwise noted.

OUT

4.0980

2.050

2.049

2.048

2.047

OUTPUT VOLTAGE (V)

2.046

2.045

–40 –20 0 20 100806040 120

TEMPERATURE (°C)

Figure 3. ADR440 Output Voltage vs. Temperature

2.5020

2.5015

2.5010

AGE (V)

2.5005

2.5000

OUTPUT VOL

2.4995

4.0975

4.0970

4.0965

4.0960

4.0955

OUTPUT VOLTAGE (V)

4.0950

4.0945

05428-042

4.0940

–40 5–10–25 503520 110958065 125

DEVICE 1

DEVICE 3

TEMPERATURE (°C)

DEVICE 2

05428-005

Figure 6. ADR444 Output Voltage vs. Temperature

5.006

5.004

5.002

5.000

4.998

OUTPUT VOLTAGE (V)

4.996

2.4990

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

Figure 4. ADR441 Output Voltage vs. Temperature

3.0020

3.0015

3.0010

3.0005

3.0000

2.9995

OUTPUT VOLTAGE (V)

2.9990

2.9985

2.9980

–40 5–10–25 503520 110958065 125

DEVICE 1

DEVICE 2

DEVICE 3

TEMPERATURE (°C)

Figure 5. ADR443 Output Voltage vs. Temperature

05428-003

05428-004

Rev. C | Page 9 of 20

4.994

–40 –20 0 20 100806040 120

TEMPERATURE (°C)

Figure 7. ADR445 Output Voltage vs. Temperature

4.0

3.5

3.0

SUPPLY CURRENT (mA)

2.5

2.0

46 10811412 18

INPUT VOLTAGE (V)

+25°C

–40°C

Figure 8. ADR441 Supply Current vs. Input Vo

05428-043

+125°C

6

05428-006

ltage

ADR440/ADR441/ADR443/ADR444/ADR445

A

A

www.BDTIC.com/ADI

4.0

10

3.5

3.0

SUPPLY CURRENT (mA)

2.5

2.0

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

Figure 9. ADR441 Supply Current vs. Temperature

3.5

3.4

3.3

3.2

3.1

3.0

2.9

2.8

SUPPLY CURRENT (mA)

2.7

2.6

2.5

5.3 9.37.3 13.311.3 17.315.3 19.3

INPUT VOLTAGE (V)

+125°C

+25°C

–40°C

Figure 10. ADR445 Supply Current vs. Input Voltage

8

6

TION (ppm/V)

4

LINE REGUL

2

05428-007

0

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

05428-010

Figure 12. ADR441 Line Regulation vs. Temperature

60

I

= 0mA TO 10mA

LOAD

55

VIN = 18V

50

TION (ppm/mA)

45

VIN = 6V

40

LOAD REGUL

35

05428-008

30

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

05428-011

Figure 13. ADR441 Load Regulation vs. Temperature

3.25

3.15

3.05

2.95

SUPPLY CURRENT (mA)

2.85

2.75

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

Figure 11. ADR445 Supply Current vs. Temperature

05428-009

Rev. C | Page 10 of 20

7

6

5

4

3

2

LINE REGULATION (ppm/V)

1

0

–40 5–10–25 503520 110958065 125

TEMPERATURE (° C)

Figure 14. ADR445 Line Regulation vs. Temperature

05428-012

ADR440/ADR441/ADR443/ADR444/ADR445

A

A

A

www.BDTIC.com/ADI

50

VIN = 6V

40

30

20

10

TION (ppm/mA)

–10

–20

LOAD REGUL

–30

–40

–50

I

= 0mA TO +10mA

LOAD

0

I

= 0mA TO –5mA

LOAD

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

Figure 15. ADR445 Load Regulation vs. Temperature

05428-013

1.0

0.9

0.8

0.7

0.6

L VOLTAGE (V)

0.5

0.4

0.3

DIFFERENTI

0.2

0.1

0

–5 0 5 10

LOAD CURRENT (mA)

+125°C

Figure 18. ADR445 Minimum Input/Output

ferential Voltage vs. Load Current

Dif

+25°C

–40°C

05428-016

0.7

0.6

0.5

0.4

L VOLTAGE (V)

0.3

0.2

DIFFERENTI

0.1

0

–10 –5 0 5 10

LOAD CURRENT (mA)

+125°C

+25°C

Figure 16. ADR441 Minimum Input/Output

ferential Voltage vs. Load Current

Dif

0.5

NO LOAD

0.4

0.3

0.2

–40°C

0.5

NO LOAD

0.4

0.3

0.2

MINIMUM HEADROOM (V)

0.1

05428-014

0

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

05428-017

Figure 19. ADR445 Minimum Headroom vs. Temperature

CIN = C

OUT

VIN = 5V/DIV

= 0.1µF

MINIMUM HEADROOM (V)

0.1

0

–40 5–10–25 503520 110958065 125

TEMPERATURE (°C)

05428-015

Figure 17. ADR441 Minimum Headroom vs. Temperature

Rev. C | Page 11 of 20

V

= 1V/DIV

OUT

Figure 20. ADR441 Turn-On Response

TIME = 10µs/DIV

05428-018

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

CIN = C

= 0.1µF

OUT

TIME = 200µs/DIV

Figure 21. ADR441 Turn-Off Response

CIN = 0.1µF

= 10µF

C

OUT

VIN = 5V/DIV

V

= 1V/DIV

OUT

VIN = 5V/DIV

V

= 1V/DIV

OUT

CIN = 0.1µF

= 10µF

C

OUT

LOAD OFF

05428-019

TIME = 200µ s/DIV

LOAD ON

5mV/DIV

05428-023

Figure 24. ADR441 Load Transient Response

CIN = C

= 0.1µF

OUT

LOAD OFF LOAD ON

5mV/DIV

Figure 22. ADR441 Turn-On Response

CIN = 0.1µF

C

= 10µF

OUT

4V

Figure 23. ADR441 Line Tr

TIME = 200µ s/DIV

2V/DIV

2mV/DIV

TIME = 100µs/DIV

ansient Response

05428-020

TIME = 200µs/DIV

05428-022

Figure 25. ADR441 Load Transient Response

1µV/DIV

CH 1 p-p

1.18µV

TIME = 1s/DIV

05428-021

05428-024

Figure 26. ADR441 0.1 Hz to 10.0 Hz Voltage Noise

Rev. C | Page 12 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

A

www.BDTIC.com/ADI

16

14

12

50µV/DIV

CH 1 p-p

49µV

10

8

6

NUMBER OF PARTS

4

TIME = 1s/ DIV

Figure 27. ADR441 10 Hz to 10 kHz Voltage Noise

1µV/DIV

TIME = 1s/ DIV

Figure 28. ADR445 0.1 Hz to 10.0 Hz Voltage Noise

50µV/DIV

TIME = 1s/ DIV

Figure 29. ADR445 10 Hz to 10 kHz Voltage Noise

05428-025

CH 1 p-p

2.24µV

05428-026

CH 1 p-p

66µV

05428-027

2

0

–150

–130

–110

–90

–30

–70

–50

DEVIATIO N (ppm)

Figure 30. ADR441 Typical Output V

10

9

8

7

6

5

4

3

OUTPUT IMPEDANCE (Ω)

2

1

0

FREQUENCY ( Hz)

Figure 31. Output Imped

0

–10

–20

–30

TIO (dB)

–40

–50

–60

–70

–80

RIPPLE REJECTION R

–90

–100

FREQUENCY ( Hz)

103050

–10

oltage Hysteresis

ADR443

ance vs. Frequency

90

70

ADR445

100k 1M10k1k100

110

130

ADR441

100k10k1k10010

05428-028

150

05428-029

05428-030

Figure 32. Ripple Rejection Ratio vs. Frequency

Rev. C | Page 13 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

V

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADR44x series of references uses a new reference generation

technique known as XFET (eXtra implanted junction FET).

This technique yields a reference with low dropout, good

thermal hysteresis, and exceptionally low noise. The core of the

XFET reference consists of two junction field-effect transistors

(JFETs), one of which has an extra channel implant to raise its

pinch-off voltage. By running the two JFETs at the same drain

current, the difference in pinch-off voltage can be amplified

and used to form a highly stable voltage reference.

The intrinsic reference voltage is around 0.5 V with a negative

t

emperature coefficient of about –120 ppm/°C. This slope is

essentially constant to the dielectric constant of silicon, and it can

be closely compensated for by adding a correction term generated

in the same fashion as the proportional-to-absolute temperature

(PTAT) term used to compensate band gap references. The

advantage of an XFET reference is its correction term, which is

approximately 20 times lower and requires less correction than

that of a band gap reference. Because most of the noise of a band

gap reference comes from the temperature compensation

circuitry, the XFET results in much lower noise.

Figure 33 shows the basic topology of the ADR44x series. The

emperature correction term is provided by a current source with

t

a value designed to be proportional to the absolute temperature.

The general equation is

= G (VP − R1 × I

V

OUT

) (1)

PTAT

where:

G i

s the gain of the reciprocal of the divider ratio.

∆V

is the difference in pinch-off voltage between the two JFETs.

P

I

is the positive temperature coefficient correction current.

PTAT

ADR44x devices are created by on-chip adjustment of R2

and R3 t

o achieve the different voltage options at the

reference output.

IN

I

PTAT

I

I

1

1

POWER DISSIPATION CONSIDERATIONS

The ADR44x family of references is guaranteed to deliver load

currents to 10 mA with an input voltage that ranges from 3 V to

18 V. When these devices are used in applications at higher

currents, use the following equation to account for the

temperature effects of increases in power dissipation:

= PD × θJA + TA (2)

T

J

where:

T

and TA are the junction and ambient temperatures,

J

respectively.

P

is the device power dissipation.

D

is the device package thermal resistance.

θ

JA

BASIC VOLTAGE REFERENCE CONNECTIONS

The ADR44x family requires a 0.1 µF capacitor on the input

and the output for stability. Although not required for operation,

a 10 µF capacitor at the input can help with line voltage

transient performance.

ADR440/

TP

1

NC

GND

ADR441/

ADR443/

2

ADR444/

3

ADR445

TOP VIEW

4

(Not to Scale)

V

IN

+

10µF

0.1µF

NOTES

1. NC = NO CONNECT

2. TP = TEST PIN (DO NOT CONNECT)

Figure 34. Basic Voltage Reference Configuration

TP

8

7

NC

V

OUT

6

TRIM

5

0.1µF

05428-034

NOISE PERFORMANCE

The noise generated by the ADR44x family of references is

typically less than 1.4 µV p-p over the 0.1 Hz to 10.0 Hz band

for ADR440, ADR441, and ADR443. Figure 26 shows the 0.1 Hz

o 10 Hz noise of the ADR441, which is only 1.2 µV p-p. The

t

noise measurement is made with a band-pass filter composed of

a 2pole high-pass filter with a corner frequency at 0.1 Hz and a

2pole low-pass filter with a corner frequency at 10.0 Hz.

R2

R3

GND

V

OUT

05428-033

ADR44x

*

ΔV

P

R1

*EXTRA CHANNEL IMP LANT

V

= G (ΔVP – R1 × I

OUT

Figure 33. Simplified Schematic Device

PTAT

)

Rev. C | Page 14 of 20

TURN-ON TIME

Upon application of power (cold start), the time required for

the output voltage to reach its final value within a specified

error band is defined as the turn-on settling time. Two components normally associated with this are the time for the active

circuits to settle and the time for the thermal gradients on the

chip to stabilize.

t

urn-off settling times for the ADR441.

Figure 20 and Figure 21 show the turn-on and

ADR440/ADR441/ADR443/ADR444/ADR445

V

V

www.BDTIC.com/ADI

APPLICATIONS INFORMATION

OUTPUT ADJUSTMENT

The ADR44x family features a TRIM pin that allows the user to

adjust the output voltage of the part over a limited range. This

allows errors from the reference and overall system errors to be

trimmed out by connecting a potentiometer between the output

and the ground, with the wiper connected to the TRIM pin.

Figure 35 shows the optimal trim configuration. R1 allows fine

ad

justment of the output and is not always required. R

be sufficiently large so that the maximum output current from

the ADR44x is not exceeded.

0.1µF

2

V

IN

V

OUT

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

TRIM

GND

4

6

5

R1

100kΩ

0.1µF

R

P

10kΩ

R2

1kΩ

VO = ±0.5%

Figure 35. ADR44x Trim Function

Using the trim function has a negligible effect on the temperature

performance of the ADR44x. However, all resistors need to be

low temperature coefficient resistors, or errors may occur.

BIPOLAR OUTPUTS

By connecting the output of the ADR44x to the inverting terminal of an operational amplifier, it is possible to obtain both

positive and negative reference voltages. Care must be taken

when choosing Resistors R1 and R2 (see Figure 36). These

r

esistors must be matched as closely as possible to ensure minimal differences between the negative and positive outputs. In

addition, care must be taken to ensure performance over

temperature. Use low temperature coefficient resistors if the

circuit is used over temperature; otherwise, differences exist

between the two outputs.

should

P

05428-035

+

DD

2

V

IN

ADR440/

ADR441/

ADR443/

0.1µF

ADR444/

ADR445

V

OUT

GND

4

6

0.1µF

R3

5kΩ

R1

10kΩ

10kΩ

+10V

–10V

+5V

R2

–5V

05428-036

Figure 36. ADR44x Bipolar Outputs

NEGATIVE REFERENCE

Figure 37 shows how to connect the ADR44x and a standard

operational amplifier, such as the OP1177, to provide negative

oltage. This configuration provides two main advantages. First,

v

it only requires two devices; therefore, it does not require

excessive board space. Second, and more importantly, it does

not require any external resistors. This means the performance

of this circuit does not rely on choosing low temperature

coefficient resistors to ensure accuracy.

+

DD

2

V

IN

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

6

V

OUT

GND

4

–V

REF

–V

DD

Figure 37. ADR44x N

V

is at virtual ground, and the negative reference is taken

OUT

egative Reference

directly from the output of the operational amplifier. If the

negative supply voltage is close to the reference output, the

operational amplifier must be dual supply and have low offset

and rail-to-rail capability.

05428-037

Rev. C | Page 15 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

V

V

V

www.BDTIC.com/ADI

PROGRAMMABLE VOLTAGE SOURCE

To obtain different voltages than those offered by the ADR44x,

some extra components are needed. In Figure 38, two potenti-

meters are used to set the desired voltage and the buffering

o

amplifier provides current drive. The potentiometer connected

between V

noninverting input of the operational amplifier, takes care of

coarse trim. The second potentiometer, with its wiper connected

to the trim terminal of the ADR44x, is used for fine adjustment.

Resolution depends on the end-to-end resistance value and the

resolution of the selected potentiometer.

For a completely programmable solution, replace the two

potentiometers in Figure 38 with one Analog Devices dual

dig

ital potentiometer, offered with either an SPI or an I

interface. These interfaces set the position of the wiper on both

potentiometers and allow the output voltage to be set.

ts compatible Analog Devices digital potentiometers.

lis

Table 9. Digital Potentiometer Parts

Part No.

AD5251 2.00 64.00 I2C 1, 10, 50, 100 5.5

AD5207 2.00 256.00 SPI 10, 50, 100 5.5

AD5242 2.00 256.00 I2C 10, 100, 1M 5.5

AD5262 2.00 256.00 SPI 20, 50, 200 15

AD5282 2.00 256.00 I2C 20, 50, 100 15

AD5252 2.00 256.00 I2C 1, 10, 50, 100 5.5

AD5232 2.00 256.00 SPI 10, 50, 100 5.5

AD5235 2.00 1024.00 SPI 25, 250 5.5

ADN2850 2.00 1024.00 SPI 25, 250 5.5

1

Can also use a negative supply.

Adding a negative supply to the operational amplifier allows

the user to produce a negative programmable reference

by connecting the reference output to the inverting terminal

of the operational amplifier. Choose feedback resistors to

minimize errors over temperature.

and GND, with its wiper connected to the

OUT

+

DD

2

V

IN

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

GND

6

V

OUT

R2

R1

10kΩ

4

10kΩ

Figure 38. Programmable Voltage Source

No. of

Channels

No. of

P

ositions ITF R (kΩ)

ADJ V

REF

05428-038

2

C®

Table 9

V

DD

(V)

1

PROGRAMMABLE CURRENT SOURCE

It is possible to build a programmable current source using a

setup similar to the programmable voltage source, as shown in

Figure 39. The constant voltage on the gate of the transistor sets

t

he current through the load. Varying the voltage on the gate

changes the current. This circuit does not require a dual digital

potentiometer.

CC

0.1µF

2

V

IN

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

V

OUT

6

GND

4

0.1µF

AD5259

Figure 39. Programmable Current Source

I

LOAD

R

SENSE

HIGH VOLTAGE FLOATING CURRENT SOURCE

Use the c ircu it in Figure 40 to generate a floating current source

with minimal self heating. This particular configuration can

operate on high supply voltages, determined by the breakdown

voltage of the N-channel JFET.

+

S

SST 111

VISHAY

2

V

IN

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

V

OUT

6

GND

4

OP90

Figure 40. Floating Current Source

2N3904

–V

S

05428-040

05428-039

Rev. C | Page 16 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

V

www.BDTIC.com/ADI

PRECISION OUTPUT REGULATOR (BOOSTED REFERENCE)

IN

C

IN

0.1µF

Higher current drive capability can be obtained without

sacrificing accuracy by using the circuit in Figure 41. The

o

perational amplifier regulates the MOSFET turn-on, forcing

V

to equal the V

O

increased current drive capability. The circuit allows a 50 mA

load; if higher current drive is required, use a larger MOSFET.

For fast transient response, add a buffer at V

capacitive loading.

2

V

IN

ADR440/

ADR441/

ADR443/

ADR444/

ADR445

V

OUT

GND

4

6

C

0.1µF

15V

OUT

–V

Figure 41. Boosted Output Reference

. Current is then drawn from VIN, allowing

REF

O

2N7002

R

L

200Ω

to aid with

C

1µF

V

L

O

5428-041

Rev. C | Page 17 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLL ING DIMENSI ONS ARE IN MILLIME TERS; INCH DIM ENSIONS

(IN PARENTHESES) ARE ROUNDED-OF F MILLIMETER E QUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DESI GN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-A A

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

Figure 42. 8-Lead Standard Small Outline Package [SOIC_N]

Nar

row Body

(R-8)

Dimensions shown in millimeters and (inches)

3.20

3.00

2.80

8

5

4

SEATING

PLANE

5.15

4.90

4.65

1.10 MAX

0.23

0.08

8°

0°

3.20

3.00

2.80

PIN 1

0.95

0.85

0.75

0.15

0.00

COPLANARITY

1

0.65 BSC

0.38

0.22

0.10

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

0.80

0.60

0.40

45°

012407-A

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 43. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dim

ensions show in millimeters

Rev. C | Page 18 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

ORDERING GUIDE

Initial

Accuracy

±mV %

Model

ADR440ARZ

1

ADR440ARZ-REEL7

ADR440ARMZ

1

Output

V

oltage (V)

2.048 3 0.15 10 8-Lead SOIC_N –40°C to +125°C R-8

1

2.048 3 0.15 10 8-Lead SOIC_N –40°C to +125°C R-8

2.048 3 0.15 10 8-Lead MSOP R01 –40°C to +125°C RM-8

ADR440ARMZ-REEL712.048 3 0.15 10 8-Lead MSOP R01 –40°C to +125°C RM-8

ADR440BRZ

ADR440BRZ-REEL7

ADR441ARZ

ADR441ARZ-REEL7

ADR441ARMZ

1

1

1

2.048 1 0.05 3 8-Lead SOIC_N –40°C to +125°C R-8

1

2.048 1 0.05 3 8-Lead SOIC_N –40°C to +125°C R-8

2.500 3 0.12 10 8-Lead SOIC_N –40°C to +125°C R-8

1

2.500 3 0.12 10 8-Lead SOIC_N –40°C to +125°C R-8

2.500 3 0.12 10 8-Lead MSOP R02 –40°C to +125°C RM-8

ADR441ARMZ-REEL712.500 3 0.12 10 8-Lead MSOP R02 –40°C to +125°C RM-8

ADR441BRZ

ADR441BRZ-REEL7

ADR443ARZ

ADR443ARZ-REEL7

ADR443ARMZ

1

1

1

2.500 1 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

1

2.500 1 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

3.000 4 0.13 10 8-Lead SOIC_N –40°C to +125°C R-8

1

3.000 4 0.13 10 8-Lead SOIC_N –40°C to +125°C R-8

3.000 4 0.13 10 8-Lead MSOP R03 –40°C to +125°C RM-8

ADR443ARMZ-REEL713.000 4 0.13 10 8-Lead MSOP R03 –40°C to +125°C RM-8

ADR443BRZ

ADR443BRZ-REEL7

ADR444ARZ

ADR444ARZ-REEL7

ADR444ARMZ

1

1

1

3.000 1.2 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

1

3.000 1.2 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

4.096 5 0.13 10 8-Lead SOIC_N –40°C to +125°C R-8

1

4.096 5 0.13 10 8-Lead SOIC_N –40°C to +125°C R-8

4.096 5 0.13 10 8-Lead MSOP R04 –40°C to +125°C RM-8

ADR444ARMZ-REEL714.096 5 0.13 10 8-Lead MSOP R04 –40°C to +125°C RM-8

ADR444BRZ

ADR444BRZ-REEL7

ADR445ARZ

ADR445ARZ-REEL7

ADR445ARMZ

1

1

1

4.096 1.6 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

1

4.096 1.6 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

5.000 6 0.12 10 8-Lead SOIC_N –40°C to +125°C R-8

1

5.000 6 0.12 10 8-Lead SOIC_N –40°C to +125°C R-8

5.000 6 0.12 10 8-Lead MSOP R05 –40°C to +125°C RM-8

ADR445ARMZ-REEL715.000 6 0.12 10 8-Lead MSOP R05 –40°C to +125°C RM-8

ADR445BRZ

ADR445BRZ-REEL7

1

Z = RoHS Compliant Part.

1

5.000 2 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

1

5.000 2 0.04 3 8-Lead SOIC_N –40°C to +125°C R-8

Temperature

C

oefficient

Package (ppm/°C)

Package

Description Branding

Temperature

Ra

nge

Package

Option

Rev. C | Page 19 of 20

ADR440/ADR441/ADR443/ADR444/ADR445

www.BDTIC.com/ADI

NOTES

Purchase of licensed I2C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I2C Patent

Rights to use these components in an I

©2005–2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05428-0-3/08(C)

2

C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

Rev. C | Page 20 of 20

Loading...

Loading...