1.2 V Ultralow Power

V

V

www.BDTIC.com/ADI

FEATURES

1.2 V precision output

Excellent line regulation: 2 ppm/V typical

High power supply ripple rejection: –80 dB at 220 Hz

Ultralow power supply current: 16 μA maximum

Temperature coefficient: 40 ppm/°C maximum

Low noise, 12.5 nV/√Hz typical

Operating supply range, 2.4 V to 5.5 V

Compact 3-lead SOT-23 and SC70 packages

APPLICATIONS

List GSM, GPRS, 3G mobile stations

Portable battery-operated electronics

Low voltage converter references

Wireless devices

GENERAL DESCRIPTION

The ADR280 is a 1.2 V band gap core reference with excellent

line regulation and power supply rejection designed specifically

for applications experiencing heavy dynamic supply variations,

such as data converter references in GSM, GPRS, and 3G

mobile station applications. Devices such as the AD6535 that

have an analog baseband IC with on-board baseband, audio

codecs, voltage regulators, and battery chargers rely on the

ability of the ADR280 to reject input battery voltage variations

during RF power amplifier activity.

In addition to mobile stations, the ADR280 is suitable for a

va

riety of general-purpose applications. Most band gap references include internal gain for specific outputs, which simplifies

the user’s design, but compromises on the cost, form factor, and

flexibility. The ADR280, on the other hand, optimizes the band

gap core voltage and allows users to tailor the voltage, current,

or transient response by simply adding their preferred op amps.

The ADR280 operates on a wide supply voltage range from

o 5.5 V. It is available in compact 3-lead SOT-23 and

2.4 V t

SC70 packages. The device is specified over the extended industrial temperature range of −40°C to +85°C.

High PSRR Voltage Reference

ADR280

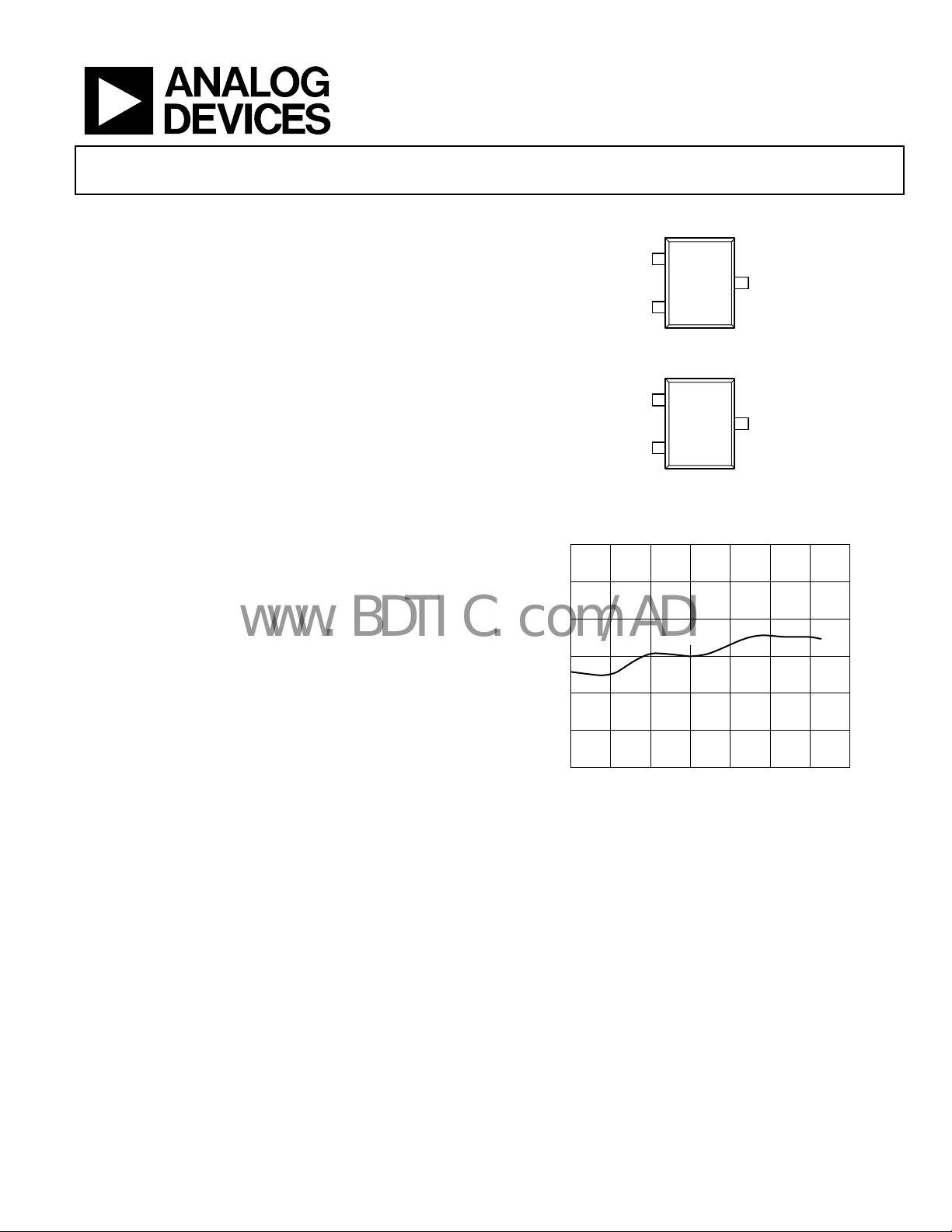

PIN CONFIGURATIONS

V+

1

ADR280

2

OUT

Figure 1. 3-Lead SOT-23

(RT Suffi

1

OUT

ADR280

V+

2

Figure 2. 3-Lead SC70

(KS Suffix)

15

10

5

3V TO 5V

0

–5

LINE REGUL ATION (ppm/V)

–10

–15

–40 –20 0 20 40 60 80 100

Figure 3. Line Regulation vs. Temperature

TEMPERATURE (°C)

V–

3

03065-001

x)

3

V–

03065-002

03065-003

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2002–2007 Analog Devices, Inc. All rights reserved.

ADR280

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Pin Configurations ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings............................................................ 4

REVISION HISTORY

4/07—Rev. B to Rev. C

Updated Format..................................................................Universal

Changes to Figure 1, Figure 2.......................................................... 1

Deleted Pin Function Descriptions Section and Pin

onfigurations Section .................................................................... 2

C

Changes to Figure 20 and Figure 21............................................... 9

Updated Outline Dimensions....................................................... 10

10/04—Rev. A to Rev. B

Changes to Pin Configurations.........................................Universal

hanges to Ordering Guide............................................................ 2

C

Changes to Outline Dimensions..................................................... 7

Thermal Resistance.......................................................................4

ESD Caution...................................................................................4

Typical Performance Characteristics..............................................5

Theory of Operation .........................................................................7

Applications Information.................................................................8

Low Cost, Low Power Current Source .......................................8

Outline Dimensions....................................................................... 10

Ordering Guide .......................................................................... 11

6/03—Rev. 0 to Rev. A

Added SC70 package..........................................................Universal

hanges to Features ..........................................................................1

C

Changes to General Description .....................................................1

Changes to Specifications.................................................................2

Changes to Ordering Guide.............................................................2

Changes to TPCs 4, 6, and 7 ............................................................3

Updated SOT-23 Outline Dimensions ...........................................7

11/02—Revision 0: Initial Version

Rev. C | Page 2 of 12

ADR280

www.BDTIC.com/ADI

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VIN = 2.55 V to 5.5 V, TA = 25°C, unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ1Max Unit

Output Voltage V

Temperature Coefficient TCVO 0°C < TA < 50°C 5 20 ppm/°C

–40°C < TA < +85°C 10 40 ppm/°C

Line Regulation ΔV

Supply Current IIN 2.4 V < VIN < 5.5 V, no load 10 16 μA

Ground Current I

Input Voltage Range VIN 2.4 5.5 V

Operating Temperature Range TA −40 +85 °C

Nominal Load Capacitance C

Output Noise Voltage VN rms f = 10 Hz to 10 kHz 12.5 μV rms

Voltage Noise Density eN f = 400 kHz 12.5 nV/√Hz

Power Supply Ripple Rejection2PSRR I

Start-Up Time tON 2 ms

1

Typical values represent average readings taken at room temperature.

2

Power supply ripple rejection measurement applies to a changing input voltage (VIN) waveform with a nominal 3.6 V baseline that drops to a 3 V value for 380 μs at a

4.6 ms repetition rate.

2.4 V < VIN < 5.5 V, 0 μA < I

OUT

/ΔVIN 2.55 V < VIN < 5.5 V, no load 2 12 ppm/V

OUT

V– grounded, I

GND

1 μF

OUT

= 10 μA −80 dB

LOAD

= 10 μA 12 20 μA

LOAD

< 10 μA, −40°C < TA < +85°C 1.195 1.200 1.205 V

OUT

Rev. C | Page 3 of 12

ADR280

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 2.

Parameter Rating

Supply Voltage 6 V

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +85°C

Junction Temperature Range −65°C to +150°C

Lead Temperature Range (Soldering, 60 Sec) 300°C

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, θJA is

specified for a device soldered in circuit board for surfacemount packages.

Table 3.

Package Type θJA θ

SOT-23 230 146 °C/W

SC70 376 102 °C/W

Unit

JC

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. C | Page 4 of 12

ADR280

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

15

1.20225

1.20200

1.20175

1.20150

(V)

1.20125

OUT

V

1.20100

1.20075

1.20050

1.20025

1.20000

–40 –20 0 20 40 60 80 100

Figure 4. V

15

14

NO LO AD

TEMPERATURE (°C)

vs. Temperature

OUT

03065-006

10

5

3V TO 5V

0

–5

LINE REGUL ATION (ppm/V)

–10

–15

–40 –20 0 20 40 60 80 100

TEMPERATURE (°C)

Figure 6. Line Regulation vs. Temperature

03065-008

13

12

(µA)

IN

I

11

10

9

–40 –20 0 20 40 60 80 100

Figure 5. Supply Current vs. Temperature

VIN=5V

VIN=3V

TEMPERATURE (°C)

1

03065-007

CH1 M 1.00s50.0µV

Figure 7. Noise Voltage Peak-to-Peak, 10 Hz to 10 kHz

03065-009

Rev. C | Page 5 of 12

ADR280

V

www.BDTIC.com/ADI

T

–40

–60

1.2

1.0

0.8

t

S

–80

–100

NOISE POWER DENSITY (dBm)

0 10.0

2.5 5.0 7.5

Figure 8. Output Noise Density Plot (V

–40dB

10dB/DI

0Hz 100kHz

Figure 9. Voltage Noise Density, 0 Hz to 100 kHz

FREQUENCY (kHz)

= 3.6 V, C

+

= 1 μF, CIN = 1 μF)

OUT

0.6

VOLTAGE (V)

0.4

0.2

0

02

24681012141618

3065-010

TIME (ms)

0

03065-012

Figure 10. Settling Time

03065-011

Rev. C | Page 6 of 12

ADR280

V

www.BDTIC.com/ADI

THEORY OF OPERATION

The ADR280 provides the basic core 1.2 V band gap reference.

It contains two NPN transistors, Q9 and Q17, with their emitter

areas scaled in a fixed ratio. The difference in the V

a proportional to absolute temperature (PTAT) voltage that

cancels the complementary to absolute temperature (CTAT) Q9

V

voltage. As a result, a core band gap voltage that is almost a

BE

constant 1.2 V over temperature is generated (see Figure 11).

Pre

cision laser trimming of the internal resistors and other

proprietary circuit techniques are used to enhance the initial

accuracy, temperature curvature, and temperature drift

performance.

produces

BE

R1

R3

Q17 Q9

Q1

Q3

+

R2

I1

R4

PNP3

Q18

R7

R5

R6

R8

R9

Q5

Figure 11. Simplified Architecture

Q2

Q6

R13

R12

Q10

C1

R10

Q7

R11

V

OUT

V–

03065-013

Rev. C | Page 7 of 12

ADR280

V

www.BDTIC.com/ADI

APPLICATIONS INFORMATION

The ADR280 should be decoupled with a 0.1 μF ceramic

capacitor at the output for optimum stability. It is also good

practice to include 0.1 μF ceramic capacitors at the IC supply

pin. These capacitors should be mounted close to their

respective pins (see

The low supply voltage input pin V− can be elevated above

ground; a 1.2 V differential voltage can therefore be established

above V− (see

The ADR280 provides the core 1.2 V band gap voltage and is

able to drive a maximum load of only 100 μA. Users can simply

buffer the output for high current or sink/source current applications, such as ADC or LCD driver references (see

OUT

Users can also tailor any specific need for voltage and dynamics

with an external op amp and discrete components (see Figure 14

a

nd Figure 15). Depending on the specific op amp and PCB

la

yout, it may be necessary to add a compensation capacitor, C2,

to prevent gain peaking and oscillation. The exact value of C2

needed requires some trial and error but usually falls in the

range of a few picofarads.

Figure 12).

0.1µF

0.1µF

Figure 12. Basic Configuration

V+

ADR280

V

OUT

Figure 13).

5V

0.1µF

1.2V + V–

0.1µF

U2

V+

ADR280

V

OUT

Figure 13. Floating References

0.1µF

Figure 14. Buffered Output

V–

V–

U1

V+

ADR280

V

OUT

0.1µF

U2 = AD8541, SC70

AD8601, SOT -23-5

03065-014

2.5V

Figure 14).

V–

03065-015

03065-016

U1

5V

V+

ADR280

V

1.8V

60kΩ ± 0.1%

120kΩ ± 0.1%

5V

1.2V

+

U2

O

C2

2.2pF

R2

R1

V+

AD8541

V–

C1

0.1µF

–

V

OUT

V–

Figure 15. 1.8 V Reference

LOW COST, LOW POWER CURRENT SOURCE

Because of its low power characteristics, the ADR280 can be

converted to a current source with just a setting resistor. In

addition to the ADR280 current capability, the supply voltage

and the load limit the maximum current. The circuit in

roduces 100 μA with 2 V compliance at a 5 V supply. The load

p

current is the sum of I

load; a R

of 13.6 kΩ yields 100 μA of load current.

SET

5V

SET

and I

GND

U1

. I

increases slightly with

GND

V+

ADR280

V–

I

SET

V

R

1.2V

SET

1kΩ

C1

+

0.1µF

–

13.6kΩ

RL

I

L

100µA

OUT

IL=I

I

GND

SET+IGND

Figure 16. Low Cost Current Source

Precision Low Power Current Source

By adding a buffer to redirect the I

can be precisely set by R

5V

R

SET

12kΩ

RL

1kΩ

Figure 17. Precision Low Power Current Source

with the equation IL = 1.2 V/R

SET

0.1µF

–

AD8541

+

I

L

100µA

=1.2V/R

I

L

in Figure 17, a current

GND

U1

V+

ADR280

V–

V

OUT

C2

5V

U2

V+

V–

SET

Figure 16

03065-018

03065-019

SET

.

03065-017

Rev. C | Page 8 of 12

ADR280

www.BDTIC.com/ADI

Boosted Current Source

Adding one more buffer to the previous circuit boosts the

current to the level that is limited only by the buffer U2 current

handling capability (see

R

SET

230Ω

RL

500Ω

Figure 18).

U1

5V

5V

+

U2

V+

–

V–

+

1.2V

–

I

L

5mA

Figure 18. Precision Current Source

V+

ADR280

V

OUT

C1

0.1µF

5V

U3

–

V+

V–

+

= 1.2V/R

I

L

U2 = U3 = AD8542, AD822

SET

V–

03065-020

Negative Reference

A negative reference can be precisely configured without using

any expensive tight tolerance resistors, as shown in Figure 19.

oltage difference between V

The v

and V− is 1.2 V. Since V

OUT

OUT

is at virtual ground, U2 closes the loop by forcing the V− pin to

be the negative reference output.

U1

+5V

0.1µF

C1

V+

V

U2

–

V+

AD8541

V–

+

ADR280

OUT

V–

–1.2V

–V

REF

100 mA load is achievable at a 5 V supply. The higher the

supply voltage, the lower the current handling is because of the

heat generated on the MOSFET. For heavy capacitive loads,

additional buffering is needed at the output to enhance the

transient response.

V

1.2V

REF

U1

C1

0.1µF

V+

ADR280

V

OUT

V–

2.5V/100mA

V

O

RL

25Ω

10.8kΩ ± 0.1%

10kΩ ± 0.1%

5V

M1*

V+

AD8541

V–

+

–

R2

C2

1pF

R1

*M1 = FDB301N, 2N7000, 2N7002, OR EQ UIVALENT .

U2

Figure 20. 2.5 V Boosted Reference

GSM and 3G Mobile Station Applications

The ADR280 voltage reference is ideal for use with analog

baseband ICs in GSM and 3G mobile station applications.

Figure 21 illustrates the use of the ADR280 with the AD6535

GS

M analog baseband. The AD6535 provides all of the data

converters and power management functions needed to

implement a GSM mobile station, including baseband codecs,

audio codecs, voltage regulators, and a battery charger. Besides

low current consumption and a small footprint, the ADR280 is

optimized for excellent PSRR, which is necessary for optimum

AD6535 device performance when the main battery voltage

fluctuates during RF power amplifier activity.

DIGITAL

BASEBAND

AD6535

ANALOG BASE BAND

BASEBAND CODEC

AUDIO CODEC

RADIO

03065-022

–2.7V

03065-021

Figure 19. Negative Reference

Boosted Reference with Scalable Output

A precision user defined output with boosted current capability

can be implemented with the circuit shown in Figure 20. In this

c

ircuit, U2 forces V

to be equal to V

O

× (1 + R2/R1) by regu-

REF

lating the turn-on of M1; the load current is therefore furnished

by the 5 V supply. For higher output voltage, U2 must be changed

and the supply voltage of M1 and U2 must also be elevated and

separated from the U1 input voltage. In this configuration, a

Rev. C | Page 9 of 12

POWER

MANAGEMENT

ADR280

VOLTAGE REFERENCE

03065-023

Figure 21. GSM Mobile Station Application

ADR280

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

3.04

2.90

1.40

1.30

1.20

PIN 1

0.10

0.01

Figure 22. 3-Lead Small Outline Transistor Package [SOT-23-3]

4.10

3.20

3.10

2.90

4.00

3.90

2.05

2.00

1.95

1.00 MIN

1.10

1.00

0.90

3.55

3.50

3.45

0.75 MIN

1.35

1.25

1.15

PIN 1

1.00

0.80

0.10 MAX

0.10 COPLANARIT Y

ALL DIMENSIONS COMPL IANT WI TH EIAJ SC70

1.55

1.50

1.45

8.30

8.00

7.70

DIRECTION O F UNREELI NG

Figure 24. 3-Lead Thin Shrink Small Outline Transistor Package [SC70]

2.80

3

1

1.90 BSC

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS TO-236-AB

2

0.95 BSC

2.64

2.10

0.50

0.30

1.12

0.89

0.60

0.50

0.40

(RT-3)

Dim

ensions shown in millimeters

1.10

1.00

2.80

2.70

2.60

0.90

0.35

0.30

0.25

Figure 23. Tape and Reel Dime

7” REEL 100.00

13” REEL 330.00

20.20

MIN

nsions

(RT-3)

Dimensions shown in millimeters

2.20

2.00

1.80

21

0.65 BSC

2.40

2.10

1.80

1.10

0.80

SEATING

PLANE

0.40

0.10

0.26

0.10

S-3)

(K

0.40

0.25

3

Dimensions shown in millimeters

OR

1.50 MIN

0.30

0.20

0.10

0.20

0.08

14.40 MIN

13.20

13.00

12.80

111505-0

7” REEL 50.00 MIN

OR

13” REEL 100.00 MIN

9.90

8.40

6.90

053006-0

Rev. C | Page 10 of 12

ADR280

www.BDTIC.com/ADI

ORDERING GUIDE

Temperature

Model

ADR280AKS-R2 −40°C to +85°C 3-Lead SC70 KS-3 RBA 1.200 250

ADR280AKS-REEL −40°C to +85°C 3-Lead SC70 KS-3 RBA 1.200 10,000

ADR280AKS-REEL7 −40°C to +85°C 3-Lead SC70 KS-3 RBA 1.200 3,000

ADR280AKSZ-R21 −40°C to +85°C 3-Lead SC70 KS-3 L25 1.200 250

ADR280AKSZ-REEL71 −40°C to +85°C 3-Lead SC70 KS-3 L25 1.200 3,000

ADR280ART-R2 −40°C to +85°C 3-Lead SOT-23 RT-3 RBA 1.200 250

ADR280ART-REEL −40°C to +85°C 3-Lead SOT-23 RT-3 RBA 1.200 10,000

ADR280ART-REEL7 −40°C to +85°C 3-Lead SOT-23 RT-3 RBA 1.200 3,000

ADR280ARTZ-R21 −40°C to +85°C 3-Lead SOT-23 RT-3 L25 1.200 250

ADR280ARTZ-REEL71 −40°C to +85°C 3-Lead SOT-23 RT-3 L25 1.200 3,000

1

Z = RoHS Compliant Part.

Range

Package

Description

Package

Option Branding Output Voltage (V) Ordering Quantity

Rev. C | Page 11 of 12

ADR280

www.BDTIC.com/ADI

NOTES

©2002–2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

C03065-0-4/07(C)

Rev. C | Page 12 of 12

Loading...

Loading...