Ultracompact, Precision

www.BDTIC.com/ADI

10.0 V/5.0 V/2.5 V/3.0 V Voltage References

FEATURES

Ultracompact SC70 and TSOT packages

Low temperature coefficient

8-lead SOIC: 3 ppm/°C

5-lead SC70, 5-lead TSOT: 9 ppm/°C

Initial accuracy ±0.1%

No external capacitor required

Low noise 10 μV p-p (0.1 Hz to 10.0 Hz)

Wide operating range

ADR01: 12.0 V to 40.0 V

ADR02: 7.0 V to 40.0 V

ADR03: 4.5 V to 40.0 V

ADR06: 5.0 V to 40.0 V

High output current 10 mA

Wide temperature range: –40°C to +125°C

ADR01/ADR02/ADR03 pin compatible to industry-

standard REF01/REF02/REF03

APPLICATIONS

Precision data acquisition systems

High resolution converters

Industrial process control systems

Precision instruments

PCMCIA cards

1

ADR01/ADR02/ADR03/ADR06

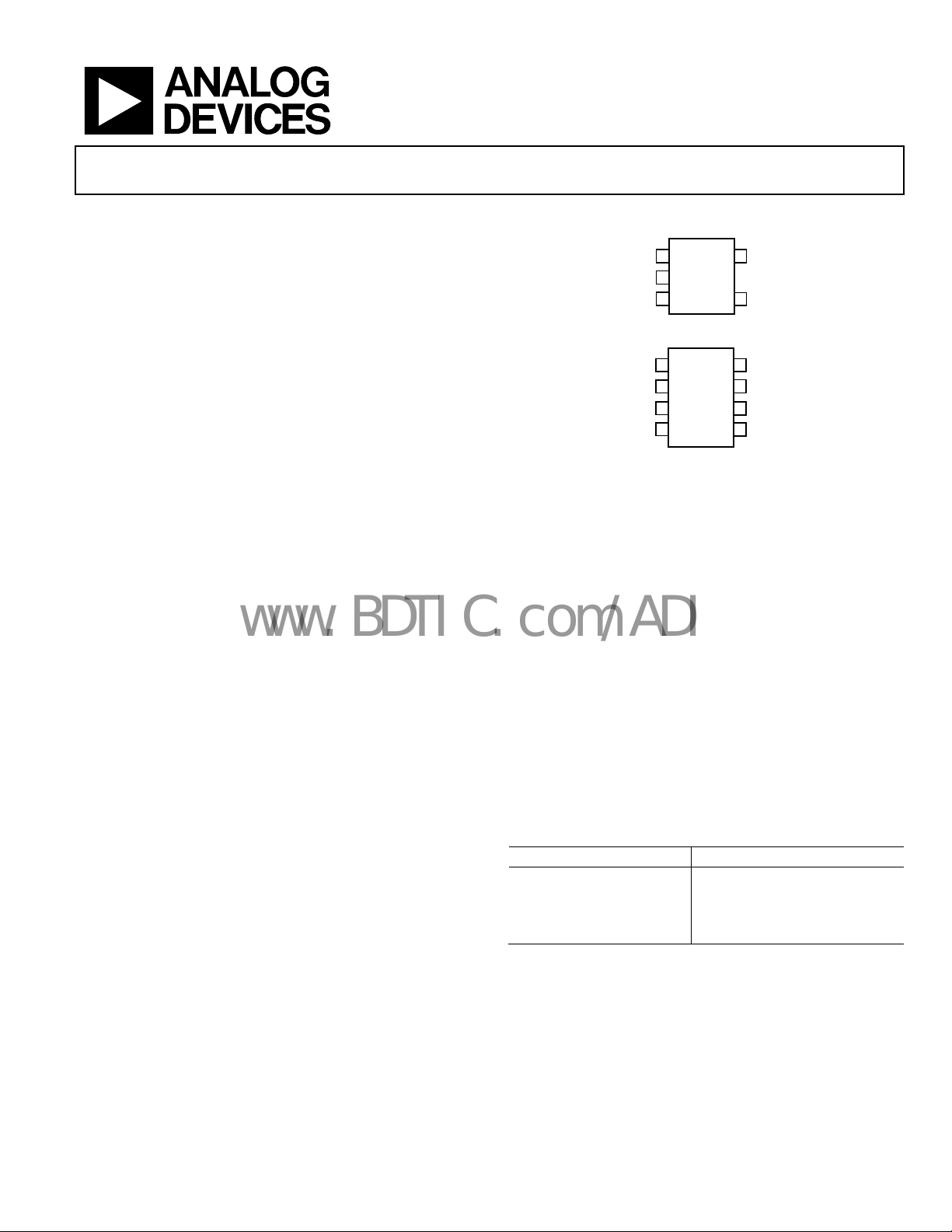

PIN CONFIGURATIONS

A

D

R

1

A

D

R

A

D

R

2

A

D

R

TOP VIEW

3

(Not to Scale)

1

A

D

R

A

D

R

2

A

D

R

A

D

R

3

TOP VIEW

4

(Not to Scale)

01/

02/

03/

06

0

0

0

0

5

TRIM

V

4

OUT

02747-001

8

TP

1

/

/

2

7

NIC

/

3

6

V

6

OUT

5

TRIM

02747-002

TEMP

GND

V

IN

Figure 1. 5-Lead, SC70/TSOT Surface-Mount Packages

TP

V

IN

TEMP

GND

NIC = NO INTERNAL CONNECT

TP = TEST PI N (DO NOT CO NNECT)

Figure 2. 8-Lead, SOIC Surface-Mount Package

GENERAL DESCRIPTION

The ADR01, ADR02, ADR03, and ADR06 are precision 10.0 V,

5.0 V, 2.5 V, and 3.0 V band gap voltage references featuring high

accuracy, high stability, and low power. The parts are housed in

tiny, 5-lead SC70 and TSOT packages, as well as in 8-lead SOIC

versions. The SOIC versions of the ADR01, ADR02, and ADR03

are drop-in replacements

REF02, and REF03. The small footprint and wide operating

range make the ADR0x references ideally suited for generalpurpose and space-constrained applications.

1

to the industry-standard REF01,

The ADR01, ADR02, ADR03, and ADR06 are compact, low

drift voltage references that provide an extremely stable output

voltage from a wide supply voltage range. They are available in

5-lead SC70 and TSOT packages, and 8-lead SOIC packages

with A, B, and C grade selections. All parts are specified over

the extended industrial (–40°C to +125°C) temperature range.

Table 1. Selection Guide

Part Number Output Voltage

ADR01 10.0 V

ADR02 5.0 V

With an external buffer and a simple resistor network, the

TEMP terminal can be used for temperature sensing and

ADR03 2.5 V

ADR06 3.0 V

approximation. A TRIM terminal is provided on the devices for

fine adjustment of the output voltage.

1

ADRO1, ADR02, and ADR03 are component-level compatible with REF01, REF02, and REF03, respectively. No guarantees for syste-level compatibility are implied. SOIC

versions of ADR01/ADR02/ADR03 are pin-to-pin compatible with 8-lead SOIC versions of REF01/REF02/REF03, respectively, with the additional temperature

monitoring function.

Rev. K

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2002–2008 Analog Devices, Inc. All rights reserved.

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

ESD Caution...................................................................................8

Applications ....................................................................................... 1

Pin Configurations ........................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

ADR01 Electrical Characteristics ............................................... 3

ADR02 Electrical Characteristics ............................................... 4

ADR03 Electrical Characteristics ............................................... 5

ADR06 Electrical Characteristics ............................................... 6

Die Electrical Characteristics ...................................................... 7

Absolute Maximum Ratings ............................................................ 8

Thermal Resistance ...................................................................... 8

REVISION HISTORY

2/08—Rev. J to Rev. K

Changes to Terminology Section.................................................... 9

Changes to Ordering Guide .......................................................... 19

Terminology .......................................................................................9

Typical Performance Characteristics ........................................... 10

Applications ..................................................................................... 15

Applying the ADR01/ADR02/ADR03/ADR06 ...................... 15

Negative Reference ..................................................................... 16

Low Cost Current Source .......................................................... 16

Precision Current Source with Adjustable Output ................ 16

Programmable 4 mA to 20 mA Current Transmitter ............ 17

Precision Boosted Output Regulator ....................................... 17

Outline Dimensions ....................................................................... 18

Ordering Guides ......................................................................... 19

8/03—Rev. C to Rev D

Added ADR06 ..................................................................... Universal

Change to Figure 27 ....................................................................... 13

3/07—Rev. I to Rev. J

Renamed Parameters and Definitions Section ............................. 9

Changes to Temperature Monitoring Section ............................ 15

Changes to Ordering Guide .......................................................... 19

7/05—Rev. H to Rev. I

Changes to Table 5 ............................................................................ 7

Updated Outline Dimensions ....................................................... 19

Changes to Ordering Guide .......................................................... 19

12/04—Rev. G to Rev. H

Changes to ADR06 Ordering Guide ............................................ 20

9/04—Rev. F to Rev. G

Changes to Table 2 ............................................................................ 4

Changes to Table 3 ............................................................................ 5

Changes to Table 4 ............................................................................ 6

Changes to Table 5 ............................................................................ 7

Changes to Ordering Guide .......................................................... 19

7/04—Rev. E to Rev. F

Changes to ADR02 Electrical Characteristics, Table 2 ................ 4

Changes to Ordering Guide .......................................................... 19

2/04—Rev. D to Rev. E

Added C grade .................................................................... Universal

Changes to Outline Dimensions ................................................... 19

Updated Ordering Guide ............................................................... 20

Rev. K | Page 2 of 24

6/03—Rev. B to Rev C

Changes to Features Section ............................................................ 1

Changes to General Description Section ....................................... 1

Changes to Figure 2 ........................................................................... 1

Changes to Specifications Section ................................................... 2

Addition of Dice Electrical Characteristics and Layout ............... 6

Changes to Absolute Maximum Ratings Section .......................... 7

Updated SOIC (R-8) Outline Dimensions .................................. 19

Changes to Ordering Guide .......................................................... 20

2/03—Rev. A to Rev. B

Added ADR03 ..................................................................... Universal

Added TSOT-5 (UJ) Package ............................................ Universal

Updated Outline Dimensions ....................................................... 18

12/02—Rev. 0 to Rev. A

Changes to Features Section ............................................................ 1

Changes to General Description ..................................................... 1

Table I deleted .................................................................................... 1

Changes to ADR01 Specifications ................................................... 2

Changes to ADR02 Specifications ................................................... 3

Changes to Absolute Maximum Ratings Section .......................... 4

Changes to Ordering Guide ............................................................. 4

Updated Outline Dimensions ....................................................... 12

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

SPECIFICATIONS

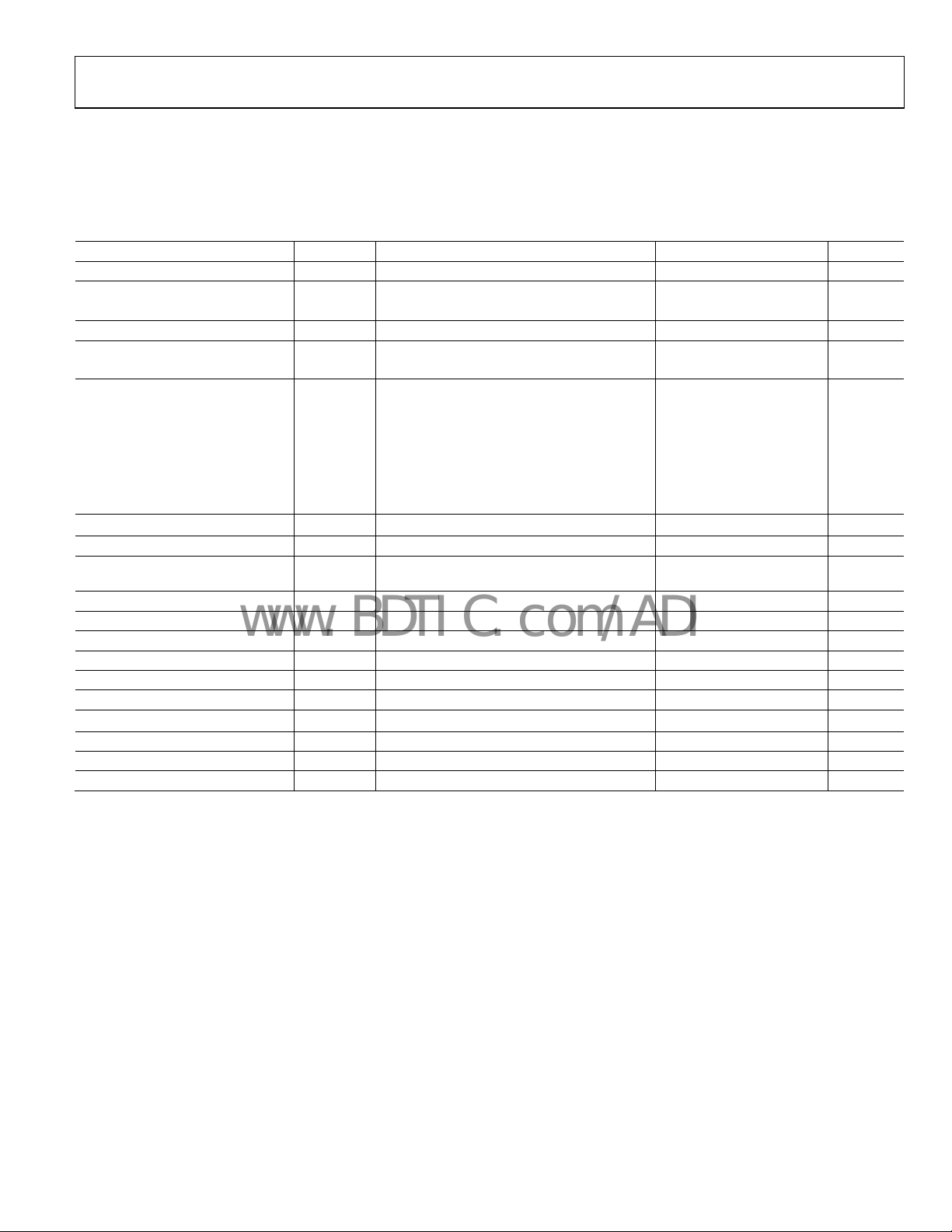

ADR01 ELECTRICAL CHARACTERISTICS

VIN = 12.0 V to 40.0 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A and C grades 9.990 10.000 10.010 V

INITIAL ACCURACY V

OUTPUT VOLTAGE VO B grade 9.995 10.000 10.005 V

INITIAL ACCURACY V

TEMPERATURE COEFFICIENT TCVO

SUPPLY VOLTAGE HEADROOM

LINE REGULATION ∆VO/∆VIN VIN = 12.0 V to 40.0 V, –40°C < TA < +125°C 7 30 ppm/V

LOAD REGULATION ∆VO/∆I

QUIESCENT CURRENT IIN No load, –40°C < TA < +125°C 0.65 1 mA

VOLTAGE NOISE e

VOLTAGE NOISE DENSITY eN 1 kHz 510 nV/√Hz

TURN-ON SETTLING TIME tR 4 μs

LONG-TERM STABILITY

1

∆V

OUTPUT VOLTAGE HYSTERESIS ∆V

RIPPLE REJECTION RATIO RRR fIN = 10 kHz

SHORT CIRCUIT TO GND ISC 30 mA

VOLTAGE OUTPUT AT TEMP PIN V

TEMPERATURE SENSITIVITY TCV

1

The long-term stability specification is noncumulative. The drift in subsequent 1000 hour periods is significantly lower than in the first 1000 hour period.

A and C grades 10 mV

OERR

0.1 %

B grade 5 mV

OERR

0.05 %

A grade, 8-lead SOIC, −40°C < T

< +125°C

A

3 10 ppm/°C

A grade, 5-lead TSOT, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –40°C < TA < +125°C 25 ppm/°C

B grade, 8-lead SOIC, –40°C < TA < +125°C 1 3 ppm/°C

B grade, 5-lead TSOT, –40°C < TA < +125°C 9 ppm/°C

B grade, 5-lead SC70, –40°C < TA < +125°C 9 ppm/°C

C grade, 8-lead SOIC, –40°C < TA < +125°C 10 40 ppm/°C

VIN − VO

0.1 Hz to 10.0 Hz 20 μV p-p

N p-p

1000 hours 50 ppm

O

O_HYS

550 mV

TEMP

TEMP

2 V

LOAD

= 0 mA to 10 mA, –40°C < TA < +125°C,

I

LOAD

V

= 15.0 V

IN

40 70 ppm/mA

70 ppm

−75

dB

1.96 mV/°C

Rev. K | Page 3 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

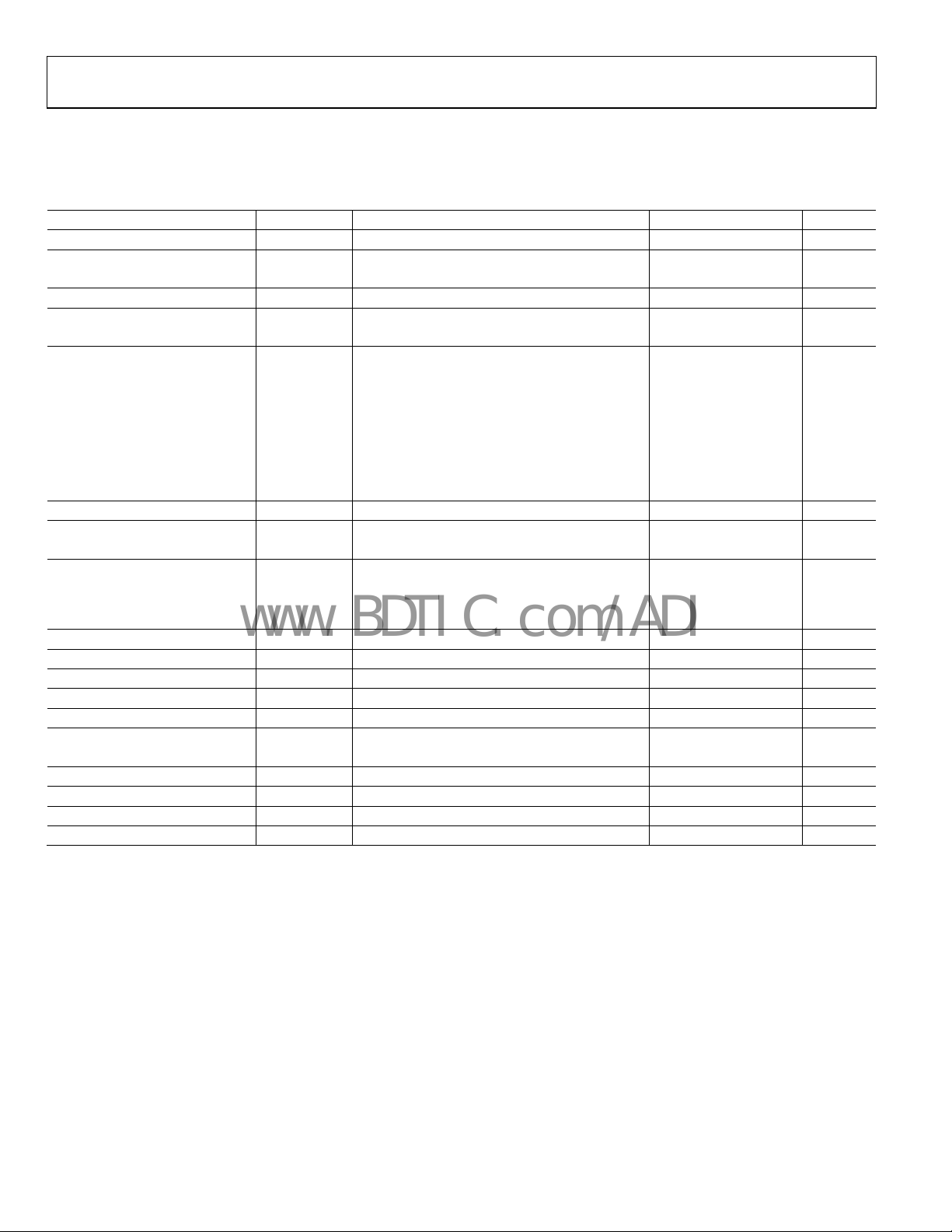

ADR02 ELECTRICAL CHARACTERISTICS

VIN = 7.0 V to 40.0 V, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A and C grades 4.995 5.000 5.005 V

INITIAL ACCURACY V

OUTPUT VOLTAGE VO B grade 4.997 5.000 5.003 V

INITIAL ACCURACY V

TEMPERATURE COEFFICIENT T

SUPPLY VOLTAGE HEADROOM VIN − VO 2 V

LINE REGULATION ∆VO/∆VIN V

V

LOAD REGULATION ∆VO/∆I

QUIESCENT CURRENT IIN No load, –40°C < TA < +125°C 0.65 1 mA

VOLTAGE NOISE eN

VOLTAGE NOISE DENSITY eN 1 kHz 230 nV/√Hz

TURN-ON SETTLING TIME tR 4 μs

LONG-TERM STABILITY

1

∆V

OUTPUT VOLTAGE HYSTERESIS ∆V

–55°C < TA < +125°C 80 ppm

RIPPLE REJECTION RATIO RRR fIN = 10 kHz –75 dB

SHORT CIRCUIT TO GND ISC 30 mA

VOLTAGE OUTPUT AT TEMP PIN V

TEMPERATURE SENSITIVITY TCV

1

The long-term stability specification is noncumulative. The drift in subsequent 1000 hour periods is significantly lower than in the first 1000 hour period.

A and C grades 5 mV

OERR

0.1 %

B grade 3 mV

OERR

0.06 %

A grade, 8-lead SOIC, –40°C < TA < +125°C 3 10 ppm/°C

CVO

A grade, 5-lead TSOT, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –55°C < TA < +125°C 30 ppm/°C

B grade, 8-lead SOIC, –40°C < TA < +125°C 1 3 ppm/°C

B grade, 5-lead TSOT, –40°C < TA < +125°C 9 ppm/°C

B grade, 5-lead SC70, –40°C < TA < +125°C 9 ppm/°C

C grade, 8-lead SOIC, –40°C < TA < +125°C 10 40 ppm/°C

= 7.0 V to 40.0 V, –40°C < TA < +125°C 7 30 ppm/V

IN

= 7.0 V to 40.0 V, –55°C < TA < +125°C 7 40 ppm/V

IN

LOAD

0.1 Hz to 10.0 Hz 10 μV p-p

p-p

1000 hours 50 ppm

O

70 ppm

O_HYS

550 mV

TEMP

1.96 mV/°C

TEMP

= 0 mA to 10 mA, –40°C < TA < +125°C,

I

LOAD

V

= 10.0 V

IN

= 0 mA to 10 mA, –55°C < TA < +125°C,

I

LOAD

= 10.0 V

V

IN

40 70 ppm/mA

45 80 ppm/mA

Rev. K | Page 4 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

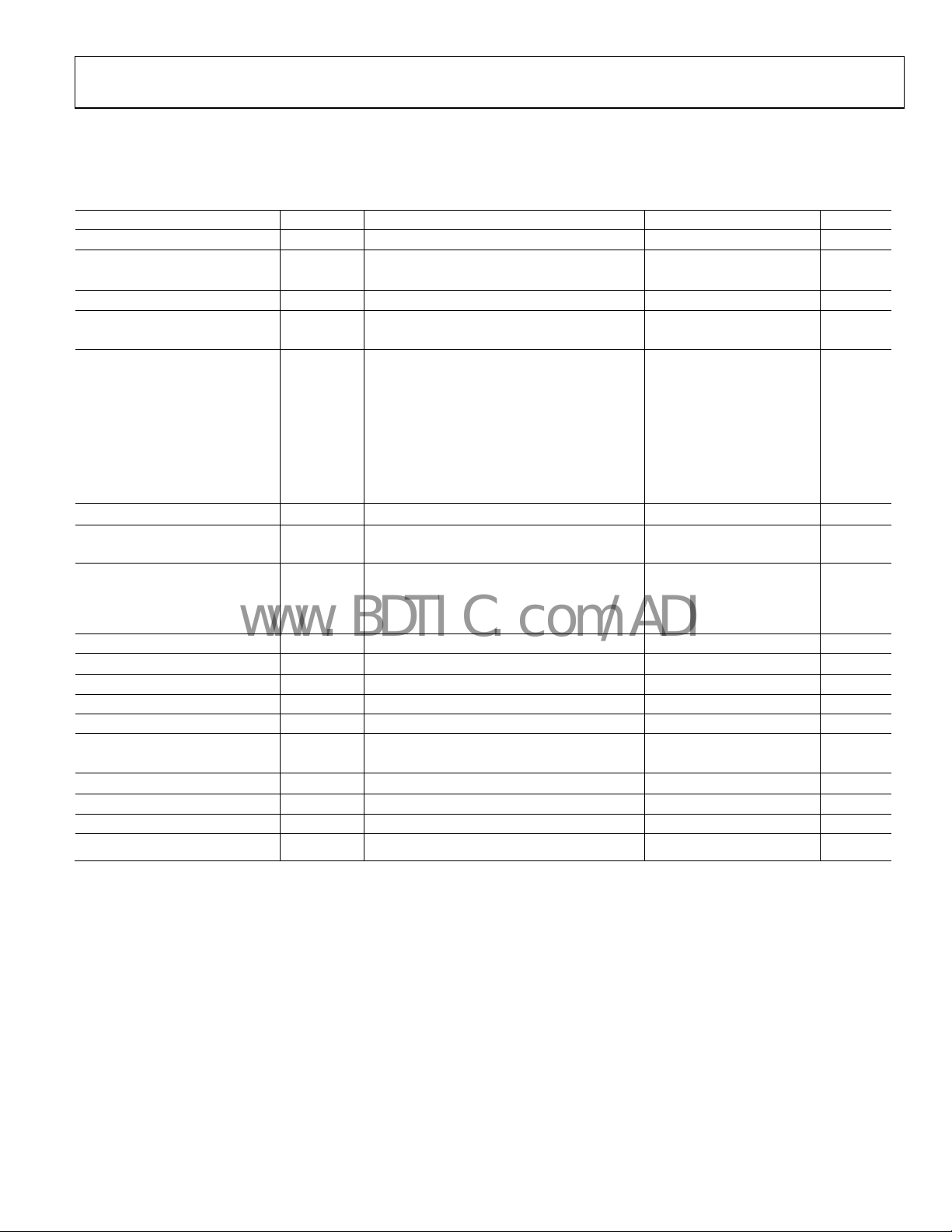

ADR03 ELECTRICAL CHARACTERISTICS

VIN = 4.5 V to 40.0 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A and C grades 2.495 2.500 2.505 V

INITIAL ACCURACY V

OUTPUT VOLTAGE VO B grades 2.4975 2.5000 2.5025 V

INITIAL ACCURACY V

TEMPERATURE COEFFICIENT TCVO A grade, 8-lead SOIC, –40°C < TA < +125°C 3 10 ppm/°C

SUPPLY VOLTAGE HEADROOM

LINE REGULATION ∆VO/∆VIN VIN = 4.5 V to 40.0 V, –40°C < TA < +125°C 7 30 ppm/V

LOAD REGULATION ∆ VO/∆I

QUIESCENT CURRENT IIN No load, –40°C < TA < +125°C 0.65 1 mA

VOLTAGE NOISE e

VOLTAGE NOISE DENSITY eN 1 kHz 230 nV/√Hz

TURN-ON SETTLING TIME tR 4 μs

LONG-TERM STABILITY

1

∆V

OUTPUT VOLTAGE HYSTERESIS ∆V

RIPPLE REJECTION RATIO RRR fIN = 10 kHz –75 dB

SHORT CIRCUIT TO GND ISC 30 mA

VOLTAGE OUTPUT AT TEMP PIN V

TEMPERATURE SENSITIVITY TCV

1

The long-term stability specification is noncumulative. The drift in subsequent 1000 hour periods is significantly lower than in the first 1000 hour period.

A and C grades 5 mV

OERR

0.2 %

B grades 2.5 mV

OERR

0.1 %

A grade, 5-lead TSOT, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –55°C < TA < +125°C 30 ppm/°C

B grade, 8-lead SOIC, –40°C < TA < +125°C 1 3 ppm/°C

B grade, 5-lead TSOT, –40°C < TA < +125°C 9 ppm/°C

B grade, 5-lead SC70, –40°C < TA < +125°C 9 ppm/°C

C grade, 8-lead SOIC, –40°C < TA < +125°C 10 40 ppm/°C

VIN − VO

2 V

VIN = 4.5 V to 40.0 V, –55°C < TA < +125°C 7 40 ppm/V

LOAD

0.1 Hz to 10.0 Hz 6 μV p-p

N p-p

1000 hours 50 ppm

O

70 ppm

O_HYS

= 0 mA to 10 mA, –40°C < TA < +125°C,

I

LOAD

= 7.0 V

V

IN

= 0 mA to 10 mA, –55°C < TA < +125°C,

I

LOAD

V

= 7.0 V

IN

25 70 ppm/mA

45 80 ppm/mA

–55°C < TA < +125°C 80 ppm

550 mV

TEMP

1.96 mV/°C

TEMP

Rev. K | Page 5 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ADR06 ELECTRICAL CHARACTERISTICS

VIN = 5.0 V to 40.0 V, TA = 25°C, unless otherwise noted.

Table 5.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE VO A and C grades 2.994 3.000 3.006 V

INITIAL ACCURACY V

OUTPUT VOLTAGE VO B grade 2.997 3.000 3.003 V

INITIAL ACCURACY V

TEMPERATURE COEFFICIENT TCVO A grade, 8-lead SOIC, –40°C < TA < +125°C 3 10 ppm/°C

SUPPLY VOLTAGE HEADROOM VIN – VO 2 V

LINE REGULATION ∆VO/∆VIN VIN = 5.0 V to 40.0 V, –40°C < TA < +125°C 7 30 ppm/V

LOAD REGULATION ∆VO/∆I

QUIESCENT CURRENT IIN No load, –40°C < TA < +125°C 0.65 1 mA

VOLTAGE NOISE e

VOLTAGE NOISE DENSITY eN 1 kHz 510 nV/√Hz

TURN-ON SETTLING TIME tR 4 μs

LONG-TERM STABILITY

1

∆V

OUTPUT VOLTAGE HYSTERESIS ∆V

RIPPLE REJECTION RATIO RRR fIN = 10 kHz –75 dB

SHORT CIRCUIT TO GND ISC 30 mA

VOLTAGE OUTPUT AT TEMP PIN V

TEMPERATURE SENSITIVITY TCV

1

The long-term stability specification is noncumulative. The drift in subsequent 1000 hour periods is significantly lower than in the first 1000 hour period.

A and C grades 6 mV

OERR

0.2 %

B grade 3 mV

OERR

0.1 %

A grade, 5-lead TSOT, –40°C < TA < +125°C 25 ppm/°C

A grade, 5-lead SC70, –40°C < TA < +125°C 25 ppm/°C

B grade, 8-lead SOIC, –40°C < TA < +125°C 1 3 ppm/°C

B grade, 5-lead TSOT, –40°C < TA < +125°C 9 ppm/°C

B grade, 5-lead SC70, –40°C < TA < +125°C 9 ppm/°C

C grade, 8-lead SOIC, –40°C < TA < +125°C 10 40 ppm/°C

= 0 mA to 10 mA, –40°C < TA < +125°C,

I

LOAD

LOAD

V

= 7.0 V

IN

0.1 Hz to 10.0 Hz 10 μV p-p

N p-p

1000 hours 50 ppm

O

70 ppm

O_HYS

550 mV

TEMP

1.96 mV/°C

TEMP

40 70 ppm/mA

Rev. K | Page 6 of 24

ADR01/ADR02/ADR03/ADR06

V

www.BDTIC.com/ADI

DIE ELECTRICAL CHARACTERISTICS

VIN = up to 40.0 V, TA = 25°C, unless otherwise noted.

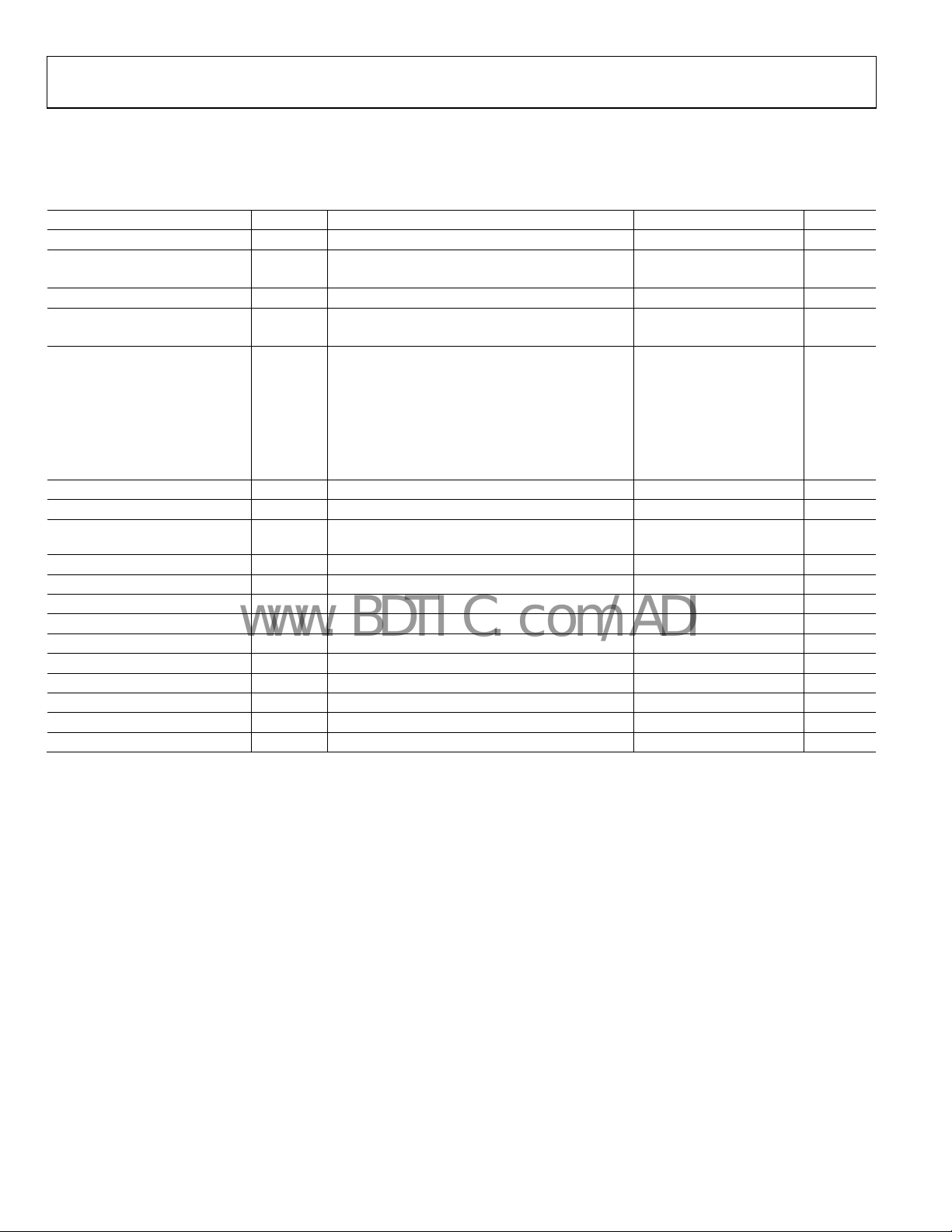

Table 6.

Parameter Symbol Conditions Min Typ Max Unit

OUTPUT VOLTAGE

ADR01NBC VO 25°C 9.995 10.004 10.005 V

ADR03BNC VO 25°C 2.4975 2.501 2.5025 V

TEMPERATURE COEFFICIENT TCVO –40°C < TA < +125°C 10 ppm/°C

LINE REGULATION

ADR01NBC ∆VO/∆VIN V

ADR03BNC ∆VO/∆VIN V

LOAD REGULATION ∆VO/∆I

I

LOAD

QUIESCENT CURRENT IIN No load 0.65 mA

VOLTAGE NOISE e

0.1 Hz to 10.0 Hz 25 μV p-p

N p-p

= 15.0 V to 40.0 V 7 ppm/V

IN

= 4.5 V to 40.0 V 7 ppm/V

IN

= 0 to 10 mA 40 ppm/mA

LOAD

TEMP

IN

GND

TRIM

DIE SIZ E: 0.83mm × 1. 01mm

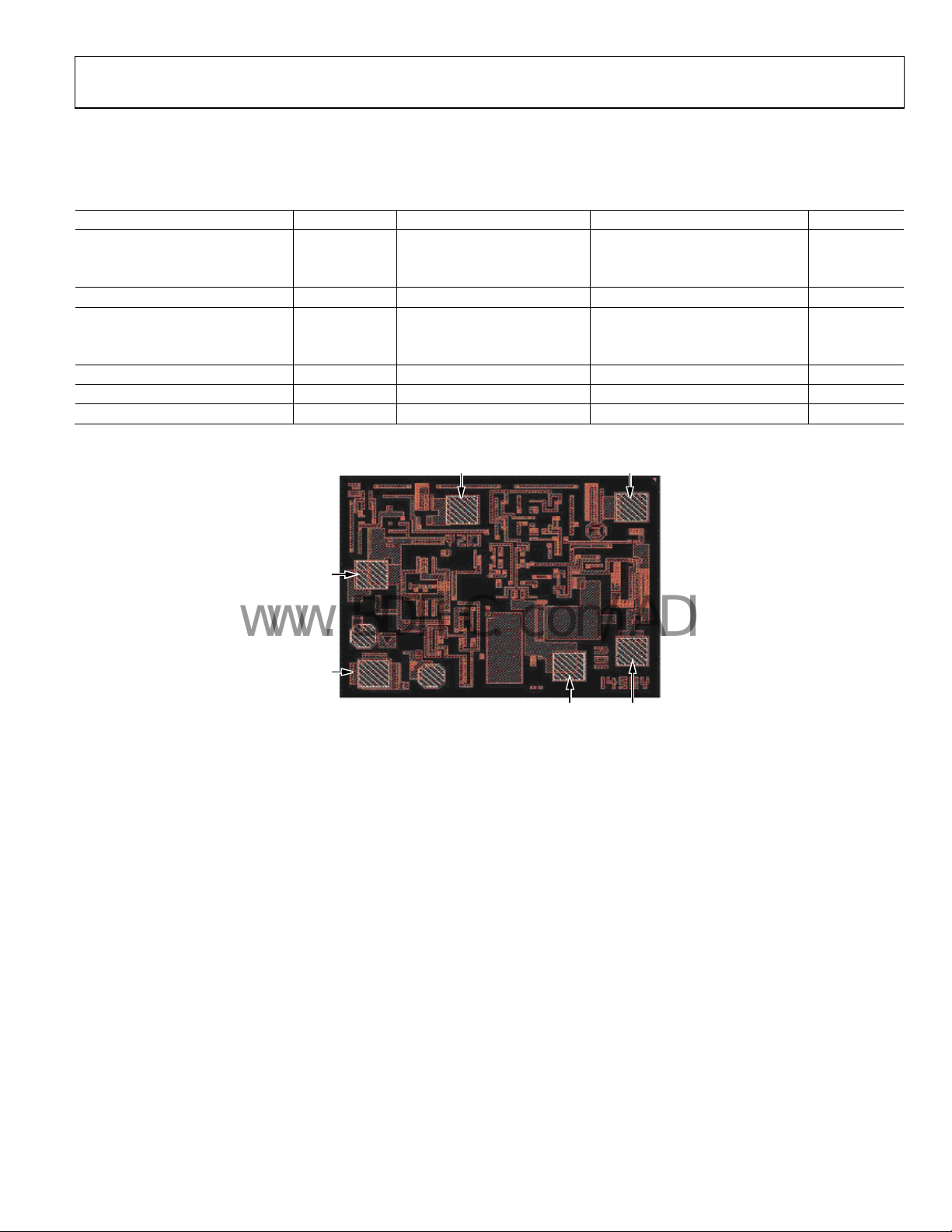

Figure 3. Die Layout

V

OUT

(SENSE)

V

OUT

(FORCE)

02747-003

Rev. K | Page 7 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Ratings at 25°C, unless otherwise noted.

Table 7.

Parameter Rating

Supply Voltage 40.0 V

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range –65°C to +150°C

Operating Temperature Range –40°C to +125°C

Junction Temperature Range –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 8. Thermal Resistance

Package Type θJA θ

5-Lead SC70 (KS-5) 376 189 °C/W

5-Lead TSOT (UJ-5) 230 146 °C/W

8-Lead SOIC (R-8) 130 43 °C/W

ESD CAUTION

Unit

JC

Rev. K | Page 8 of 24

ADR01/ADR02/ADR03/ADR06

(

www.BDTIC.com/ADI

TERMINOLOGY

Temperature Coefficient

The change of output voltage with respect to operating temperature changes normalized by the output voltage at 25°C. This

parameter is expressed in ppm/°C and can be determined by the

following equation:

TCV

ppm

⎤

⎡

O

⎥

⎢

°

⎦

⎣

O

=

()

O

() ()

TVTV

−

2

C25C

1

O

()

TTV

−×°

12

6

10

×

where:

V

(25°C) = VO at 25°C.

O

V

) = VO at Temperature 1.

O(T1

V

) = VO at Temperature 2.

O(T2

Line Regulation

The change in output voltage due to a specified change in input

voltage. This parameter accounts for the effects of self-heating. Line

regulation is expressed in either percent per volt, parts-per-million

per volt, or microvolts per volt change in input voltage.

Load Regulation

The change in output voltage due to a specified change in load

current. This parameter accounts for the effects of self-heating.

Load regulation is expressed in either microvolts per milliampere,

parts-per-million per milliampere, or ohms of dc output resistance.

Long-Term Stability

Typical shift of output voltage at 25°C on a sample of parts

subjected to a test of 1000 hours at 25°C.

)()(

tVtVV −=Δ

0

OO

ppmV

][ ×

O

=Δ

1

O

tVtV

)()(

−

0

O

O

tV

)(

0

O

6

1

10

where:

V

) = VO at 25°C at Time 0.

O(t0

) = VO at 25°C after 100 hours of operation at 25°C.

V

O(t1

The majority of the shift is seen in the first 200 hours, and as

time goes by, the drift decreases significantly. This drift is much

smaller for the subsequent 1000 hours of time points than for

the first.

Thermal Hysteresis

The change of output voltage after the device is cycled through

temperatures from +25°C to –40°C to +125°C and back to

+25°C. This is a typical value from a sample of parts put

through such a cycle.

V

= VO(25°C) − V

O_HYS

[]

ppmV

O_HYS

=

O_TC

C25

O

()

V

O

)

VV

−°

O_TC

C25

°

6

10

×

where:

V

(25°C) = VO at 25°C.

O

V

= VO at 25°C after temperature cycle at +25°C to −40°C

O_TC

to +125°C and back to +25°C.

Input Capacitor

Input capacitors are not required on the ADR01/ADR02/

ADR03/ADR06. There is no limit to the value of the capacitor

used on the input, but a 1 μF to 10 μF capacitor on the input

improves transient response in applications where the supply

suddenly changes. An additional 0.1 μF in parallel also helps to

reduce noise from the supply.

Output Capacitor

The ADR01/ADR02/ADR03/ADR06 do not require output

capacitors for stability under any load condition. An output

capacitor, typically 0.1 μF, filters out any low-level noise voltage

and does not affect the operation of the part. Alternatively, the

load transient response can be improved with an additional

1 μF to 10 μF output capacitor in parallel. A capacitor here acts

as a source of stored energy for a sudden increase in load

current. The only parameter that degrades by adding an output

capacitor is the turn-on time, and it depends on the size of the

capacitor chosen.

Rev. K | Page 9 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

10.010

3.002

10.005

10.000

(V)

OUT

V

9.995

9.990

9.985

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

Figure 4. ADR01 Typical Output Voltage vs. Temperature

5.008

5.004

(V)

5.000

OUT

V

4.996

3.001

(V)

3.000

OUT

V

2.999

2.998

–40 –25 –10 5 20 35 50 65 80 95 110 125

02747-004

TEMPERATURE (°C)

02747-007

Figure 7. ADR06 Typical Output Voltage vs. Temperature

0.8

0.7

0.6

SUPPLY CURRENT (mA)

0.5

+125°C

+25°C

–40°C

4.992

–40 –25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

Figure 5. ADR02 Typical Output Voltage vs. Temperature

2.502

2.501

(V)

2.500

OUT

V

2.499

2.498

–40

–25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE (°C)

Figure 6. ADR03 Typical Output Voltage vs. Temperature

0.4

12 2816 20 24 32 36 40

02747-005

INPUT VOLTAGE (V)

02747-008

Figure 8. ADR01 Supply Current vs. Input Voltage

0.8

0.7

0.6

SUPPLY CURRENT (mA)

0.5

0.4

02747-006

12 2816 20 24 32 36 408

+125°C

+25°C

–40°C

INPUT VOLTAGE (V)

02747-009

Figure 9. ADR02 Supply Current vs. Input Voltage

Rev. K | Page 10 of 24

ADR01/ADR02/ADR03/ADR06

A

www.BDTIC.com/ADI

0.85

0.80

0.75

0.70

0.65

0.60

0.55

SUPPLY CURRENT (mA)

0.50

0.45

0.40

+125°C

+25°C

–40°C

5

10

20 25 30

15

INPUT VOLTAGE (V)

40

35

02747-010

50

40

30

20

10

0

LOAD REGULATION (ppm/mA)

–10

–20

V

= 8V

IN

0–40

= 40V

V

IN

25

TEMPERATURE (° C)

IL = 0mA TO 5mA

85 125

02747-013

Figure 10. ADR03 Supply Current vs. Input Voltage

0.80

0.75

0.70

0.65

0.60

0.55

SUPPLY CURRENT (mA)

0.50

0.45

0.40

5

10

+125°C

+25°C

20

15

INPUT VOLTAG E (V)

Figure 11. ADR06 Supply Current vs. Input Voltage

40

30

20

10

0

–10

–20

LOAD REGULATION (ppm/mA)

–30

–40

V

IN

= 40V

V

= 14V

IN

25

TEMPERATURE ( °C)

–40°C

25

500–40

30

35

IL = 0mA TO 10mA

85 125

Figure 13. ADR02 Load Regulation vs. Temperature

60

IL = 0mA TO 10mA

50

40

30

20

LOAD REGULATION (ppm/mA)

10

0

–40

40

02747-011

–25 –10

5

35

20

TEMPERATURE (° C)

VIN = 40V

50 65

VIN = 7V

80

125

110

95

02747-014

Figure 14. ADR03 Load Regulation vs. Temperature

40

IL = 0mA TO 10mA

30

VIN = 40V

20

10

TION (ppm/mA)

0

–10

LOAD REGUL

–20

–30

–40 –25

02747-012

520355065

–10

VIN = 7V

TEMPERATURE (°C)

80

95 110

125

02747-015

Figure 12. ADR01 Load Regulation vs. Temperature

Rev. K | Page 11 of 24

Figure 15. ADR06 Load Regulation vs. Temperature

ADR01/ADR02/ADR03/ADR06

A

A

A

A

A

www.BDTIC.com/ADI

2

0

VIN = 14V TO 40V

10

VIN = 6V TO 40V

8

–2

TION (ppm/V)

–4

–6

LINE REGUL

–8

–10

–40

–25

–10

5

35

20

TEMPERATURE (°C)

50

Figure 16. ADR01 Line Regulation vs. Temperature

8

4

TION (ppm/V)

0

–4

LINE REGUL

80

65

VIN = 8V TO 40V

6

4

TION (ppm/V)

2

0

LINE REGUL

–2

–4

–40

125

110

95

02747-016

–25

–10

5

35

20

TEMPERATURE (°C)

50

80

65

95

110

125

2747-019

Figure 19. ADR06 Line Regulation vs. Temperature

5

4

3

L VOLTA GE ( V )

2

–40°C

DIFFERENTI

1

+125°C

+25°C

–8

–40

–25

–10

5

35

20

TEMPERATURE (°C)

50

Figure 17. ADR02 Line Regulation vs. Temperature

4

2

TION (ppm/mV)

0

–2

LINE REGUL

–4

–40

–25 –10

520355065

TEMPERATURE (°C)

Figure 18. ADR03 Line Regulation vs. Temperature

80

65

80

110

95

VIN = 5V TO 40V

95 110

125

125

0

02747-017

4602

LOAD CURRENT (mA)

81

0

02747-020

Figure 20. ADR01 Minimum Input-Output

Voltage Differential vs. Load Current

8

4

+125°C

2

DIFFERENTIAL VOLTAGE (V)

0

0

02747-018

–40°C

2

LOAD CURRENT (mA)

+25°C

46

8

10

2747-021

Figure 21. ADR02 Minimum Input-Output

Voltage Differential vs. Load Current

Rev. K | Page 12 of 24

ADR01/ADR02/ADR03/ADR06

A

A

T

V

V

www.BDTIC.com/ADI

6

5

4

3

LVOLTAGE (V)

2

–40°C

DIFFERENTI

1

0

4602

LOAD CURRENT (mA)

Figure 22. ADR03 Minimum Input-Output

Voltage Differential vs. Load Current

4.5

4.0

3.5

3.0

AGE (V)

2.5

LVOL

2.0

1.5

1.0

DIFFERENTI

0.5

0

0246

LOAD CURRENT (mA)

Figure 23. ADR06 Minimum Input-Output

Voltage Differential vs. Load Current

0.70

T

= 25°C

A

0.65

+125°C

81

+125°C

8

+25°C

+25°C

–40°C

0

2747-022

10

02747-023

1µV/DI

TIME (1s/DIV)

Figure 25. ADR02 Typical Noise Voltage 0.1 Hz to 10.0 Hz

50µV/DI

TIME (1ms/DIV)

Figure 26. ADR02 Typical Noise Voltage 10 Hz to 10 kHz

V

5V/DIV

OUT

10V

8V

02747-025

02747-026

0.60

0.55

QUIESCENT CURRENT (mA)

0.50

0

246

LOAD CURRENT (mA)

8

10

2747-024

Figure 24. ADR01 Quiescent Current vs. Load Current

Rev. K | Page 13 of 24

NO LOAD CAPACITOR

NO INPUT CAPACITOR

TIME (2ms/DIV)

Figure 27. ADR02 Line Transient Response

02747-027

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

NO LOAD CAPACITOR

VIN5V/DIV

CIN = 0.01µF

NO LOAD CAPACITOR

VIN10V/DIV

LOAD OFF

TIME (1ms/DIV)

Figure 28. ADR02 Load Transient Response

C

= 100nF

LOAD

LOAD OFF

TIME (1ms/DIV)

Figure 29. ADR02 Load Transient Response

LOAD ON

V

OUT

LOAD = 5mA

VIN5V/DIV

LOAD ON

V

OUT

LOAD = 5mA

100mV/DIV

100mV/DIV

V

5V/DIV

OUT

02747-028

TIME (4µs/DIV)

02747-031

Figure 31. ADR02 Turn-On Response

VIN10V/DIV

CL = 0.01µF

NO INPUT CAPACITOR

V

5V/DIV

OUT

02747-029

TIME (4µs/DIV)

02747-032

Figure 32. ADR02 Turn-Off with No Input Capacitor

CIN = 0.01µF

NO LOAD CAPACITOR

TIME (4µs/DIV)

Figure 30. ADR02 Turn-Off Response

VIN10V/DIV

V

5V/DIV

OUT

02747-030

Rev. K | Page 14 of 24

CL = 0.01µF

NO INPUT CAPACITOR

TIME (4µs/DIV)

VIN10V/DIV

V

5V/DIV

OUT

Figure 33. ADR02 Turn-Off with No Input Capacitor

02747-033

ADR01/ADR02/ADR03/ADR06

V

V

www.BDTIC.com/ADI

APPLICATIONS

The ADR01/ADR02/ADR03/ADR06 are high precision, low

drift 10.0 V, 5.0 V, 2.5 V, and 3.0 V voltage references available

in an ultracompact footprint. The 8-lead SOIC versions of the

devices are drop-in replacements of the REF01/REF02/REF03

sockets with improved cost and performance.

These devices are standard band gap references (see Figure 35).

The band gap cell contains two NPN transistors (Q18 and Q19)

that differ in emitter area by 2×. The difference in their V

BE

produces a proportional-to-absolute temperature current

(PTAT) in R14, and, when combined with the V

produces a band gap voltage, V

, that is almost constant in

BG

of Q19,

BE

temperature. With an internal op amp and the feedback

network of R5 and R6, V

is set precisely at 10.0 V, 5.0 V, 2.5 V,

O

and 3.0 V for the ADR01, ADR02, ADR06, and ADR03,

respectively. Precision laser trimming of the resistors and other

proprietary circuit techniques are used to further enhance the

initial accuracy, temperature curvature, and drift performance

of the ADR01/ADR02/ADR03/ADR06.

The PTAT voltage is made available at the TEMP pin of the

ADR01/ADR02/ADR03/ADR06. It has a stable 1.96 mV/°C

temperature coefficient, such that users can estimate the

temperature change of the device by knowing the voltage

change at the TEMP pin.

APPLYING THE ADR01/ADR02/ADR03/ADR06

The devices can be used without any external components to

achieve the specified performance. Because of the internal op

amp amplifying the band gap cell to 10.0 V/5.0 V/2.5 V/3.0 V,

power supply decoupling helps the transient response of the

ADR01/ADR02/ADR03/ADR06. As a result, a 0.1 μF ceramic

type decoupling capacitor should be applied as close as possible

to the input and output pins of the device. An optional 1 μF to

10 μF bypass capacitor can also be applied at the V

maintain the input under transient disturbance.

Output Adjustment

The ADR01/ADR02/ADR03/ADR06 trim terminal can be used

to adjust the output voltage over a nominal voltage. This feature

allows a system designer to trim system errors by setting the

reference to a voltage other than 10.0 V/5.0 V/2.5 V/3.0 V. For

finer adjustment, add a series resistor of 470 kΩ. With the configuration shown in Figure 36, the ADR01 can be adjusted from

9.70 V to 10.05 V, the ADR02 can be adjusted from 4.95 V to

5.02 V, the ADR06 can be adjusted from 2.8 V to 3.3 V, and the

ADR03 can be adjusted from 2.3 V to 2.8 V. Adjustment of the

output does not significantly affect the temperature performance

of the device, provided the temperature coefficients of the resistors are relatively low.

node to

IN

IN

C1

0.1µF

Figure 34. Basic Configuration

R1 R2 R3

Q1 Q2 Q7 Q8

D3

Q12

R14

R17

R27

R13

Q14

Q15

1×

Q19

Q16 Q17

R32

R24

R11

TEMP

R12

2×

Q18

Figure 35. Simplified Schematic Diagram

ADR01/

ADR02/

ADR03/

V

IN

ADR06

V

TEMP

Figure 36. Optional Trim Adjustment

Temperature Monitoring

As described at the end of the Applications section, the ADR01/

ADR02/ADR03/ADR06 provide a TEMP output (Pin 1 in Figure 1

and Pin 3 in Figure 2) that varies linearly with temperature. This

output can be used to monitor the temperature change in the

system. The voltage at V

and the temperature coefficient is approximately 1.96 mV/°C

(see Figure 37). A voltage change of 39.2 mV at the TEMP pin

corresponds to a 20°C change in temperature.

U1

ADR01/

ADR02/

ADR03/

ADR06

V

V

OUT

IN

TEMP

TRIM

GND

Q3

Q13

IN

GND

TEMP

D1

D2

Q4

C1

R41

U1

V

OUT

TRIM

R1

470kΩ

is approximately 550 mV at 25°C,

Q20

C2

0.1µF

Q23

I1

R42

V

V

POT

10kΩ

R2

1kΩ

O

Q9

R5

BG

R6

V

O

02747-035

Q10

02747-036

R20

GND

IN

V

O

TRIM

R4

02747-034

Rev. K | Page 15 of 24

ADR01/ADR02/ADR03/ADR06

V

V

×

V

www.BDTIC.com/ADI

0.80

V

= 15V

IN

SAMPLE SIZE = 5

0.75

0.70

0.65

(V)

0.60

TEMP

V

0.55

0.50

0.45

0.40

–25

0–50

TEMPERATURE (°C)

ΔV

TEMP

/ΔT ≈ 1.96mV/°C

12525 50 75 100

02747-037

Figure 37. Voltage at TEMP Pin vs. Temperature

The TEMP function is provided as a convenience rather than a

precise feature. Because the voltage at the TEMP node is

acquired from the band gap core, current pulling from this pin

has a significant effect on V

. Care must be taken to buffer the

OUT

TEMP output with a suitable low bias current op amp, such as

the AD8601, AD820, or OP1177, all of which result in less than

a 100 μV change in ΔV

(see Figure 38). Without buffering,

OUT

even tens of microamps drawn from the TEMP pin can cause

to fall out of specification.

V

OUT

U1

ADR01/

ADR02/

ADR03/

ADR06

V

V

OUT

IN

TEMP TRIM

GND

V

O

02747-038

V

TEMP

1.9mV/°C

U2

15V

V+

OP1177

V–

V

IN

Figure 38. Temperature Monitoring

NEGATIVE REFERENCE

Without using any matching resistors, a negative reference can

be configured, as shown in Figure 39. For the ADR01, the

voltage difference between V

is at virtual ground, U2 closes the loop by forcing the

V

OUT

and GND is 10.0 V. Because

OUT

GND pin to be the negative reference node. U2 should be a

precision op amp with a low offset voltage characteristic.

LOW COST CURRENT SOURCE

Unlike most references, the ADR01/ADR02/ADR03/ADR06

employ an NPN Darlington in which the quiescent current

remains constant with respect to the load current, as shown in

Figure 24. As a result, a current source can be configured as

shown in Figure 40 where I

the sum of I

and IQ. Although simple, IQ varies typically from

SET

0.55 mA to 0.65 mA, limiting this circuit to general-purpose

applications.

SET

= (V

OUT

− VL)/R

. IL is simply

SET

U1

ADR01/

ADR02/

ADR03/

ADR06

V

+5

TO +15V

V

OUT

IN

TEMP

TRIM

GND

–V

REF

+15V

U2

V+

OP1177

V–

–15V

02747-039

Figure 39. Negative Reference

IN

I

IN

ADR01/

ADR02/

ADR03/

ADR06

GND

V

OUT

IQ≈ 0.6mA

R

SET

I

= (V

– VL)/R

OUT

SET

V

L

I

= I

R

L

+ I

L

SET

SET

Q

02747-040

Figure 40. Low Cost Current Source

PRECISION CURRENT SOURCE WITH ADJUSTABLE OUTPUT

Alternatively, a precision current source can be implemented

with the circuit shown in Figure 41. By adding a mechanical or

digital potentiometer, this circuit becomes an adjustable current

source. If a digital potentiometer is used, the load current is

simply the voltage across Terminal B to Terminal W of the

B

100kΩ

A

+12V

U2

V+

OP1177

V–

–12V

SET

.

)

L

W

R

1kΩ

SET

V

L

R

1kΩ

L

I

L

02747-041

digital potentiometer divided by R

DV

REF

=

I

L

R

(1)

SET

where D is the decimal equivalent of the digital potentiometer

input code.

U1

ADR01/

ADR02/

ADR03/

ADR06

+12

V

IN

TEMP

GND

Figure 41. Programmable 0 mA to 5 mA Current Source

V

OUT

TRIM

–5V TO V

0V TO (5V + V

AD5201

L

Rev. K | Page 16 of 24

ADR01/ADR02/ADR03/ADR06

V

V

www.BDTIC.com/ADI

To optimize the resolution of this circuit, dual-supply op amps

should be used because the ground potential of ADR02 can

swing from −5.0 V at zero scale to V

at full scale of the

L

potentiometer setting.

PROGRAMMABLE 4 mA TO 20 mA CURRENT TRANSMITTER

Because of their precision, adequate current handling, and small

footprint, the devices are suitable as the reference sources for

many high performance converter circuits. One of these

applications is the multichannel 16-bit, 4 mA to 20 mA current

transmitter in the industrial control market (see Figure 42).

This circuit employs a Howland current pump at the output to

yield better efficiency, a lower component count, and a higher

voltage compliance than the conventional design with op amps

and MOSFETs. In this circuit, if the resistors are matched such

that R1 = R1

′, R2 = R2′, R3 = R3′, the load current is

R1R3)(R2

I

+

= (2)

L

R3

×

′

REF

DV

×

N

2

latter is true, oscillation can occur. For this reason, connect

Capacitor C1 in the range of 1 pF to 10 pF between VP and the

output terminal of U4 to filter any oscillation.

V

t

Z

==

O

I

t

⎛

⎜

⎝

R1

′

R1R2

′

(3)

R2R1

⎞

−

1

⎟

′

⎠

In this circuit, an ADR01 provides the stable 10.000 V reference

for the AD5544 quad 16-bit DAC. The resolution of the adjustable current is 0.3 μA/step; the total worst-case INL error is

merely 4 LSBs. Such error is equivalent to 1.2 μA or a 0.006%

system error, which is well below most systems’ requirements.

The result is shown in Figure 43 with measurement taken at 25°C

and 70°C; total system error of 4 LSBs at both 25°C and 70°C.

5

RL= 500Ω

I

= 0mA TO 20mA

L

4

3

where D is similarly the decimal equivalent of the DAC input

code and N is the number of bits of the DAC.

According to Equation 2, R3′ can be used to set the sensitivity.

R3′ can be made as small as necessary to achieve the current

needed within U4 output current driving capability. Alternatively, other resistors can be kept high to conserve power.

In this circuit, the AD8512 is capable of delivering 20 mA of

current, and the voltage compliance approaches 15.0 V.

0VTO –10V

5V

10V

V

V

GND

U2

RF

DD

REF

DIGITAL INP UT

AD5544

IO

IO

U1

15

U1 = ADR01/ADR02/ADR03/ADR06, REF 01

U2 = AD5543/AD5544/AD5554

U3, U4 = AD8512

V

V

OUT

IN

TEMP TRIM

GND

CODE 20%–100% FUL L SCALE

+15V

U3

–15V

AD8512

V

X

R1'

150kΩ

R1

150kΩ

R2

15kΩ

VP

C1

10pF

U4

R2'

15kΩ

VN

LOAD

500Ω

4mA TO 20mA

R3

50Ω

R3'

50Ω

V

O

V

L

Figure 42. Programmable 4 mA to 20 mA Transmitter

The Howland current pump yields a potentially infinite output

impedance, that is highly desirable, but resistance matching is

critical in this application. The output impedance can be determined using Equation 3. As shown by this equation, if the

resistors are perfectly matched, Z

they are not matched, Z

is either positive or negative. If the

O

is infinite. Alternatively, if

O

2

INL (LSB)

1

0

–1

70°C

0 655368192 16384 24576 32768 40960 49152 57344

25°C

CODE (Decimal)

02747-043

Figure 43. Result of Programmable 4 mA to 20 mA Current Transmitter

PRECISION BOOSTED OUTPUT REGULATOR

A precision voltage output with boosted current capability can

be realized with the circuit shown in Figure 44. In this circuit,

U2 forces V

to be equal to V

O

N1, thereby making the load current furnished by V

configuration, a 50 mA load is achievable at V

Moderate heat is generated on the MOSFET, and higher current

can be achieved with a replacement of a larger device. In

addition, for a heavy capacitive load with a fast edging input

signal, a buffer should be added at the output to enhance the

transient response.

02747-042

IN

U1

ADR01/

ADR02/

ADR03/

ADR06

V

IN

TEMP

GND

V

OUT

TRIM

Figure 44. Precision Boosted Output Regulator

by regulating the turn-on of

REF

of 15.0 V.

IN

N1

2N7002

15V

V+

OP1177

V–

U2

R

200Ω

L

. In this

IN

C

L

1µF

V

O

02747-044

Rev. K | Page 17 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

1.35

1.25

1.15

1.00

0.90

0.70

0

.

1

0

M

Figure 45. 5-Lead Thin Shrink Small Outline Transistor Package [SC70]

1.60 BSC

*

0.90

0.87

0.84

0.10 MAX

Figure 46. 5-Lead Thin Small Outline Transistor Package [TSOT]

2.20

2.00

1.80

2.40

45

123

PIN 1

X

A

0.10 COPLANARITY

0.30

0.15

COMPLIANT TO JEDEC STANDARDS MO-203-AA

2.10

1.80

0.65 BSC

SEATING

PLANE

1.10

0.80

0.40

0.10

0.22

0.08

(KS-5)

Dimensions shown in millimeters

2.90 BSC

54

2.80 BSC

123

PIN 1

*

COMPLIANT TO JEDEC STANDARDS MO-193-AB WITH

THE EXCEPTION OF PACKAGE HEIGHT AND THICKNESS.

1.90

BSC

0.50

0.30

0.95 BSC

*

1.00 MAX

SEATING

PLANE

0.20

0.08

(UJ-5)

Dimensions shown in millimeters

5.00 (0.1968)

4.80 (0.1890)

0.46

0.36

0.26

8°

4°

0°

0.60

0.45

0.30

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLL ING DIMENSI ONS ARE IN MILLIMETERS; INCH DI MENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DESIGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-A A

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

Figure 47. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

Rev. K | Page 18 of 24

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

012407-A

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ORDERING GUIDES

ADR01 Ordering Guide

Initial Accuracy

Model (mV) (%) Branding

Output

Voltage

(V)

V

O

Temperature

Coefficient

(ppm/°C)

Temperature

Range

Package

Description

Package

Option

ADR01AR 10 10 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR01AR-REEL7 10 10 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR01ARZ

ADR01ARZ-REEL7

1

10 10 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

10 10 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR01BR 10 5 0.05 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR01BR-REEL7 10 5 0.05 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR01BRZ

ADR01BRZ-REEL7

1

10 5 0.05 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

10 5 0.05 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR01AUJ-REEL7 10 10 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R8A

ADR01AUJ-R2 10 10 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 250 R8A

ADR01AUJZ-REEL7

1

10 10 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1E

ADR01BUJ-REEL7 10 5 0.05 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R8B

ADR01BUJ-R2 10 5 0.05 9 –40°C to +125°C 5-Lead TSOT UJ-5 250 R8B

ADR01BUJZ-REEL7

1

10 5 0.05 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1F

ADR01AKS-REEL7 10 10 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R8A

ADR01AKS-R2 10 10 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 250 R8A

ADR01AKSZ-REEL7

1

10 10 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1E

ADR01BKS-REEL7 10 5 0.05 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R8B

ADR01BKS-R2 10 5 0.05 9 –40°C to +125°C 5-Lead SC70 KS-5 250 R8B

ADR01BKSZ-REEL7

ADR01CRZ

ADR01CRZ-REEL

1

1

10 5 0.05 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1F

10 10 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

10 10 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

ADR01NBC 10 5 0.05 10 (typ) Die 360

1

Z = RoHS Compliant Part.

Ordering

Quantity

Rev. K | Page 19 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ADR02 Ordering Guide

Model

Output

Voltage

V

(V)

O

Initial Accuracy

(mV) (%) Branding

Temperature

Coefficient

(ppm/°C)

Temperature

Range

Package

Description

Package

Option

Ordering

Quantity

ADR02AR 5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR02AR-REEL 5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

ADR02AR-REEL7 5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR02ARZ

ADR02ARZ-REEL

ADR02ARZ-REEL7

1

5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

1

5 5 0.1 10 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

ADR02BR 5 3 0.06 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR02BR-REEL7 5 3 0.06 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR02BRZ

ADR02BRZ-REEL7

1

5 3 0.06 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

5 3 0.06 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR02AUJ-REEL7 5 5 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R9A

ADR02AUJ-R2 5 5 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 250 R9A

ADR02AUJZ-REEL7

1

5 5 0.1 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1G

ADR02BUJ-REEL7 5 3 0.06 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R9B

ADR02BUJ-R2 5 3 0.06 9 –40°C to +125°C 5-Lead TSOT UJ-5 250 R9B

ADR02BUJZ-R2

ADR02BUJZ-REEL7

1

5 3 0.06 9 –40°C to +125°C 5-Lead TSOT UJ-5 250 R9B

1

5 3 0.06 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1H

ADR02AKS-REEL7 5 5 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R9A

ADR02AKS-R2 5 5 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 250 R9A

ADR02AKSZ-REEL7

1

5 5 0.1 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1G

ADR02BKS-REEL7 5 3 0.06 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R9B

ADR02BKS-R2 5 3 0.06 9 –40°C to +125°C 5-Lead SC70 KS-5 250 R9B

ADR02BKSZ-REEL7

ADR02CRZ

ADR02CRZ-REEL

1

Z = RoHS Compliant Part.

1

1

5 3 0.06 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1H

5 5 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

5 5 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

Rev. K | Page 20 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ADR03 Ordering Guide

Model

Output

Voltage

VO (V)

Initial Accuracy

ADR03AR 2.5 5 0.2 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR03AR-REEL7 2.5 5 0.2 10 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR03ARZ

ADR03ARZ-REEL7

1

2.5 5 0.2 10 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

2.5 5 0.2 10 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR03BR 2.5 2.5 0.1 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

ADR03BR-REEL7 2.5 2.5 0.1 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR03BRZ

ADR03BRZ-REEL7

1

2.5 2.5 0.1 3 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

2.5 2.5 0.1 3 –40°C to +125°C 8-Lead SOIC-N R-8 1,000

ADR03AUJ-REEL7 2.5 5 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 RFA

ADR03AUJ-R2 2.5 5 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 250 RFA

ADR03AUJZ-REEL7

1

2.5 5 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1J

ADR03BUJ-REEL7 2.5 2.5 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 RFB

ADR03BUJ-R2 2.5 2.5 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 250 RFB

ADR03BUJZ-REEL7

1

2.5 2.5 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1K

ADR03AKS-REEL7 2.5 5 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 RFA

ADR03AKS-R2 2.5 5 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 250 RFA

ADR03AKSZ-REEL7

1

2.5 5 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1J

ADR03BKS-REEL7 2.5 2.5 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 RFB

ADR03BKS-R2 2.5 2.5 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 250 RFB

ADR03BKSZ-REEL7

ADR03CRZ

ADR03CRZ-REEL

1

1

2.5 2.5 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1K

2.5 5 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 98

1

2.5 5 0.1 40 –40°C to +125°C 8-Lead SOIC-N R-8 2,500

ADR03NBC 2.5 2.5 0.1 10 (typ) Die 360

1

Z = RoHS Compliant Part.

Temperature

Coefficient

(ppm/°C)

Temperature

Range

Package

Description

Package

Option

Ordering

Quantity Branding (mV) (%)

Rev. K | Page 21 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

ADR06 Ordering Guide

Output

Voltage

Model

VO (V)

ADR06AR 3 6 0.2 10 –40°C to +125°C

ADR06AR-REEL7 3 6 0.2 10 –40°C to +125°C

ADR06ARZ

ADR06ARZ-REEL7

1

3 6 0.2 10 –40°C to +125°C

1

3 6 0.2 10 –40°C to +125°C

ADR06BR 3 3 0.1 3 –40°C to +125°C

ADR06BR-REEL7 3 3 0.1 3 –40°C to +125°C

ADR06BRZ

ADR03BRZ-REEL7

1

3 3 0.1 3 –40°C to +125°C

1

3 3 0.1 3 –40°C to +125°C

Initial Accuracy

(mV) (%) Branding

Temperature

Coefficient

(ppm/°C)

Temperature

Range

Package

Description

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

8-Lead SOIC-N

Package

Option

Ordering

Quantity

R-8 98

R-8 1,000

R-8 98

R-8 1,000

R-8 98

R-8 1,000

R-8 98

R-8 1,000

ADR06AUJ-REEL7 3 6 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 RWA

ADR06AUJ-R2 3 6 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 250 RWA

ADR06AUJZ-REEL7

1

3 6 0.2 25 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1L

ADR06BUJ-REEL7 3 3 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 RWB

ADR06BUJ-R2 3 3 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 250 RWB

ADR06BUJZ-REEL7

1

3 3 0.1 9 –40°C to +125°C 5-Lead TSOT UJ-5 3,000 R1M

ADR06AKS-REEL7 3 6 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 RWA

ADR06AKS-R2 3 6 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 250 RWA

ADR06AKSZ-REEL7

1

3 6 0.2 25 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1L

ADR06BKS-REEL7 3 3 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 RWB

ADR06BKS-R2 3 3 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 250 RWB

ADR06BKSZ-REEL7

ADR06CRZ

ADR06CRZ-REEL

1

Z = RoHS Compliant Part.

1

1

3 3 0.1 9 –40°C to +125°C 5-Lead SC70 KS-5 3,000 R1M

3 6 0.2 40 –40°C to +125°C

1

3 6 0.2 40 –40°C to +125°C

8-Lead SOIC-N

8-Lead SOIC-N

R-8 98

R-8 2,500

Rev. K | Page 22 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

NOTES

Rev. K | Page 23 of 24

ADR01/ADR02/ADR03/ADR06

www.BDTIC.com/ADI

NOTES

©2002–2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D02747-0-2/08(K)

Rev. K | Page 24 of 24

Loading...

Loading...