Charge Pump Driven 9-Channel LED Driver with

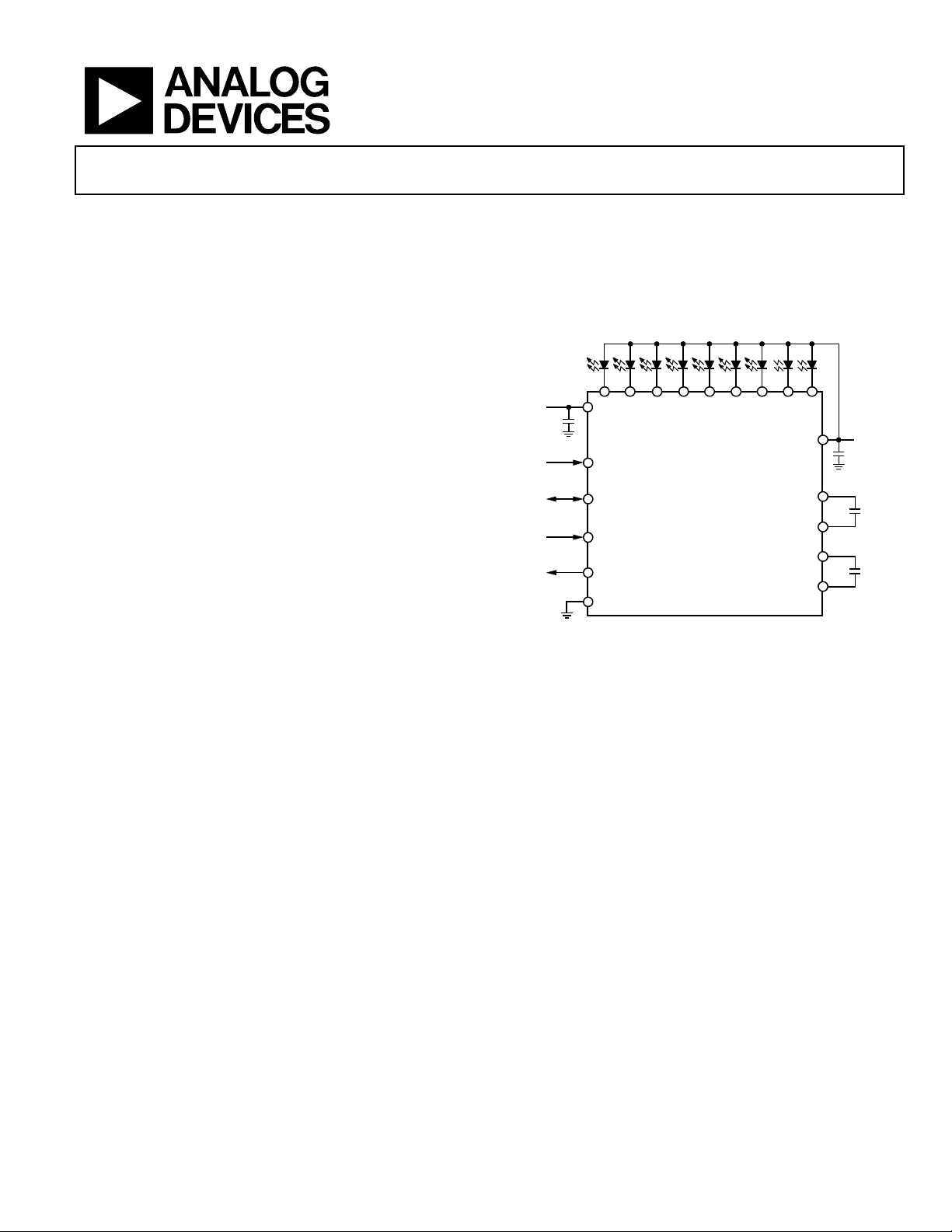

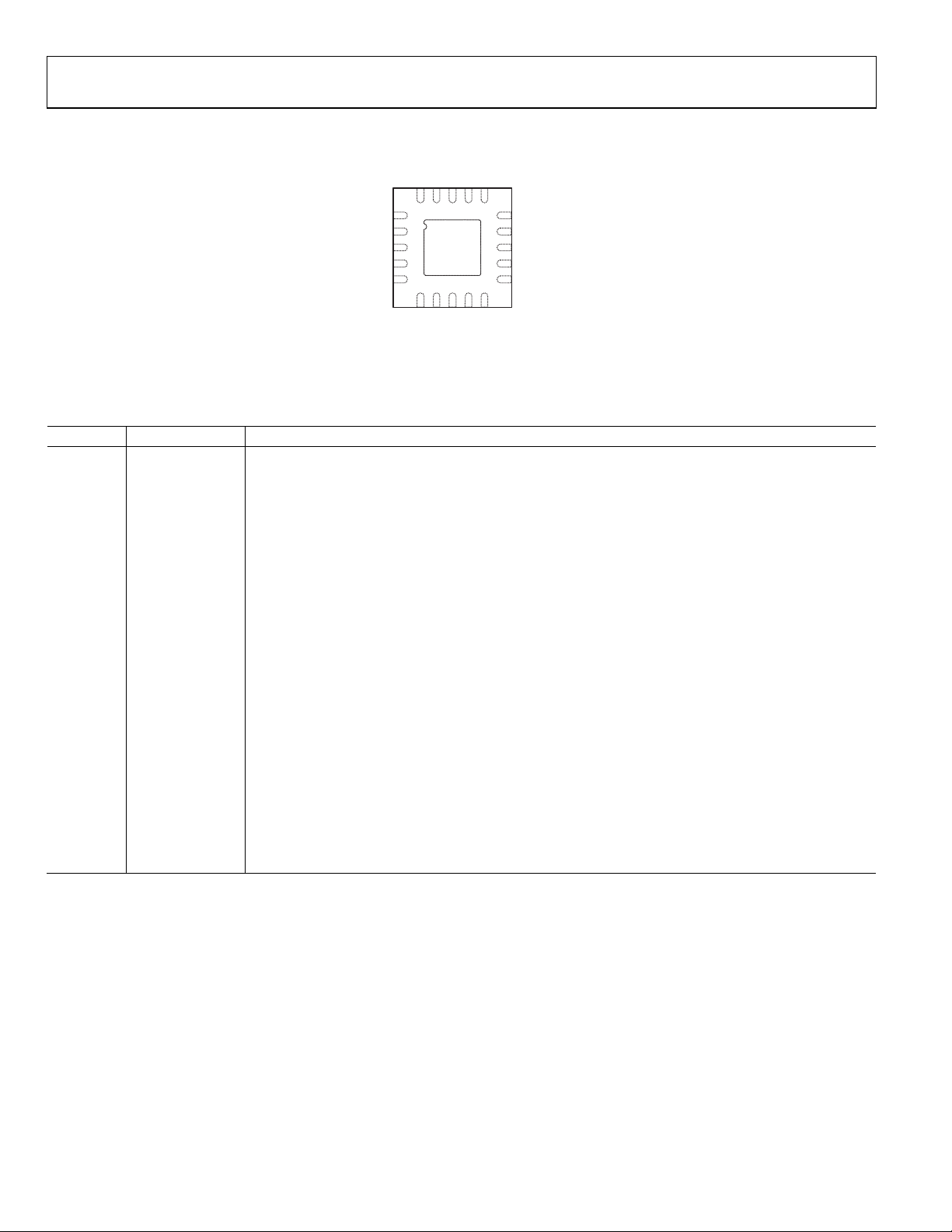

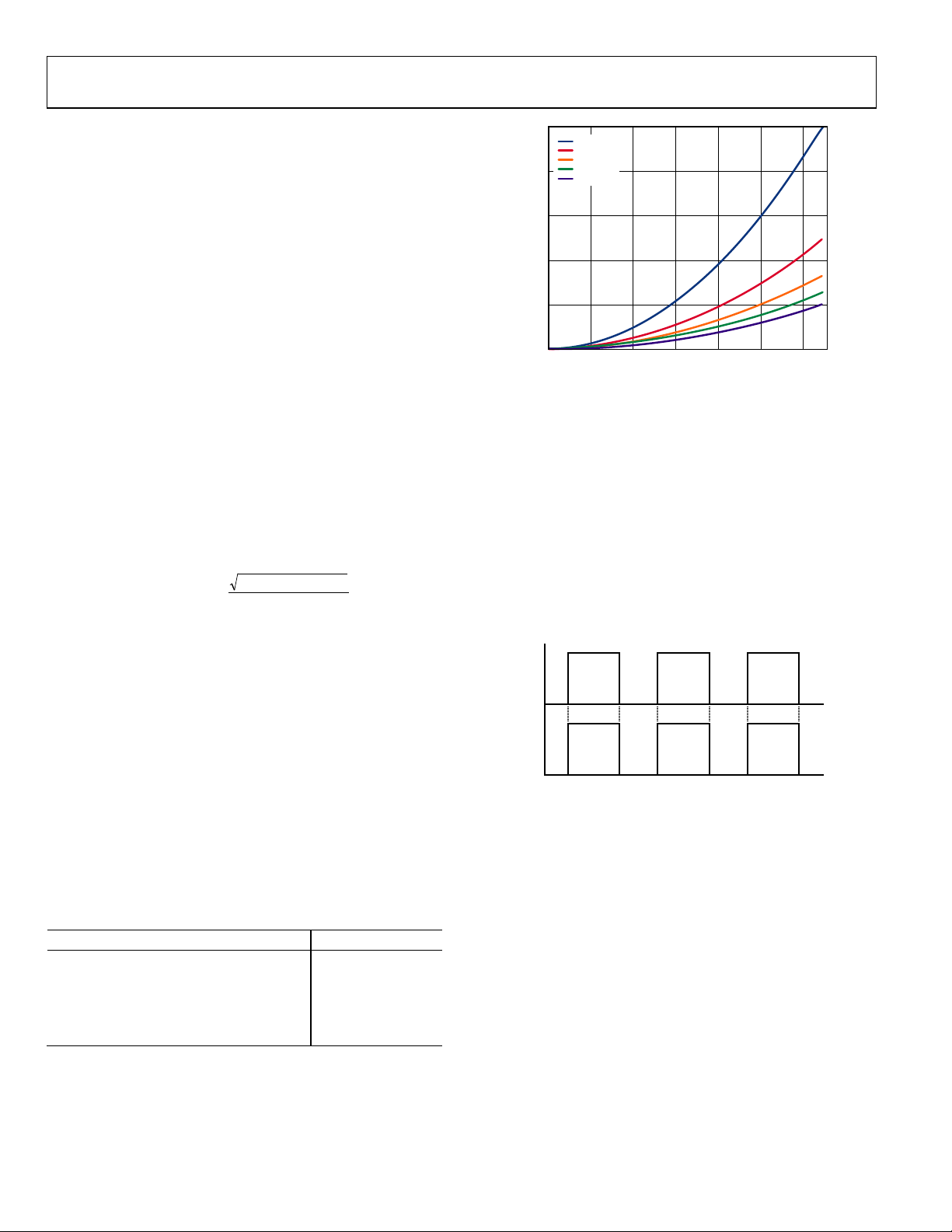

09478-001

D1

D2 D3

D4 D5

D7D6

D8 D9

nRST

SDA

SCL

nINT

GND

VIN

1µF

C2+

C2–

C2

1µF

C1+

C1–

C1

1µF

VOUT

1µF

ADP8866

FEATURES

Charge pump with automatic gain selection of 1×, 1.5×, and

2× for maximum efficiency

92% peak efficiency

9 independent and programmable LED drivers

Each driver is capable of 25 mA (full scale)

Each driver has 7 bits (128 levels) of nonlinear current

settings

Standby mode for <1 µA current consumption

16 programmable fade-in and fade-out times (0.0 sec to

1.75 sec) with choice of square or cubic rates

Automated and customizable LED blinking

Unique heartbeat mode for programmable double pulse

lighting effects on 4 channels (D6 to D9)

PWM input for implementing content adjustable brightness

control (cABC)

2

I

C compatible interface for all programming

Dedicated reset pin and built-in power on reset (POR)

Short circuit, overvoltage, and overtemperature protection

Internal soft start to limit inrush currents

Input to output isolation during faults or shutdown

Operates down to V

(UVLO) at 1.9 V

Small lead frame chip scale package (LFCSP)

= 2.5 V, with undervoltage lockout

IN

Automated LED Lighting Effects

ADP8866

APPLICATIONS

Mobile display backlighting

Mobile phone keypad backlighting

LED indication and status lights

Automated LED blinking

TYPICAL OPERATING CIRCUIT

Figure 1.

GENERAL DESCRIPTION

The ADP8866 combines a programmable backlight LED charge

pump driver with automatic blinking functions. Nine LED drivers

can be independently programmed at currents up to 25 mA.

The current level, fade time, and blinking rate can be programmed

once and executed autonomously on a loop. Separate fade-in

and fade-out times can be set for the backlight LEDs.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of th eir respective owners.

Driving all of this is a two-capacitor charge pump with gains of

1×, 1.5×, and 2×. This setup is capable of driving a maximum

I

of 240 mA from a supply of 2.5 V to 5.5 V. A full suite of

OUT

safety features including short-circuit, overvoltage, and overtemperature protection allows easy implementation of a safe

and robust design. Additionally, input inrush currents are

limited via an integrated soft start combined with controlled

input to output isolation.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADP8866

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Typical Operating Circuit ................................................................ 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 5

Maximum Temperature Ranges ................................................. 5

Thermal Resistance ...................................................................... 5

ESD Caution .................................................................................. 5

Pin Configurations and Function Descriptions ........................... 6

Typical Performance Characteristics ............................................. 7

Theory of Operation ...................................................................... 11

Power Stage.................................................................................. 12

Operating Modes ........................................................................ 13

LED Groups................................................................................. 14

Output Current Settings ............................................................ 14

Output Current Range Selection .............................................. 14

PWM Dimming .......................................................................... 14

Automated Fade-in and Fade-Out ........................................... 14

CABC Fade Disable ................................................................... 15

Independent Sink Control (ISC) .............................................. 15

Advanced Blinking Controls .................................................... 16

Short-Circuit Protection (SCP) Mode ..................................... 17

Overvoltage Protection (OVP) ................................................. 17

Thermal Shutdown (TSD)/Overtemperature Protection ..... 17

Interrupts ..................................................................................... 19

Backlight Off Interrupt .............................................................. 19

Independent Sink Off Interrupt ............................................... 19

Applications Information .............................................................. 20

Layout Guidelines....................................................................... 20

I2C Programming and Digital Control ........................................ 21

Register Descriptions ..................................................................... 22

Backlight Register Descriptions ............................................... 29

Independent Sink Register Descriptions ................................. 34

Outline Dimensions ....................................................................... 50

Ordering Guide .......................................................................... 50

REVISION HISTORY

3/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 52

ADP8866

SPECIFICATIONS

VIN = 3.6 V, SCL = 2.7 V, SDA = 2.7 V, nINT = open, nRST = 2.7 V, V

T

= 25°C and are not guaranteed. Minimum and maximum limits are guaranteed from TJ = −40°C to +105°C, unless otherwise noted.

J

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

SUPPLY

Input Voltage

Operating Range VIN 2.5 5.5 V

Startup Level V

Low Level V

V

Hysteresis V

IN (STA RT )

UVLO Noise Filter t

VIN increasing 1.98 2.25 V

IN (STA RT )

VIN decreasing 1.75 1.90 V

IN(STOP)

After startup 80 mV

IN(HYS)

10 μs

UVLO

Quiescent Current IQ

During Standby I

Q(STBY)

= 3.6 V, Bit nSTBY = 0, SCL = SDA =

V

IN

0 V

Current Consumption

During Blinking Off Time

Switching I

I

Q(OFF)

= 3.6 V, Bit nSTBY = 1, I

V

IN

Measured during blinking off time

VIN = 3.6 V, Bit nSTBY = 1, I

Q(ACTIVE)

Gain = 1.0× 1.2 2.0 mA

Gain = 1.5× 3.7 5.4 mA

Gain = 2.0× 4.3 6.2 mA

OSCILLATOR Charge pump gain = 2×

Switching Frequency fSW 0.8 1 1.2 MHz

Duty Cycle D 50 %

OUPUT CURRENT CONTROL

Maximum Drive Current I

D1:D9(MAX)

V

= 0.4 V

D1:D9

TJ = 25°C 23.0 25.0 27.0 mA

TJ = −40°C to +85°C 22.5 27.5 mA

LED Current Source Matching I

All Current Sinks I

D1 to D5 Current Sinks I

Leakage Current on LED Pins I

Equivalent Output Resistance R

Gain = 1× VIN = 3.6 V, I

Gain = 1.5× VIN = 3.1 V, I

Gain = 2× VIN = 2.5 V, I

Regulated Output Voltage V

MAT CH

V

MAT CH9

V

MAT CH5

VIN = 5.5 V, V

D1:D9(LKG)

OUT

VIN = 3 V, gain = 2×, I

OUT(REG)

= 0.4 V 1.4 %

D1:D9

= 0.4 V 1.1 %

D1:D5

= 2.5 V, Bit nSTBY = 1 0.5 μA

D1:D9

= 100 mA 0.5 Ω

OUT

= 100 mA 3.0 Ω

OUT

= 100 mA 3.8 Ω

OUT

AUTOMATIC GAIN SELECTION

Minimum Voltage

Gain Increases V

Minimum Current Sink

Decrease VDX until the gain switches up 145 200 240 mV

HR(UP)

V

HR(MIN)

IDX = I

× 95% 210 mV

DX(MAX)

Headroom Voltage

Gain Delay t

GAIN

The delay after gain has changed and

before gain is allowed to change again

FAULT PROTECTION

Startup Charging Current

VIN = 3.6 V, V

I

SS

= 0.8 × VIN 3.5 7 11 mA

OUT

Source

Output Voltage Threshold V

Exit Soft Start V

Short-Circuit Protection V

Output Overvoltage Protection V

OUT

V

OUT(START)

V

OUT(SC)

OVP

rising 0.92 × VIN V

OUT

falling 0.55 × VIN V

OUT

Activation Level 5.7 6.0 V

OVP Recovery Hysteresis 500 mV

= 0.4 V, C1 = 1 μF, C2 = 1 μF, C

D1:D9

= 1 μF, typical values are at

OUT

0.25 1.0 μA

= 0 mA

OUT

= 0 mA

OUT

= 10 mA 4.4 4.9 5.2 V

OUT

245 325 μA

100 μs

Rev. 0 | Page 3 of 52

ADP8866

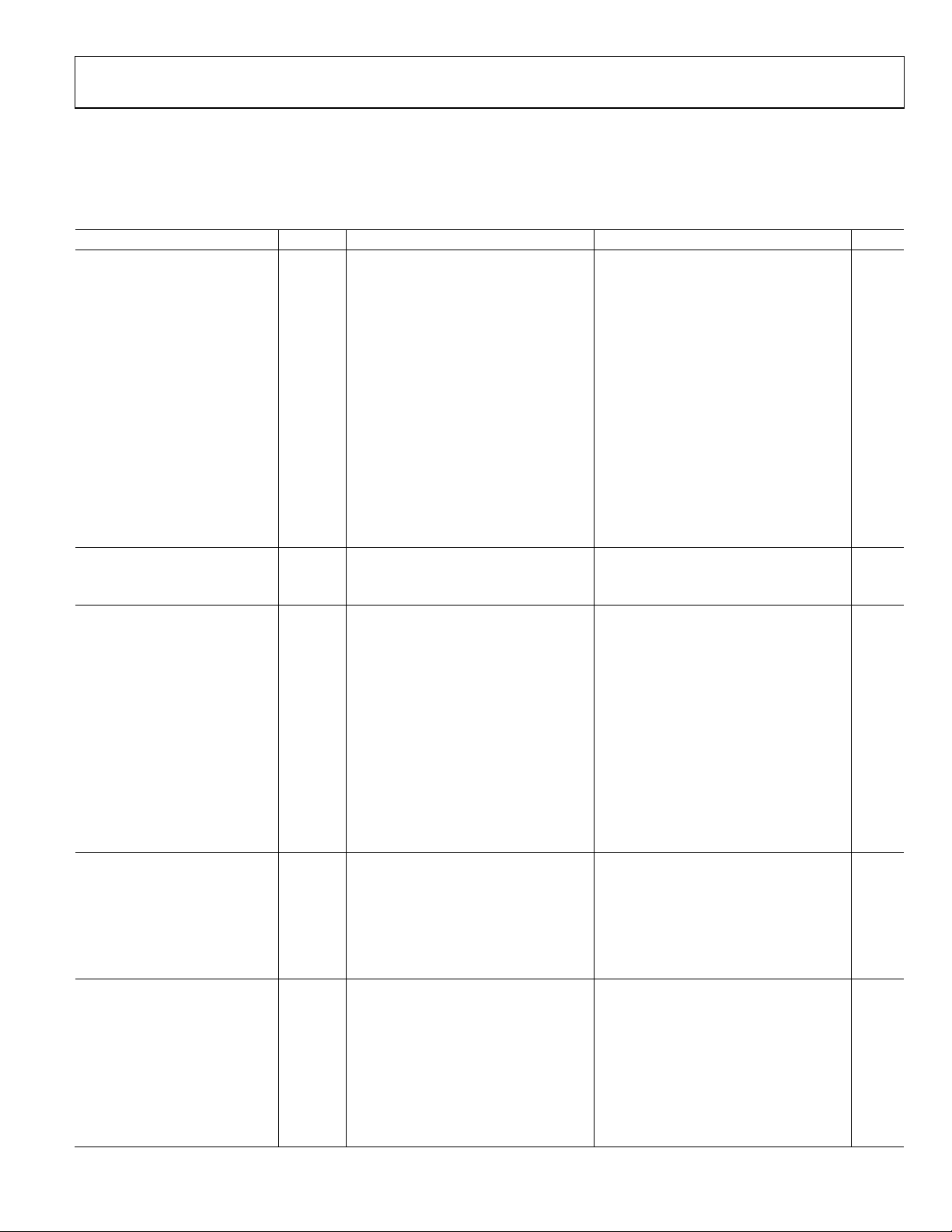

SDA

SCL

S

S = START CONDITION

Sr = REPEAT E D S TART CONDI TION

P = STOP CONDITION

Sr

P

S

t

LOW

t

R

t

HD, DAT

t

HIGH

t

SU, DAT

t

F

t

F

t

SU, STA

t

HD, STA

t

SP

t

SU, STO

t

BUF

t

R

09478-002

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

Thermal Shutdown

Threshold TSD Increasing temperature 150 °C

Hysteresis TSD

Isolation from Input to

Output During Fault

Time to Validate a Fault t

I2C INTERFACE

V

Voltage Operating Range V

DDIO

Logic Low Input VIL VIN = 2.5 V 0.5 V

Logic High Input VIH VIN = 5.5 V 1.55 V

I2C TIMING SPECIFICATIONS Guaranteed by design

Delay from Reset Deassertion

2

C Access

to I

SCL Clock Frequency f

SCL High Time t

SCL Low Time t

Setup Time

Data t

Repeated Start t

Stop Condition t

Hold Time

Data t

Start/Repeated Start t

Bus Free Time (Stop and Start

Conditions)

Rise Time (SCL and SDA) tR 20 + 0.1 × CB 300 ns

Fall Time (SCL and SDA) tF 20 + 0.1 × CB 300 ns

Pulse Width of Suppressed

Spike

Capacitive Load Per Bus Line C

Timing Diagram

20 °C

(HYS)

VIN = 5.5 V, V

I

OUTLKG

2 μs

FAU LT

5.5 V

DDIO

20 μs

t

RESET

400 kHz

SCL

0.6 μs

HIGH

1.3 μs

LOW

100 ns

SU , DAT

0.6 μs

SU, STA

0.6 μs

SU, STO

0 0.9 μs

HD, DAT

0.6 μs

HD, STA

t

1.3 μs

BUF

0 50 ns

t

SP

B

400 pF

= 0 V, Bit nSTBY = 0 1 μA

OUT

2

Figure 2. I

C Interface Timing Diagram

Rev. 0 | Page 4 of 52

ADP8866

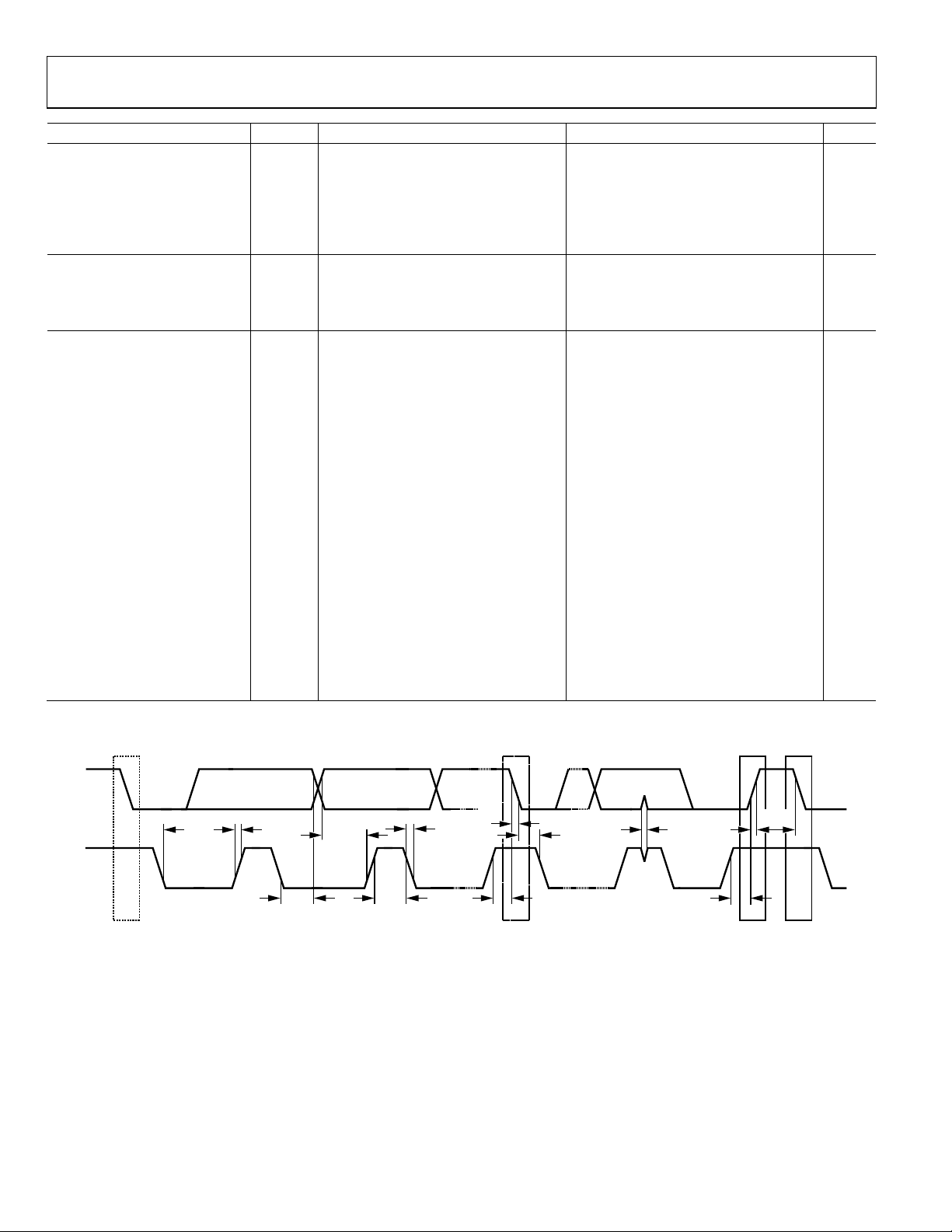

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VIN, VOUT to GND −0.3 V to +6 V

D1, D2, D3, D4, D5, D6, D7, D8, and D9 to

−0.3 V to +6 V

GND

nINT, nRST, SCL, and SDA to GND −0.3 V to +6 V

Output Short-Circuit Duration Indefinite

Operating Ambient Temperature Range −40°C to +85°C1

Operating Junction Temperature Range −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Soldering Conditions JEDEC J-STD-020

ESD (Electrostatic Discharge)

Human Body Model (HBM) ±2.0 kV

Charged Device Model (CDM) ±1.5 kV

1

The maximum operating junction temperature (T

maximum operating ambient temperature (T

Temperature Ranges section for more information.

) supersedes the

J(MAX)

). See the Maximum

A(MAX)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational section of

this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in

combination. Unless otherwise specified, all voltages are

referenced to GND.

THERMAL RESISTANCE

The θJA (junction to air) and θJC (junction to case) are

determined according to JESD51-9 on a 4-layer printed circuit

board (PCB) with natural convection cooling. The exposed pad

must be soldered to GND.

Table 3. Thermal Resistance

Package Type θJA θJC Unit

LFCSP 38.6 3.56 °C/W

ESD CAUTION

MAXIMUM TEMPERATURE RANGES

The maximum operating junction temperature (T

supersedes the maximum operating ambient temperature

(T

). Therefore, in situations where the ADP8866 is

A(MAX)

exposed to poor thermal resistance and a high power dissipation

(P

), the maximum ambient temperature may need to be derated.

D

In these cases, the ambient temperature maximum can be

calculated with the following equation:

T

A(MAX)

= T

J(MAX)

− (θJA × P

D(MAX)

).

J(MAX)

)

Rev. 0 | Page 5 of 52

ADP8866

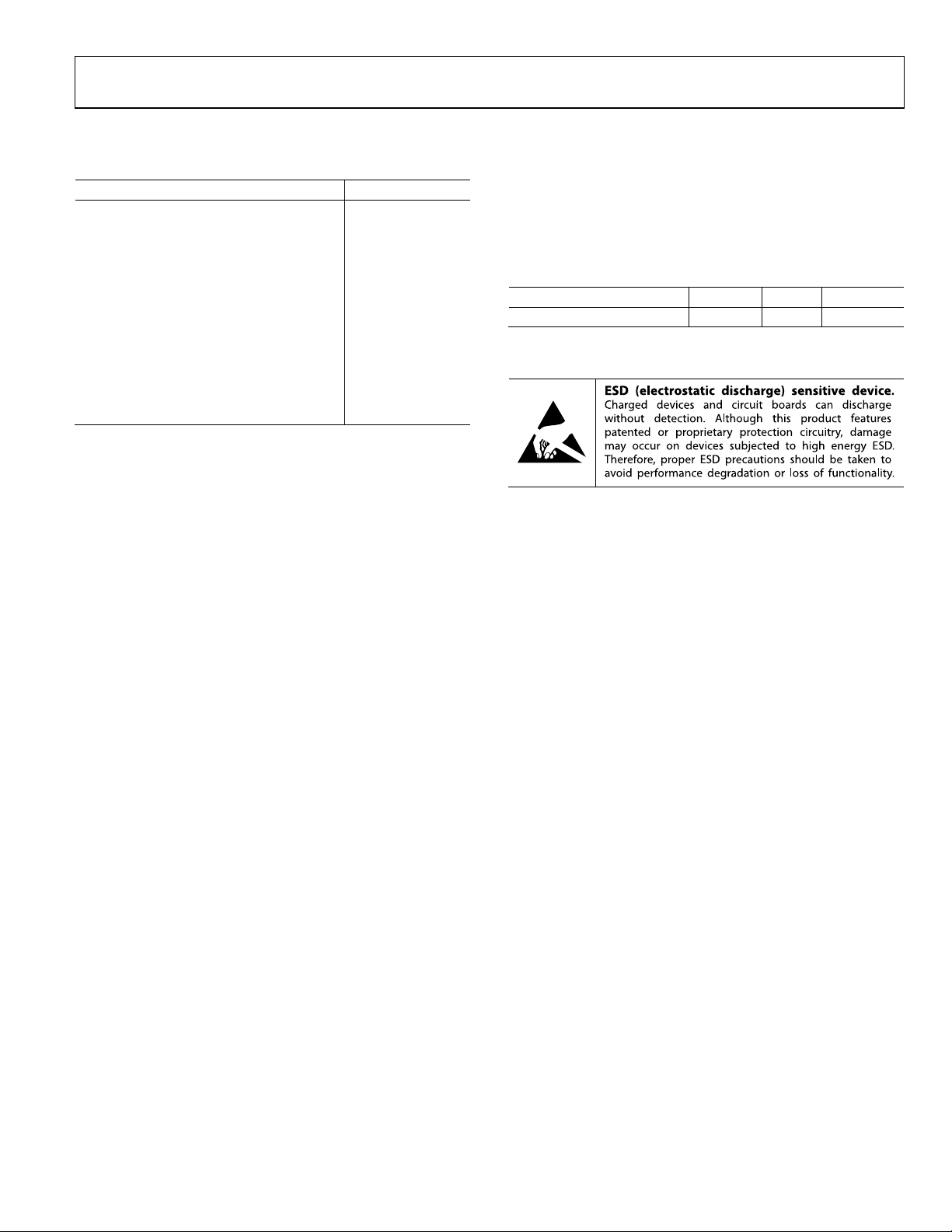

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

D4

D5

20

19

D8

D6

D7

16

18

17

1

D3

2

D2

D1

D9

nRST

NOTES

1. CONNECT THE EXPOSED

PADDLE TO GND.

3

4

5

ADP8866

TOP VIEW

(Not to S cale)

8

6

7

SCL

SDA

nINT

9

C1–

10

C2–

15 GND

14

VIN

13

VOUT

12

C2+

11

C1+

09478-003

Figure 3. LFCSP Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

14 VIN Battery Voltage 2.5 V to 5.5 V.

3 D1 LED Sink 1 Output.

2 D2 LED Sink 2 Output.

1 D3 LED Sink 3 Output.

20 D4 LED Sink 4 Output.

19 D5 LED Sink 5 Output.

18 D6 LED Sink 6 Output.

17 D7 LED Sink 7 Output.

16 D8 LED Sink 8 Output.

4 D9 LED Sink 9 Output.

13 VOUT Charge Pump Output.

11 C1+ Charge Pump C1+.

9 C1−

Charge Pump C1−.

12 C2+ Charge Pump C2+.

10 C2− Charge Pump C2−.

15 GND Ground. Connect the exposed paddle to GND.

8 nINT

Processor Interrupt (Active Low). Requires an external pull-up resistor. If this pin is not used, it can be left

floating. Alternatively, this pin can be set as the PWM input for implementing cABC dimming (see the

PWM Dimming section).

5 nRST

Hardware Reset Input (Active Low). This bit resets the device to the default conditions. If not used, this pin

must be tied above V

IH(MAX)

.

7 SDA I2C Serial Data Input. Requires an external pull-up resistor.

6 SCL I2C Clock Input. Requires an external pull-up resistor.

Rev. 0 | Page 6 of 52

ADP8866

1400

1200

1000

800

600

400

200

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

Q

(µA)

09478-004

+105°C

+85°C

+25°C

–40°C

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0.5

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

Q

(mA)

09478-005

+105°C

+85°C

+25°C

–40°C

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0.5

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

Q

(mA)

09478-006

+105°C

+85°C

+25°C

–40°C

400

350

300

250

200

150

100

50

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

Q (OFF)

(µA)

09478-007

+105°C

+85°C

+25°C

–40°C

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

STANDBY I

Q

(µA)

09478-008

+105°C

+85°C

+25°C

–40°C

SCL = SDA = 0V

27.0

26.5

26.0

25.5

25.0

24.5

24.0

23.5

23.0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

LED

(mA)

09478-009

+105°C

+85°C

+25°C

–40°C

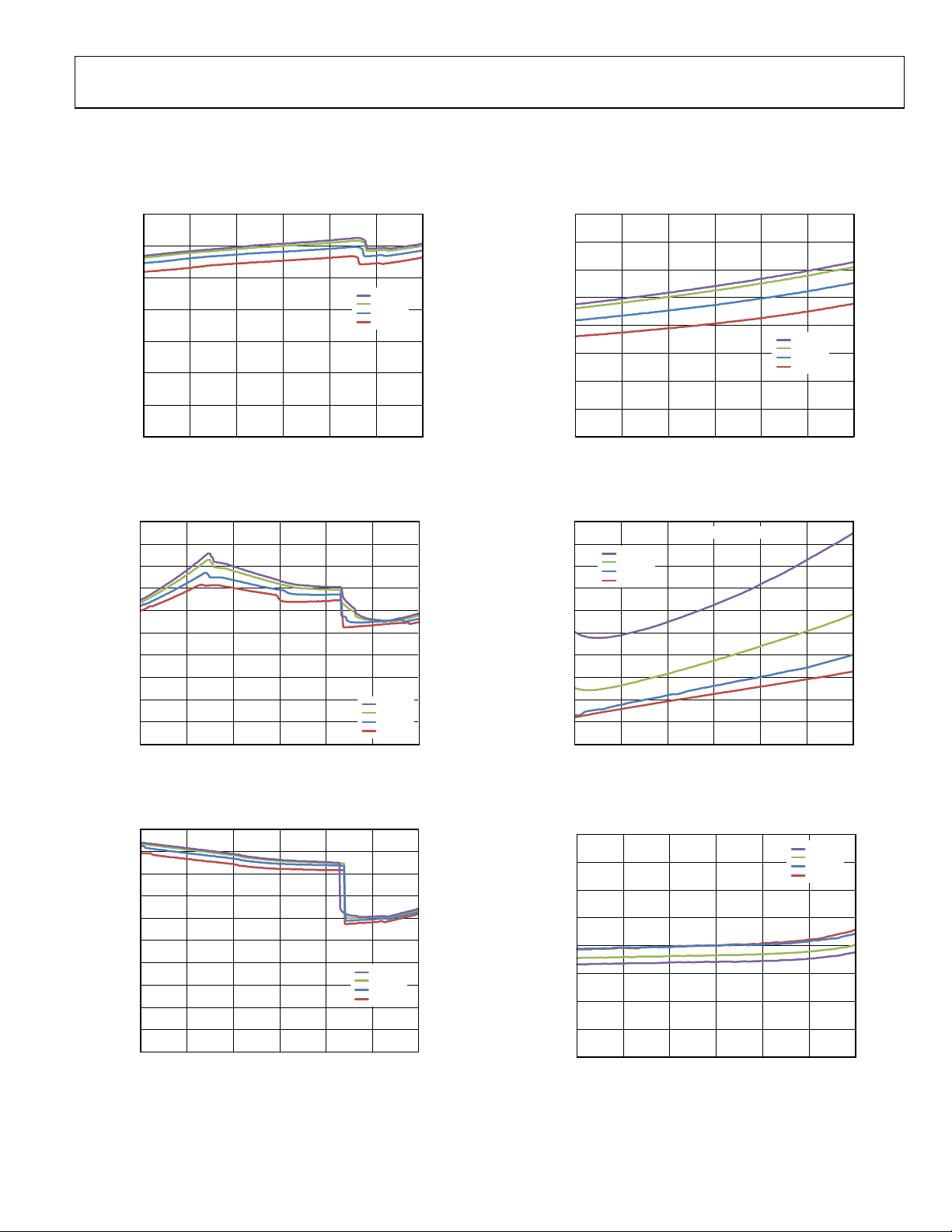

TYPICAL PERFORMANCE CHARACTERISTICS

VIN = 3.6 V, SCL = 2.7 V, SDA = 2.7 V, nRST = 2.7 V, V

unless otherwise noted.

D1:D9

= 0.4 V, I

= 0 mA, CIN = 1 μF, C1 = 1 μF, C2 = 1 μF, C

OUT

= 1 μ F, TA= 25°C,

OUT

Figure 4. Typical Operating Current, G = 1×

Figure 5. Typical Operating Current, G = 1.5×

Figure 7. Typical Off Time Current (I

Q(OFF)

)

Figure 8. Typical Standby IQ

Figure 6. Typical Operating Current, G = 2×

Figure 9. Typical Diode Current vs. VIN

Rev. 0 | Page 7 of 52

ADP8866

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

MATCHING ( %)

09478-010

+105°C

+85°C

+25°C

–40°C

I

D1:D9

= 25mA

26.5

26.0

25.5

25.0

24.5

24.0

23.5

27.0

23.0

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

V

HR

(V)

I

LED

CURRENT (mA)

09478-011

+105°C

+85°C

+25°C

–40°C

1.4

1.2

1.0

0.8

0.6

0.4

0.2

1.6

0

0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

V

HR

(V)

MATCHING ( %)

09478-012

+105°C

+85°C

+25°C

–40°C

I

D1:D9

= 25mA

0.1

0

–0.1

–0.2

–0.3

–0.4

–0.5

–0.6

–0.7

–0.8

–40 –15 10 35 60 85 110

TEMPERATURE (°C)

I

OUT

DEVIATI ON (%)

09478-013

I

OUT

= 100mA

1.2

1.0

0.8

0.6

0.4

0.2

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

R

OUT

(Ω)

09478-014

+105°C

+85°C

+25°C

–40°C

I

OUT

= 100mA

6

5

4

3

2

1

0

2.2 2.4 2.6 2.8 3.0 3.2 3.4

V

IN

(V)

R

OUT

(Ω)

09478-015

+105°C

+85°C

+25°C

–40°C

I

OUT

= 100mA

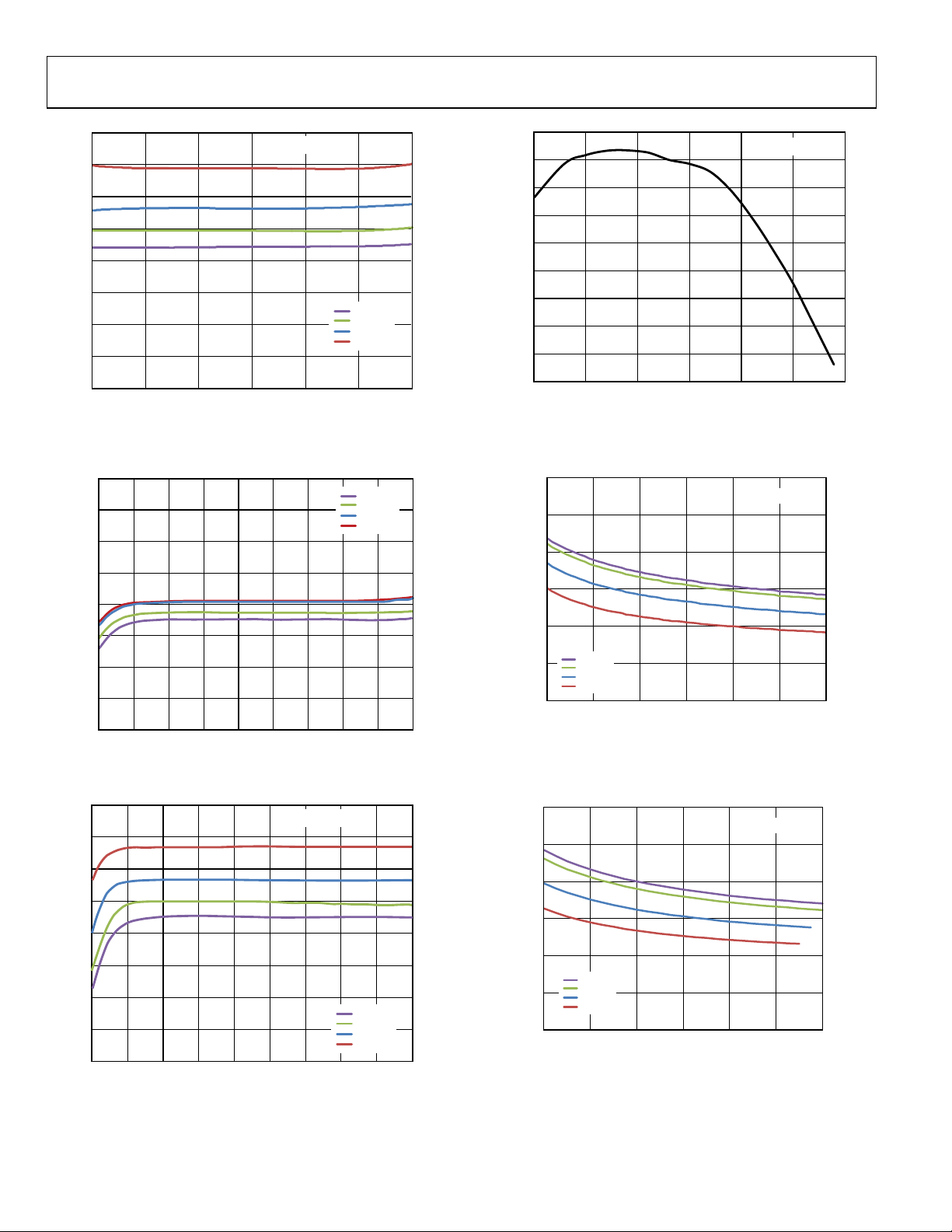

Figure 10. Typical Diode Matching vs. V

IN

Figure 13. Typical Change in Diode Current vs. Temperature

Figure 11. Typical Diode Matching vs. Current Sink Headroom Voltage (VHR)

Figure 12. Typical Diode Current vs. Current Sink Headroom Voltage (VHR)

Figure 14. Typical R

(G = 1×) vs. VIN

OUT

Figure 15. Typical R

(G = 1.5×) vs. VIN

OUT

Rev. 0 | Page 8 of 52

ADP8866

6

5

4

3

2

1

0

2.2 2.3 2.4 2.5 2.6 2.7 2.8

V

IN

(V)

R

OUT

(Ω)

09478-016

+105°C

+85°C

+25°C

–40°C

I

OUT

= 100mA

20

18

16

14

12

10

8

6

4

2

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

I

SS

(mA)

09478-017

+105°C

+85°C

+25°C

–40°C

VOUT = 80% OF VIN

30

25

20

15

10

5

0

0 20 40 60 80 100

PWM DUTY CYCLE (%)

AVERAGE LE D CURRE NT (mA)

09478-018

+85°C

+25°C

–40°C

1.4

1.0

1.2

0.6

0.8

0.2

0.4

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

THRESHOL D ( V )

09478-019

VIL, +25°C

V

IH

, +25°C

V

IL

, –40°C

V

IH

, –40°C

V

IL

, +85°C

V

IH

, +85°C

V

IL

, +105°C

V

IH

, +105°C

5.3

5.2

5.1

5.0

4.9

4.8

4.7

4.6

–40 –15 10 35 60 85 110

TEMPERATURE (°C)

V

OUT(REG)

(V)

09478-020

6.0

5.9

5.8

5.7

5.6

5.5

5.4

5.3

5.2

5.1

5.0

–40 –15 10 35 60 85 110

TEMPERATURE (°C)

V

OUT

(V)

09478-021

THRESHOLD

RECOVERY

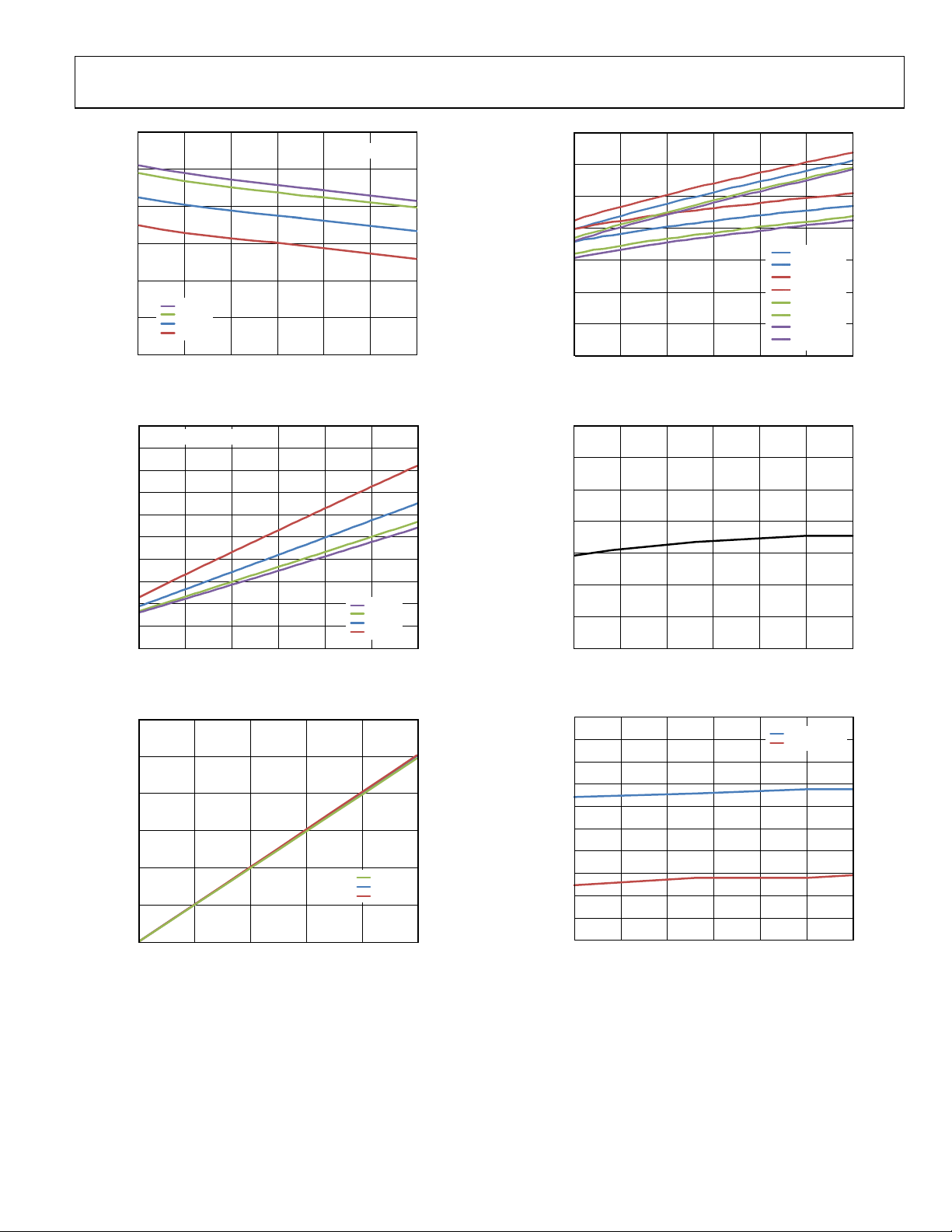

Figure 16. Typical R

(G = 2×) vs. VIN

OUT

Figure 17. Typical Output Soft Start Current, ISS

Figure 19. Typical I2C Thresholds, VIH and VIL

Figure 20. Typical Regulated Output Voltage (V

OUT(REG)

)

Figure 18. Typical Average I

OUT

vs. PWM Duty (f

= 300 Hz)

PWM

Figure 21. Typical Overvoltage Protection (OVP) Threshold

Rev. 0 | Page 9 of 52

ADP8866

100

90

80

70

60

50

40

30

20

10

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

IN

(V)

EFFICIENCY (%)

09478-022

V

F

= 3.4V

V

F

= 4.0V

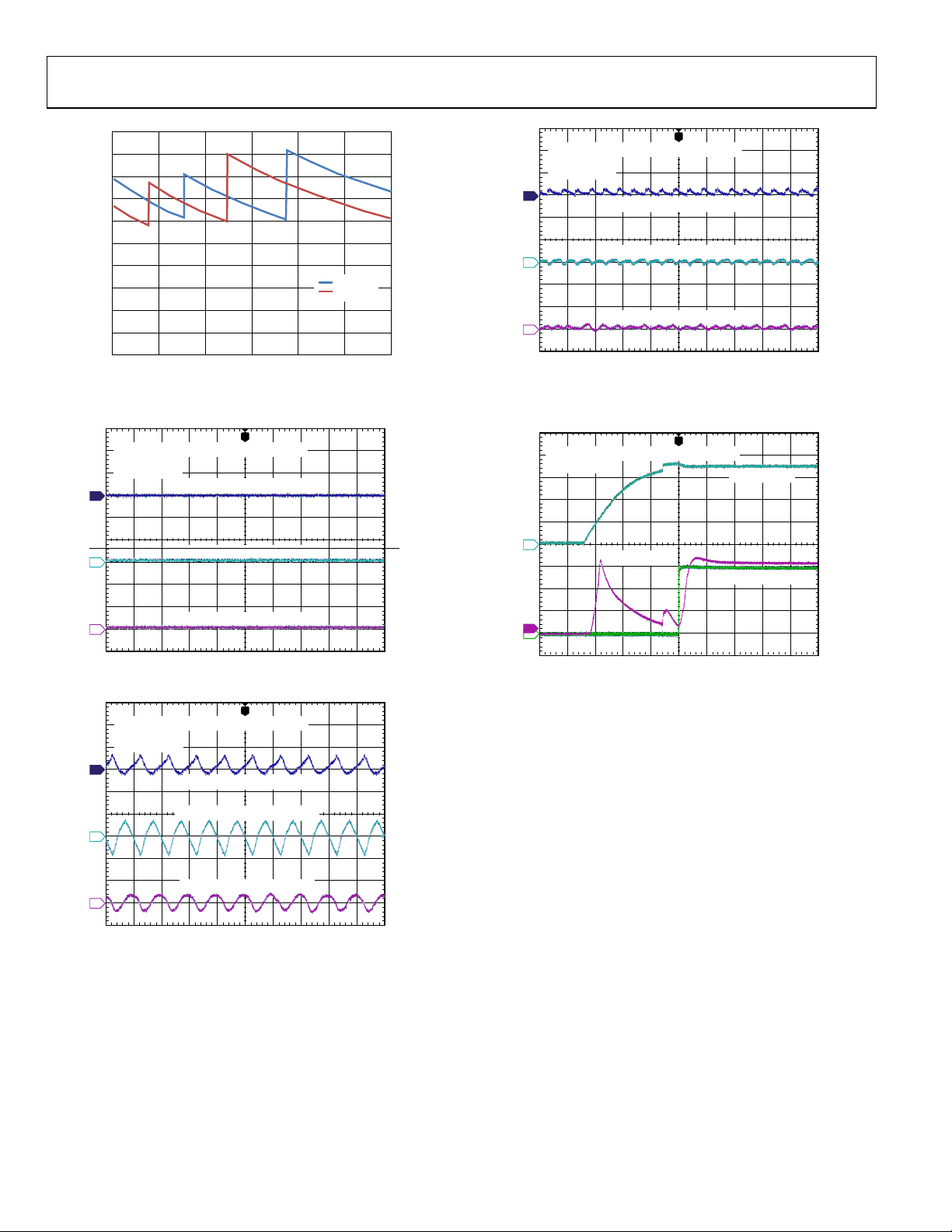

09478-024

1µs/DIV

1

2

3

V

IN

(AC-COUPLE D) 50mV /DIV

V

OUT

(AC-COUPLE D) 50mV /DIV

I

IN

(AC-COUPLE D) 10mA/DIV

T

C

IN

= 1µF, C

OUT

= 1µF, C1 = 1µ F, C2 = 1µF

V

IN

= 3.6V

I

OUT

= 120mA

09478-025

1µs/DIV

1

2

3

VIN (AC-COUPLE D) 50mV /DIV

V

OUT

(AC-COUPLE D) 50mV /DIV

IIN (AC-COUPLE D) 10mA/DIV

T

CIN = 1µF, C

OUT

= 1µF, C1 = 1µ F, C2 = 1µF

V

IN

= 3.0V

I

OUT

= 120mA

09478-026

1µs/DIV

1

2

3

VIN (AC-COUPLE D) 50mV /DIV

V

OUT

(AC-COUPLE D) 50mV /DIV

I

IN

(AC-COUPLE D) 10mA/DIV

T

C

IN

= 1µF, C

OUT

= 1µF, C1 = 1µ F, C2 = 1µF

V

IN

= 2.5V

I

OUT

= 120mA

09478-027

100µs/DIV

2

4

IIN (10mA/DIV)

V

OUT

(1V/DIV)

I

OUT

(10mA/DIV)

T

3

C

IN

= 10µF, C

OUT

= 1µF, C1 = 1µ F, C2 = 1µF

V

IN

= 3.6V

Figure 22. Typical Efficiency (Each LED Set to 25 mA)

Figure 25. Typical Operating Waveforms, G = 2×

Figure 23. Typical Operating Waveforms, G = 1×

Figure 24. Typical Operating Waveforms, G = 1.5×

Figure 26. Typical Startup Waveforms

Rev. 0 | Page 10 of 52

ADP8866

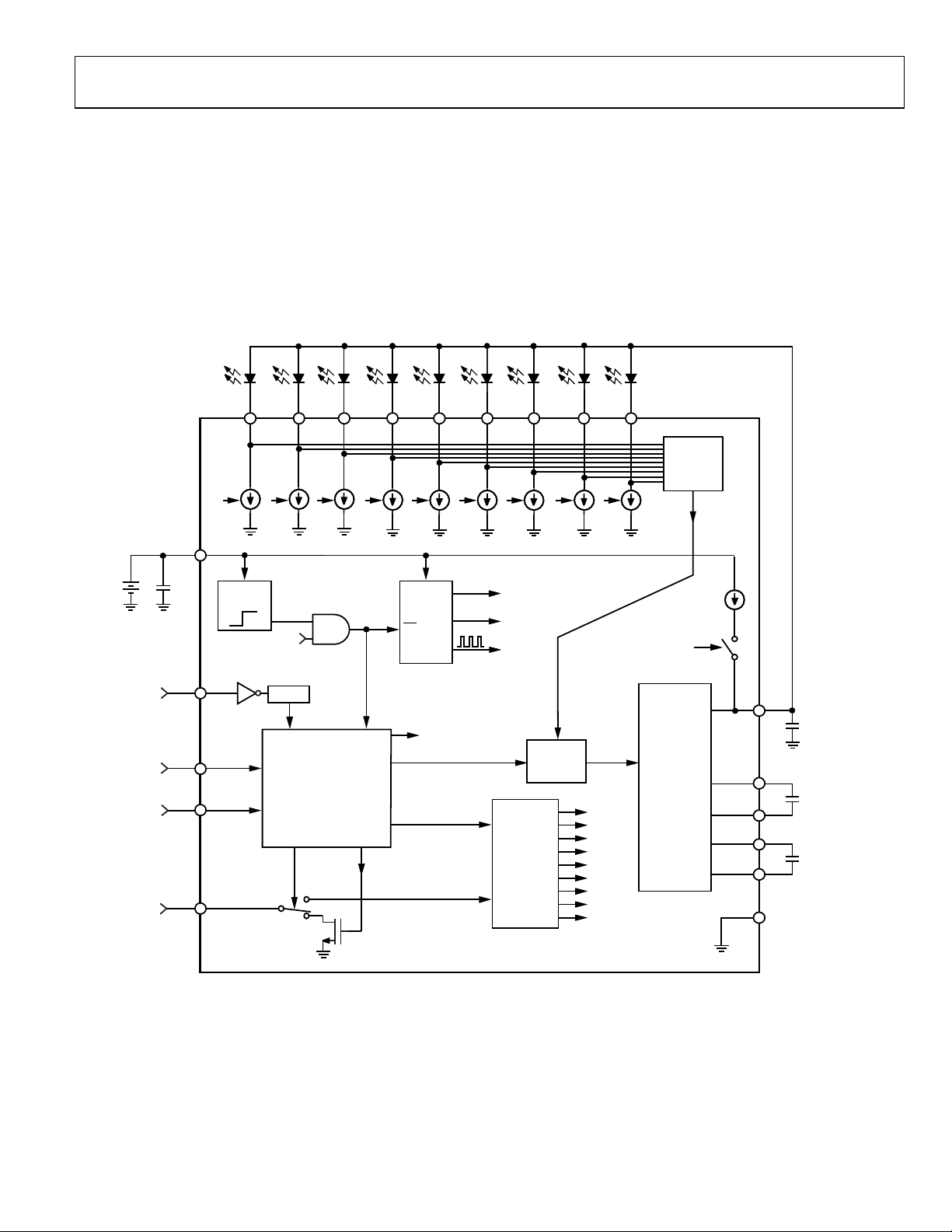

09478-028

C1

1µF

C2

1µF

nINT

C

OUT

VOUT

C

IN

VIN

V

REFS

I

REFS

STANDBY

EN

VIN

C1+

SDA

SCL

I2C LOGIC

STANDBY

ILED CONTROL

C1–

C2+

C2–

nRST

NOISE FILTER

50µs

RESET

D2 D3

D4 D5

D6 D7

D1

ID1

ID2

ID3

ID4 ID5

ID6

ID7

GAIN

SELECT

LOGIC

CHARGE

PUMP

LOGIC

GND

CLK

UVLO

CHARGE

PUMP

(1x, 1.5x, 2x)

SOFT

START

LED

OUTPUT

CURRENT

ID1

ID2

ID3

ID4

ID5

ID6

ID7

I

SS

D8 D9

ID8 ID9

ID8

ID9

nINT MUX INT

PWM

VIN

GAIN CONTROL

THEORY OF OPERATION

The ADP8866 combines a programmable backlight LED charge

pump driver with automatic blinking functions. Nine LED drivers

can be independently programmed at currents up to 25 mA.

The current level, fade time, and blinking rate can be programmed

once and executed autonomously on a loop. Separate fade-in

and fade-out times can be set for the backlight LEDs.

Driving all of this is a two capacitor charge pump with gains of

1×, 1.5×, and 2×. This setup is capable of driving a maximum

I

of 240 mA from a supply of 2.5 V to 5.5 V. A full suite of

OUT

safety features including short-circuit, overvoltage, and overtemperature protection allows easy implementation of a safe

and robust design. Additionally, input inrush currents are

limited via an integrated soft start combined with controlled

input to output isolation.

Figure 27. Detailed Block Diagram

Rev. 0 | Page 11 of 52

ADP8866

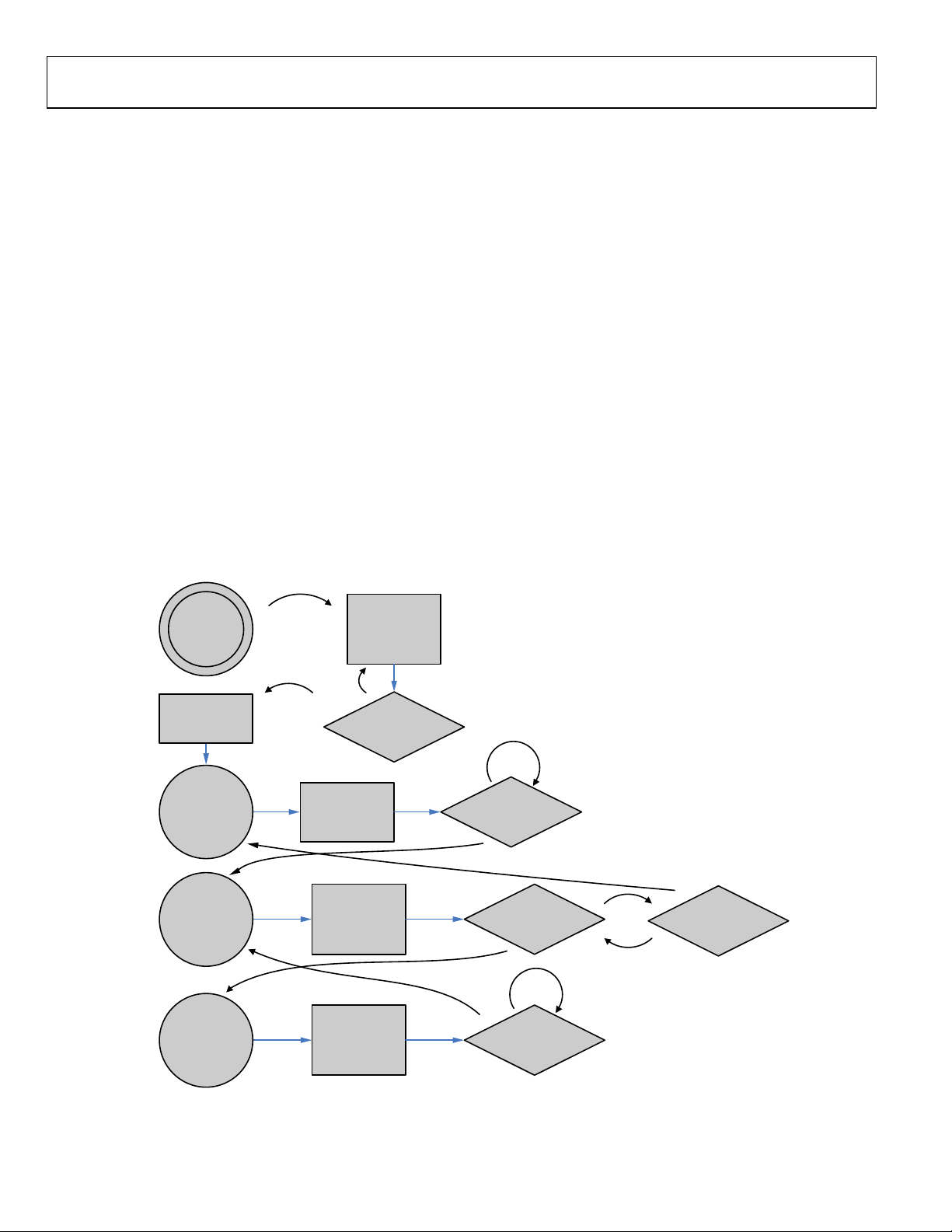

09478-029

NOTES

1. V

DMAX

IS THE CAL CULATED GAI N DOWN TRANSITION P OINT.

WAIT

100µs (TYP)

MIN (V

D1:D9

) < V

HR(UP)

0

0

1

1

1

1

0

0

STARTUP:

CHARGE

V

IN

TO V

OUT

EXIT STANDBY

VOUT > V

OUT(START)

1

WAIT

100µs (TYP)

WAIT

100µs (TYP)

MIN (V

D1:D9

) < V

HR(UP)

MIN (V

D1:D9

) > V

DMAX

MIN (V

D1:D9

) < V

DMAX

G = 2

G = 1.5

EXIT

STARTUP

G = 1

STANDBY

0

POWER STAGE

Typical white LEDs require up to 4 V to drive them. Therefore,

some form of boosting is required to cover the typical Li Ion

battery voltage variation. The ADP8866 accomplishes this with

a high efficiency charge pump capable of producing a maximum

I

of 240 mA over the entire input voltage range of 2.5 V to

OUT

5.5 V. Charge pumps use the basic principle that a capacitor

stores charge based on the voltage applied to it, as shown in the

following equation:

Q = C × V (1)

By charging the capacitors in different configurations, the

charge and, therefore, the gain can be optimized to deliver the

voltage required to power the LEDs. Because a fixed charging

and discharging combination must be used, only certain

multiples of gain are available. The ADP8866 is capable of

automatically optimizing the gain (G) from 1×, 1.5×, and 2×.

These gains are accomplished with two capacitors and an

internal switching network.

In G = 1× mode, the switches are configured to pass VIN

directly to VOUT. In this mode, several switches are connected

in parallel to minimize the resistive drop from input to output.

In G = 1.5× and G = 2× modes, the switches alternatively charge

from the battery and discharge into the output. For G = 1.5×,

the capacitors are charged from VIN in series and are discharged to

VOUT in parallel. For G = 2×, the capacitors are charged from

VIN in parallel and are discharged to VOUT in parallel. In

certain fault modes, the switches are opened and the output is

physically isolated from the input.

Automatic Gain Selection

Each LED that is driven requires a current source. The voltage

on this current source must be greater than a minimum headroom

voltage (V

) in Tabl e 1) to maintain accurate current

HR(MIN

regulation. The gain is automatically selected based on the

minimum voltage (V

) at all of the current sources. At startup,

DX

the device is placed into G = 1× mode and the output charges to

VIN. If any V

level is less than the required headroom, the

DX

gain is increased to the next step (G = 1.5×). A 100 μs delay is

allowed for the output to stabilize prior to the next gain

switching decision. If there remains insufficient current sink

headroom, the gain is increased again to 2×. Conversely, to

optimize efficiency, it is not desirable for the output voltage to be

too high. Therefore, the gain reduces when the headroom

voltage is too great. This point (labeled V

in Figure 28) is

DMAX

internally calculated to ensure that the lower gain still results in

ample headroom for all the current sinks. The entire cycle is

illustrated in Figure 28.

Figure 28. State Diagram for Automatic Gain Selection

Rev. 0 | Page 12 of 52

ADP8866

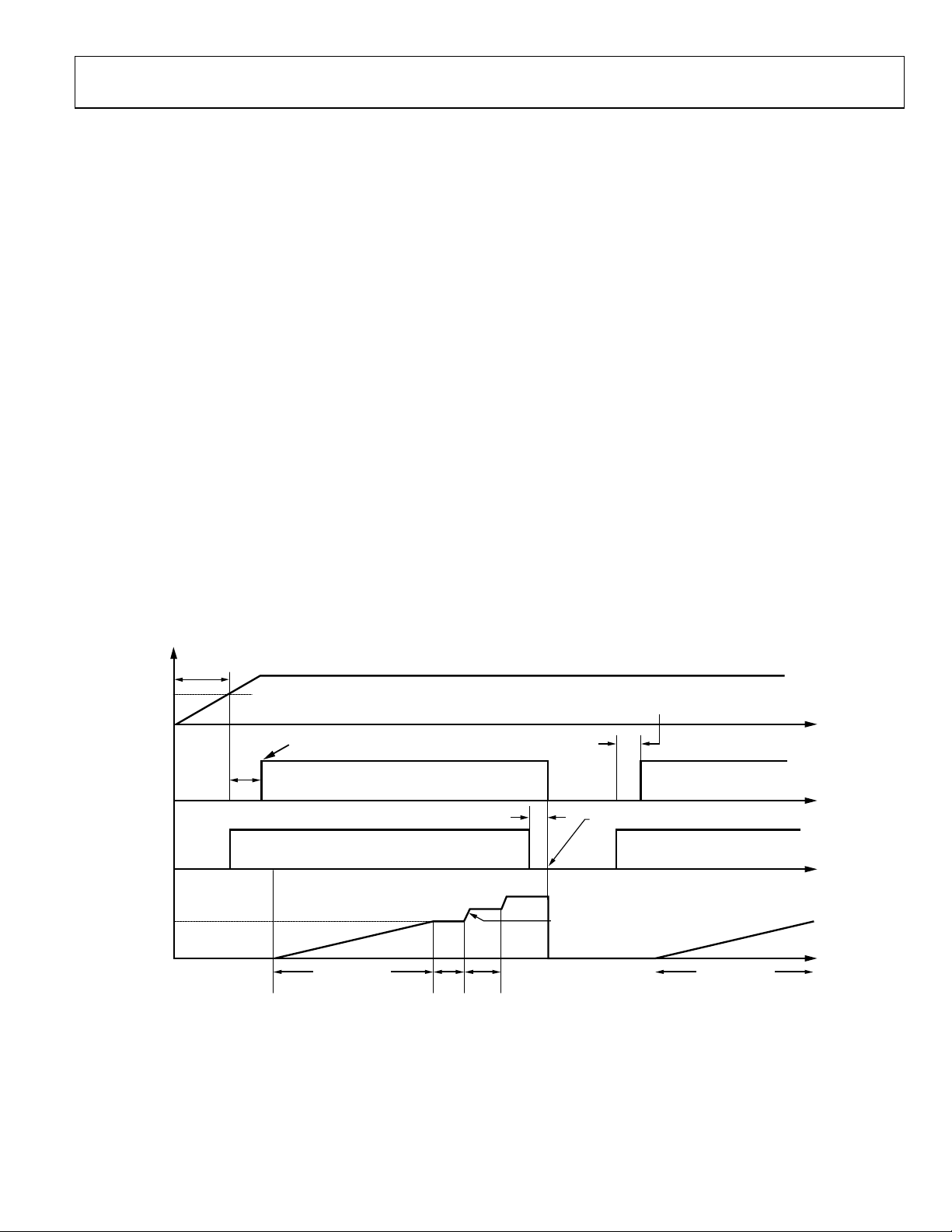

V

IN

nSTBY

nRST

V

OUT

V

IN

SHUTDOWN

VIN CROSSES ~ 2.0V AND TRIGGERS POWER ON RE S E T

BIT nSTBY IN REGISTER

MDCR GOES HIGH

nRST MUS T BE HIGH FOR 20µs (MAX )

BEFORE S E NDING I

2

C COMMANDS

nRST IS LOW, WHICH FORCES nSTBY LOW

AND RESETS ALL I

2

C REGISTERS

GAIN CHANGE S ONLY OCCUR WHEN NECESSARY

BUT HAVE A MI NIMUM TI M E BE FORE

CHANGING

~100µs DELAY BE TWEEN POWER UP AND

WHEN I

2

C COMMANDS CAN BE RE CE IVED

~7.0mA CHARGES

V

OUT

TO VIN LEVEL

25µs TO 100µ s NOISE F ILTER

1×

1.5×

2×

SOFT STARTSOFT START

10µs 100µs

09478-030

Note that the gain selection criteria applies only to active

current sources. If a current source has been deactivated

through an I

2

C command (that is, only five LEDs are used for

an application), the voltages on the deactivated current sources

are ignored.

Soft Start Feature

At startup (either from UVLO activation or fault/standby

recovery), the output is first charged by I

until it reaches about 92% of V

. This soft start feature reduces

IN

(7.0 mA typical)

SS

the inrush current that is otherwise present when the output

capacitance is initially charged to V

. When this point is

IN

reached, the controller enters 1× mode. If the output voltage is

not sufficient, the automatic gain selection determines the

optimal point as defined in the Automatic Gain Selection section.

OPERATING MODES

There are four different operating modes: active, standby,

shutdown, and reset.

Active Mode

In active mode, all circuits are powered up and in a fully

operational state. This mode is entered when nSTBY (in

Register MDCR) is set to 1.

Standby Mode

Standby mode disables all circuitry except for the I2C receivers.

Current consumption is reduced to less than 1 μA. This mode is

entered when nSTBY is set to 0 or when the nRST pin is held

low for more than 100 μs (maximum). When standby is exited,

a soft start sequence is performed.

Shutdown Mode

Shutdown mode disables all circuitry, including the I2C receivers.

Shutdown occurs when V

When V

rises above V

IN

is below the undervoltage thresholds.

IN

(2.0 V typical), all registers are

IN(START)

reset and the part is placed into standby mode.

Reset Mode

In reset mode, all registers are set to their default values and the

part is placed into standby. There are two ways to reset the part:

power on reset (POR) and the nRST pin. POR is activated anytime that the part exits shutdown mode. After a POR sequence

is complete, the part automatically enters standby mode.

After startup, the part can be reset by pulling the nRST pin low.

As long as the nRST pin is low, the part is held in a standby state

2

but no I

C commands are acknowledged (all registers are kept

at their default values). After releasing the nRST pin, all registers

remain at their default values, and the part remains in standby;

however, the part does accept I

2

C commands.

The nRST pin has a 50 μs (typical) noise filter to prevent inadvertent activation of the reset function. The nRST pin must be

held low for this entire time to activate reset.

The operating modes function according to the timing diagram

in Figure 29.

Figure 29. Typical Timing Diagram

Rev. 0 | Page 13 of 52

ADP8866

2

127

CurrentScaleFull

Codet(mA)LED_Curren

−

×=

25

20

15

10

5

0

0 12010080604020

OUTPUT CURRE NT (mA)

OUTPUT CURRE NT CODE (0 TO 127)

09478-031

25.00mA

12.50mA

8.33mA

6.25mA

5.00mA

09478-032

TIME

LED OUTP UT

CURRENT

nTNT PIN

(INPUT)

LED GROUPS

The nine LED channels can be separated into two groups: backlight

(BL) and independent sinks (ISC). The group select is done in

Register 0x09 and Register 0x0A, with the default being that all

LEDs are part of the backlight.

Each group has its own fade-in and fade-out times (Register

0x12 for backlight and Register 0x22 for ISCs). Each group also

has its own master enable located in Register 0x01. However,

this master enable is overwritten if any of the SCx_EN bits

(Register 0x1A and Register 0x1B) in a group are set high. This

allows complete independent control of each LED channel in

both groups.

OUTPUT CURRENT SETTINGS

The current setting is determined by a 7-bit code programmed

by the user into diode current control registers (Register 0x13

for the backlight and Register 0x23 to Register 0x2B for the

independent sinks). The 7-bit resolution allows the user to set

the backlight to one of 128 different levels between 0 mA and

25 mA. The ADP8866 implements a square law algorithm to

achieve a nonlinear relationship between input code and

backlight current. The LED output current (in milliamperes) is

determined by the following equation:

(2)

where:

Code is the input code programmed by the user.

Full-Scale Current is the maximum sink current allowed

per LED.

Figure 30. Output Code Effect on Various LEVEL_SET Ranges

The LEDs that receive this alternate current range are determined

by the DxLVL bits in Register 0x07 and Register 0x08.

PWM DIMMING

Setting the LEVEL_SET code to 111111 (binary) allows the

ADP8866 to dim its LEDs based on a PWM signal applied to the

nINT pin. The LED output current is pulse width modulated with

the signal applied to the nINT pin. The typical waveform and

timing are shown in Figure 29. Due to the inherent delays and

rise/fall times of this system, the best accuracy of the average output

current is obtained with PWM frequencies below 1 kHz.

OUTPUT CURRENT RANGE SELECTION

The default maximum current range of each sink of the

ADP8866 is 25.0 mA (typical). However, the ADP8866 also

allows the user to select an alternative maximum current range

to be applied to one or more LEDs. This alternate current range

still has 128 codes for its current setting. This provides

improved resolution when operating at reduced maximum

currents. One of up to 60 alternate current ranges can be

selected. An example of some of the available current ranges is

shown below. For the complete list, see Tab le 23.

Table 5. Example Current Range Options in Register 0x07

LEVEL_SET Code Range

000010 25.00 mA

001100 12.50 mA

010110 8.33 mA

100000 6.25 mA

101010 5.00 mA

In this mode, the nINT pin functions as an input. It no longer

provides notification of the INT_STAT register.

AUTOMATED FADE-IN AND FADE-OUT

The LED drivers are easily configured for automated fade-in

and fade-out. Sixteen fade-in and fade-out rates can be selected

via the I

0.0 sec to 1.75 sec (per full-scale current). Separate fade times are

assigned to the backlight LEDs and the ISC LEDs (see the LED

Groups section). The BLOFF_INT bit in Register 0x02 can be used

to flag the interrupt pin when an automated backlight fade-out has

occurred.

Rev. 0 | Page 14 of 52

Figure 31. PWM Input Waveform and Resultant LED Current

2

C interface. Fade-in and fade-out rates range from

ADP8866

30

0

5

10

15

20

25

0 1.000.750.500.25

CURRENT (mA)

UNIT FADE TIME

SQUARE

CUBIC 11

CUBIC 10

09478-033

09478-034

BACKLIGHT CURRE NT

CABCFADE = 0 (DEFAULT)

BL EN = 1 BL EN = 0

TIME

FADE IN

COMPLETE

CHANGE

BL SETTING

CHANGE

BL SETTING

CABCFADE = 1

MAX

SCx_EN

SCx

CURRENT

FADE-IN FADE-OUT FADE-IN FADE-OUT

ON TIME ON TIME

OFF

TIME

OFF

TIME

SET BY USER

09478-035

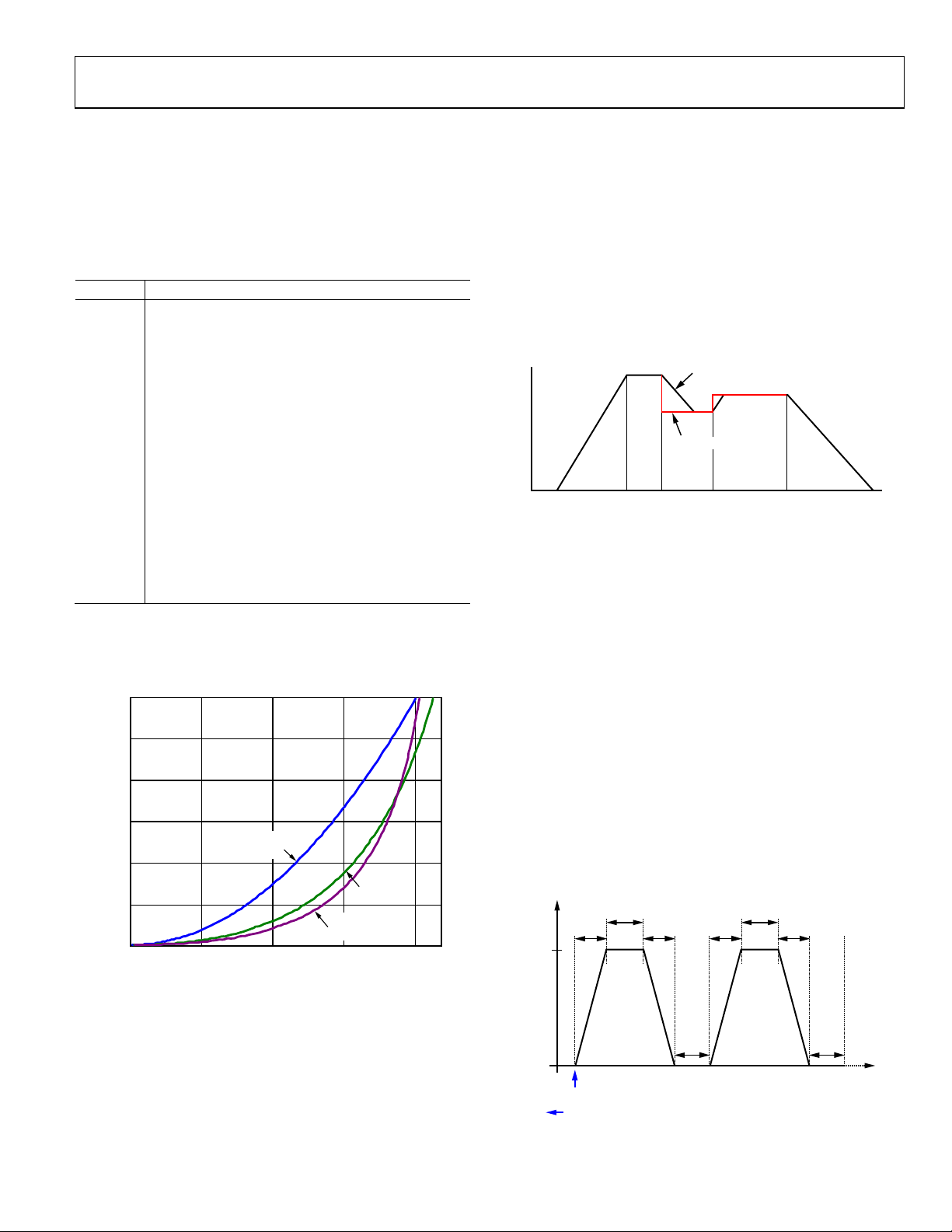

The fade profile is based on the transfer law selected (square,

Cubic 10, or Cubic 11) and the delta between the actual current

and the target current. Smaller changes in current reduce the

fade time. For square law fades, the fade time is given by

Fade Time = Fade Rate × (Code/127) (4)

where the Fade Rate is shown in Tabl e 6.

Table 6. Available Fade-In and Fade-Out Times

Code Fade Rate (Seconds per 128 Codes)

0000 0.0

0001 0.05

0010 0.10

0011 0.15

0100 0.20

0101 0.25

0110 0.30

0111 0.35

1000 0.40

1001 0.45

1010 0.50

1011 0.75

1100 1.0

1101 1.25

1110 1.50

1111 1.75

The Cubic 10 and Cubic 11 laws also use the square backlight

currents in Equation 3; however, the time between each step is

varied to produce a steeper slope at higher currents and a

shallower slope at lighter currents (see Figure 32).

brightness control) operation, the BLMX register is updated as

often as 60 times per second. And the changes to BLMX must

be implemented as soon as possible. Therefore, the ADP8866

has a unique mode that allows the backlight to have very fast

changes after the initial ramp in and ramp out. This mode is

entered when CABCFADE in Register 0x10 is set high.

In this mode, the backlight fades in when BL_EN and nSTBY in

Register 0x01 are set high, and it fades out when BL_EN or

nSTBY is set low. However, after the fade-in is complete, any

changes to the BLMX register result in near instantaneous

changes to the backlight current. The situation is illustrated in

Figure 33.

Figure 33. Effect of the CABCFADE Bit

INDEPENDENT SINK CONTROL (ISC)

Each of the nine LEDs can be configured (in Register 0x10 and

Register 0x11) to operate as either part of the backlight or an

independent sink current (ISC). Each ISC can be enabled

independently and has its own current level. All ISCs share the

same fade-in rates, fade-out rates, and fade law.

The ISCs have additional timers to facilitate blinking functions.

A shared on timer (SCON), used in conjunction with the off

timers of each ISC (SC1OFF, SC2OFF, SC3OFF, SC4OFF,

SC5OFF, SC6OFF, and SC7OFF; see Register 0x1C through

Register 0x21) allow the LED current sinks to be configured in

various blinking modes. The on and off times are listed in the

Register Descriptions section. Blink mode is activated by setting

the off timers to any setting other than disabled.

Figure 32. Comparison of the Dimming Transfers Law 25 mA Scale Shown

CABC FADE DISABLE

The fade settings applied to the backlight in Register 0x12 are

also used when the BLMX (Register 0x13) current is changed.

This provides a smooth transition to new backlight current

levels.

Howe ver, in some modes of operation, this feature is not

desired. For example, during cABC (content adjustable

Figure 34. LEDx Blink Mode with Fading

Rev. 0 | Page 15 of 52

ADP8866

09478-036

EN

SCFI

ISCx CURRENT

ISCx_HB CURRENT

SCFO SCFI SCFO

EVEN PULSE

OFFTIMERx

0 TO 126 SEC

SCON

0 TO 750ms

SCON_HB

0 TO 750ms

OFFTIMERx_HB

0 T

O 126 SEC

CURRENT (mA)

EVEN PULSE

ODD PULSE

ODD PULSE

Program all fade-in and fade-out timers before enabling any of

the LED current sinks. If ISCx is on during a blink cycle and

SCx_EN in Register 0x1B is cleared, it turns off (or fades to off

if fade-out is enabled). If ISCx is off during a blink cycle and

SCx_EN is cleared, it stays off.

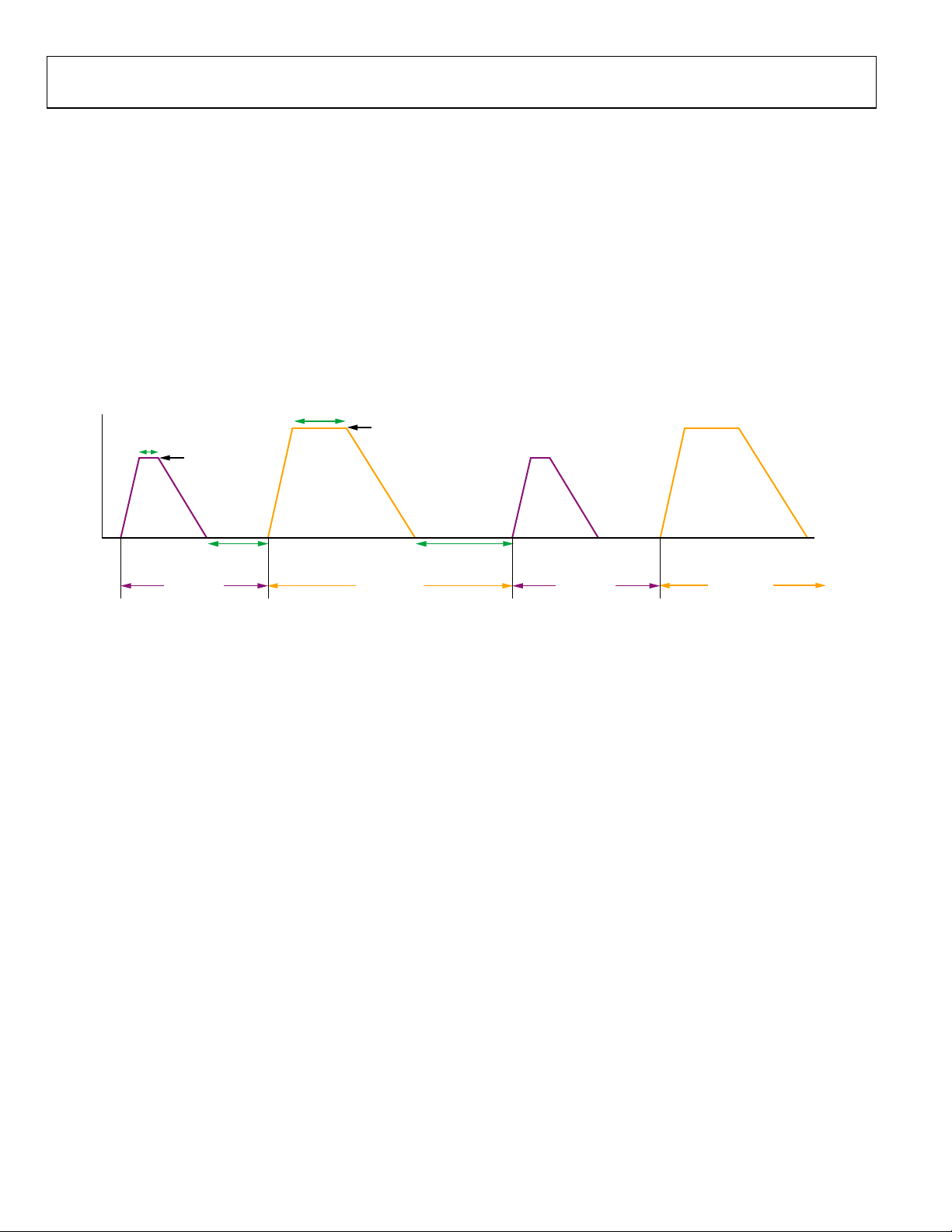

ADVANCED BLINKING CONTROLS

Diode D1 to Diode D5 have basic blinking controls, while

Channel D6 to Channel D9 have much more advanced

capabilities. These advanced features include

• Programmable delays: Register 0x3C to Register 0x3F set

the individual delays for D6 to D9. Delays are activated

when the individual diode is enabled. Delay times range

from 0 sec to 1.270 sec in 10 ms increments.

• Additional off time selections: D6 to D9 off times that

range from 0 sec to 12.5 sec in 100 ms increments (Register

0x1E to Register 0x21). The off times can also be set to off,

which turns the channel off at the completion of the blink

cycle. The LED turns on again when the enable signal is

toggled.

• Heartbeat mode: This mode allows a double pulse to be

issued in a fully automated and customizable loop. Register

0x2C through Register 0x35 control the heartbeat effect.

Up to four channels (D6 to D9) can be configured to

operate in the heartbeat mode. The approximate shape of

the heartbeat is shown in Figure 35:

Figure 35. Customizable Heartbeat Pulse

Rev. 0 | Page 16 of 52

Loading...

Loading...