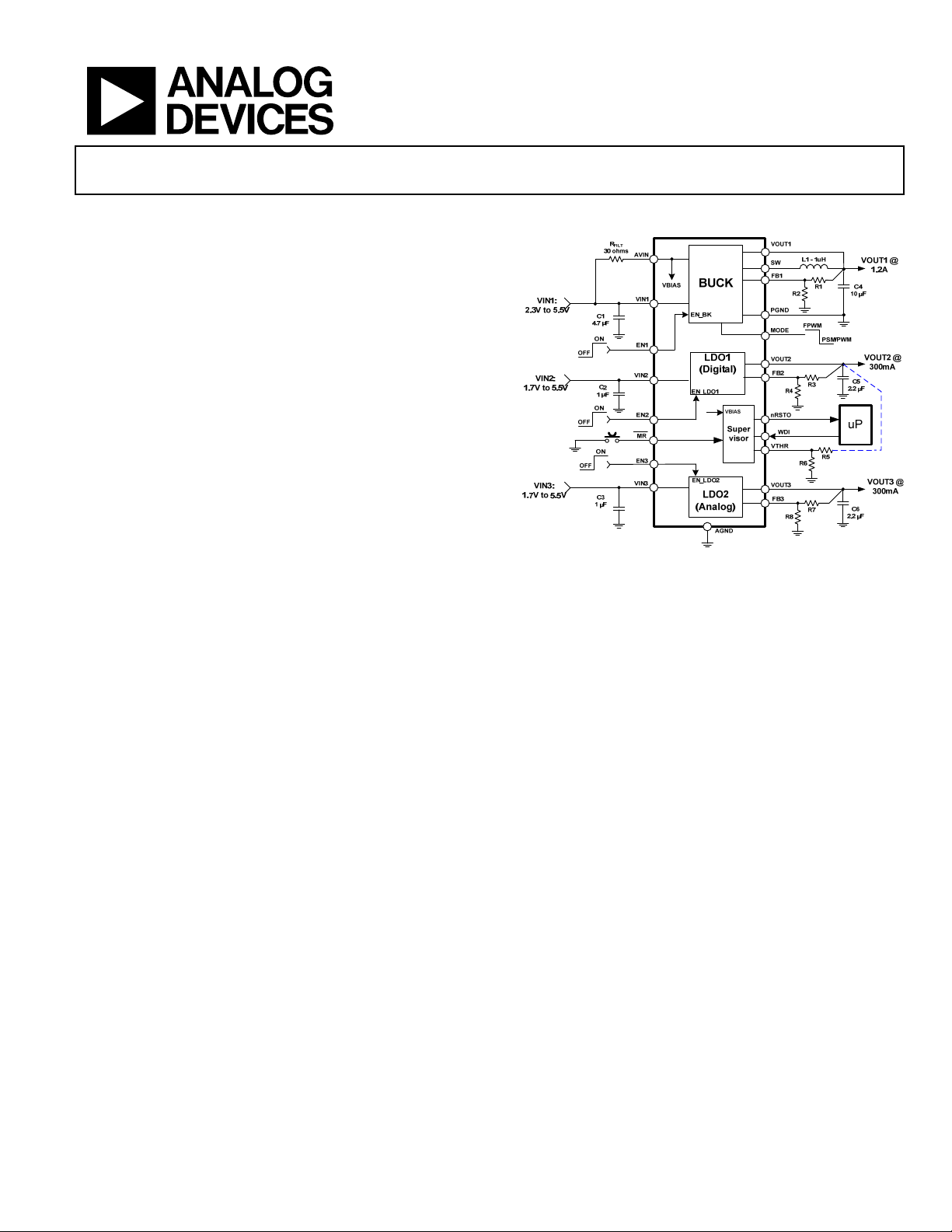

Micro PMU with 1.2 A Buck, Two 300 mA LDOs

Supervisory, Watchdog and Manual Reset

Preliminary Technical Data

FEATURES

Input voltage range: 2.3 V to 5.5 V

One 1.2 A buck regulator

Two 300 mA LDOs

20-lead, 4 mm × 4 mm LFCSP package

Overcurrent and thermal protection

Soft start

Undervoltage lockout

Open drain processor reset with externally adjustable

threshold monitoring

Guaranteed reset output valid to V

Manual reset input

Watchdog refresh input

Buck key specifications

Output voltage range 0.8 V to 3.8 V

Current mode topology for excellent transient response

3 MHz operating frequency

Peak Efficiency up to 96%

Uses tiny multilayer inductors and capacitors

Mode pin selects forced PWM or auto PWM/PSM modes

100% duty cycle low dropout mode

LDOs key specifications

Output Voltage Range 0.8 V to 5.2 V

Low input supply voltage from 1.7 V to 5.5 V

Stable with 2.2 μF ceramic output capacitors

High PSRR, 60 dB PSRR up to 1 kHz/10 kHz

Low output noise

Low dropout voltage

−40°C to +125°C junction temperature range

AVIN

= 1 V

ADP5041

HIGH LEVEL BLOCK DIAGRAM

Figure 1.

GENERAL DESCRIPTION

The ADP5041 combines one high performance buck regulator and

two low dropout regulators (LDO) in a small 20-lead LFCSP to

meet demanding performance and board space requirements.

The high switching frequency of the buck regulator enables

use of tiny multilayer external components and minimizes board

space.

When the MODE pin is set to logic high, the buck regulator

operates in forced PWM mode. When the MODE pin is set to logic

low, the buck regulator operates in PWM mode when the load is

around the nominal value. When the load current falls below a

predefined threshold the regulator operates in power save mode

(PSM) improving the light-load efficiency.

The low quiescent current, low dropout voltage, and wide input

Rev. PrE

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

voltage range of the ADP5041 LDOs extend the battery life of

portable devices. The ADP5041 LDOs maintain a power supply

rejection greater than 60 dB for frequencies as high as 10 kHz while

operating with a low headroom voltage.

Each regulator in ADP5041 is activated by a high level on the

respective enable pin. The regulators’ output voltages and the reset

threshold are programmed though external resistor dividers to

address a variety of applications. The ADP5041 contains

supervisory circuits that monitor power supply voltage levels and

code execution integrity in microprocessor-based systems. They

also provide power-on reset signals. An on-chip watchdog timer

can reset the microprocessor if it fails to strobe within a preset

timeout period.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

ADP5041 Preliminary Technical Data

TABLE OF CONTENTS

Features .............................................................................................. 1

High Level Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

General Specification ................................................................... 3

Supervisory Specification ............................................................ 3

Buck Specifications ....................................................................... 4

LDO1, LDO2 Specifications ....................................................... 5

Input and Output Capacitor, Recommended Specifications .. 6

Absolute Maximum Ratings ............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Typical Performance Characteristics ............................................. 9

Theory of Operation ...................................................................... 18

Power Management Unit ........................................................... 18

Buck Section ................................................................................ 19

LDO Section ............................................................................... 20

Supervisory Section ................................................................... 20

Applications Information .............................................................. 23

Buck External Component Selection ....................................... 23

LDO EXTERNAL COMPONENT Selection ......................... 24

Supervisory Section ................................................................... 25

Power Dissipation/Thermal Considerations ............................. 26

PCB Layout Guidelines .............................................................. 28

Suggested Layout ........................................................................ 29

Bill of Materials ........................................................................... 29

Application Diagram ................................................................. 30

Factory Programmable Options ................................................... 31

Outline Dimensions ....................................................................... 32

Ordering Guide .......................................................................... 32

Rev. PrE | Page 2 of 32

Preliminary Technical Data ADP5041

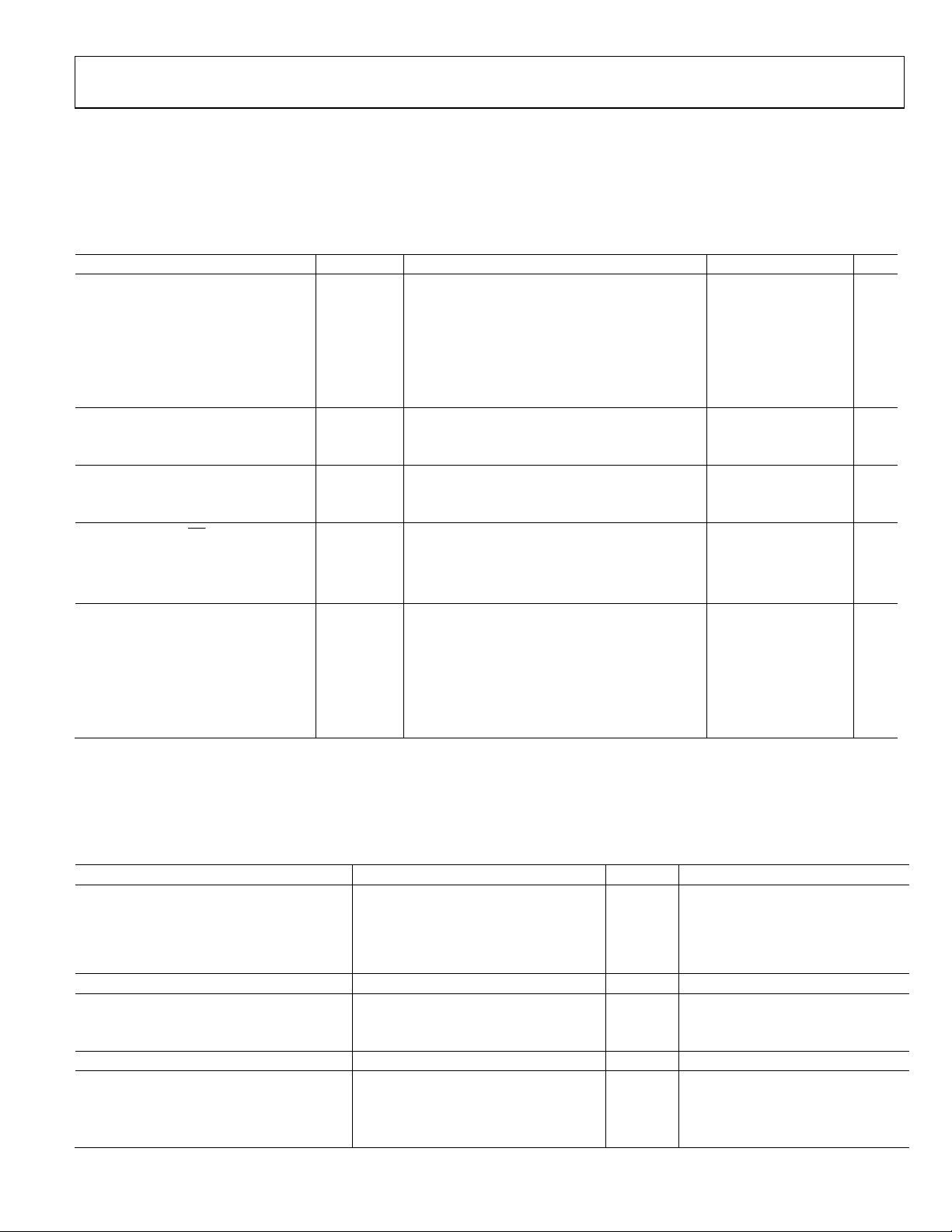

SPECIFICATIONS

GENERAL SPECIFICATION

AVIN, VIN1 = 2.3V to 5.5V; AVIN, VIN1 ≥VIN2, VIN3; VIN2, VIN3 = 1.7 V to 5.5 V, TJ = −40°C to +125°C for minimum/maximum

specifications, and T

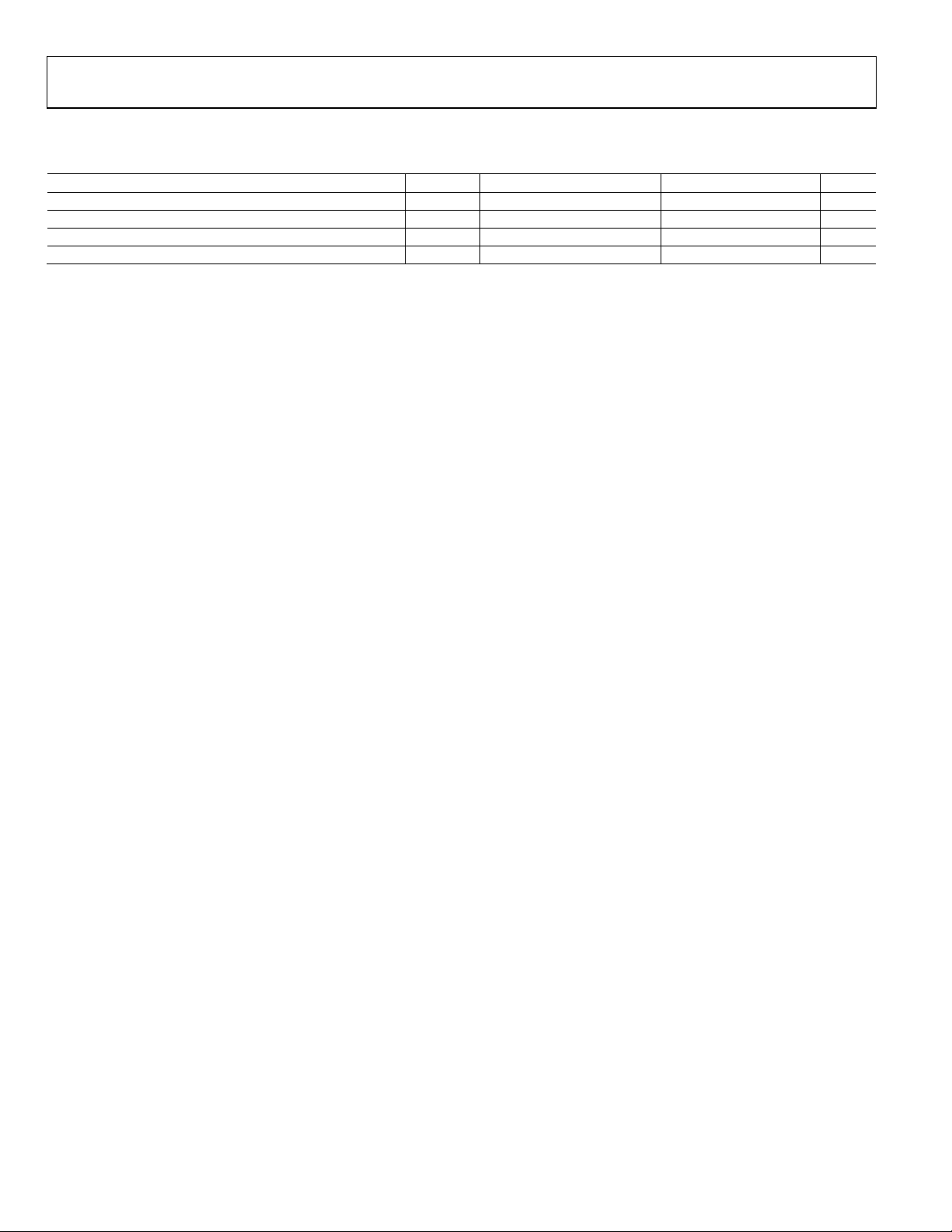

Table 1.

Parameter Symbol Description Min Typ Max Unit

AVIN UNDERVOLTAGE LOCKOUT UVLO

Input Voltage Rising UVLO

Option 0 2.275 V

Option 1 3.9 V

Input Voltage Falling UVLO

Option 0 1.95 V

Option 1 3.1 V

SHUTDOWN CURRENT I

Thermal Shutdown Threshold TSSD T

Thermal Shutdown Hysteresis TS

START-UP TIME1

BUCK t

LDO1, LDO2 t

ENx, WDI, MODE, MR INPUTS

Input Logic High VIH 2.5 V ≤ AVIN ≤ 5.5 V 1.2 V

Input Logic Low VIL 2.5 V ≤ AVIN ≤ 5.5 V 0.4 V

Input Leakage Current V

OPEN-DRAIN OUTPUT

nRSTO Output Voltage V

V

V

V

Open-Drain Reset Output Leakage

Current

= 25°C for typical specifications, unless otherwise noted.

A

AVIN

AVIN RI SE

AVIN FALL

ENx = GND 0.1 2 µA

GND-SD

rising 150 °C

J

20 °C

SD-HYS

250 µs

START1

START2

VOUT2, VOUT3 = 3.3 V

ENx = AVIN or GND 0.05 1 µA

I-LEAKAGE

OL1V

OL1V2

AVIN ≥ 2.7 V, I

OL2V7

AVIN ≥ 4.5 V, I

OL4V5

AVIN ≥ 1.0 V, I

AVIN ≥ 1.2 V, I

= 50 μA

SINK

= 100 μA

SINK

= 1.2 mA 0.3

SINK

= 3.2 mA 0.4

SINK

AVIN = 5.5 V 1 µA

85 µs

0.3

0.3

V

V

V

V

SUPERVISORY SPECIFICATION

AVIN, VIN1 = 2.3 V to 5.5 V; TJ = -40°C to +125°C for minimum/maximum specifications, and TA = 25°C for typical specifications

unless otherwise noted.

Table 2.

Parameter Min Typ Max Unit Test Conditions/Comments

SUPPLY

Supply Current (Supervisory Circuit Only) 45 55 µA

43 52 µA

THRESHOLD VOLTAGE 0.495 0.500 0.505 V

RESET TIMEOUT PERIOD

ADP5041B 24 30 36 ms

ADP5041C 160 200 240 ms

VCC TO RESET DELAY 80 µs VIN falling at 1 mV/µs

WATCHDOG INPUT

Watchdog Timeout Period

ADP5041xX 81.6 102 122.4 ms

ADP5041xY 1.28 1.6 1.92 sec

Rev. PrE | Page 3 of 32

AVIN = VIN1 = EN1 = EN2 = EN3 =

5.5V

AVIN = VIN1 = EN1 = EN2 = EN3 =

3.6V

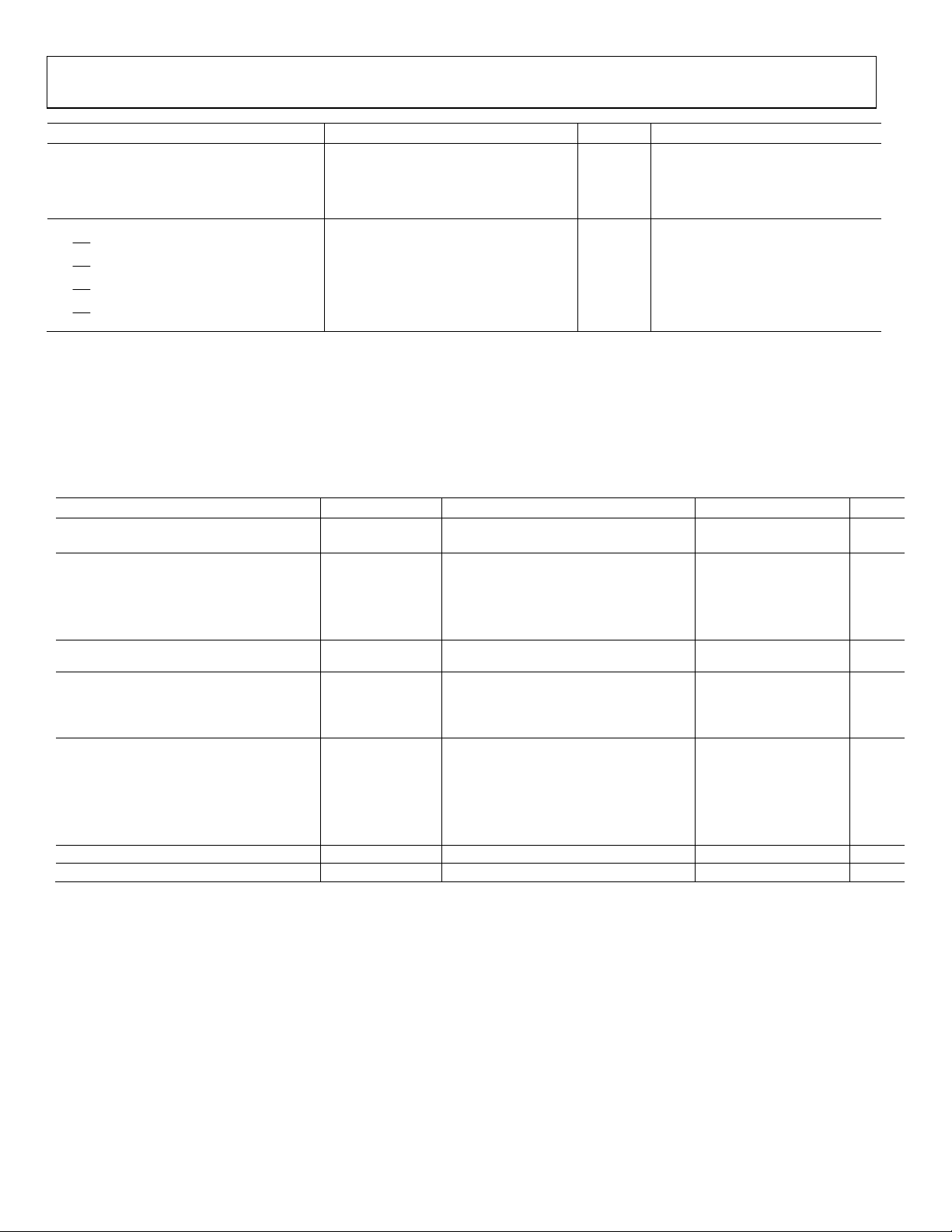

ADP5041 Preliminary Technical Data

Parameter Min Typ Max Unit Test Conditions/Comments

WDI Pulse Width 80 ns VIL = 0.4 V, VIH = 1.2 V

WDI Input Threshold 0.4 1.2 V

WDI Input Current (Source) 8 15 20 µA V

WDI Input Current (Sink) −30 −25 -15 µA V

MANUAL RESET INPUT

MR Input Pulse Width

MR Glitch Rejection

MR Pull-Up Resistance

MR to Reset Delay

1

Start-up time is defined as the time from EN1 = EN2 = EN3 from 0 V to V

Start-up times are shorter for individual channels if another channel is already enabled. See the Typical Performance Characteristics section for more information.

1 µs

220 ns

25 52 90 kΩ

280 ns VCC = 5 V

to VOUT1, VOUT2, and VOUT3 reaching 90% of their nominal level.

AVIN

BUCK SPECIFICATIONS

AVIN, VIN1 = 2.3V to 5.5 V; V

specifications, and T

= 25°C for typical specifications, unless otherwise noted.1

A

Table 3.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Input Voltage Range VIN1 2.3 5.5 V

OUTPUT CHARACTERISTICS

Output Voltage Accuracy V

Line Regulation (∆V

Load Regulation (∆V

VOLTAGE FEEDBACK V

PWM TO POWER SAVE MODE CURRENT

THRESHOLD

INPUT CURRENT CHARACTERISTICS MODE = ground

DC Operating Current I

Shutdown Current I

SW CHARACTERISTICS

SW On Resistance R

PFET, AVIN = VIN1 = 5 V 140 190 mΩ

R

NFET, AVIN = VIN1 = 5 V 150 210 mΩ

Current Limit I

ACTIVE PULL-DOWN EN1 = 0 V 85 Ω

OSCILLATOR FREQUENCY F

1

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

= 1.8 V; L = 1 µH; CIN = 10 µF; C

OUT1

PWM mode, I

OUT1

OUT1/VOUT1

OUT1/VOUT1

0.485 0.5 0,515 V

FB1

I

PSM_L

NOLOAD

SHTD

PFET

NFET

LIMIT

OSC

)/∆V

)/∆I

100 mA

EN1 = 0 V, TA = TJ = −40°C to +125°C 0.2 1.0 A

NFET, AVIN = VIN1 = 3.6 V 170 235 mΩ

2.5 3.0 3.5 MHz

= 10 µF; TJ= −40°C to +125°C for minimum/maximum

OUT

= 0 mA to 1200 mA −3 +3 %

LOAD

PWM mode -0.05 %/V

IN1

I

OUT1

= mA to 1200 mA, PWM mode -0.1 %/A

LOAD

I

= 0 mA, device not switching, all other

LOAD

channels disabled

PFET, AVIN = VIN1 = 3.6 V 180 240 mΩ

PFET switch peak current limit 1600 1950 2300 mA

= VCC, time average

WDI

= 0, time average

WDI

21 35 A

Rev. PrE | Page 4 of 32

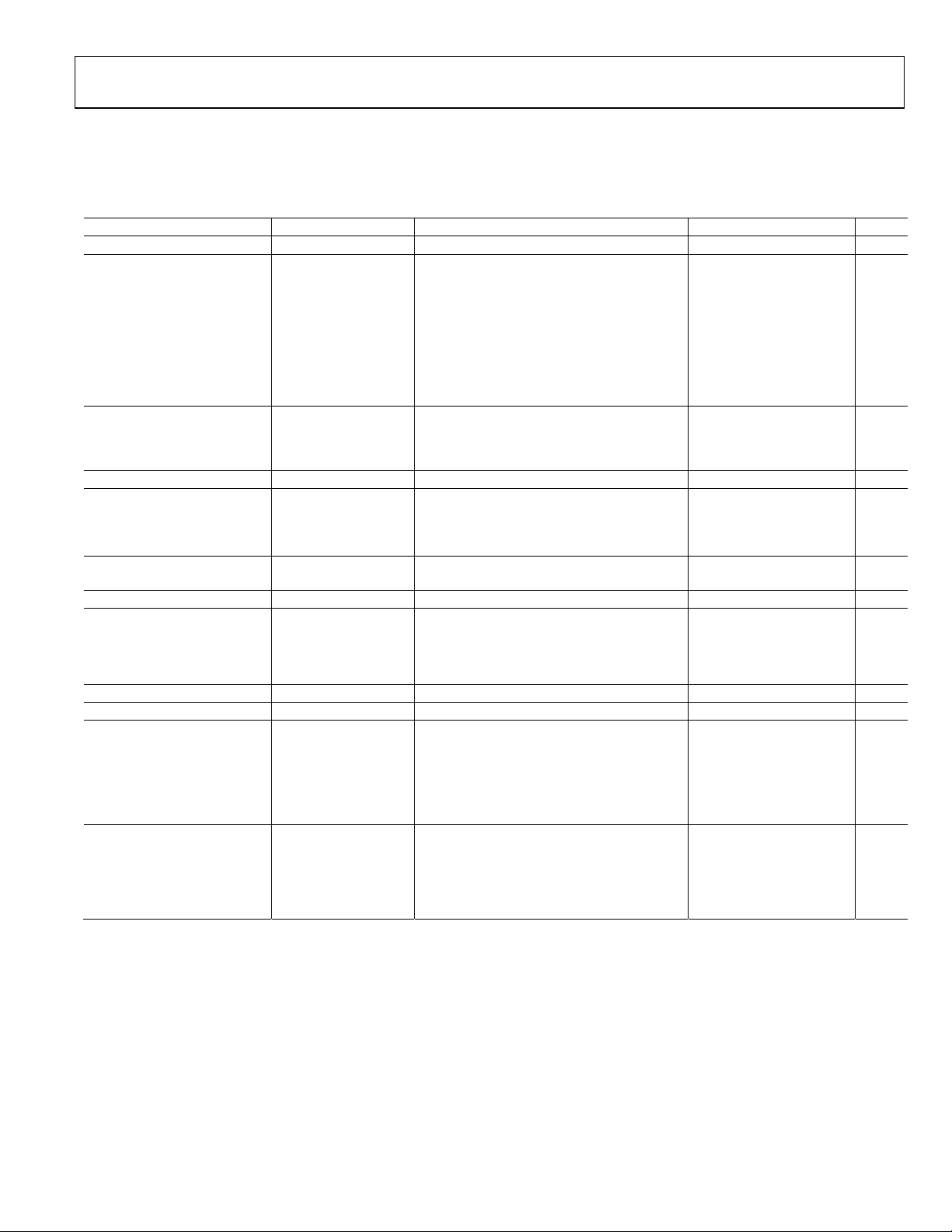

Preliminary Technical Data ADP5041

LDO1, LDO2 SPECIFICATIONS

V

to +125°C for minimum/maximum specifications and T

Table 4.

1

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

2

This is the input current into VIN2/VIN3, which is not delivered to the output load.

3

Based on an end-point calculation using 1 mA and 300 mA loads.

4

Dropout voltage is defined as the input-to-output voltage differential when the input voltage is set to the nominal output voltage. This applies only for output

5

Current-limit threshold is defined as the current at which the output voltage drops to 90% of the specified typical value. For example, the current limit for a 3.0 V

IN2, VIN3

= (V

OUT2,VOUT3

+ 0.5 V) or 1.7 V (whichever is greater) to 5.5V; AVIN, VIN1 ≥ VIN2, VIN3; CIN = 1 µF, C

= 25°C for typical specifications, unless otherwise noted. 1

A

= 2.2 µF; TJ= −40°C

OUT

Parameter Symbol Conditions Min Typ Max Unit

INPUT VOLTAGE RANGE V

, V

T

IN2

IN3

= −40°C to +125°C 1.7

J

5.5 V

OPERATING SUPPLY CURRENT

Bias Current per LDO2

I

Total System Input Current

I

VIN2BIAS

IIN

/ I

I

VIN3BIAS

= I

= 0 µA

OUT4

= I

= 10 mA 60 100 µA

OUT3

= I

= 300 mA 165 245 µA

OUT3

I

OUT3

OUT2

OUT2

Includes all current into AVIN, VIN1, VIN2 and

10 30 µA

VIN3

LDO1 or LDO2 Only

LDO1 and LDO2 Only

OUTPUT VOLTAGE ACCURACY V

OUT2, VOUT3

100 µA < I

I

I

OUT2

OUT2

= I

= 0 µA, all other channels disabled

OUT3

= I

= 0 µA, buck disabled

OUT3

< 300 mA, 100 µA < I

OUT2

< 300 mA

OUT3

53

74

µA

µA

−3 +3 %

VIN2 = (VOUT2 + 0.5 V) to 5.5 V,

VIN3 = (VOUT3 + 0.5 V) to 5.5 V

REFERENCE VOLTAGE V

0.485 0.500 0.515 V

FB2,3

REGULATION

Line Regulation (∆V

(∆V

OUT2/VOUT2

OUT3/VOUT3

)/∆V

)/∆V

IN2

IN3

I

Load Regulation3 (∆V

DROPOUT VOLTAGE4 V

(∆V

DROPOUT

OUT2/VOUT2

OUT3/VOUT3

)/∆I

OUT2

)/∆I

OUT3

ACTIVE PULL-DOWN R

CURRENT-LIMIT THRESHOLD5 I

OUTPUT NOISE OUT

EN2/EN3 = 0 V 600 Ω

PDLDO

T

LIMIT

10 Hz to 100 kHz, VIN3 = 5 V, VOUT3 = 3.3 V 123 µV rms

LDO2NOISE

VIN2,

VIN3 = (VOUT2, VOUT3 + 0.5 V)

to 5.5 V

= 1 mA

OUT2, IOUT3

I

= 1 mA to 300 mA 0.002 0.0075 %/mA

OUT2, IOUT3

V

= V

= V

= V

= V

OUT3

OUT3

OUT3

OUT3

= 5.0 V, I

= 3.3 V, I

= 2.5 V, I

= 1.8 V, I

OUT2

V

OUT2

V

OUT2

V

OUT2

= −40°C to +125°C 335 470 mA

J

OUT2

OUT2

OUT2

OUT2

= I

= 300 mA

OUT3

= I

= 300 mA

OUT3

= I

= 300 mA

OUT3

= I

= 300 mA

OUT3

−0.03 +0.03 %/ V

72 mV

86 140 mV

107 mV

180 mV

10 Hz to 100 kHz, VIN3 = 5 V, VOUT3 = 2.8 V 110 µV rms

10 Hz to 100 kHz, VIN3 = 5 V, VOUT3 = 1.5 V 59 µV rms

OUT

10 Hz to 100 kHz, VIN2 = 5 V, VOUT2 = 3.3 V 140 µV rms

LDO1NOISE

10 Hz to 100 kHz, VIN2 = 5 V, VOUT2 = 2.8 V 129 µV rms

10 Hz to 100 kHz, VIN2 = 5 V, VOUT2 = 1.5 V 66

POWER SUPPLY REJECTION RATIO PSRR 1 kHz, V IN2, VIN3 = 3.3 V, VOUT2, VOUT3 = 2.8 V,

= 100 mA

I

OUT

100 kHz, VIN2, VIN3 = 3.3 V, VOUT2, VOUT3 = 2.8 V,

= 100 mA

I

OUT

1 MHz, VIN2, VIN3 = 3.3 V, VOUT2, VOUT3 = 2.8 V,

I

= 100 mA

OUT

66 dB

57 dB

60 dB

µV rms

voltages above 1.7 V.

output voltage is defined as the current that causes the output voltage to drop to 90% of 3.0 V, or 2.7 V.

Rev. PrE | Page 5 of 32

ADP5041 Preliminary Technical Data

INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS

Table 5.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CAPACITANCE (BUCK)1 C

OUTPUT CAPACITANCE (BUCK)2 C

INPUT AND OUTPUT CAPACITANCE3 (LDO1, LDO2) C

CAPACITOR ESR R

1

The minimum input capacitance should be greater than 4.7 µF over the full range of operating conditions. The full range of operating conditions in the application

must be considered during device selection to ensure that the minimum capacitance specification is met. X7R and X5R type capacitors are recommended, Y5V and

Z5U capacitors are not recommended for use with the Buck.

2

The minimum output capacitance should be greater than 7 µF over the full range of operating conditions. The full range of operating conditions in the application

must be considered during device selection to ensure that the minimum capacitance specification is met. X7R and X5R type capacitors are recommended, Y5V and

Z5U capacitors are not recommended for use with the Buck.

3

The minimum input and output capacitance should be greater than 0.70 µF over the full range of operating conditions. The full range of operating conditions in the

application must be considered during device selection to ensure that the minimum capacitance specification is met. X7R and X5R type capacitors are recommended,

Y5V and Z5U capacitors are not recommended for use with LDOs.

T

MIN1

T

MIN2

TJ = −40°C to +125°C 0.70 µF

MIN34

T

ESR

= −40°C to +125°C 4.7 40 µF

J

= −40°C to +125°C 7 40 µF

J

= −40°C to +125°C 0.001 1 Ω

J

Rev. PrE | Page 6 of 32

Preliminary Technical Data ADP5041

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter Rating

AVIN to AGND −0.3 V to +6 V

VIN1 to AVIN −0.3 V to +0.3 V

PGND to AGDN −0.3 V to +0.3 V

VIN2, VIN3, VOUTx, ENx, MODE, MR , WDI,

nRSTO, FBx, VTHR, SW to AGND

SW to PGND −0.3 V to (VIN1 + 0.3 V)

Storage Temperature Range −65°C to +150°C

Operating Junction Temperature Range −40°C to +125°C

Soldering Conditions JEDEC J-STD-020

ESD Human Body Model 3000 V

ESD Charged Device Model 1500 V

ESD Machine Model 200 V

Stresses above those listed under absolute maximum ratings

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

−0.3 V to (AVIN + 0.3 V)

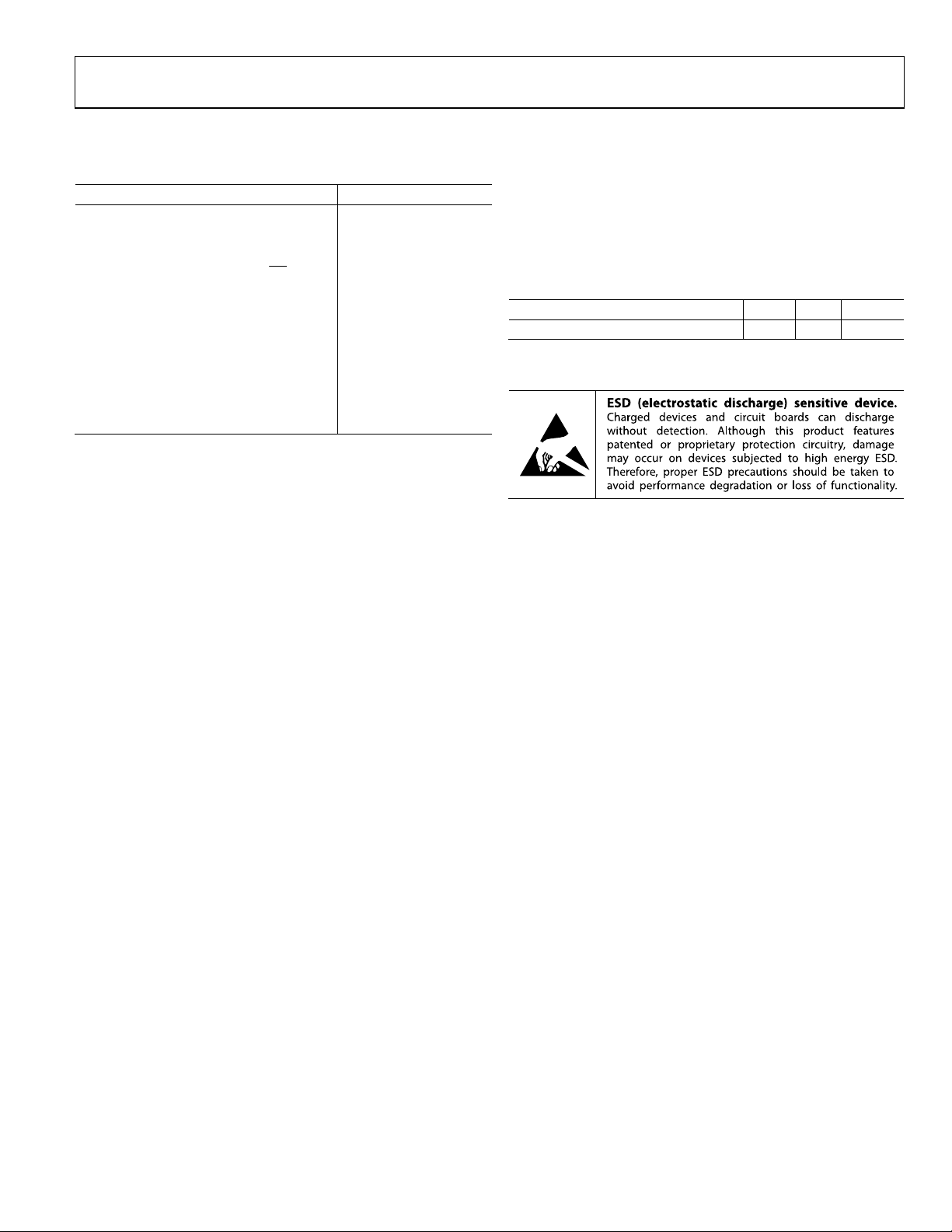

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 7. Thermal Resistance

Package Type θJA θJC Unit

20-Lead, 0.5 mm pitch LFCSP 38 4.2 °C/W

ESD CAUTION

Rev. PrE | Page 7 of 32

ADP5041 Preliminary Technical Data

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration—View from Top of the Die

Table 8. Preliminary Pin Function Descriptions

Pin No. Mnemonic Description

1 FB3 LDO2 Feedback Input

2 VOUT3 LDO2 Output Voltage

3 VIN3 LDO2 Input Supply (1.7V to 5.5V)

4 EN3 EN3 = HIGH: Turn LDO2. EN3 = LOW: Turn off LDO2.

5 nRSTO Open-Drain reset output, active low

6 AVIN Housekeeping and Supervisory Input Supply (2.3V to 5.5V)

7 VIN1 BUCK Input Supply (2.3V to 5.5V)

8 SW BUCK switching Node

9 PGND Dedicated Power Ground for BUCK regulator

10 EN1 EN1 = HIGH: Turn BUCK. EN1 = LOW: Turn off BUCK.

11 VOUT1 BUCK Output Sensing Node

12 FB1 BUCK Feedback Input

13 VIN2 LDO1 Input Supply (1.7V to 5.5V)

14 VOUT2 LDO1 Output Voltage

15 FB2 LDO1 Feedback Input

16 EN2 EN2 = HIGH: Turn LDO1. EN2 = LOW: Turn off LDO1.

17 MODE

18 VTHR Reset Threshold Programming

19 WDI Watchdog Refresh input from processor. If WDI is in HiZ, Watchdog is disabled

20

TP AGND Analog Ground (TP = Exposed Pad). Exposed pad must be connected to system Ground Plane

MR

HIGH: The Buck regulator operates in fixed PWM mode. MODE = LOW: The Buck regulator operates in power

saving mode (PSM) at light load and in constant PWM at higher load.

Manual Reset Input, active low

Rev. PrE | Page 8 of 32

Preliminary Technical Data ADP5041

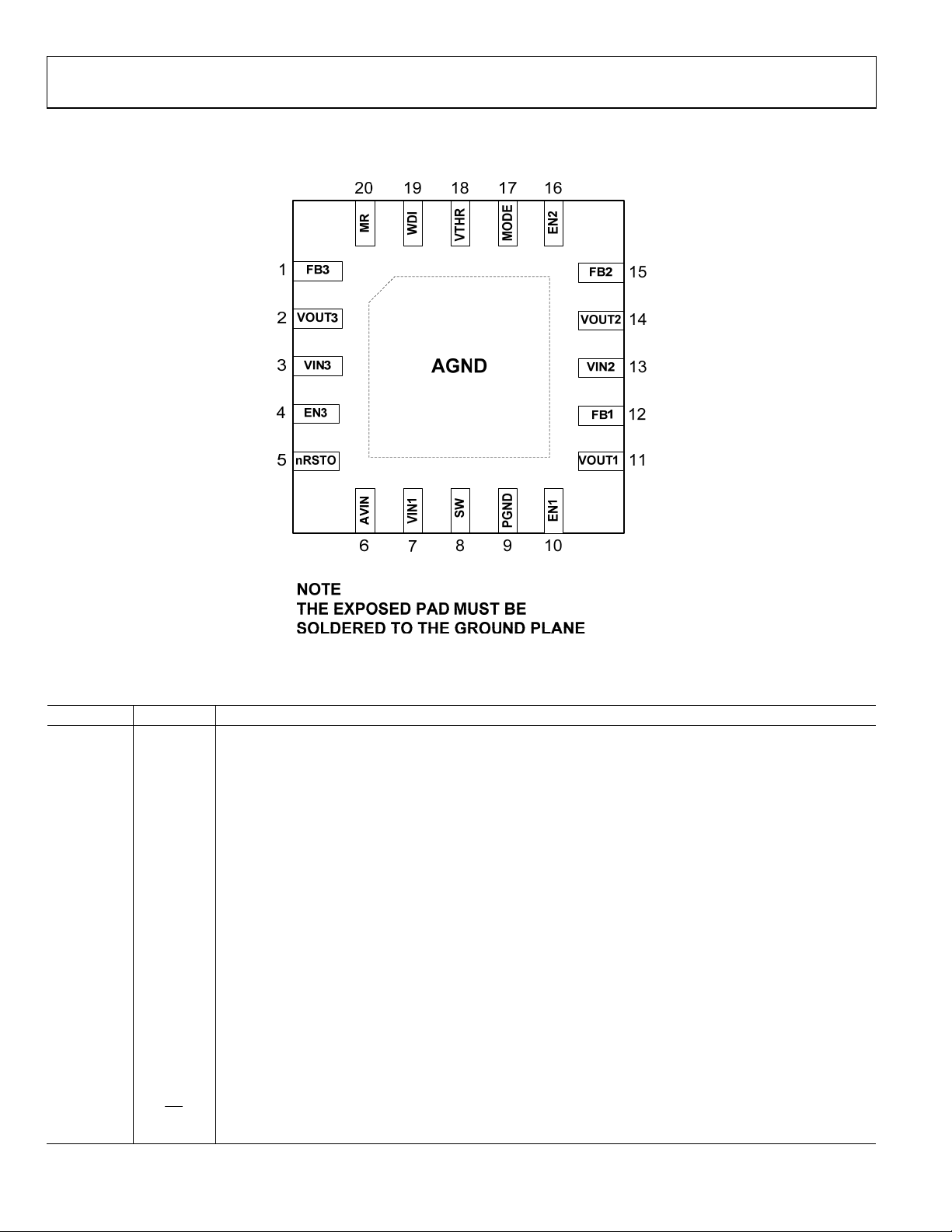

TYPICAL PERFORMANCE CHARACTERISTICS

VIN1 = VIN2 = VIN3 = AVIN = 5.0 V, TA = 25°C, unless otherwise noted.

1

2

3

VOUT1

VOUT2

VOUT3

CH1 2.0V/DIV 1MΩ

CH2 2.0V/DIV 1MΩ

CH3 2.0V/DIV 1MΩ

B

20.0M

W

B

W

B

W

A CH1 1.76V 200µs/DIV

500M

20.0M

50.0MS/s

20.0ns/pt

08811-003

Figure 3. 3-Channel Start-Up Waveforms

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

SYSTEM QUI ESCENT CURRENT (mA)

0.1

0

2.3 2.8 3 .3 3.8 4.3 4.8 5. 3

VOUT1 = 1.8V,

VOUT2 = VO UT = 3.3V

INPUT VOLTAGE (V)

08811-004

Figure 4. System Quiescent Current (Sum of All the Input Currents) vs. Input Voltage,

VOUT1 = 1.8 V, VOUT2 = VOUT3 = 3.3 V

08811-006

Figure 6. Buck Startup, VOUT1 = 3.3 V, I

3.34

3.32

3.30

3.28

3.26

OUTPUT VOLTAGE (V)

3.24

3.22

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

OUTPUT CURRENT (A)

OUT2

= 20 mA

–40°C

+25°C

+85°C

08811-007

Figure 7. Buck Load Regulation Across Temperature, VOUT1 = 3.3 V, Auto Mode

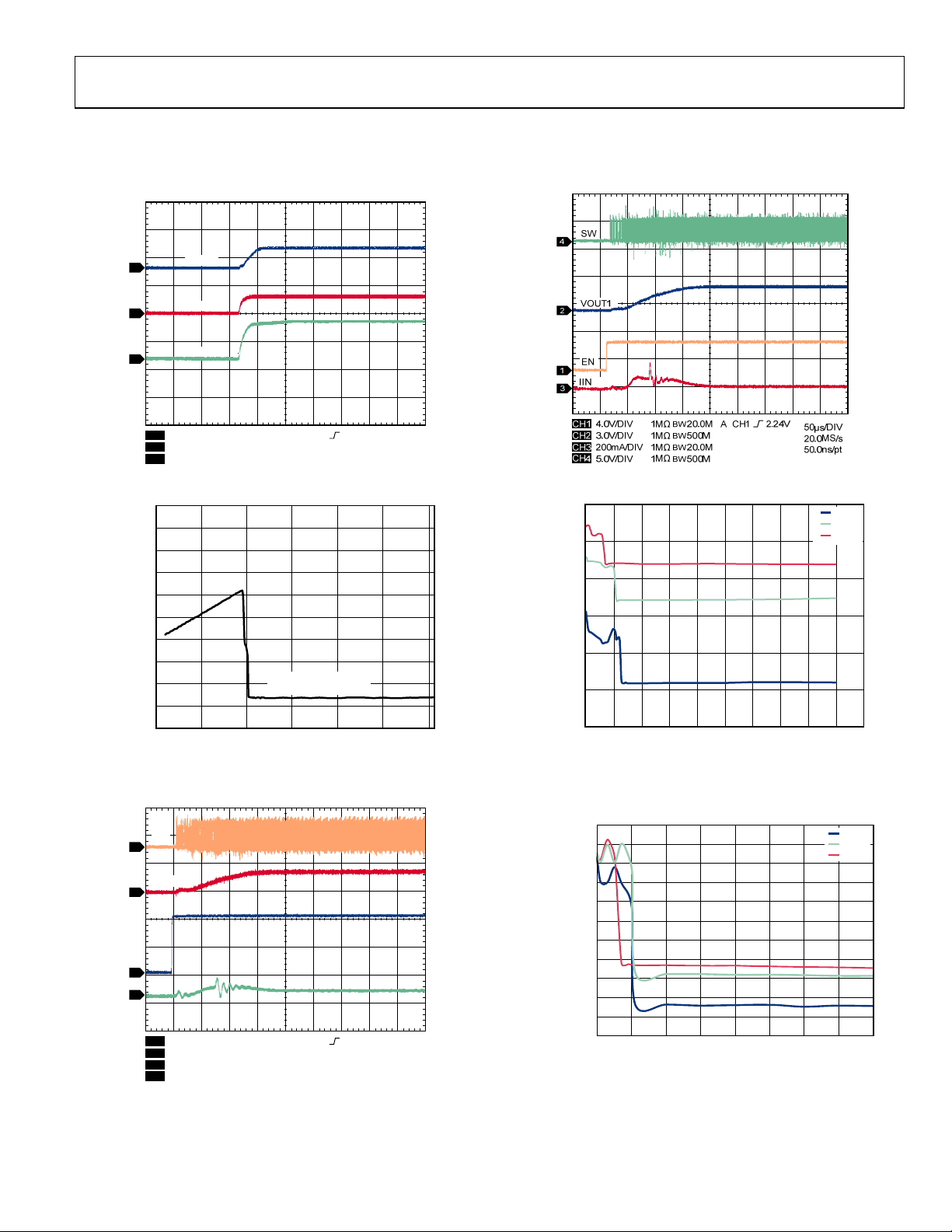

SW

4

VOUT1

2

EN

1

IIN

3

CH1 2.0V/DIV 1MΩ

CH2 2.0V/DIV 1MΩ

CH3 100mA/DIV 1MΩ

CH4 5.0V/DIV 1MΩ

B

20.0M

W

B

500M

W

B

20.0M

W

B

500M

W

Figure 5. Buck Startup, VOUT1 = 1.8 V, I

A CH1 2.92V 50µs/DIV

OUT1

50.0MS/s

20.0ns/pt

= 20 mA

08811-005

Figure 8. Buck Load Regulation Across Temperature, VOUT1 = 1.8 V, Auto Mode

Rev. PrE | Page 9 of 32

1.830

1.825

1.820

1.815

1.810

1.805

1.800

1.795

OUTPUT VO LTAGE (V)

1.790

1.785

1.780

1.775

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

OUTPUT CURRENT (A)

–40°C

+25°C

+85°C

08811-008

ADP5041 Preliminary Technical Data

1.795

1.794

1.793

1.792

1.791

1.790

1.789

1.788

OUTPUT VOLTAGE (V)

1.787

1.786

1.785

1.784

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

+85°C

+25°C

–40°C

08811-009

OUTPUT CURRENT (A)

Figure 9. Buck Load Regulation Across Temperature, VOUT1 = 1.8 V, PWM Mode

1.797

1.796

1.795

1.794

1.793

OUTPUT VO LTAGE (V )

1.792

1.791

1.790

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8

VIN = 5.5V

VIN = 4.5V

VIN = 3.6V

08811-010

OUTPUT CURRENT (A)

Figure 10. Buck Load Regulation Across Input Voltage, VOUT1 = 1.8 V, PWM Mode

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.0001 0.001 0.01 0.1 1

OUTPUT CURRENT (A)

3.6V

4.5V

5.5V

08811-011

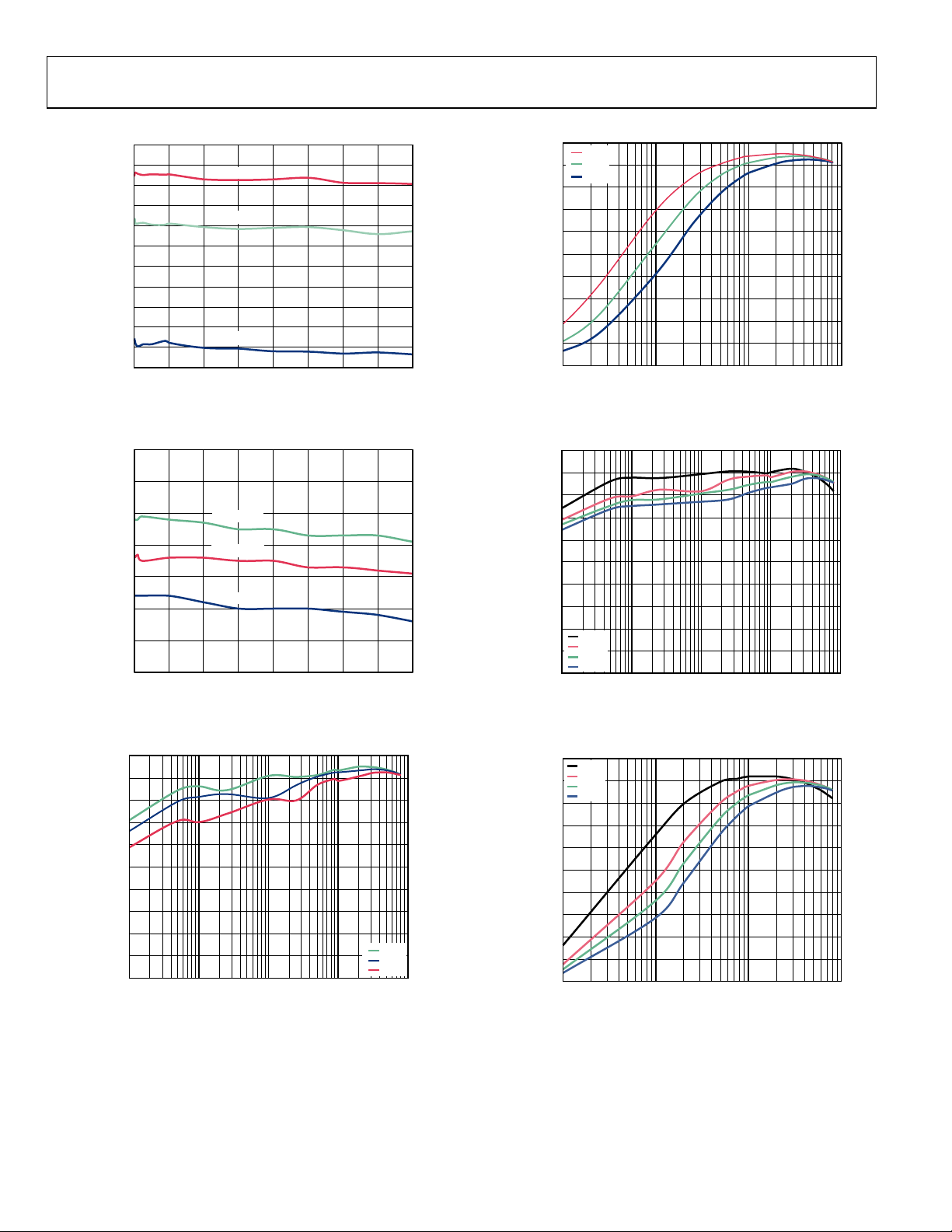

Figure 11. Buck Efficiency vs. Load Current, Across Input Voltage,

VOUT1 = 3.3 V, Auto Mode

100

3.6V

4.5V

90

5.5V

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.001 0.01 0.1 1

OUTPUT CURRENT (A)

Figure 12. Buck Efficiency vs. Load Current, Across Input Voltage,

VOUT1 = 3.3 V, PWM Mode

100

90

80

70

60

50

40

EFFICIENCY (%)

30

20

2.4V

3.6V

10

4.5V

5.5V

0

0.0001 0. 001 0. 01 0. 1 1

OUTPUT CURRENT (A)

Figure 13. Buck Efficiency vs. Load Current, Across Input Voltage,

VOUT1 = 1.8 V, Auto Mode

100

2.4V

3.6V

90

4.5V

5.5V

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.001 0.01 0.1 1

I

(A)

OUT

Figure 14. Buck Efficiency vs. Load Current, Across Input Voltage,

VOUT1 = 1.8 V, PWM Mode

08811-012

08811-013

08811-014

Rev. PrE | Page 10 of 32

Loading...

Loading...