ANALOG DEVICES ADP5024 Service Manual

Dual 3 MHz, 1200 mA Buck

Data Sheet

FEATURES

Main input voltage range: 2.3 V to 5.5 V

Two 1200 mA buck regulators and one 300 mA LDO

24-lead, 4 mm × 4 mm LFCSP package

Regulator accuracy: ±3%

Factory programmable or external adjustable VOUTx

3 MHz buck operation with forced PWM and automatic

PWM/PSM modes

BUCK1/BUCK2: output voltage range from 0.8 V to 3.8 V

LDO: output voltage range from 0.8 V to 4.75 V

LDO: low input supply voltage from 1.7 V to 5.5 V

LDO: high PSRR and low output noise

APPLICATIONS

Power for processors, ASICS, FPGAs, and RF chipsets

Portable instrumentation and medical devices

Space constrained devices

Regulators with One 300 mA LDO

ADP5024

GENERAL DESCRIPTION

The ADP5024 combines two high performance buck regulators and one low dropout (LDO) regulator in a small, 24-lead,

4 mm × 4 mm LFCSP to meet demanding performance and

board space requirements.

The high switching frequency of the buck regulators enables tiny

multilayer external components and minimizes the board space.

When the MODE pin is set high, the buck regulators operate in

forced PWM mode. When the MODE pin is set low, the buck

regulators operate in PWM mode when the load current is above

a predefined threshold. When the load current falls below a predefined threshold, the regulator operates in power save mode

(PSM), improving the light load efficiency.

The two bucks operate out of phase to reduce the input capacitor

requirement. The low quiescent current, low dropout voltage, and

wide input voltage range of the LDO extends the battery life of

portable devices. The ADP5024 LDO maintains power supply

rejection greater than 60 dB for frequencies as high as 10 kHz

while operating with a low headroom voltage.

Regulators in the ADP5024 are activated though dedicated

enable pins. The default output voltages can be either externally

set in the adjustable version or factory programmable to a wide

range of preset values in the fixed voltage version.

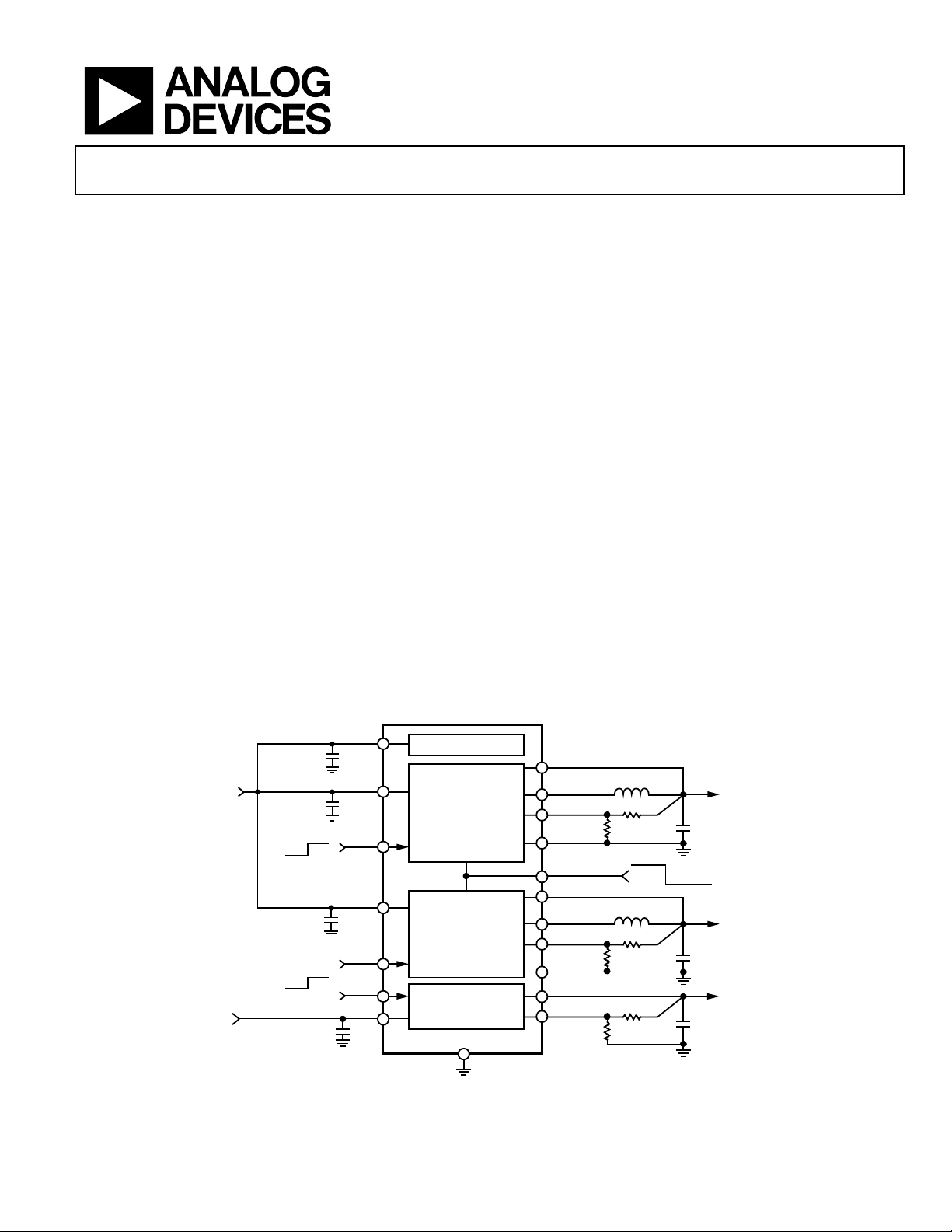

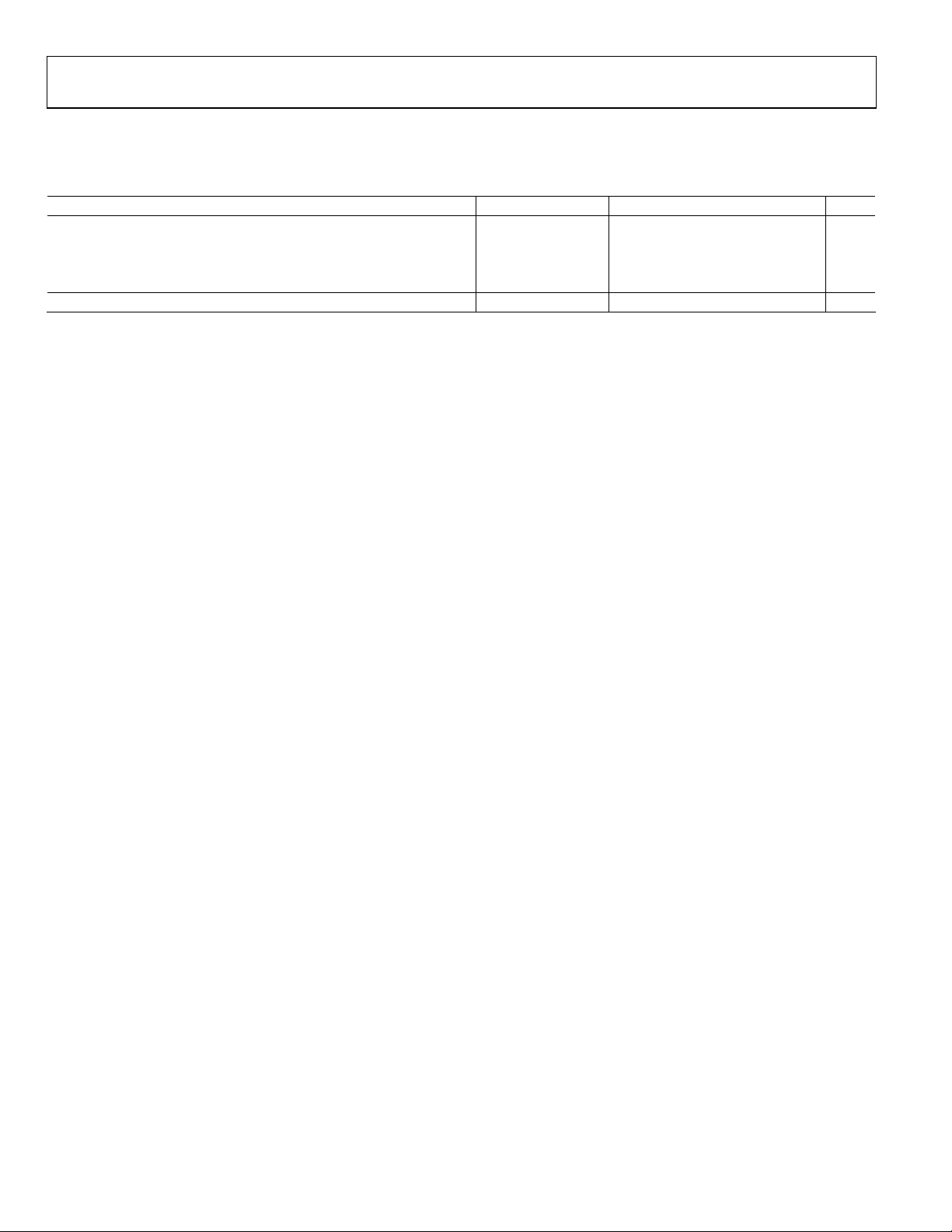

TYPICAL APPLICATION CIRCUIT

C1

C2

ON

ON

C3

1µF

AVIN

VIN1

EN1

VIN2

EN2

EN3

VIN3

C

AVIN

0.1µF

2.3V TO

5.5V

1.7V TO

5.5V

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

4.7µF

OFF

4.7µF

OFF

HOUSEKEEPING

EN1

EN2

EN3

(ANALOG)

ADP5024

AGND

BUCK1

MODE

MODE

BUCK2

LDO

VOUT1

SW1

FB1

PGND1

MODE

VOUT2

SW2

FB2

PGND2

VOUT3

FB3

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

L1 1µH

R1

R2

PWM

L2 1µH

R3

R4

R5

R6

C5

10µF

PSM/PWM

C6

10µF

C7

10µF

V

OUT1

1200mA

V

OUT2

1200mA

V

OUT3

300mA

AT

AT

AT

09888-001

ADP5024 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Typical Application Circuit ............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

General Specifications ................................................................. 3

BUCK1 and BUCK2 Specifications ........................................... 4

LDO Specifications ...................................................................... 5

Input and Output Capacitor, Recommended Specifications.. 6

Absolute Maximum Ratings............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics ............................................. 9

REVISION HISTORY

8/11—Revision 0: Initial Version

Theory of Operation ...................................................................... 16

Power Management Unit........................................................... 17

BUCK1 and BUCK2 .................................................................. 19

LDO.............................................................................................. 20

Applications Information.............................................................. 21

Buck External Component Selection....................................... 21

LDO External Component Selection ...................................... 23

Power Dissipation and Thermal Considerations....................... 24

Buck Regulator Power Dissipation .......................................... 24

Junction Temperature................................................................ 25

PCB Layout Guidelines.................................................................. 26

Typical Application Schematics.................................................... 27

Bill of Materials........................................................................... 27

Outline Dimensions....................................................................... 28

Ordering Guide .......................................................................... 28

Rev. 0 | Page 2 of 28

Data Sheet ADP5024

SPECIFICATIONS

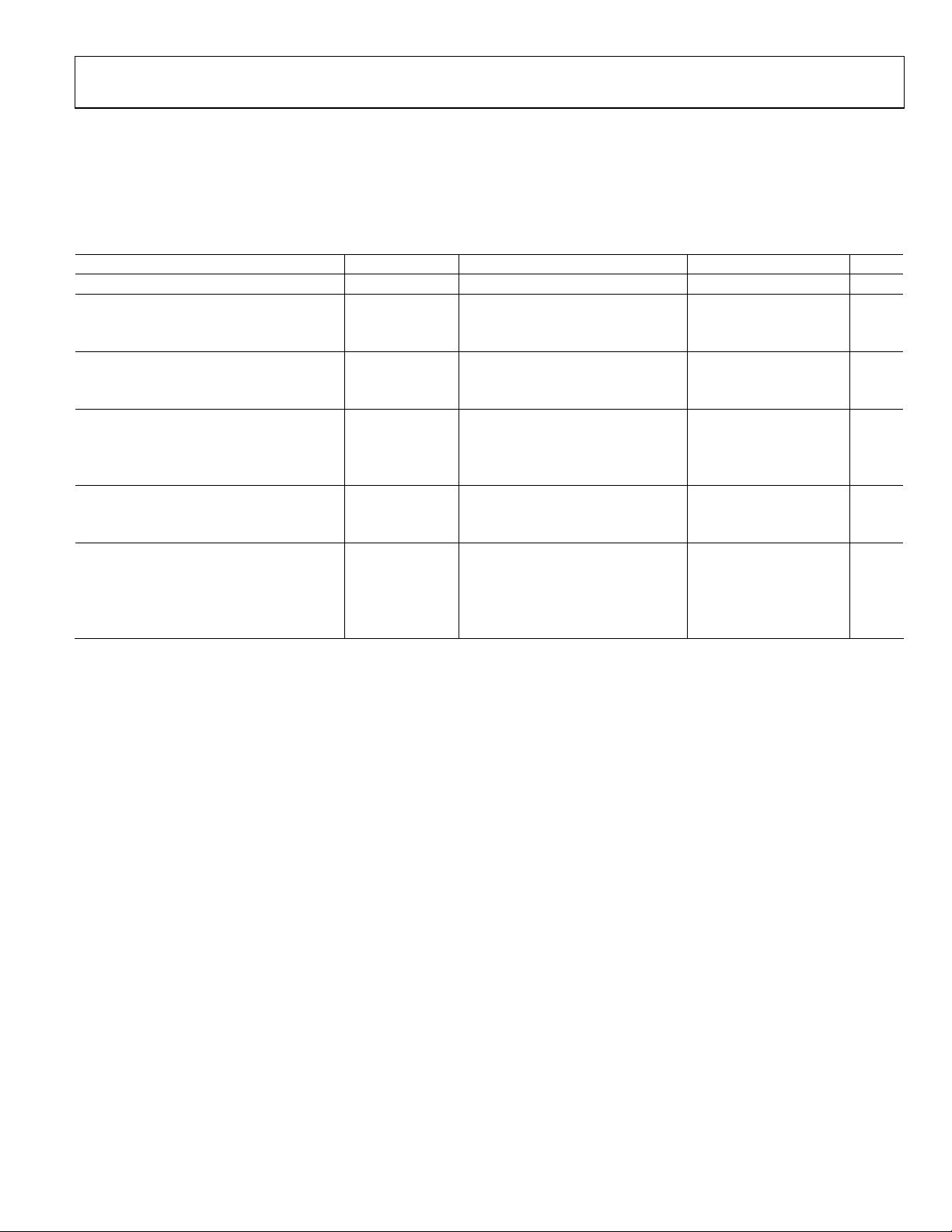

GENERAL SPECIFICATIONS

V

= V

= V

AVI N

IN1

= 2.3 V to 5.5 V; V

IN2

typical specifications, unless otherwise noted.

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT VOLTAGE RANGE V

THERMAL SHUTDOWN

Threshold TSSD T

Hysteresis TS

START-UP TIME1

BUCK1, LDO t

BUCK2 t

EN1, EN2, EN3, MODE INPUTS

Input Logic High VIH 1.1 V

Input Logic Low VIL 0.4 V

Input Leakage Current V

INPUT CURRENT

All Channels Enabled I

All Channels Disabled I

VIN1 UNDERVOLTAGE LOCKOUT

High UVLO Input Voltage Rising UVLO

High UVLO Input Voltage Falling UVLO

Low UVLO Input Voltage Rising UVLO

Low UVLO Input Voltage Falling UVLO

1

Start-up time is defined as the time from EN1 = EN2 = EN3 from 0 V to V

shorter for individual channels if another channel is already enabled. See the section for more information. Typical Performance Characteristics

= 1.7 V to 5.5 V; TJ = −40°C to +125°C for minimum/maximum specifications, and TA = 25°C for

IN3

, V

, V

AVIN

SD-HYS

START1

START2

I-LEAKAGE

STBY-NOSW

SHUTDOWN

2.3 5.5 V

IN1

IN2

rising 150 °C

J

20 °C

250 µs

300 µs

0.05 1 µA

No load, no buck switching 108 175 µA

T

3.9 V

VIN1RISE

3.1 V

VIN1FALL

2.275 V

VIN1RISE

1.95 V

VIN1FALL

= −40°C to +85°C 0.3 1 µA

J

to VOUT1, VOUT2, and VOUT3 reaching 90% of their nominal levels. Start-up times are

AVIN

Rev. 0 | Page 3 of 28

ADP5024 Data Sheet

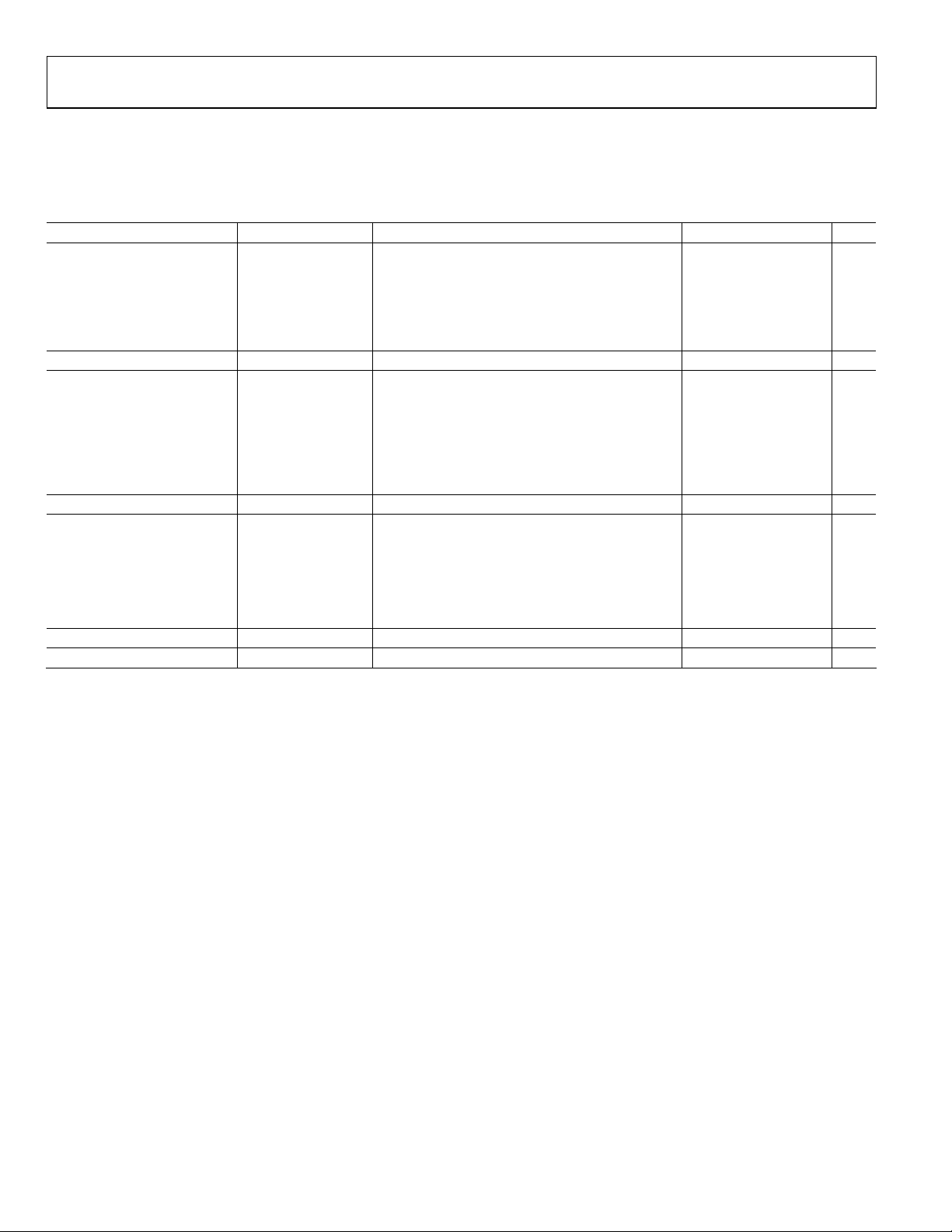

BUCK1 AND BUCK2 SPECIFICATIONS

V

= V

= V

AVI N

IN1

specifications, unless otherwise noted.

Table 2.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

OUTPUT CHARACTERISTICS

Output Voltage Accuracy V

Line Regulation

Load Regulation

VOLTAGE FEEDBACK V

OPERATING SUPPLY CURRENT MODE = ground

BUCK1 Only IIN

BUCK2 Only IIN

BUCK1 and BUCK2 IIN

PSM CURRENT THRESHOLD I

SW CHARACTERISTICS

SW On Resistance R

R

R

R

Current Limit I

ACTIVE PULL-DOWN R

OSCILLATOR FREQUENCY fSW 2.5 3.0 3.5 MHz

1

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

= 2.3 V to 5.5 V; TJ = −40°C to +125°C for minimum/maximum specifications, and TA = 25°C for typical

IN2

OUT1

(∆V

(∆V

(∆V

(∆V

FB1

1

, V

I

OUT2

)/∆V

OUT1/VOUT1

OUT2/VOUT2

OUT1/VOUT1

OUT2/VOUT2

, V

Models with adjustable outputs 0.485 0.5 0.515 V

FB2

)/∆V

)/∆I

)/∆I

IN1

IN2

OUT1

OUT2

,

,

= I

LOAD 1

= 0 mA to 1200 mA, PWM mode −3 +3 %

LOAD 2

PWM mode −0.05 %/V

I

= 0 mA to 1200 mA, PWM mode −0.1 %/A

LOAD

= 0 mA, device not switching, all other

I

LOAD 1

44 A

channels disabled

= 0 mA, device not switching, all other

I

LOAD 2

55 A

channels disabled

I

LOAD 1

= I

= 0 mA, device not switching, LDO

LOAD 2

67 A

channels disabled

PSM to PWM operation 100 mA

PSM

V

PFET

V

NFET

V

PFET

V

NFET

, I

LIMIT1

LIMIT2

Channel disabled 75 Ω

PDWN-B

= V

= 3.6 V 155 240 mΩ

IN1

IN2

= V

= 3.6 V 205 310 mΩ

IN1

IN2

= V

= 5.5 V 162 204 mΩ

IN1

IN2

= V

= 5.5 V 137 243 mΩ

IN1

IN2

PFET switch peak current limit 1600 1950 2300 mA

Rev. 0 | Page 4 of 28

Data Sheet ADP5024

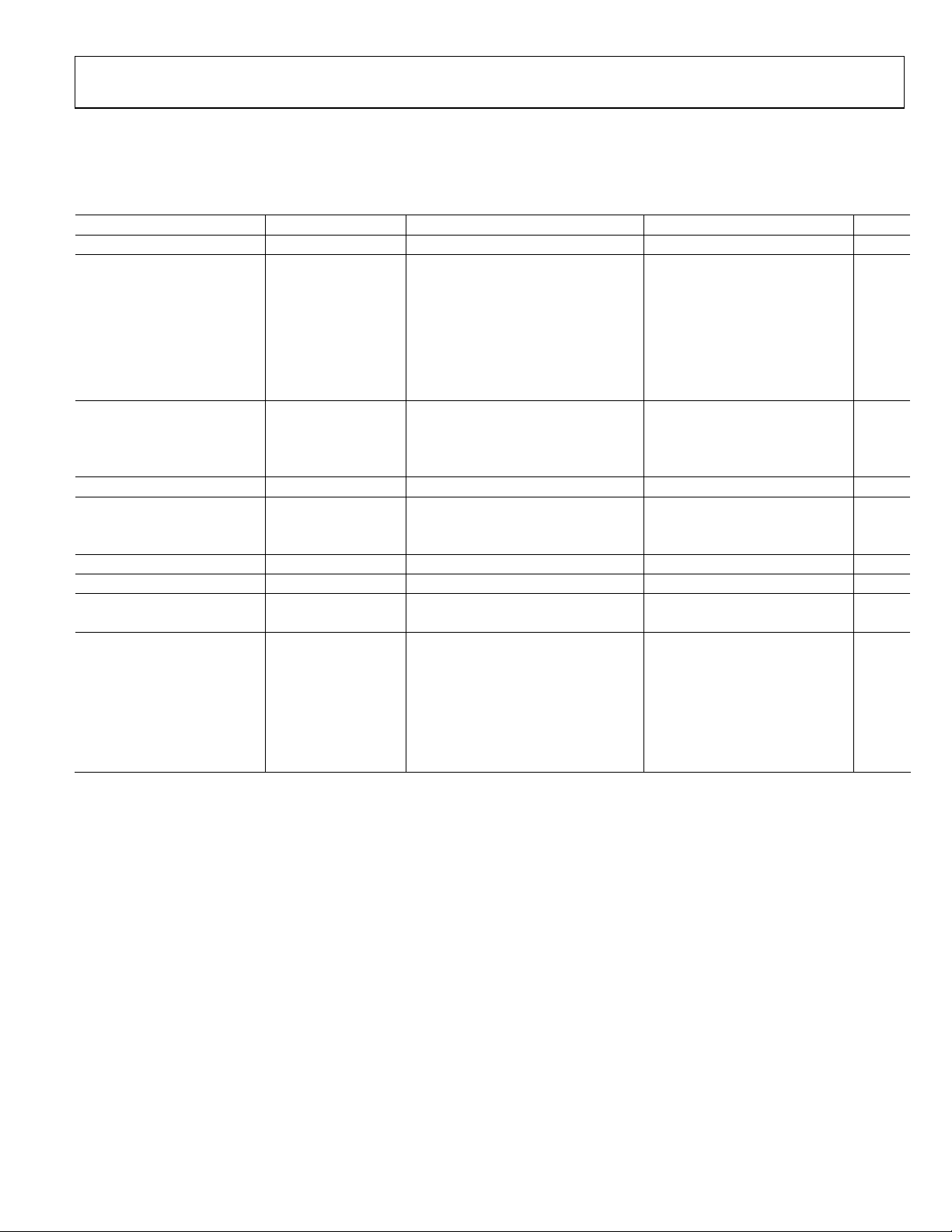

LDO SPECIFICATIONS

V

= (V

IN3

specifications, and T

Table 3.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT VOLTAGE RANGE V

OPERATING SUPPLY CURRENT

Bias Current per LDO2 I

I

I

Total System Input Current

LDO Only

OUTPUT CHARACTERISTICS

Output Voltage Accuracy

Line Regulation (∆V

Load Regulation3 (∆V

VOLTAGE FEEDBACK

DROPOUT VOLTAGE4 V

V

V

CURRENT-LIMIT THRESHOLD5 I

ACTIVE PULL-DOWN R

OUTPUT NOISE

Regulator LDO NOISE

POWER SUPPLY REJECTION

RATIO

Regulator LDO

1

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

2

This is the input current into VIN3, which is not delivered to the output load.

3

Based on an endpoint calculation using 1 mA and 300 mA loads.

4

Dropout voltage is defined as the input-to-output voltage differential when the input voltage is set to the nominal output voltage. This applies only to output voltages

above 1.7 V.

5

Current-limit threshold is defined as the current at which the output voltage drops to 90% of the specified typical value. For example, the current limit for a 3.0 V

output voltage is defined as the current that causes the output voltage to drop to 90% of 3.0 V or 2.7 V.

+ 0.5 V) or 1.7 V (whichever is greater) to 5.5 V; CIN = C

OUT3

= 25°C for typical specifications, unless otherwise noted.1

A

1.7 5.5 V

IN3

I

VIN3BIAS

IIN

OUT3

OUT3

OUT3

Includes all current into AVIN, VIN1,

VIN2, and VIN3

I

OUT3

disabled

100 µA < I

V

OUT3

)/∆V

)/∆I

I

IN3

I

OUT3

OUT3

OUT3

0.485 0.5 0.515 V

OUT3

OUT3

OUT3

OUT3/VOUT3

OUT3/VOUT3

V

FB3

V

DROPOUT

335 600 mA

LIMIT3

Channel disabled 600 Ω

PDWN-L

10 Hz to 100 kHz, V

LDO

PSRR

10 kHz, V

I

OUT3

100 kHz, V

I

OUT3

1 MHz, V

I

OUT3

= 1 µF; TJ = −40°C to +125°C for minimum/maximum

OUT

= 0 µA 10 30 µA

= 10 mA 60 100 µA

= 300 mA 165 245 µA

= 0 µA, all other channels

< 300 mA −3 +3 %

OUT3

53 µA

= 1 mA −0.03 +0.03 %/V

= 1 mA to 300 mA 0.001 0.003 %/mA

= 3.3 V, I

= 2.5 V, I

= 1.8 V, I

= 300 mA 75 140 mV

OUT3

= 300 mA 100 mV

OUT3

= 300 mA 180 mV

OUT3

= 3.3 V, V

IN3

= 5 V, V

IN3

OUT3

= 2.8 V 100 µV rms

OUT3

= 2.8 V,

60 dB

= 1 mA

= 3.3 V, V

IN3

OUT3

= 2.8 V,

62 dB

= 1 mA

= 3.3 V, V

IN3

OUT3

= 2.8 V,

63 dB

= 1 mA

Rev. 0 | Page 5 of 28

ADP5024 Data Sheet

INPUT AND OUTPUT CAPACITOR, RECOMMENDED SPECIFICATIONS

TA = −40°C to +125°C, unless otherwise specified.

Table 4.

Parameter Symbol Min Typ Max Unit

SUGGESTED INPUT AND OUTPUT CAPACITANCE

BUCK1, BUCK2 Input Capacitor C

BUCK1, BUCK2 Output Capacitor C

LDO1 Input and Output Capacitor C

CAPACITOR ESR R

1

The minimum input and output capacitance should be greater than 0.70 µF over the full range of operating conditions. The full range of operating conditions in the

application must be considered during device selection to ensure that the minimum capacitance specification is met. X7R- and X5R-type capacitors are

recommended; Y5V and Z5U capacitors are not recommended for use because of their poor temperature and dc bias characteristics.

, C

MIN1

MIN1

MIN3

ESR

4.7 40 µF

MIN2

, C

10 40 µF

MIN2

, C

0.70 µF

MIN4

0.001 1 Ω

Rev. 0 | Page 6 of 28

Data Sheet ADP5024

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

AVIN to AGND −0.3 V to +6 V

VIN1, VIN2 to AVIN −0.3 V to +0.3 V

PGND1, PGND2 to AGND −0.3 V to +0.3 V

VIN3, VOUT1, VOUT2, FB1, FB2, FB3,

EN1, EN2, EN3, MODE to AGND

VOUT3 to AGND −0.3 V to (VIN3 + 0.3 V)

SW1 to PGND1 −0.3 V to (VIN1 + 0.3 V)

SW2 to PGND2 −0.3 V to (VIN2 + 0.3 V)

Storage Temperature Range −65°C to +150°C

Operating Junction Temperature

Range

Soldering Conditions JEDEC J-STD-020

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

For detailed information on power dissipation, see the Power

Dissipation and Thermal Considerations section.

−0.3 V to (AVIN + 0.3 V)

−40°C to +125°C

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 6. Thermal Resistance

Package Type θJA θJC Unit

24-Lead, 0.5 mm pitch LFCSP 35 3 °C/W

ESD CAUTION

Rev. 0 | Page 7 of 28

ADP5024 Data Sheet

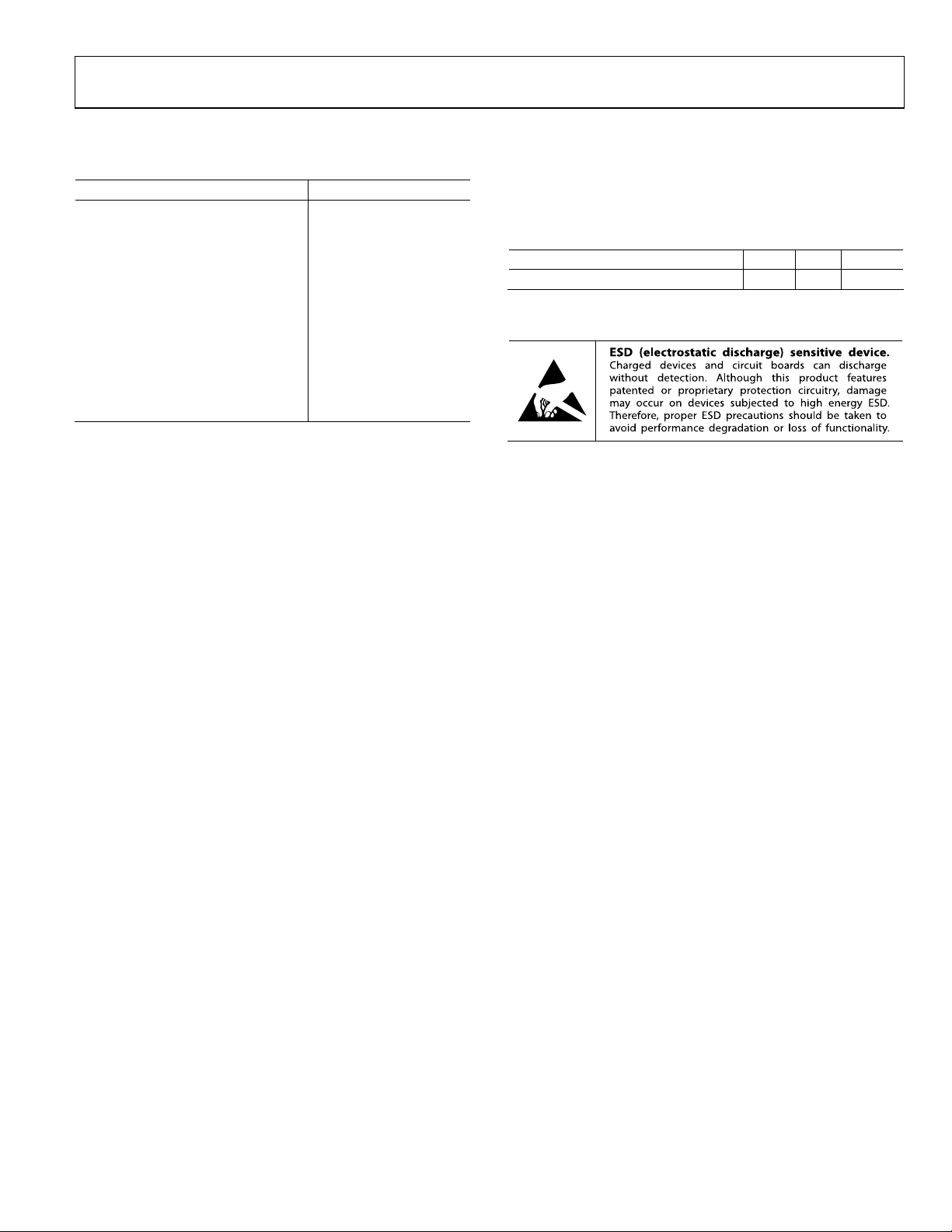

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

AGND

AGND

EN3

VIN3

VOUT3

24

23

1

AGND

2

AGND

3

VIN2

SW

PGND2

NC

NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PI N.

2. IT IS RECOMMENDED THAT THE EXPO SED PAD

BE SOLDERED TO THE G ROUND PLANE.

ADP5024

2

TOP VIEW

4

5

6

8

7

FB2

EN2

Figure 2. Pin Configuration—View from Top of the Die

Table 7. Pin Function Descriptions

Pin No. Mnemonic Description

1 AGND Analog Ground.

2 AGND Analog Ground.

3 VIN2 BUCK2 Input Supply (2.3 V to 5.5 V). Connect VIN2 to VIN1 and AVIN.

4 SW2 BUCK2 Switching Node.

5 PGND2 Dedicated Power Ground for BUCK2.

6 NC No Connect. Leave this pin unconnected.

7 EN2 BUCK2 Enable Pin. High level turns on this regulator, and low level turns it off.

8 FB2

BUCK2 Feedback Input. For device models with an adjustable output voltage, connect this pin to the middle of the

BUCK2 resistor divider. For device models with a fixed output voltage, leave this pin unconnected.

9 VOUT2 BUCK2 Output Voltage Sensing Input. Connect VOUT2 to the top of the capacitor on VOUT2.

10 VOUT1 BUCK1 Output Voltage Sensing Input. Connect VOUT1 to the top of the capacitor on VOUT1.

11 FB1

BUCK1 Feedback Input. For device models with an adjustable output voltage, connect this pin to the middle of the

BUCK1 resistor divider. For device models with a fixed output voltage, leave this pin unconnected.

12 EN1 BUCK1 Enable Pin. High level turns on this regulator, and low level turns it off.

13 MODE

BUCK1/BUCK2 Operating Mode. MODE = high for forced PWM operation. MODE = low for automatic PWM/PSM

operation.

14 PGND1 Dedicated Power Ground for BUCK1.

15 SW1 BUCK1 Switching Node.

16 VIN1 BUCK1 Input Supply (2.3 V to 5.5 V). Connect VIN1 to VIN2 and AVIN.

17 AVIN Analog Input Supply (2.3 V to 5.5 V). Connect AVIN to VIN1 and VIN2.

18 AGND Analog Ground.

19 FB3

LDO Feedback Input. For device models with an adjustable output voltage, connect this pin to the middle of the

LDO resistor divider. For device models with a fixed output voltage, leave this pin unconnected.

20 VOUT3 LDO Output Voltage.

21 VIN3 LDO Input Supply (1.7 V to 5.5 V).

22 EN3 LDO Enable Pin. High level turns on this regulator, and low level turns it off.

23 AGND Analog Ground.

24 AGND Analog Ground.

EPAD (EP) Exposed Pad. It is recommended that the exposed pad be soldered to the ground plane.

FB3

22

21

20

19

18

AGND

17

AVIN

16

VIN1

15

SW

1

14

PGND1

MODE

13

9

11

10

12

FB1

EN1

VOUT2

VOUT1

09888-002

Rev. 0 | Page 8 of 28

Data Sheet ADP5024

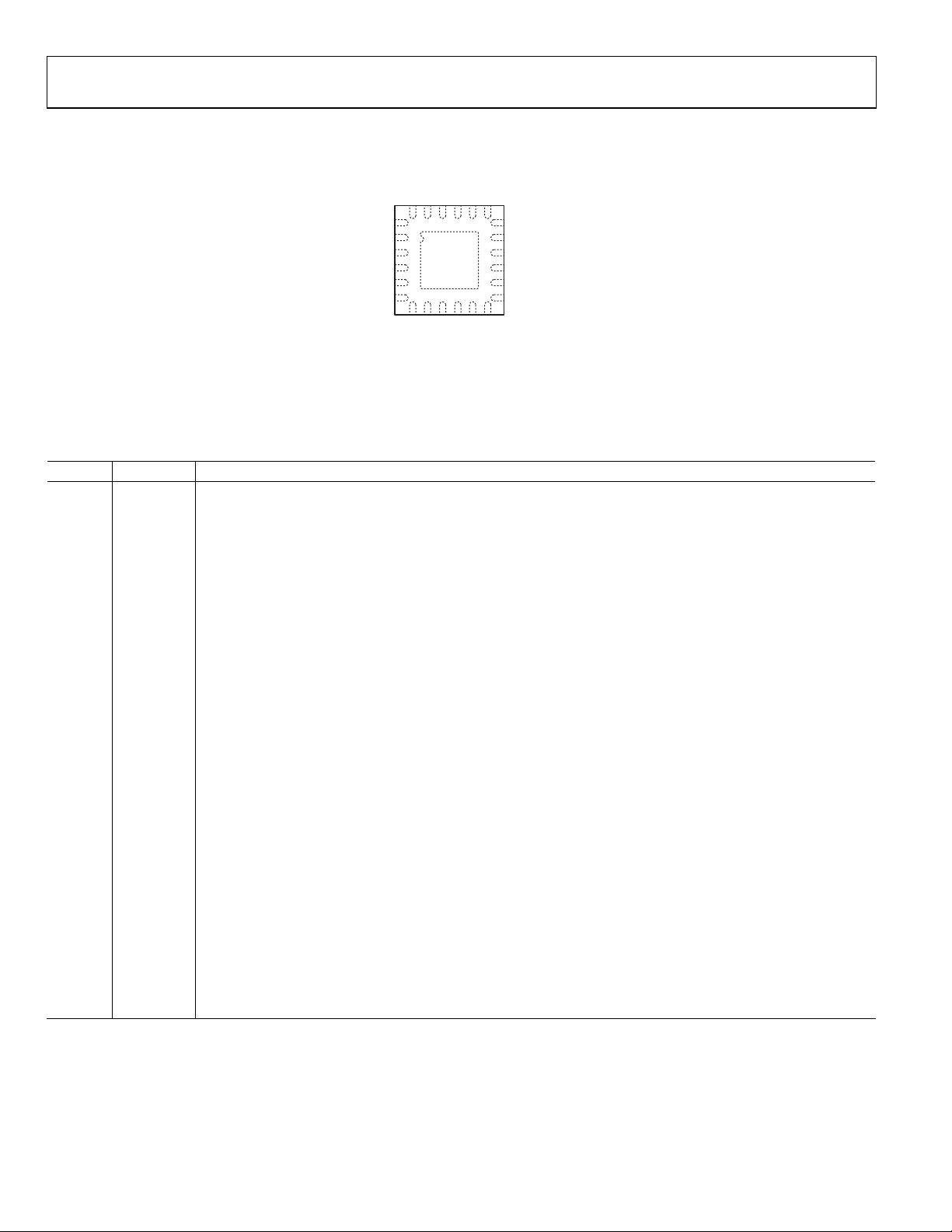

TYPICAL PERFORMANCE CHARACTERISTICS

V

= V

= V

IN1

IN2

140

= 3.6 V, TA = 25°C, unless otherwise noted.

IN3

3.35

120

100

80

60

40

QUIESCENT CURRENT (µA)

20

0

2.3 2.8 3.3 3.8 4.3 4.8 5.3

INPUT VOLTAGE (V)

Figure 3. System Quiescent Current vs. Input Voltage, V

= 1.8 V, V

V

OUT2

T

4

2

1

3

SW

IOUT

VOUT

EN

= 1.2 V, All Channels Unloaded

OUT3

OUT1

= 3.3 V,

3.33

VIN = 3.6V, +25° C

3.31

(V)

OUT

V

3.29

3.27

3.25

09888-003

0 0.2 0.4 0.6 0.8 1.0 1.2

Figure 6. BUCK1 Load Regulation Across Temperature, V

VIN = 3.6V, +85° C

V

= 3.6V, –40° C

IN

I

OUT

(A)

OUT1

= 3.3 V,

09888-006

Automatic Mode

1.864

(V)

OUT

V

1.844

1.824

1.804

1.784

VIN = 3.6V, + 25°C

VIN = 3.6V, +85°C

V

= 3.6V, –40 °C

IN

CH1 2.00V

CH3 5.00V

B

W

B

W

Figure 4. BUCK1 Startup, V

T

4

2

1

3

CH1 2.00V

CH3 5.00V

SW

IOUT

VOUT

EN

B

B

W

W

CH2 50.0mA

CH4 5.00V

Figure 5. BUCK2 Startup, V

CH2 50.0mA

CH4 5.00V

B

M 40.0µs A CH3 2. 2V

W

B

W

T 11.20%

OUT1

= 1.8 V, I

OUT1

= 5 mA

B

M 40.0µs A CH3 2.2V

W

B

W

T 11.20%

OUT2

= 3.3 V, I

= 10 mA

OUT2

09888-004

09888-005

Rev. 0 | Page 9 of 28

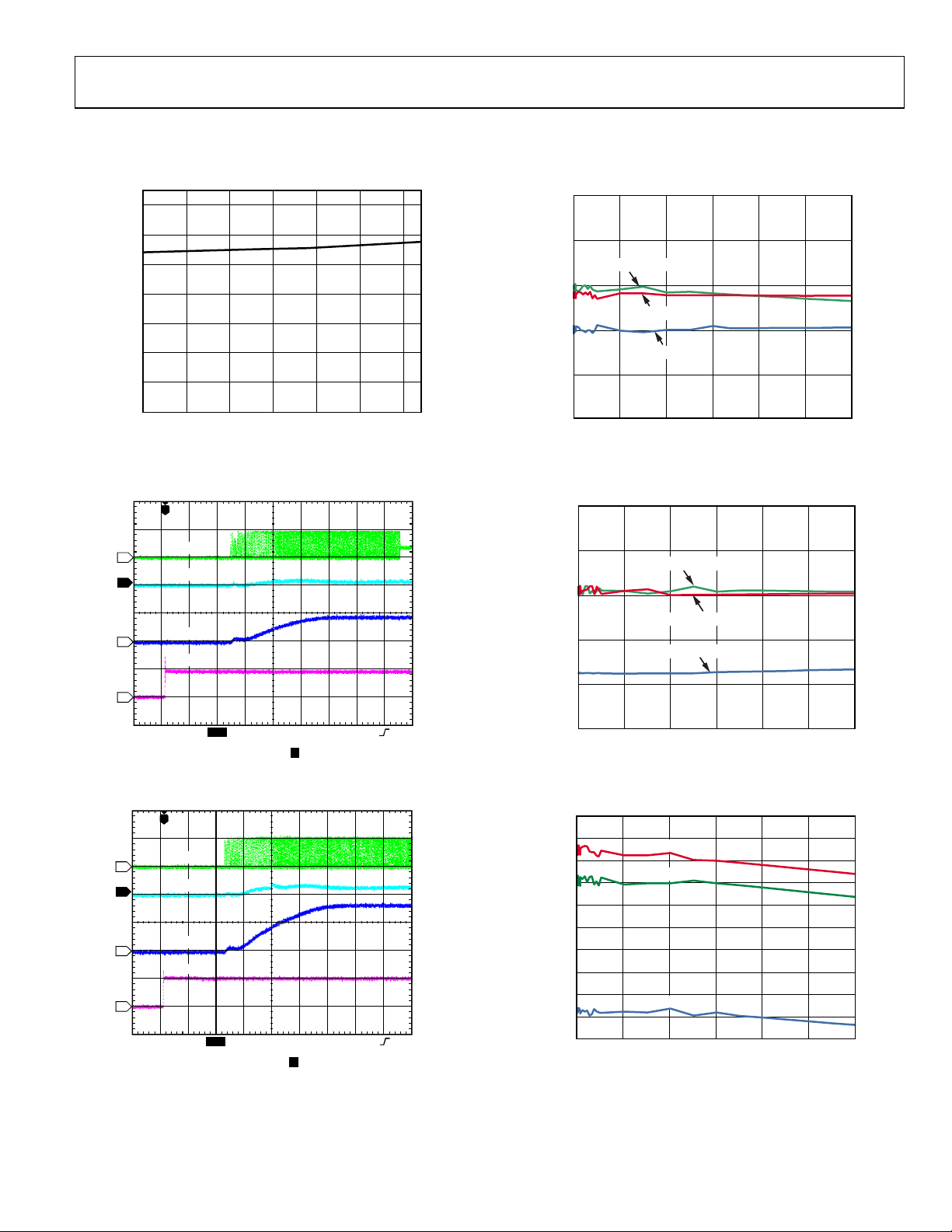

1.764

0 0.20.40.60.81.01.2

I

(A)

OUT

Figure 7. BUCK2 Load Regulation Across Temperature, V

Automatic Mode

0.799

0.798

0.797

0.796

0.795

(V)

0.794

OUT

V

0.793

0.792

0.791

0.790

0.789

0 0.2 0.4 0.6 0.8 1.0 1.2

VIN = 3.6V, + 85°C

VIN = 3.6V, + 25°C

V

= 3.6V, –40° C

IN

I

OUT

(A)

Figure 8. BUCK1 Load Regulation Across Input Voltage, V

PWM Mode

OUT2

OUT1

= 1.8 V,

= 0.8 V,

09888-007

09888-008

Loading...

Loading...