Analog Devices ADP3510ARU Datasheet

a

CDMA Power Management System

ADP3510

FEATURES

Handles All CDMA Baseband Power Management

Six LDOs Optimized for Specific CDMA Subsystems

Li-Ion and NiMH Battery Charge Function

Ambient Temperature: 20C to +85C

TSSOP 28-Lead Package

Optimized for LSI Logic Baseband Chipset

APPLICATIONS

CDMA Handsets

GENERAL DESCRIPTION

The ADP3510 is a multifunction power system chip optimized for

CDMA handset power management. It contains six specialized

LDOs, one to power each of the critical CDMA subblocks.

Sophisticated controls are available for power-up during battery

charging, keypad interface, and RTC alarm. If a Li-Ion battery

is being charged, the charge circuit maintains low current

charging during the initial charge phase and provides an end of

charge (EOC) signal when the cell has been fully charged.

The ADP3510 is specified over the temperature range of –20∞C to

+85∞C and is available in a narrow body TSSOP 28-Lead package.

PWRONKEY

ROWX

PWRONIN

ALARM

PDCAP

TCXOEN

RESCAP

CHRDET

EOC

CHGEN

GATEIN

BATSNS

ISENSE

GATEDR

CHRIN

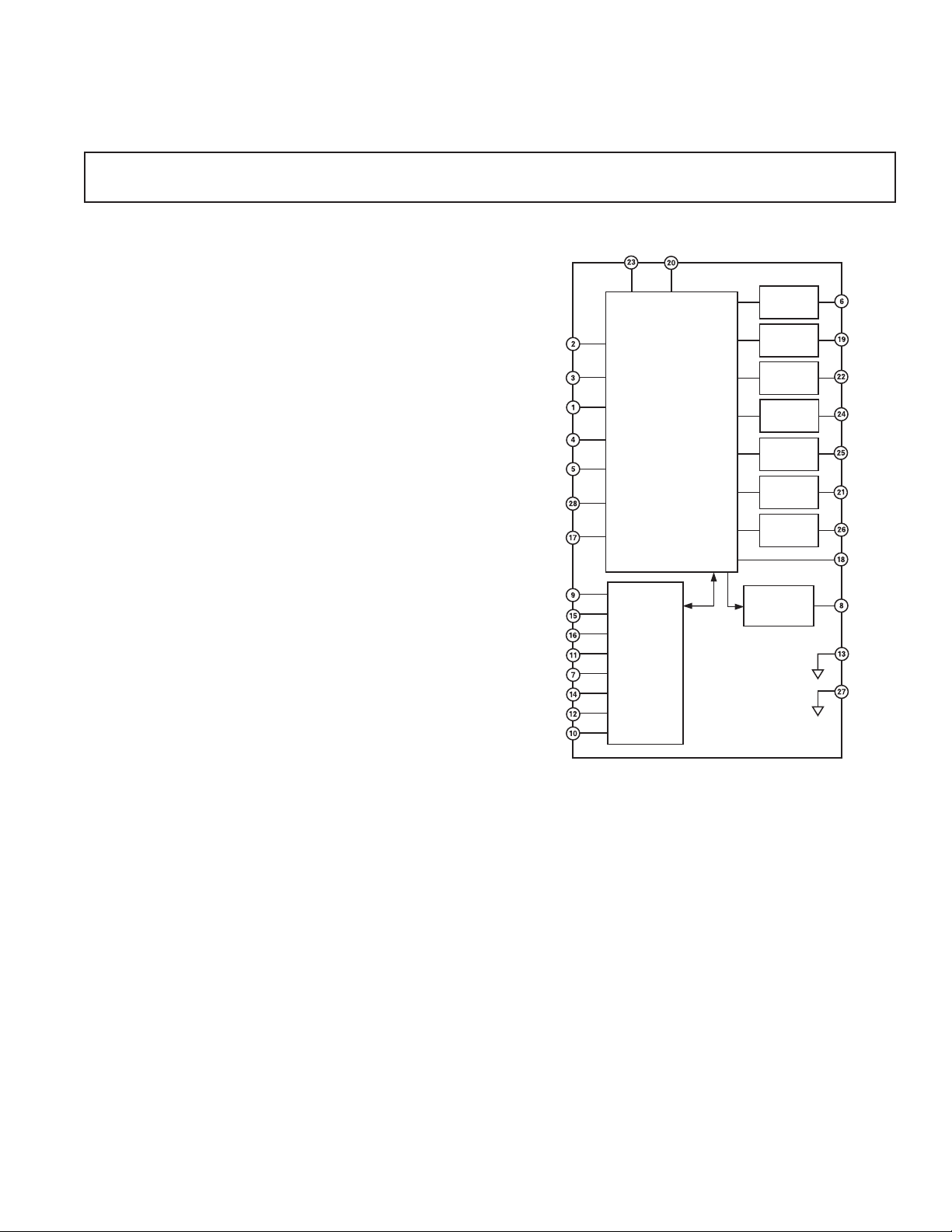

FUNCTIONAL BLOCK DIAGRAM

VBAT VBAT2

RTC

VIO

LDO

DIGITAL

CORE LDO

POWER-UP

SEQUENCING

AND

PROTECTION

LOGIC

BATTERY

CHARGE

CONTROLLER

ADP3510

ANALOG

LDO

TCXO

LDO

MEMORY

LDO

REF

BUFFER

BATTERY

VOLTA G E

DIVIDER

VTRC

VIO

VCORE

VA N

VTCXO

VMEM

REFOUT

RESET

MVBAT

DGND

AGN D

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

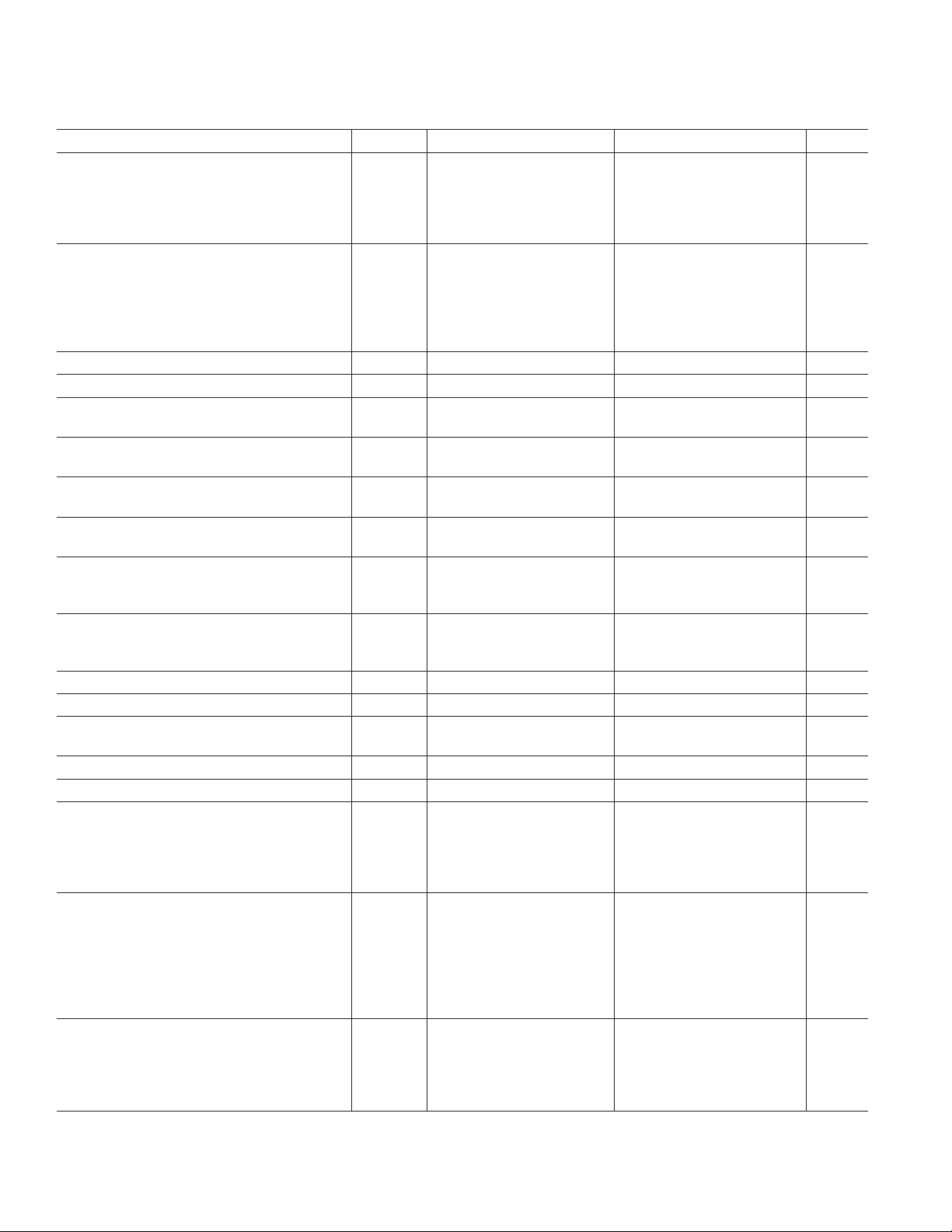

ADP3510–SPECIFICATIONS

(–20C ⱕ TA ⱕ +85C, VBAT = VBAT2 = 3.2 V–7.5 V, CVIO = CVCORE = CVAN = CVMEM = 2.2 F,

1

ELECTRICAL CHARACTERISTICS

P

arameter Symbol Conditions Min Typ Max Unit

SHUTDOWN SUPPLY CURRENT ICC

VBAT £ 2.5 V VBAT = VBAT2 = 2.3 V 5 15 mA

(Deep Discharged Lockout Active)

2.5 V < VBAT £ 3.2 V (UVLO Active) VBAT = VBAT2 = 3.15 V 30 55 mA

VBAT >3.2 V VBAT = VBAT2 = 4.0 V 45 60 mA

OPERATING GROUND CURRENT IGND

All LDOs On Except TCXO Minimum Loads 300 390 mA

All LDOs On Minimum Loads 340 430 mA

All LDOs On Maximum Loads 2.0 3.5 % of

UVLO ON THRESHOLD VBAT 3.1 3.2 3.3 V

UVLO HYSTERESIS VBAT 200 mV

DEEP DISCHARGED LOCKOUT VBAT 2.0 2.4 2.75 V

ON THRESHOLD

DEEP DISCHARGED LOCKOUT VBAT 100 mV

HYSTERESIS

INPUT HIGH VOLTAGE (PWRONIN, V

TCXOEN, CHGEN, GATEIN)

INPUT LOW VOLTAGE (PWRONIN, V

TCXOEN, CHGEN, GATEIN)

INPUT HIGH BIAS CURRENT I

(PWRONIN, TCXOEN,

CHGEN, GATEIN)

INPUT LOW BIAS CURRENT I

(PWRONIN, TCXOEN,

CHGEN, GATEIN)

PWRONKEY INPUT HIGH VOLTAGE

PWRONKEY INPUT LOW VOLTAGE

PWRONKEY INPUT PULLUP

RESISTANCE TO VBAT 70 105 145 kW

THERMAL SHUTDOWN THRESHOLD

THERMAL SHUTDOWN HYSTERESIS 25 ºC

ROWX CHARACTERISTICS

ROWX Output Low Voltage V

ROWX Output High Leakage Current I

I/O LDO (VIO)

Output Voltage VIO Line, Load, Temp 2.85 2.935 3.02 V

Line Regulation DVIO Minimum Load 1 mV

Load Regulation DVIO 50 mA £ I

Output Capacitor Required for Stability

Dropout Voltage V

DIGITAL CORE LDO (VCORE)

Output Voltage VCORE Line, Load, Temp 1.78 1.85 1.92 V

Line Regulation DVCORE Minimum Load 1 mV

Load Regulation DVCORE 50 mA £ I

Output Capacitor Required for Stability C

VTCXO = 0.47 F, CVBAT = 10 F, min. loads applied on all outputs, unless otherwise noted.)

Max Load

Current

IH

IL

IH

IL

V

IH

V

IL

2

OL

L

PWRONKEY = Low 0.4 V

I

= 200 mA

OL

PWRONKEY = High 1 mA

2.0 V

0.4 V

1.0 mA

–1.0 mA

0.7 VBAT V

0.3 VBAT V

150 ºC

V(ROWX) = 5 V

£ 25 mA 3 mV

C

O

DO

O

VO = V

I

LOAD

LOAD

2.2 mF

– 100 mV

INITIAL

= 25 mA 50 150 mV

£ 120 mA 8 mV

LOAD

2.2 mF

–2–

REV. 0

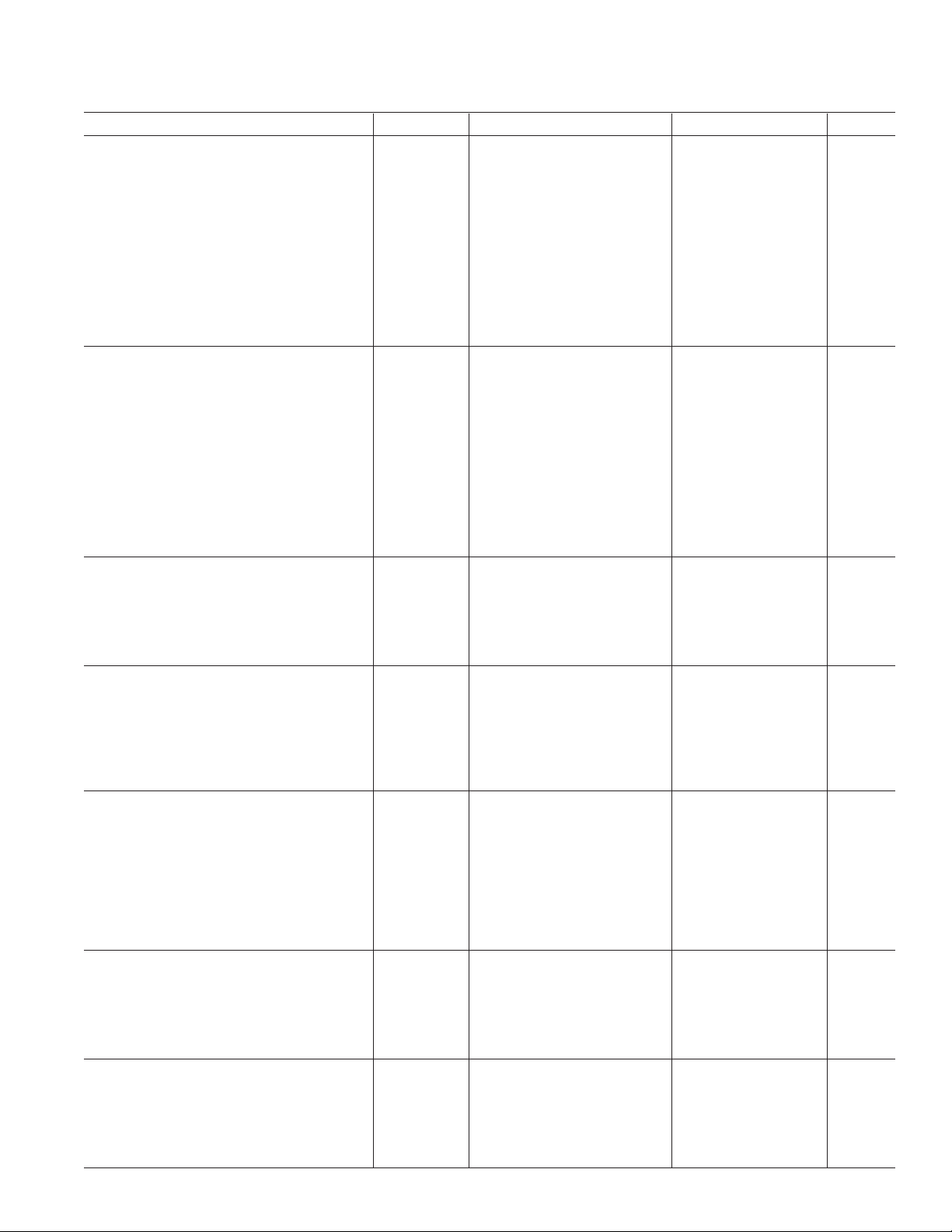

ADP3510

Parameter Symbol Conditions Min Typ Max Unit

ANALOG LDO (VAN)

Output Voltage VAN Line, Load, Temp 2.85

Line Regulation DVAN Minimum Load 1 mV

Load Regulation DVAN 50 mA £ I

Output Capacitor Required for Stability C

Dropout Voltage V

O

DO

VO = V

I

= 75 mA 100 175 mV

LOAD

£ 75 mA 6 mV

LOAD

2.2 mF

100 mV

INITIAL

Ripple Rejection DVBAT/ f = 217 Hz (T = 4.6 ms) 75 dB

DVAN VBAT = 3.6 V

Output Noise Voltage V

NOISE

f = 10 Hz to 100 kHz 80 mV rms

I

= 75 mA

LOAD

VBAT = 3.6 V

TCXO LDO (VTCXO)

Output Voltage VTCXO Line, Load, Temp 2.71 2.765 2.82 V

Line Regulation DVTCXO Minimum Load 1 mV

Load Regulation DVTCXO 50 mA £ I

Output Capacitor Required for Stability C

Dropout Voltage V

O

DO

VO = V

I

LOAD

= 10 mA

£ 10 mA 3 mV

LOAD

0.47 mF

– 100 mV 175 mV

INITIAL

Ripple Rejection DVBAT/ f = 217 Hz (T = 4.6 ms) 75 dB

DVTCXO VBAT = 3.6 V

Output Noise Voltage V

NOISE

f = 10 Hz to 100 kHz 80 mV rms

I

= 10 mA

LOAD

VBAT = 3.6 V

REAL-TIME CLOCK LDO/

BATTERY CHARGER (VRTC)

Maximum Output Voltage VRTC 1 mA £ I

Off Reverse Input Current I

Dropout Voltage V

L

DO

2.0 V < VBAT < UVLO 1 mA

VO = V

I

LOAD

£ 6 mA2.772.85 2.93 V

LOAD

– 100 mV 175 mV

INITIAL

= 10 mA

MEMORY LDO (VMEM)

Output Voltage VMEM Line, Load, Temp 2.85 2.935 3.02 V

Line Regulation DVMEM Minimum Load 1 mV

Load Regulation DVMEM 50 mA £ I

Output Capacitor Required for Stability C

Dropout Voltage V

O

DO

VO = V

I

LOAD

= 60 mA

£ 60 mA 5 mV

LOAD

– 100 mV 100 175 mV

INITIAL

REFOUT

Output Voltage VREFOUT Line, Load, Temp 1.19 1.210 1.23 V

Line Regulation DVREFOUT Minimum Load 0.3 mV

Load Regulation DVREFOUT 0 mA £ I

£ 50 mA 0.6 mV

LOAD

VBAT = 3.6 V

Ripple Rejection DVBAT/ f = 217 Hz (T = 4.6 ms) 75 dB

DVREFOUT VBAT = 3.6 V

Maximum Capacitive Load C

Output Noise Voltage V

O

NOISE

f = 10 Hz to 100 kHz 40 mV rms

RESET GENERATOR (RESET)

Output High Voltage V

Output Low Voltage V

Output Current I

Delay Time per Unit Capacitance T

OH

OL

OL/IOH

D

IOH = +500 mA 2.4 V

IOL = –500 mA0.25V

0.8 1.5 4.0 ms/nF

Applied to RESCAP Pin

SEQUENCING

Delay Time per Unit Capacitance T

D

0.3 0.8 3.0 ms/nF

Applied to PDCAP Pin

V

PDCAP Charging Current I

OH

= 0 2.5 5 8 mA

PDCAP

VAN Discharge Resistance 200 W

VIO Discharge Resistance 200 W

2.935

3.02 V

2.2 mF

100 pF

1mA

REV. 0

–3–

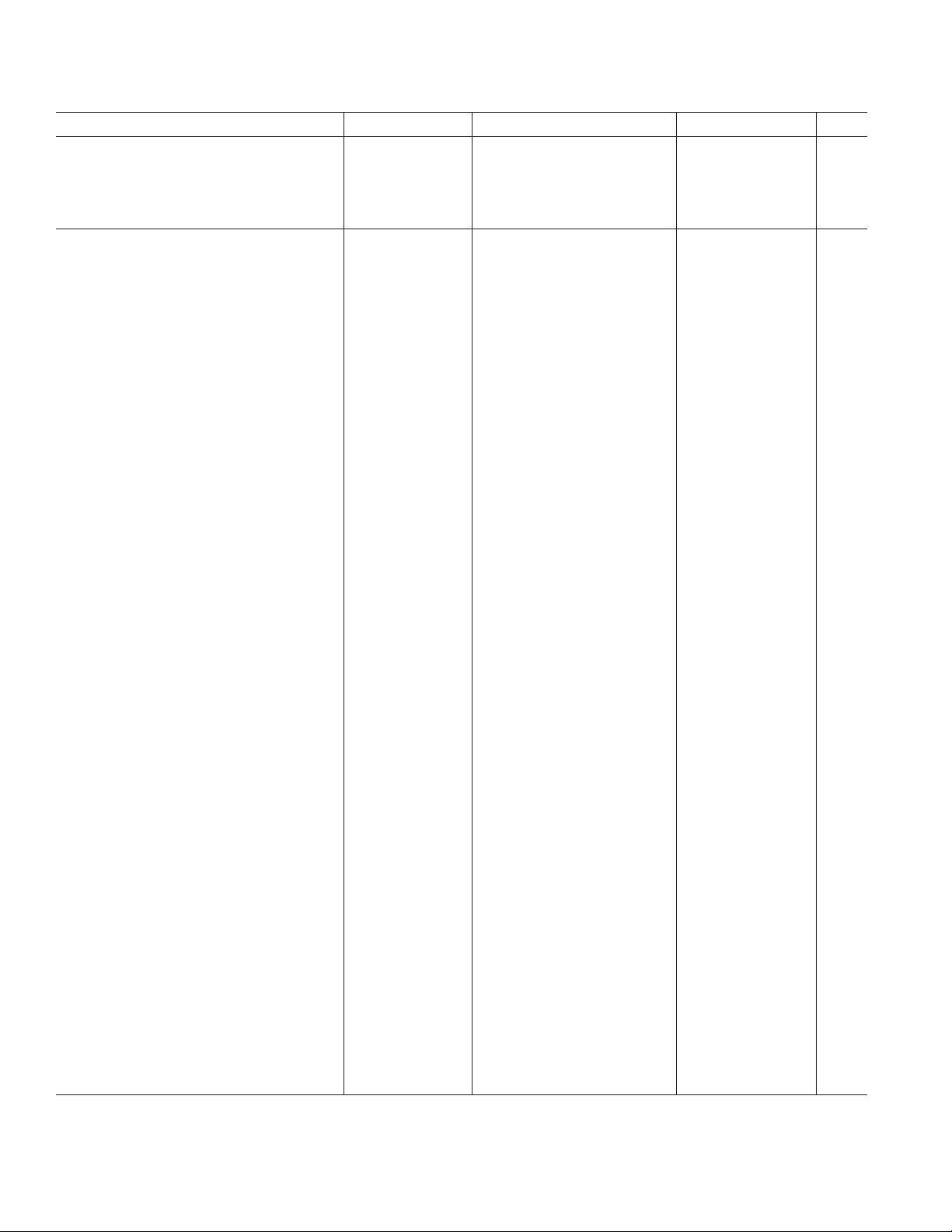

ADP3510

Parameter Symbol Conditions Min Typ Max Unit

BATTERY VOLTAGE DIVIDER

Divider Ratio BATSNS/MVBAT TCXOEN = High 2.94 3.00 3.06

Divider Impedance at MVBAT Z

O

Divider Leakage Current TCXOEN = Low 1 mA

Divider Resistance TCXOEN = High 230 350 430 kW

BATTERY CHARGER

Charger Output Voltage BATSNS 4.5 V < CHRIN < 10 V, 4.158 4.200 4.242 V

CHGEN = Low,

= 0∞C to 50∞C

T

Charger Output Voltage BATSNS

A

CHRIN = 10 V, V

= 0∞C to 50∞C

T

A

SENSE

= 10 mV,

Load Regulation ⌬BATSNS CHRIN = 5 V, 2 8 mV

0<CHRIN – ISENSE

< Current Limit Threshold,

CHGEN = Low

CHRDET on Threshold CHRIN–VBAT VBAT = 3.6 V 260 mV

CHRDET Hysteresis 70 mV

CHRDET Off Delay

3

CHRIN < VBAT 6 ms/nF

CHRIN Supply Current CHRIN = 5 V 0.6 1 mA

Current Limit Threshold CHRIN–ISENSE

High Current Limit CHRIN = 5 V dc 150 172 195 mV

(100%: UVLO Not Active) VBAT = 3.6 V

CHGEN = Low

Low Current Limit CHRIN = 5 V 2 15 30 mV

(10%: UVLO Active) VBAT = 2 V

CHGEN = Low

ISENSE Bias Current CHRIN = 5 V 180 250 mA

End of Charge Signal Threshold CHRIN–ISENSE CHRIN = 5 V dc 2 12 26 mV

VBAT > 4.0 V

CHGEN = Low

End of Charge Reset Threshold VBAT CHGEN = Low 3.82 3.96 4.10 V

GATEDR Transition Time t

, t

R

F

CHRIN = 5 V 1 10 ms

VBAT > 3.6 V

GATEDR High Voltage V

OH

CHGEN = High, C

CHRIN = 5 V 4.5 V

=2nF

L

VBAT = 3.6 V

CHGEN = High

GATEIN = High

I

= –1 mA

OH

GATEDR Low Voltage V

OL

CHRIN = 5 V 0.5 V

VBAT = 3.6 V

CHGEN = High

GATEIN = Low

I

= +1 mA

Output High Voltage V

OH

OL

IOH= –250 mA 2.4 V

(EOC, CHRDET)

Output Low Voltage V

OL

IOL = +250 mA 0.25 V

(EOC, CHRDET)

Battery Overvoltage BATSNS CHRIN = 7.5 V 5.30 5.50 5.70 V

Protection Threshold CHGEN = High

(GATEDRÆHigh) GATEIN = Low

Battery Overvoltage BATSNS CHRIN = 7.5 V 400 mV

Protection Hysteresis CHGEN = High

GATEIN = Low

NOTES

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

This feature is intended to protect against catastrophic failure of the device. Maximum allowed operating junction temperature is 125C. Operation beyond 125C could cause

permanent damage to the device.

3

Delay set by external capacitor on the RESCAP pin.

Specifications subject to change without notice.

–4–

50 80 110 kW

4.162 4.200 4.238 V

REV. 0

ADP3510

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Voltage on any pin with respect to

any GND Pin . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +10 V

Voltage on any pin may not exceed VBAT, with the following

exceptions: CHRIN, GATEDR, ISENSE

Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C

Operating Ambient Temperature Range . . . . –20∞C to +85∞C

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 125∞C

, Thermal Impedance (TSSOP-28)

q

JA

2-Layer PCB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98∞C/W

4-Layer PCB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68∞C/W

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300∞C

*This is a stress rating only; operation beyond these limits can cause the device to

be permanently damaged.

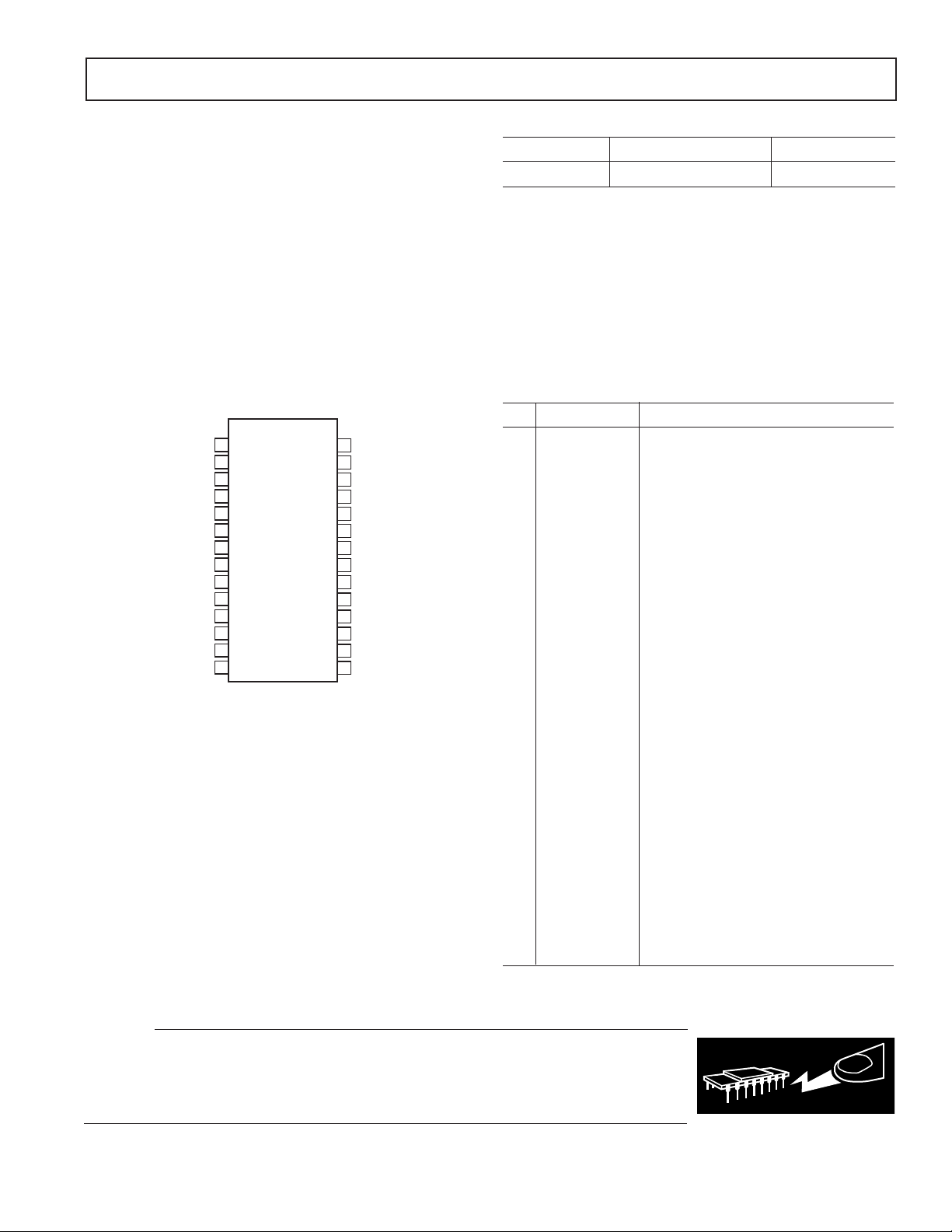

PIN CONFIGURATION

∑

PWRONIN

PWRONKEY

ROWX

ALARM

PDCAP

VRTC

BATSNS

MVBAT

CHRDET

CHRIN

GATEIN

GATEDR

DGND

ISENSE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

ADP3510

TOP VIEW

(Not to Scale)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

TCXOEN

AGND

REFOUT

VTCXO

VAN

VBAT

VCORE

VMEM

VBAT2

VIO

RESET

RESCAP

CHGEN

EOC

ORDERING GUIDE

Model Temperature Range Package Option

ADP3510ARU –20∞C to 85∞C RU-28

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1PWRONIN Power-On/-Off Signal from

Microprocessor

2 PWRONKEY Power-On/-Off Key

3 ROWX Power Key Interface Output

4 ALARM Alternative Power-On

5 PDCAP Power-On Delay Timer Capacitor

6 VRTC VRTC LDO Output

7 BATSNS Battery Voltage Sense Input

8 MVBAT Divided Battery Voltage Output

9CHRDET Charge Detect Output

10 CHRIN Charger Input Voltage

11 GATEIN Microprocessor Gate Input Signal

12 GATEDR Gate Drive Output

13 DGND Digital Ground

14 ISENSE Charge Current Sense Input

15 EOC End of Charge Signal

16 CHGEN Charger Enable for GATEIN, NiMH

Pulse Charging

17 RESCAP Reset Delay Time

18 RESET Main Reset

19 VIO I/O LDO Output

20 VBAT2 Battery Input Voltage 2

21 VMEM Memory LDO Output

22 VCORE Digital Core LDO Output

23 VBAT Battery Input Voltage

24 VAN Analog LDO Output

25 VTCXO TCXO LDO Output

26 REFOUT Output Reference

27 AGND Analog Ground

28 TCXOEN TCXO LDO Enable and MVBAT

Enable

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate

on the human body and test equipment and can discharge without detection. Although the

ADP3510 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. 0

–5–

Loading...

Loading...