a CDMA Power Management System

PRELIMINARY TECHNICAL DATA

Preliminary Technical Data ADP3500

FEATURES

Handles all CDMA Baseband and RF/IF Power Management

Functions

LDOs Optimized for Specific CDMA Subsystems

Four Backup LDOs for Stand-By mode operation

Four Li-Ion Battery Charge Modes

5mA Pre Charge

Low Current Charge

Full Current Charge

Regulator mode (no current limit)

Ambient Temperature: -30 °°°°Cto+85°°°°C

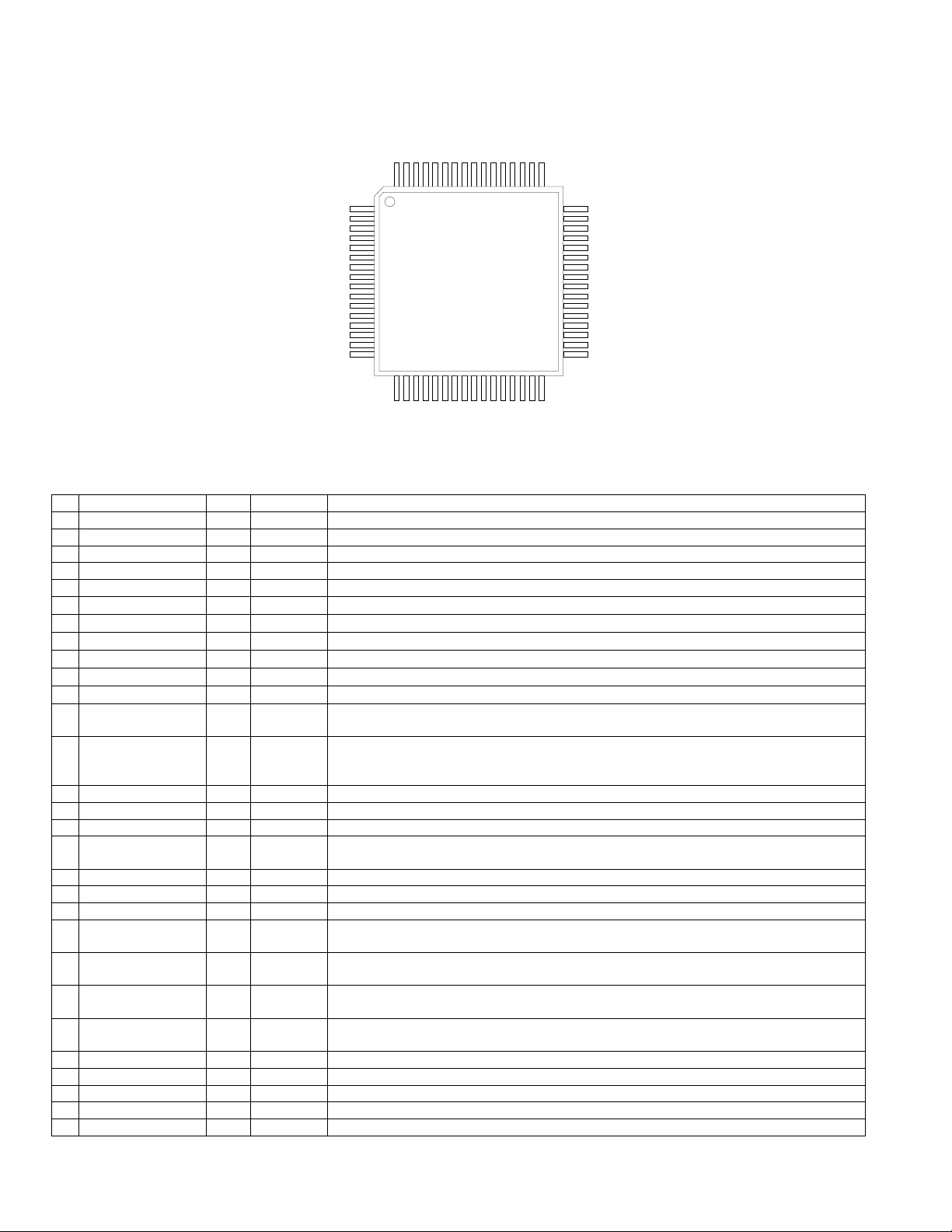

64pin 7x7 LQFP package

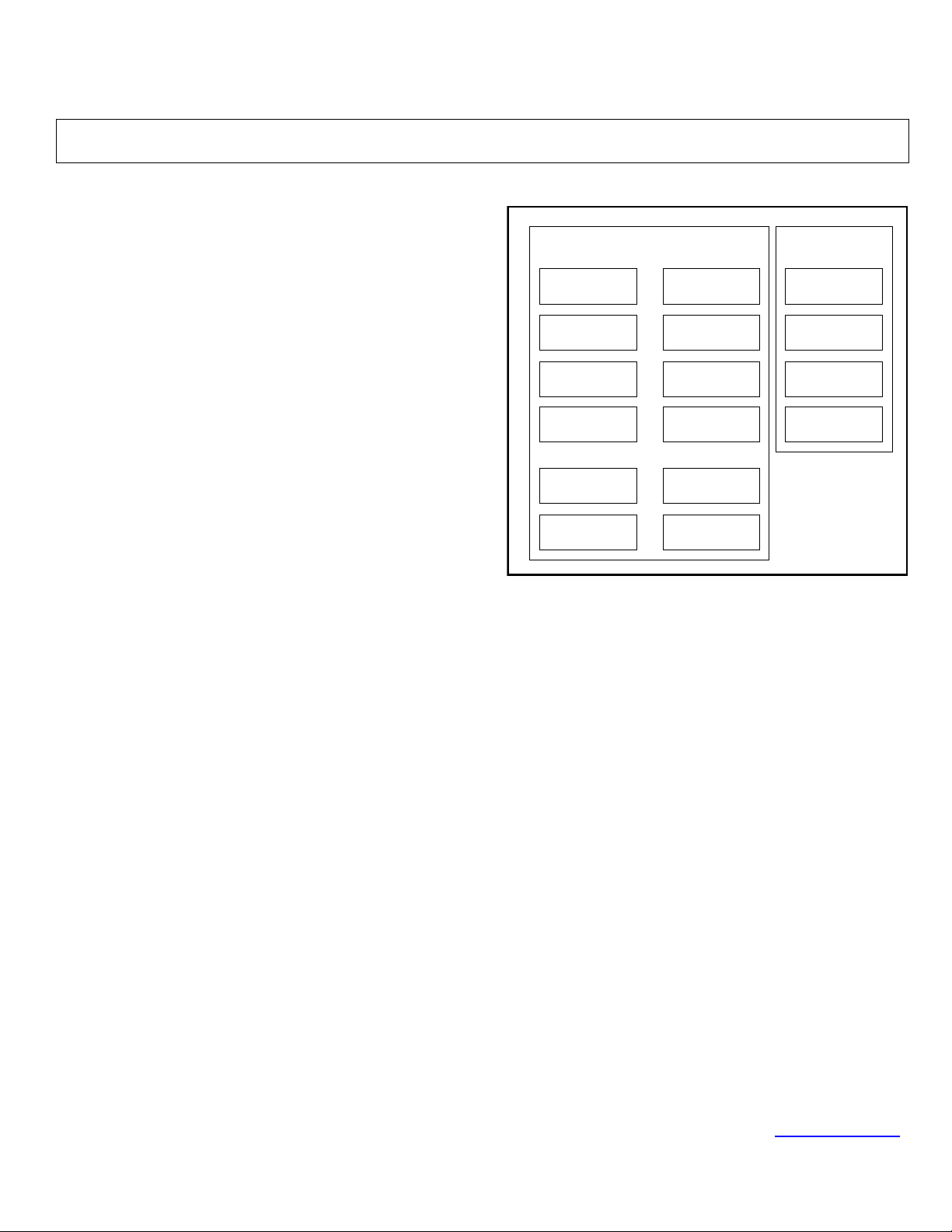

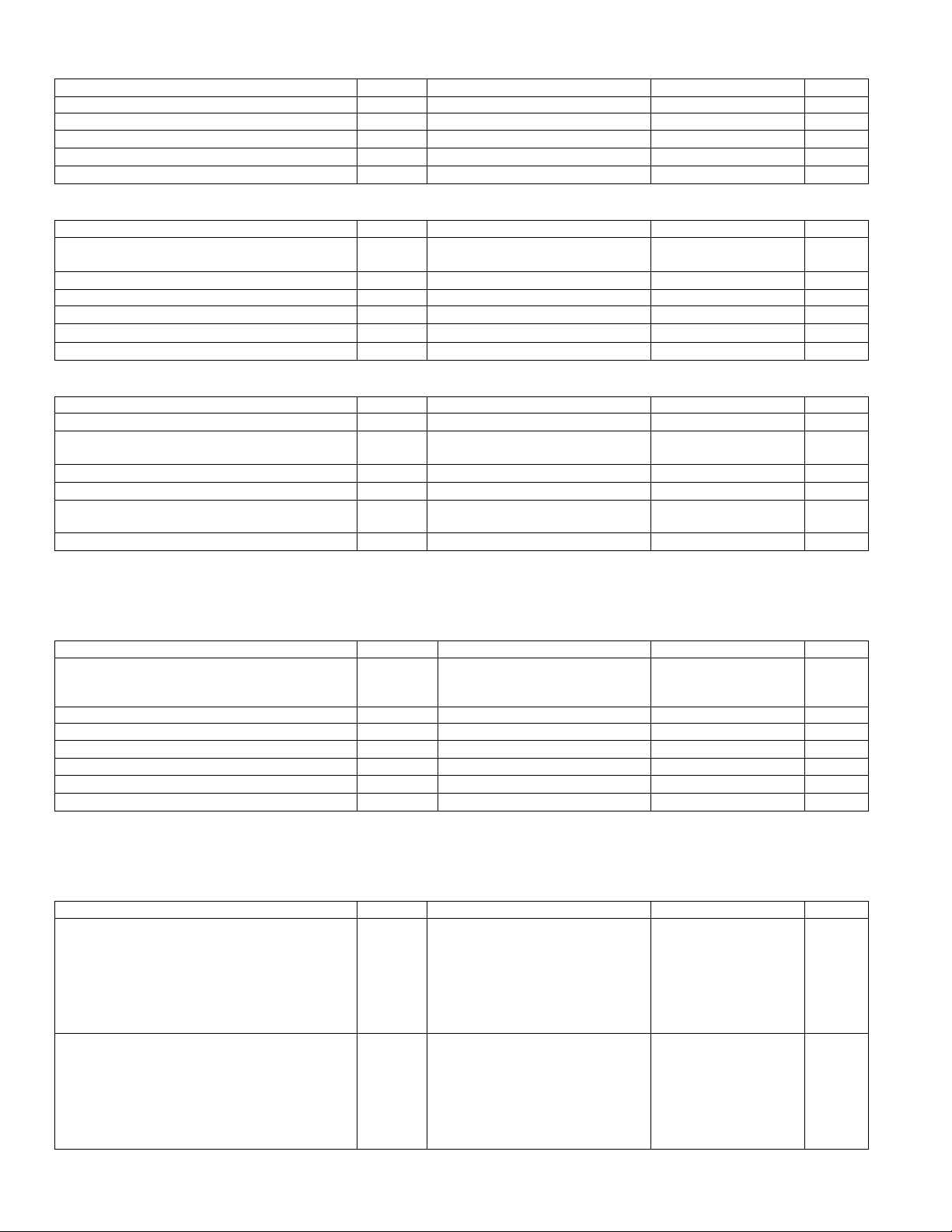

POWER ON

KEYPAD I/F

GPIO

LOGIC

BLOCK

DELAY 10mS

INTERRUPT

CONTROL

LDO CONTROL

ANALOG

BLOCK

BATTERY

CHARGER

REFERENCE

LDO1 to 11

APPLICATIONS

CDMA/CDMA2000/PCS Handsets

GENERAL DESCRIPTION

The ADP3500 is a multifunction power system chip optimized

for CDMA cell phone power management. It contains 15 LDOs.

Sophisticated controls are available for power up during battery

charging, keypad interface, GPIO/INT function and RTC

function. The battery charger has four modes as Pre-charge, Low

Current Charge, Full Current Charge, and Regulator modes, and

is designed for Li-Ion/Li-Polymer batteries.

SERIAL I/F

32KHz OUTPUT

CONTROL

RESET OUTPUT

Figure 1. Functional Block Diagram

RESET

RTC COUNTER

STAY-ALIVE

TIMER

VOLTAGE

DETECTOR

ADP3500

REV. PrP 2/6/02

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or apatent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-87ß3 ANALOG DEVICES, INC., 2002

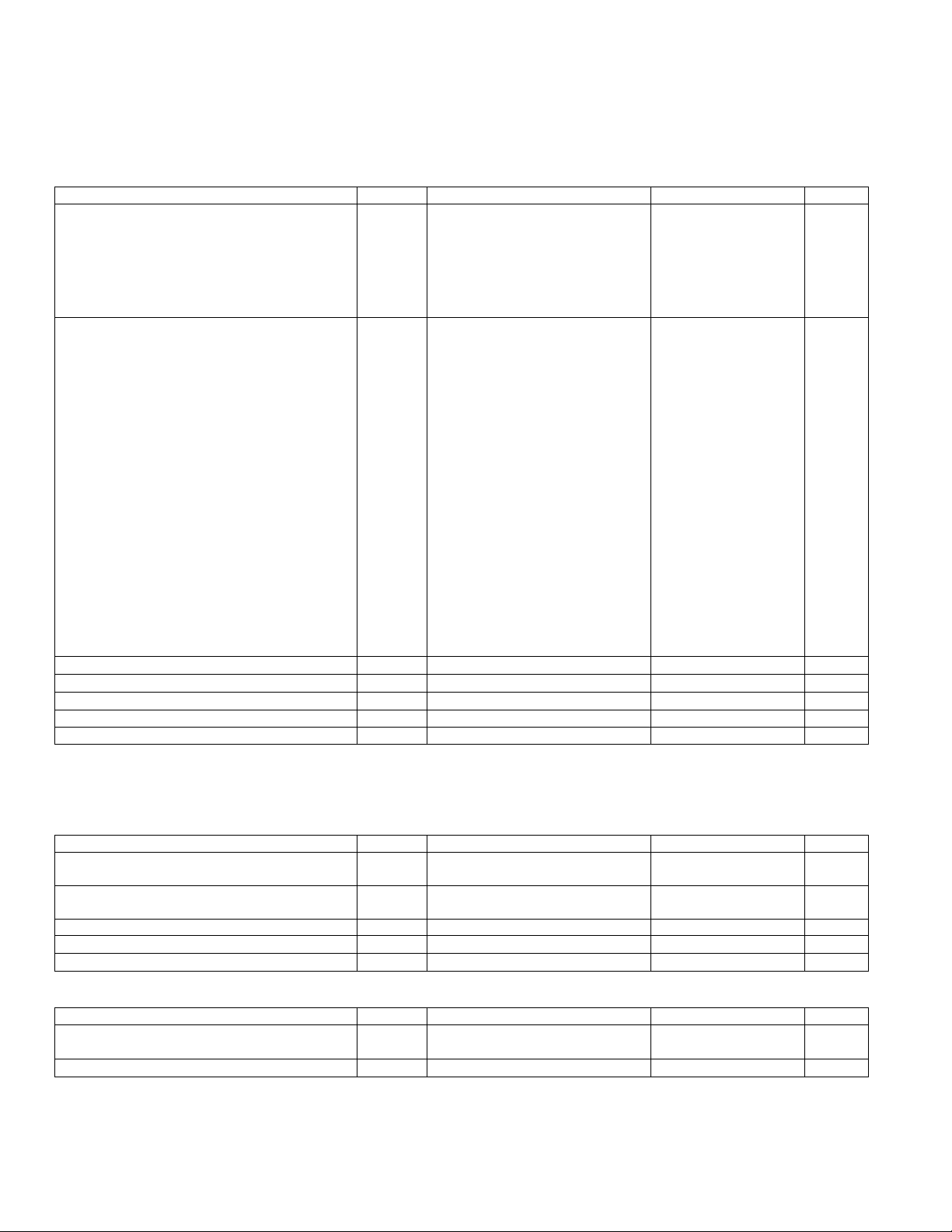

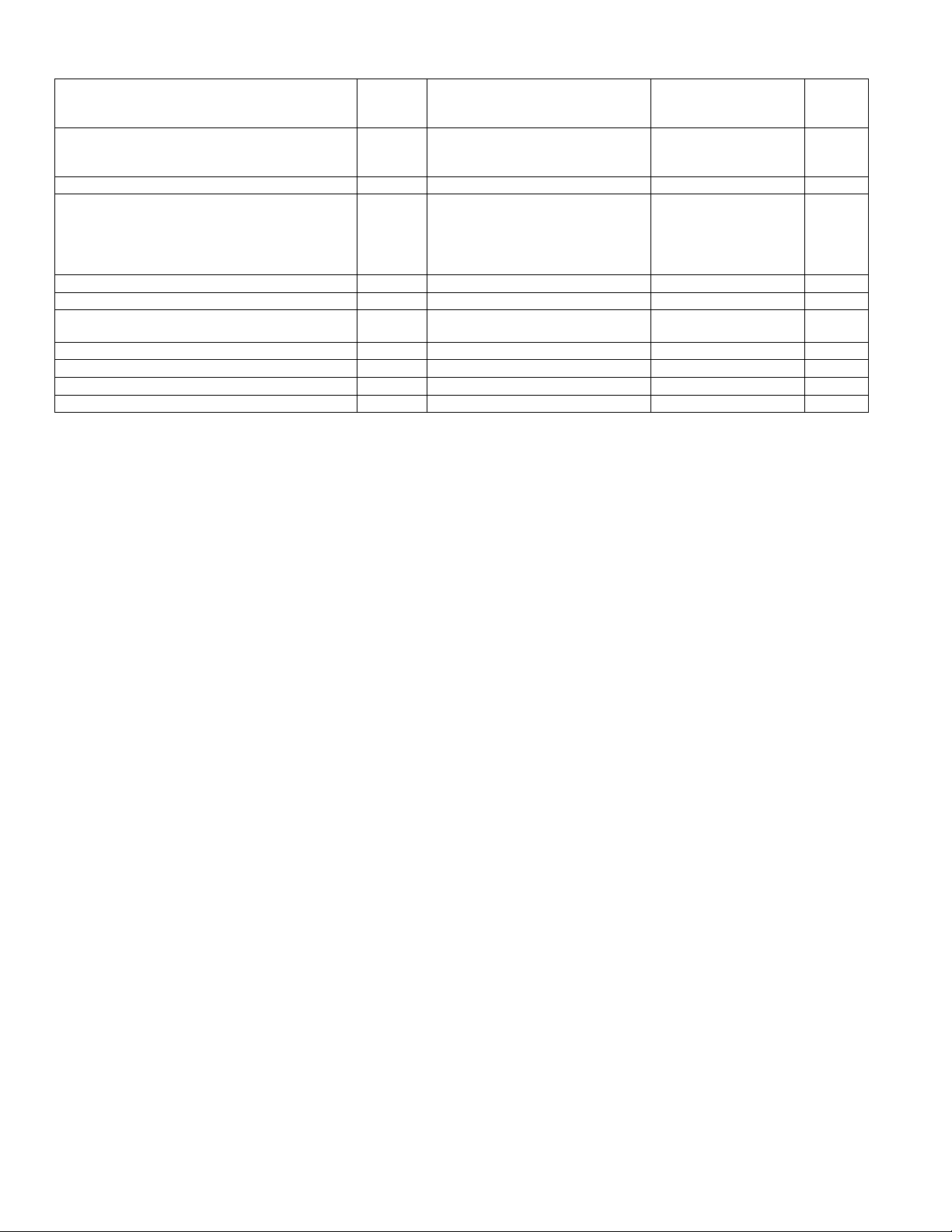

ADP3500 - SPECIFICATIONS

PRELIMINARY TECHNICAL DATA

MAIN FUNCTIONS

TA=-30 to +85°C, C

Parameter Symbol Conditions Min Typ Max Units

SHUTDOWN GND CURRENT

Power OFF

OPERATING GND CURRENT

Stand-by mode operation (light load)

Stand-by mode operation (Mid-load)

Active operation

Thermal Shutdown Threshold 160

Thermal Shutdown Hysteresis 35

Operational Temperature range Tope -30 +85

Adapter Voltage range (recommendation) VADP 5.5 12 V

VBAT Voltage range VBAT 3.3 5.5 V

=1µF MLCC, VBAT=3.6V unless otherwise noted. See Table 2 for C

VBAT

IGND

LDO3b : ON, connect to RTCV

through Schottky diode.

RTC/32K OSC : Active

AllotherLDOs:OFF

All logic inputs : VBAT or GND

MVBAT: OFF

IGND

LDO1b, 2b, 3b, 6b: ON

Io=1mA for LDO1b & 3b

Io=300µA for LDO2b & 6b

AllotherLDOs:OFF

RTC/32K OSC: Active

MVBAT: OFF

All logic output: no load

LDO1, 2, 3, 6, all Sub-LDO: ON,

Io=70% load

AllotherLDOs:OFF

RTC/32K OSC: Active

MVBAT: ON

All logic outputs: n o load

LDO5: OFF

All other LDOs: ON, 70% load

RTC/32K OSC: Active

All logic outputs: n o load

MVBAT: ON

OUT

.

25 40

60

275

650

125

µA

µA

µA

µA

°C

°C

°C

LDO SPECIFICATIONS

TA=25°C, C

Baseband VDD Main-LDO (LDO #1a)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

OUTPUT CAPACITOR REQUIRED FOR

STABILITY

DROPOUT VOLTAGE V

Start-up time from shutdown 250

GND Current I

Baseband VDD Sub-LDO (LDO #1b)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

GND Current I

REV.PrP 2/6/02 - 2 -

=1µF MLCC, VBAT = Vout+1V, NRCAP=0.1µF. See Table 2 for C

VBAT

LDO#1

C

LDO#1

DO

LDO#1

LDO#1b

LDO#1b

Io = 1 to 150 mA

Ta= -30 to +85°C

Io = 150 mA 200 mV

Io = 150 mA 50

Io = 1mA

Ta= -30 to +85°C

OUT

.

2.81 2.90 2.99 V

2.2

2.8 2.87 3.0 V

10

µF

µS

µA

µA

ADP3500

PRELIMINARY TECHNICAL DATA

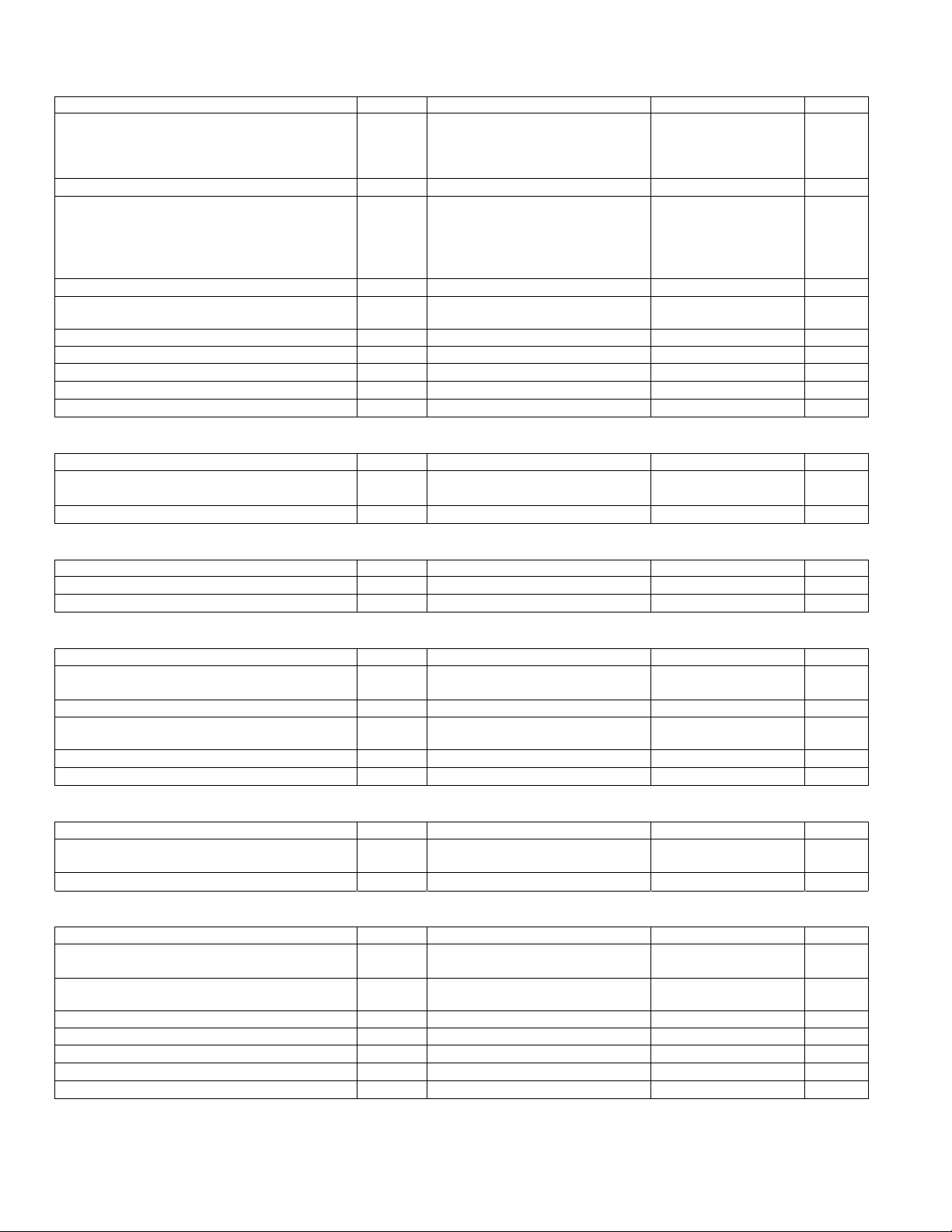

Baseband AVDD Main-LDO (LDO #2a)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT Voltage V

OUTPUT default voltage V

OUTPUT Voltage V

LDO#2

LDO#2

LDO#2

16 steps, 20mV/step, Ta= 25C,

Io=50mA

Code : 1000

Code : 0111

Io=50mA,Ta=25°C

16 steps, 20mV/step, Io=50mA, Ta=

-30to+85°C

Code : 1000

Code : 0111

2.30

2.60

2.36

2.66

2.43

2.74VV

2.46 2.52 2.6 V

2.29

2.57

2.36

2.66

2.47

2.81VV

OUTPUT default voltage V

OUTPUT CAPACITOR REQUIRED FOR

C

LDO#2

LDO#2

Io=50mA,Ta=-30to+85°C

2.42 2.52 2.66 V

1

µF

STABILITY

DROPOUT VOLTAGE V

DO

Io = 50 mA 210 mV

RIPPLE REJECTION f = 1KHz 50 dB

OUTPUT NOISE VOLTAGE V

NOISE

Start-up time from shutdown 250

GND Current I

LDO#2

f = 100 Hz to 100 kHz 120

Io = 50 mA 50

µV

µS

µA

Baseband AVDD Sub-LDO (LDO #2b)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT Voltage V

LDO#2b

Io = 300 µA, V

LDO#2a

=2.6V

2.50 2.70 V

Ta= -30 to +85°C

GND Current I

LDO#2b

5

µA

REFO switch

Parameter Symbol Conditions Min Typ Max Units

On resistance R

Off leak I

ON

LEAK

Ta= -30~+85°C, Io=500µA

LDO2: ON, Switch: OFF 0.01 1

50 130

Ω

µA

Coin Cell Main-LDO (LDO #3a)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

Dropout Voltage V

OUTPUT CAPACITOR REQUIRED FOR

C

LDO#3

DO

LDO#3

STABILITY

Start-up time from shutdown 250

GND Current I

LDO#3

Io = 1 to 50 mA

2.85 3.0 3.09 V

Ta= -30 to +85°C

Io= 50 mA 140 mV

1

µF

µS

Io = 50 mA 50

µA

RMS

Coin Cell Sub-LDO (LDO #3b)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

LDO#3b

Io=1mA

2.85 2.97 3.15 V

Ta= -30 to +85°C

GND Current I

LDO#3b

10

µA

Audio LDO (LDO #4)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

LDO#4

Io = 1 to 180 mA

2.81 2.90 2.99 V

Ta=-30to+85°C

OUTPUT CAPACITOR REQUIRED FOR

C

LDO#4

2.2

µF

STABILITY

Dropout Voltage V

DO

Io = 180 mA 200 mV

RIPPLE REJECTION f = 1KHz 50 dB

OUTPUT NOISE VOLTAGE V

NOISE

Start-up time from shutdown 250

GND Current I

LDO#4

f = 100 Hz to 10 kHz 50

Io = 180 mA 50

µV

µS

µA

REV.PrP 2/6/02 - 3 -

RMS

ADP3500

PRELIMINARY TECHNICAL DATA

Vibrator LDO (LDO #5)

Parameter Symbol Conditions Min Typ Max Units

Output Voltage V

Dropout Voltage V

Output capacitor required for stability C

GND Current I

LDO#5

DO

LDO#5

LDO#5

Baseband Core Main-LDO (LDO #6a)

Parameter Symbol Conditions Min Typ Max Units

Output Voltage V

Output capacitor required for stability C

Dropout Voltage V

LDO#6

LDO#6

DO

Start-up time from shutdown 250

GND Current I

LDO#6

Baseband Core Sub-LDO (LDO #6b)

Parameter Symbol Conditions Min Typ Max Units

OUTPUT VOLTAGE V

GND Current I

LDO#6b

LDO#6b

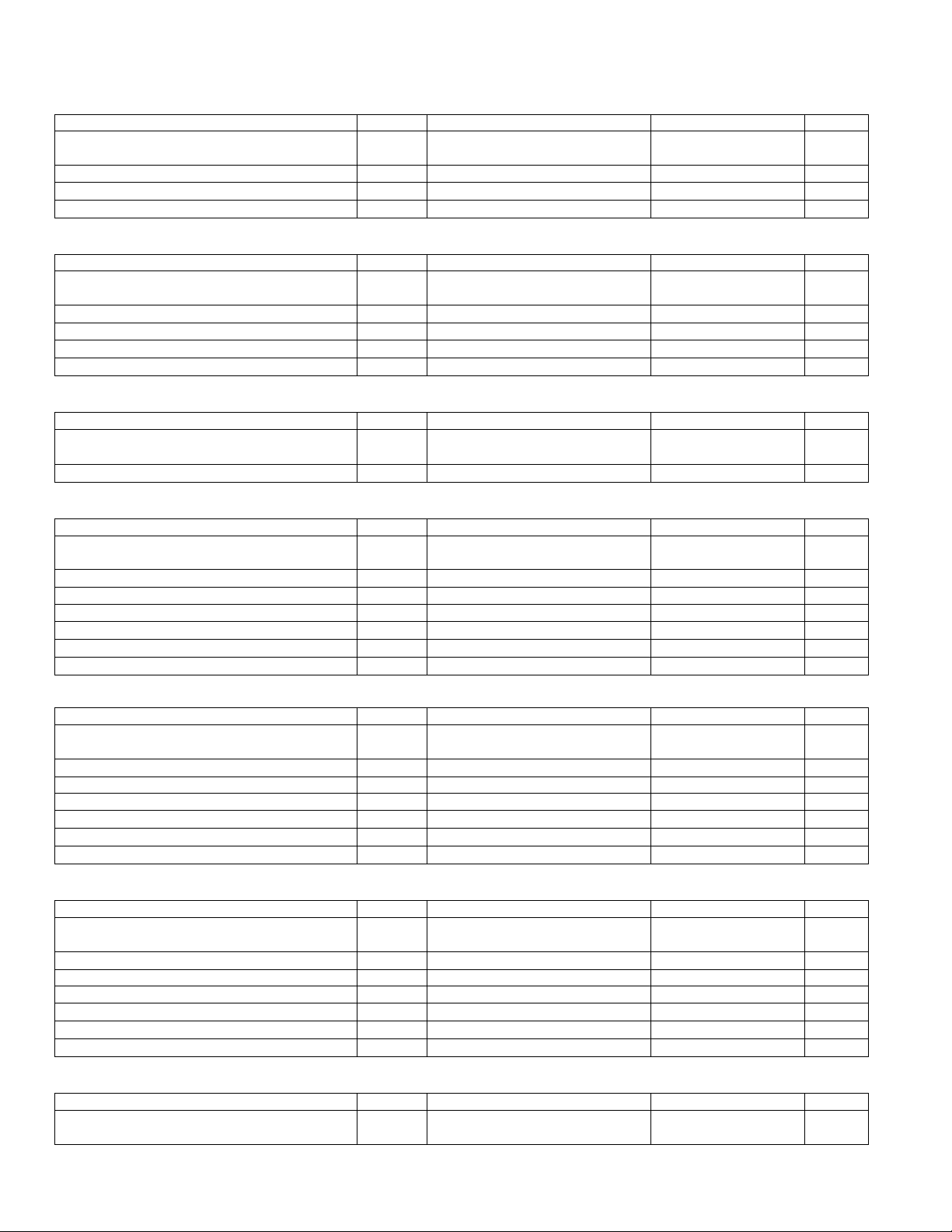

RF Rx1 LDO (LDO #7)

Parameter Symbol Conditions Min Typ Max Units

Output voltage V

Output capacitor required for stability C

Dropout voltage V

Ripple rejection f = 1KHz 50 dB

Output noise voltage V

Start-up time from shutdown 250

GND Current I

LDO#7

LDO#7

DO

NOISE

LDO#7

Io = 1 to 150 mA

2.75 2.9 3.05 V

Ta= -30 to +85°C

Io = 150mA 200 mV

2.2

Io = 150 mA 50

Io = 1 to 50 mA

2.52 2.60 2.68 V

µF

µA

Ta= -30 to +85°C

1

µF

Io = 50 mA 160 mV

µS

Io = 50 mA 50

Io = 300 µA

2.5 2.57 2.7 V

µA

Ta= -30 to +85°C

Io = 1 to 100 mA

5

2.81 2.9 2.99 V

µA

Ta= -30 to +85°C

1.5

µF

Io = 100 mA 200 mV

f = 100 Hz to 100KHz 40

µV

µS

Io=100mA 50

µA

RMS

RF Tx LDO (LDO #8)

Parameter Symbol Conditions Min Typ Max Units

Output voltage V

LDO#8

Io = 1 to 150 mA

2.81 2.9 2.99 V

Ta= -30 to +85°C

Output capacitor required for stability C

Dropout voltage V

LDO#8

DO

Io = 150mA 200 mV

2.2

µF

Ripple Rejection f = 1KHz 50 dB

Output noise voltage V

NOISE

Start-up time from shutdown 250

GND Current I

LDO#8

f = 100 Hz to 100KHz 40

Io=150mA 50

µV

µS

µA

RF Rx 2 LDO (LDO #9)

Parameter Symbol Conditions Min Typ Max Units

Output voltage V

LDO#9

Io = 1 to 50 mA

2.81 2.9 2.99 V

Ta= -30 to +85°C

Output capacitor required for stability C

Dropout voltage V

LDO#9

DO

Io = 50mA 150 mV

1

µF

Ripple Rejection f = 1KHz 50 dB

Output noise voltage V

NOISE

Start-up time from shutdown 250

GND Current I

LDO#9

f = 100 Hz to 100KHz 40

Io=50mA 50

µV

µS

µA

RF Optional LDO (LDO #10)

Parameter Symbol Conditions Min Typ Max Units

Output voltage V

LDO#10

Io= 1 to 50 mA

Ta= -30 to +85°C

2.81 2.9 2.99 V

RMS

RMS

REV.PrP 2/6/02 - 4 -

ADP3500

PRELIMINARY TECHNICAL DATA

Output capacitor required for stability C

Dropout voltage V

LDO#10

DO

Io = 50mA 150 mV

Ripple rejection f = 1KHz 50 dB

Output noise voltage V

NOISE

f = 100 Hz to 100KHz 40

Start-up Time from Shutdown 250

GND Current I

LDO#10

Io=50mA 50

Optional LDO (LDO #11)

Parameter Symbol Conditions Min Typ Max Units

Output voltage V

LDO#11

Io = 1 to 100 mA

Ta= -30 to +85°C

Output capacitor required for stability C

LDO#11

Ripple rejection f = 1KHz 50 dB

Output noise voltage V

NOISE

f = 100 Hz to 100KHz 50

Start-up Time from Shutdown 250

GND Current I

LDO#11

Io=150mA 50

Voltage Detector for LDO1 and LDO6

Parameter Symbol Conditions Min Typ Max Units

LDO1 detect voltage V

LDO1 release voltage V

LDO1 Hysteresis V

LDO6 detect voltage V

LDO6 release voltage V

LDO6 Hysteresis V

DET1

DET1

HYS1

DET6

DET6

HYS6

Ta= -30 to +85°C

Ta= -30 to +85°C

Ta= -30 to +85°C

Ta= -30 to +85°C

Ta= -30 to +85°C

Ta= -30 to +85°C

1

1.42 1.5 1.58 V

2.2

2.7 2.72 V

2.77 V

LDO1

-NOM

35 52 85 mV

2.3 2.33 V

2.40 V

LDO6

-NOM

40 60 100 mV

µF

µV

µS

µA

µF

µV

µS

µA

V

V

RMS

RMS

BATTERY VOLTAGE DIVIDER: MVBAT

TA=-30 to 85°C, C

Parameter Symbol Conditions Min Typ Max Units

MVBAT Output voltage

5 – bit programmable V

MVBAT Output voltage step Vstep VBAT=4.35V, MVEN = 1 6 mV/lsb

Output drive current capability Iout 1 2 mA

MVBAT Load Regulation

MVBAT Output Voltage Step VBAT = 4.35 V, MVEN = 1 6 mV

Operating Battery Current VBAT = 4.35 V, MVEN = 1 65 85

Shutdown Current VBAT = 4.35 V, MVEN = 0 1

=10µF MLCC, C

VBAT

=1µFMLCC

Adapter

unless otherwise noted

VBAT=4.35V, MVEN = 1

MVBAT

∆ΜVBAT 0 < Iout < 100 µA

code 10000

code 01111

2.484

2.673

2.508

2.697

2.533

2.727

V/V

V/V

35mV

µA

µA

BATTERY CHARGER

TA=-30 to 85°C, C

Parameter Symbol Conditions Min Typ Max Units

Charger Control Voltage Range

2 – bit programmable

Charger Control Voltage Range

2 – bit programmable

=10µF MLCC, C

VBAT

=1µF MLCC, 4.0V ≤ ADAPTER ≤ 12V

Adapter

VBAT

SENSE

Ta= 25 °C,

V

R_SENSE

5.5V ≤ ADAPTER ≤ 12V (note 1)

code 00 (default)

code 01

code 10

code 11

VBAT

SENSE

Ta= -20 to 55°C,

V

R_SENSE

5.5V ≤ ADAPTER ≤ 12V (note 1)

code 00 (default)

code 01

code 10

code 11

unless otherwise noted

= 6mV & 115mV,

= 6mV & 115mV,

3.926

4.150

4.170

4.190

3.905

4.130

4.146

4.166

3.980

4.190

4.210

4.230

3.980

4.190

4.210

4.230

4.034

4.230

4.250

4.270

4.065

4.250

4.278

4.300

V

V

V

V

V

V

V

V

REV.PrP 2/6/02 - 5 -

ADP3500

PRELIMINARY TECHNICAL DATA

Charger Detect On Threshold ADAPT

ERVBAT

Charger Detect Off Threshold ADAPT

ER-

VBAT

Charger Supply Current I

Current Limit Threshold

High Current Limit

(Full charge current enabled)

Low Current Limit

(Full charge current disabled)

Pre-Charge Current Source

Base Pin Drive Current Note 2. 15 28 mA

Deep Discharge Lock-Out (Releasing voltage) DDLO VBAT<DDLO, Ta=25C, 5mA Pre-

Deep Discharge Lock-Out Hysteresis 200 mV

ISENSE Bias Current I

BATID pull-up resistor to ADAPTER R

Minimum Load for Stability I

ADAPTER

ADAPT

ER-V

ISNS

BATID

L

ADAPTER=5V,VBAT=4.3V 2 mA

ADAPTER=5V

VBAT=3.6V

ISNS

VBAT=3.0 V

VBAT ≤ DDLO

charge, VBAT ramping up

V

=5V 1

ISNS

BATID=H. Note 3. 10 mA

Note 1: Overhead includes external components, including sense resistor, PNP and isolation diode.

2: DDLO hysteresis is dependent upon DDLO threshold value. If DDLO threshold is at maximum, DDLO hysteresis is at

maximum at the same time.

3: Guaranteed but not tested.

110 165 225 mV

52350mV

135401605518570mV

mV

357mA

2.675 2.78 V

µA

70 100 130

KΩ

REV.PrP 2/6/02 - 6 -

ADP3500

PRELIMINARY TECHNICAL DATA

LOGICS

DC Specifications

TA=25°C, C

Parameter Symbol Conditions Min Typ Max Units

CS, CLKIN, RESETIN-, TCXO_ON, SLEEP-,

KEYPADROW (Internal 10KΩ pull-up)

Input High Voltage

Input Low Voltage

Hysteresis

GPIO, DATA

Input High Voltage

Input Low Voltage

Hysteresis

Output High Voltage

Output Low Voltage

INT-

Output High Voltage

Output Low Voltage

BLIGHT (Open Drain Output)

Output Low Voltage

KEYPADCOL (Open Drain Output)

Output Low Voltage

PWRONKEY-, OPT1 (Internal 140KΩ Pull-up)

Input High Voltage

Input Low Voltage

Hysteresis

OPT2- (Input/Open Drain Output)

Input High Voltage

Input Low Voltage

Hysteresis

Output Low Voltage

OPT3

Input High Voltage

Input Low Voltage

Hysteresis

32KOUT

Output High Voltage

Output Low Voltage

RESET+ (Open Drain Output)

Output Low Voltage

OFF Leak

RSTDELAY-, RESETOUT- (Open Drain Output)

Output Low Voltage

BATID (Internal 100KΩ pull-up)

Input High Voltage

Input Low Voltage

Hysteresis

Supply Current of RTCV I

VADP: Adapter voltage

=1µF MLCC, VBAT = 3.6 V

VBAT

VIH

VIL

VIH

VIL

VOH

VOL

VOH

VOL

VOL

VOL

VIH

VIL

Vhys

VIH

VIL

Vhys

VOL

VIH

VIL

Vhys

VOH

VOL

VOL

OFF

VOL

VIH

VIL

OSC

IOH=400µA

IOL=-1.8mA

IOH=400µA

IOL=-1.8mA

IOL=-100mA

IOL=-1.8mA

IOL=-1.8mA

IOH=400µA

IOL=-1.8mA

IOL=-1.8mA

LEAK

IOL=-1.8mA

VADP=5 to 12V 0.8xVADP

RTCV=3V,

VBAT=0V

All logic: No load.

2.25

2.25

2.69

2.69

0.8xVBAT

0.8xVBAT

0.7xVBAT

0.9xRTCV

470

470

950

950

300

0.005

0.16 x

VADP

1

0.5

0.5

0.28

0.28

0.4

0.15

0.2xVBAT

0.2xVBAT

0.1xVBAT

0.2xVBAT

0.1xRTCVVV

0.1xRTCV

1

0.1xRTCV

0.2xVADPVV

V

V

mV

V

V

V

mV

V

V

V

V

V

V

V

V

mV

V

V

mV

V

V

V

mV

V

µA

V

V

µA

AC Specifications

All specs include temperature unless otherwise noted

Parameter Symbol Conditions Min Typ Max Units

Operational Supply Range RTCV 2 3.1* V

Oscillator Frequency F

Start-up Time (note) t

Frequency deviation f

REV.PrP 2/6/02 - 7 -

CLK

START

DEV

RTCV=0V to 3V 100 200 mS

RTCV=2 to 3V TBD

32.768 KHz

ADP3500

PRELIMINARY TECHNICAL DATA

Frequency Jitter

Cycle to Cycle

>100cycles

Long term Drift RTCV=3V, 3 minutes 10* ppm

SERIAL INTERFACE

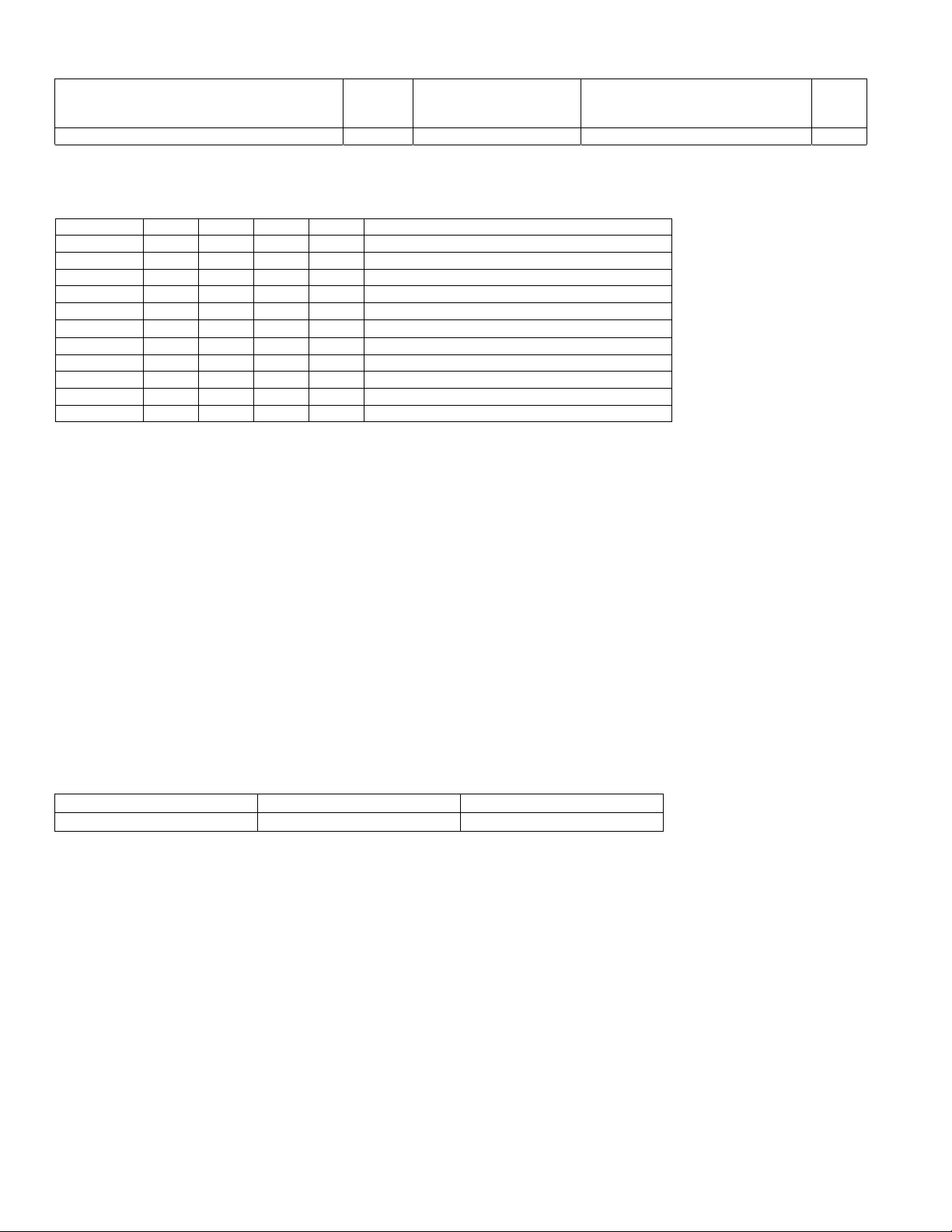

Parameter Min. Typ. Max Units Test Condition/Comments

t

t

t

t

t

t

t

t

t

t

t

CKS

CSS

CKH

CKL

CSH

CSR

DS

DH

RD

RZ

CSZ

50 nS CLK set-up time

50 nS CS set-up time

100 nS CLK “High” Duration

100 nS CLK “Low” Duration

100 nS CS hold time

62

µS

50 nS Input data set-up time

40 nS Input data hold time

50 nS Data output delay time

50 nS Data output floating time

50 nS Data output floating time after CS goes low.

Note: These parameters are not tested.

ABSOLUTE MAXIMUM RATINGS

Voltage on ADAPTER pin to GND ……………………………..... -0.3, 15Vmax

Voltage on VBAT pin to GND …………………………………… -0.3, 7Vmax

Voltage on Pin 6-13, 21-28 to GND ……………………………… -0.3, V

Voltage on Pin 1, 62-64 ………………………………………….. - 0.3, VBAT+0.3V max

Voltage on Pin 20, 32 …………………………………………….. - 0.3, V

Voltage on Pin 60, 61 ……………………………………………... - 0.3, V

Voltage on Pin 2-5, 14, 30, 31, 33 …………………………………. - 0.3, 7V max

Storage Temperature Range ………………………………………. - 65 to +150 °C

Operating Temperature Range ……………………………………. - 30 to +85°C

Maximum Junction Temperature …………………………………. 125°C

Thermal Impedance (LQFP-64) ………………………………. 2 layer bo ard 76°C/W

θ

JA

θ

Thermal Impedance (LQFP-64) ………………………………. 4 layer bo ard 54°C/W

JA

Lead Temperature Range (Soldering, 60 sec) ……………………... 300°C

/S

f

JITTER

EC

CS recovery time

RTCV=3V, TA=25°C

+0.3Vmax

LDO1

+0.3V max

RTCV

ADAPTER

40*

50*

+0.3V max

nS

nS

ORDERING GUIDE

Model Temperature Range Package

ADP3500AST -30 C to 85 C LQFP 64 pins

REV.PrP 2/6/02 - 8 -

ADP3500

:

PRELIMINARY TECHNICAL DATA

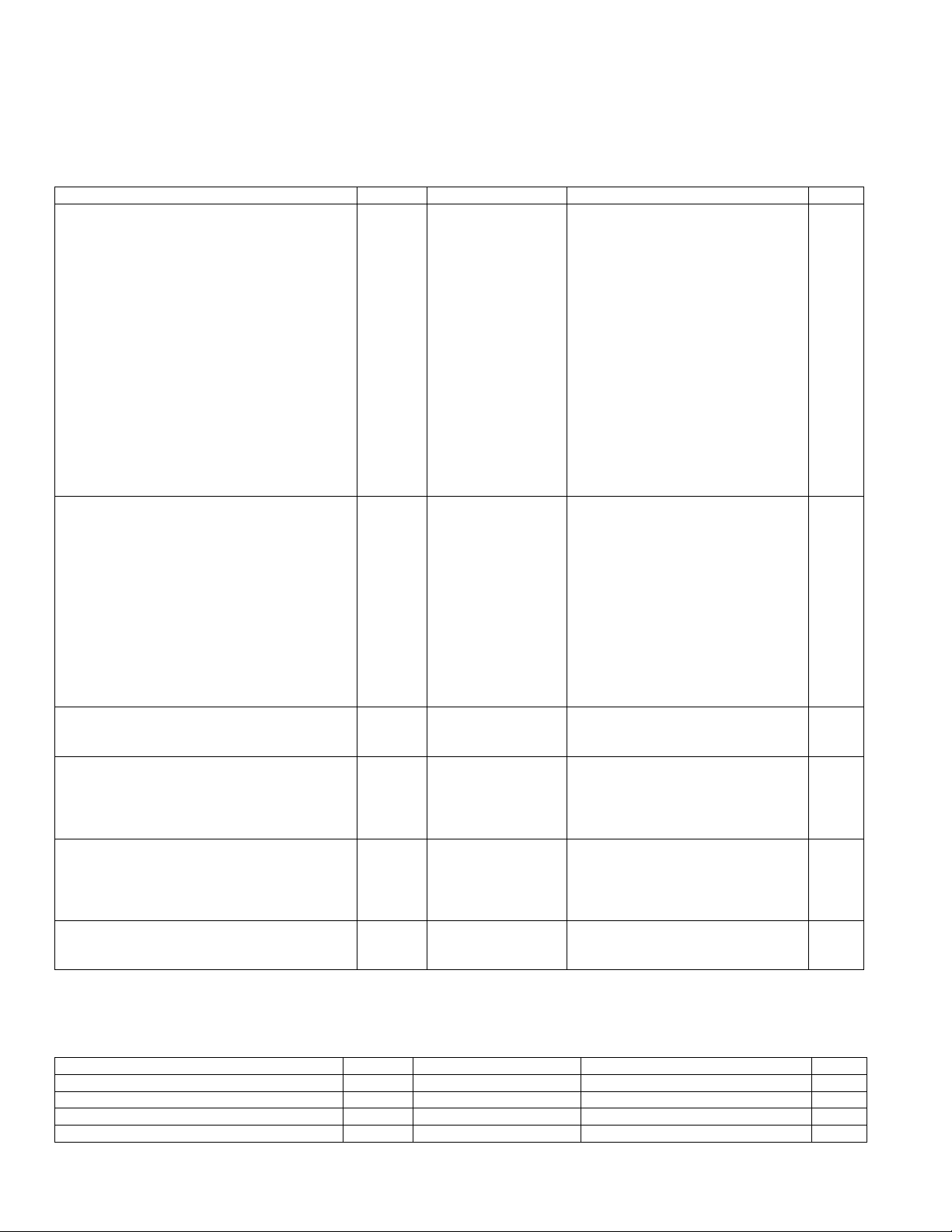

PIN CONFIGURATION

R

E

E

2

T

P

O

T

S

D

P

E

I

N

A

T

S

E

A

A

D

W

S

B

B

I

A

P

64 49

1

OPT3

KEYPADCOL0

KEYPADCOL1

KEYPADCOL2

KEYPADCOL3

KEYPADROW0

KEYPADROW1

KEYPADROW2

KEYPADROW3

KEYPADROW4

KEYPADROW5

TCXO_ON

SLEEPBLIGHT

DGND

INT-

16

17

0

1

V

C

T

R

2

D

O

O

O

N

I

I

I

C

G

P

P

P

S

A

G

G

G

O

Figure 2. Pin Configuration

PIN DESCRIPTION

Pin Mnemonic I/O Supply Function

1 OPT3 I VBAT Optional Power ON input. ADP3500 will keep “power ON” during this pin goes “High”.

2 KEYPADCOL0 O LDO1 Keypad Column Strobe 0 (Open Drain, pull low)

3 KEYPADCOL1 O LDO1 Keypad Column Strobe 1 (Open Drain, pull low)

4 KEYPADCOL2 O LDO1 Keypad Column Strobe 2 (Open Drain, pull low)

5 KEYPADCOL3 O LDO1 Keypad Column Strobe 3 (Open Drain, pull low)

6 KEYPADROW0 I LDO1

7 KEYPADROW1 I LDO1

8 KEYPADROW2 I LDO1

9 KEYPADROW3 I LDO1

10 KEYPADROW4 I LDO1

11 KEYPADROW5 I LDO1

12 TCXO_ON I LDO1 Logic input pin for Main LDOs (LDO1, LDO2, LDO3, LDO6) turning on control. L: OFF, H

13 SLEEP- I LDO1 Logic input pin for RF Rx LDOs (LDO7 and LDO9). Gatingregister data with this input for

14 BLIGHT O VBAT LEDdrive. Open drain output.

15 DGND - - Digital Ground

16 INT- O LDO1 Interrupt signal output

17 RTCV - - Supply input for RTC, 32KHz OSC, and some other logics. Connects to Coin cell battery in

18 OSCOUT - RTCV Connect to 32.768KHz crystal.

19 AGND - - Analog Ground

20 OSCIN - RTCV Connect to 32.768KHz crystal.

21 GPIO0 I/O LDO1 General Purpose Input and Output port. Integrated Interrupt function. Interrupt occurs both

22 GPIO1 I/O LDO1 General Purpose Input and Output port. Integrated Interrupt function. Interrupt occurs both

23 GPIO2 I/O LDO1 General Purpose Input and Output port. Integrated Interrupt function. Interrupt occurs both

24 GPIO3 I/O LDO1 General Purpose Input and Output port. Integrated Interrupt function. Interrupt occurs both

25 DATA I/O LDO1 Serial Interface data input and output.

26 CS I LDO1 Serial Interface Chip Select input. ActiveHigh input.

27 CLKIN I LDO1 Serial Interface Clock input.

28 RESETIN- I LDO1 Reset input signal for internal reset signal and starts Stay-Alive timer.

29 32KOUT O RTCV 32.768KHz output. Output after 30mS when Reset is released.

Keypad Row Input 0. Pulled up internally, 10KΩ

Keypad Row Input 1. Pulled up internally, 10KΩ

Keypad Row Input 2. Pulled up internally, 10KΩ

Keypad Row Input 3. Pulled up internally, 10KΩ

Keypad Row Input 4. Pulled up internally, 10KΩ

Keypad Row Input 5. Pulled up internally, 10KΩ

ON

these LDOs. LDO7 and LDO9 are turned OFF when SLEEP- goes Low even if the registers

set to ON.

typical operation.

falling and raising edge.

falling and raising edge.

falling and raising edge.

falling and raising edge.

)

n

o

i

t

)

p

2

)

x

x

O

T

R

F

F

F

R

(

R

R

(

(

P

T

0

A

D

A

B

N

C

V

R

G

N

M

A

D

1

9

8

T

N

S

A

O

O

V

B

O

G

B

D

D

D

A

V

L

L

L

48

VBAT

LDO7 (RF Rx1)

LDO6 (Baseband Core)

VBAT

LDO5 (Vibrator)

LDO4 (Audio)

VBAT

LDO2 (Baseband AVDD)

REFO

AGND

LDO3 (RT C/Coin-cell)

VBAT

LDO1 (Baseband VDD)

LDO11 (Option)

VBAT

RSTDELAY-

33

32

3

T

O

I

A

P

D

G

+

S

N

I

C

K

L

C

T

T

N

T

S

I

U

E

E

T

O

S

T

E

T

E

S

E

R

E

S

R

E

R

-

-

A

REV.PrP 2/6/02 - 9 -

Loading...

Loading...