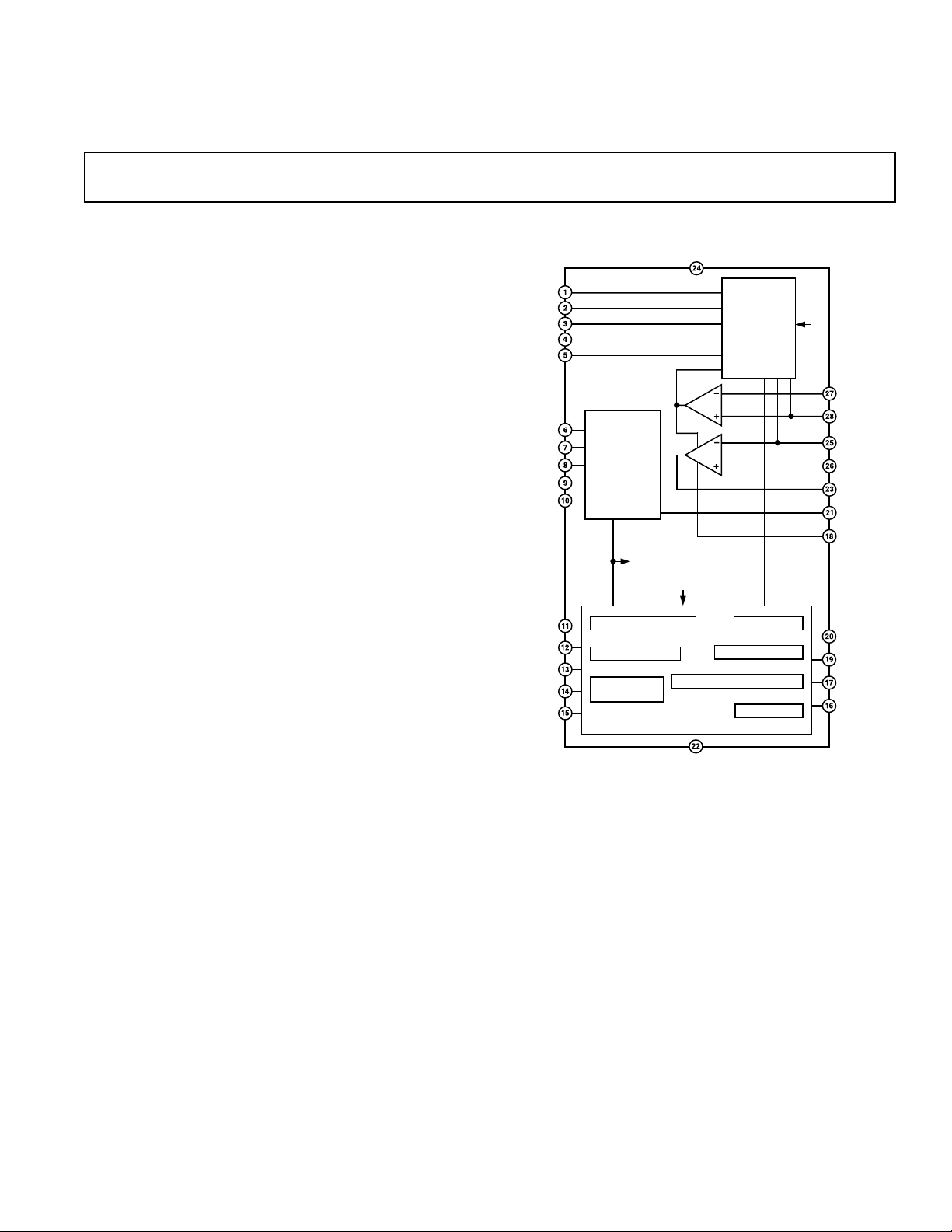

Analog Devices ADP3422JRU Datasheet

IMVP-II-Compliant

BOMSEL

HYSTERESIS

AND

SHIFT-SETTING

DSLPSEL

VID4

VID3

VID2

VID1

VID0

CS+

CS–

ADP3422

VR

CLIM

CORE

PROGRAMMED

DAC

AND

FIXED

REFERENCE

VCC

VCC

VR

GND

COREFB

SS

DRVLSD

CLAMP

RAMP

REG

OUT

DACOUT

SWFB

EN

UVLO AND MAIN BIAS

SR CONTROL

PWRGD MONITOR

PWRGD BLANKER

SS-HICCUP TIMER AND OCP

OVP AND RVP

OP MODE

SELECTOR

POWER MANAGEMENT

SD

PWRGD

DPRSLP

DSLP

BOM

CPUSET

HYSSET

FSHIFT

DSHIFT

BSHIFT

a

Core Power Controller for Mobile CPUs

FEATURES

Certified IMVP-II Controller

Excellent Transient Containment

Minimum Number of Output Capacitors

Fast, Smooth, Output Transition During VID Code Change

Current Limit with Hiccup Protection

Transient-Glitch-Free Power Good

Low Shutdown Current

Soft Start Eliminates In-Rush Current Surge

Adaptive Noise-Blanking Enhancement for Speed and

Stability

Highly Redundant Over-Voltage and Reverse-Voltage

Protection

Controls Synchronous Rectifier for Improved Battery Life

APPLICATIONS

IMVP-II Enabled Core DC/DC Converters

Fixed-Voltage Mobile CPU Core DC/DC Converters

Notebook/Laptop Power Supplies

Programmable Output Power Supplies

ADP3422

FUNCTIONAL BLOCK DIAGRAM

GENERAL DESCRIPTION

The ADP3422 is a hysteretic dc-dc buck converter controller to

power a mobile processor’s core. The optimized low voltage

design is powered from the 3.3 V system supply. The output

voltage is set by a 5-bit VID code. To accommodate the transition

time required by the newest processors for on-the-fly VID

changes, the ADP3422 features high-speed operation to allow a

minimized inductor size that results in the fastest change of

current to the output. To further allow for the minimum number

of output capacitors to be used, the ADP3422 features active

voltage positioning that can be optimally compensated to ensure a

superior load transient response. The output signal interfaces

with the ADP3415 MOSFET driver that is optimized for high

speed and high efficiency for driving both the upper and lower

(synchronous) MOSFETs of the buck converter.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

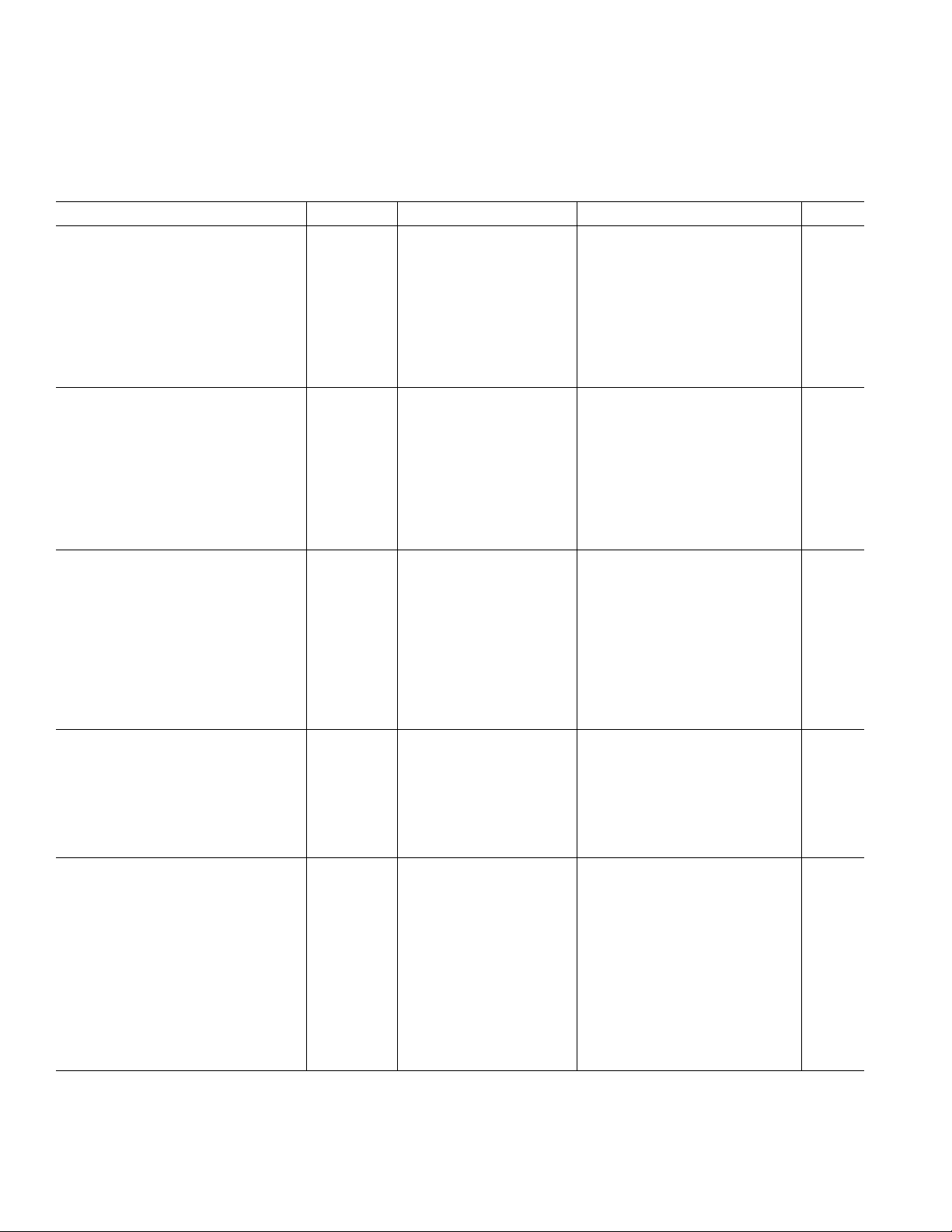

ADP3422–SPECIFICATIONS

1

ELECTRICAL CHARACTERISTICS

( V

DACOUT

), V

REG

= V

CS–

= V

= 1.25 V, V

VID

CPUSET

(0 ≤ TA ≤ 85ⴗC, High (H) = VCC, Low (L) = 0 V, VCC = 3.3 V, SD = H, V

= 0 V, R

= 100 k⍀, C

OUT

= 10 pF, CSS = 47 nF, R

OUT

= 5 k⍀ to VCC, R

PWRGD

to VCC, HYSSET, BSHIFT, DSHIFT, and FSHIFT are open, BOM = H, DSLP = H, DPRSLP = L, SWFB = L, unless otherwise noted. Current sunk

by a pin has a positive sign, sourced by a pin has a negative sign.)

Parameter Symbol Conditions Min Typ Max Unit

SUPPLY-UVLO-SHUTDOWN

Normal Supply Current I

UVLO Supply Current I

Shutdown Supply Current I

CC

CC(UVLO)

CCSD

SD = L 1 µA

615 mA

200 µA

UVLO Threshold

VCC Rising Up, VSS = 0 V 2.95 V

VCC Falling, VSS Floating 2.7 V

50 mV

VCC/2

UVLO Hysteresis V

Shutdown Threshold (CMOS Input) V

V

CCH

V

CCL

CCHYS

SDTH

POWERGOOD

Core Feedback Threshold Voltage V

PowerGood Output Voltage V

COREFBH

PWRGD

(Open Drain Output) V

Blanking Time t

PWRGD,BLNK

0.9 V < V

V

COREFB

V

COREFB

V

COREFB

V

COREFB

V

COREFB

COREFB

2

VCC = 3.3 V 100 µs

< 1.675 V

DAC

Rising 1.12 V

Falling 1.095 V

Rising 0.88 V

Falling 0.855 V

= V

DACOUT

= 0.8 V

DACOUT

0.95 V

0 0.8 V

DAC

DAC

DAC

DAC

CC

1.145 V

1.12 V

0.905 V

0.88 V

V

SOFT-START/HICCUP TIMER

Charge/Discharge Current I

Soft-Start Enable/Hiccup V

SS

SSEN

Termination Threshold V

Soft-Start Termination/Hiccup V

SSTERM

Enable Threshold V

VSS = 0.5 V –16 µA

= 0.5 V, VCC = 2.5 V 0.6 µA

V

SS

V

= 1.25 V,

REG

= V

RAMP

Falling 150 200 mV

V

SS

V

Rising 200 mV

SS

V

= V

RAMP

Rising 2.05 V

SS

COREFB

COREFB

= 1.27 V

= 1.27 V

VSS Falling 2.0 V

VID DAC

VID Input Threshold (CMOS Inputs) V

VID Input Current I

VID0...4

VID0...4

VID 0...4 = L 10 40 µA

0.8 0.7 V

(Internal Active Pull-up)

Output Voltage V

Output Voltage Accuracy ⌬V

Output Voltage Settling Time

3

t

DACS

DAC

DAC/VDAC

4

See VID Code Table 1 0.600 1.750 V

–0.85 +0.85 %

1.3 µs

CORE COMPARATOR

Input Offset Voltage V

Input Bias Current I

Output Voltage V

Propagation Delay Time

Rise and Fall Time

3

2

Blanking Time t

COREOS

REG

OUT_H

V

OUT_L

t

RMPOUT_PD

6

t

OUT_R

6

t

OUT_F

BLNK

V

= 1.25 V ±1.5 mV

REG

V

REG

= V

= 1.25 V ±0.3 µA

RAMP

VCC = 3.0 V 2.5 3.0 V

VCC = 3.6 V 0 0.4 V

5

50 ns

310 ns

310 ns

OUT L-H Transition 75 ns

OUT H-L Transition 140 ns

Switch Feedback Threshold V

SWFB_TH

VCC/2 V

(CMOS Input)

COREFB

CLAMP

CC

= V

DAC

= 5.1 k⍀

DAC

DAC

DAC

DAC

CC

V

V

V

V

V

V

–2–

REV. 0

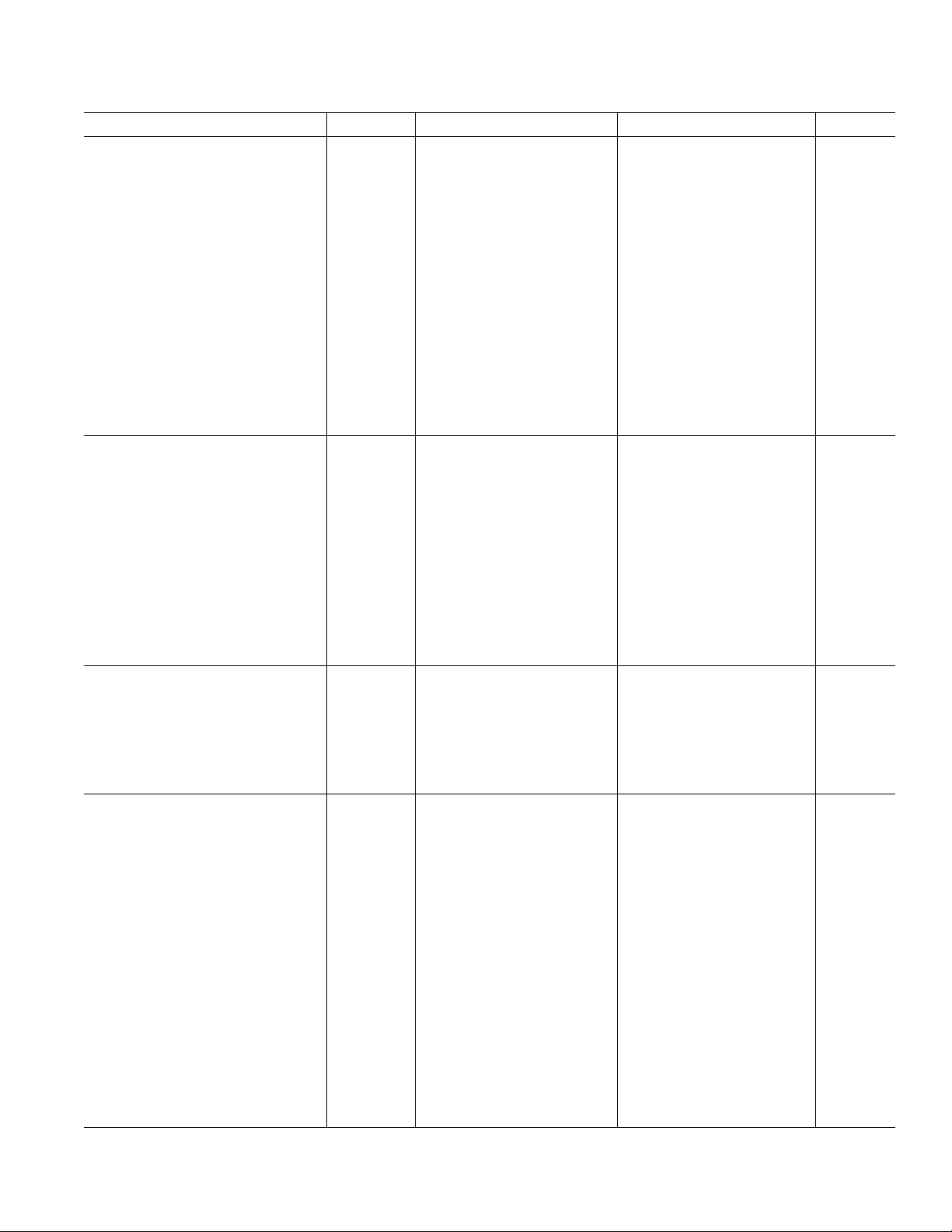

ADP3422

Parameter Symbol Conditions Min Typ Max Unit

HYSTERESIS SETTING

Hysteresis Current I

Hysteresis Reference Voltage V

SHIFT SETTING

Battery-Shift Current I

Battery-Shift Reference Voltage V

DeepSleep-Shift Current I

DeepSleep-Shift Reference Voltage V

CPU-FID-Shift Current I

CPU-FID-Shift Reference Voltage V

SHIFT CONTROL INPUTS

BOM Threshold V

(CMOS Input)

DSLP Threshold V

(IO-Level CMOS Input)

DPRSLP Mode Threshold V

(CMOS Input)

CURRENT LIMIT COMPARATOR

Input Offset Voltage V

Input Bias Current I

Hysteresis Current I

Propagation Delay Time t

RAMP_H

HYSSET

RAMPB

BSHIFT

RAMPD

DSHIFT

RAMPF

FSHIFT

BOM

DSLP

DPRSLP

CLIMOS

CS+

CS–

5

CLPD

V

= 1.25 V

REG

V

I

V

I

I

V

I

I

V

I

I

V

I

I

= V

COREFB

HYSSET

RAMP

HYSSET

HYSSET

RAMP

HYSSET

HYSSET

RAMP

HYSSET

HYSSET

RAMP

HYSSET

HYSSET

DAC

= 0 ±1 µA

= 1.23 V, BOM = H

= –10 µA +8 +10 +12 µA

= –100 µA +89 +100 +111 µA

= 1.27 V, BOM = H

= –10 µA –8 –10 –12 µA

= –100 µA –89 –100 –111 µA

= 1.23 V, BOM = L

= –10 µA +6.4 +8 +9.6 µA

= –100 µA +71 +80 +89 µA

= 1.27 V, BOM = L

= –10 µA –6.4 –8 –9.6 µA

= –100 µA –71 –80 –89 µA

1.61 1.7 1.79 V

V

= 1.25 V –92.5 –100 –107.5 µA

VID

I

= –100 µA, BOM = L

BSHIFT

DSLP = H, V

V

= 1.25 V –92.5 –100 –107.5 µA

VID

= –100 µA, BOM = H

I

DSHIFT

DSLP = L, V

V

= 1.25 V –92.5 –100 –107.5 µA

VID

I

= –100 µA, BOM = L

FSHIFT

DSLP = H, V

CPUSET

CPUSET

CPUSET

= 0 V

= 0 V

= 2 V

V

V

V

DAC

DAC

DAC

V

V

V

VCC/2 V

0.9 V

VCC/2 V

V

= 1.25 V ±0.2 ±6mV

CS–

V

= 1.25 V –0.3 µA

CS+

V

V

V

V

V

V

= V

COREFB

= V

REG

CS+

CS+

CS+

CS+

CS–

I

HYSSET

= 1.23 V BOM = H

I

HYSSET

I

HYSSET

= 1.27 V, BOM = H –1.5 –3 µA

I

HYSSET

I

HYSSET

= 1.23 V, BOM = L

I

HYSSET

I

HYSSET

= 1.27 V, BOM = L

I

HYSSET

I

HYSSET

= 1.23 V

RAMP

= 1.25 V

= 0 –0.6 –3 µA

= –10 µA –27 –31.5 –36 µA

= –100 µA –270 –301.5 –333 µA

= –10 µA –18 –21.5 –25 µA

= –100 µA –180 –201.5 –223 µA

= –10 µA –21 –25.5 –30 µA

= –100 µA –226 –241.5 –267 µA

= –10 µA –14 –17.5 –21 µA

= –100 µA –144 –161.5 –179 µA

65 ns

REV. 0

–3–

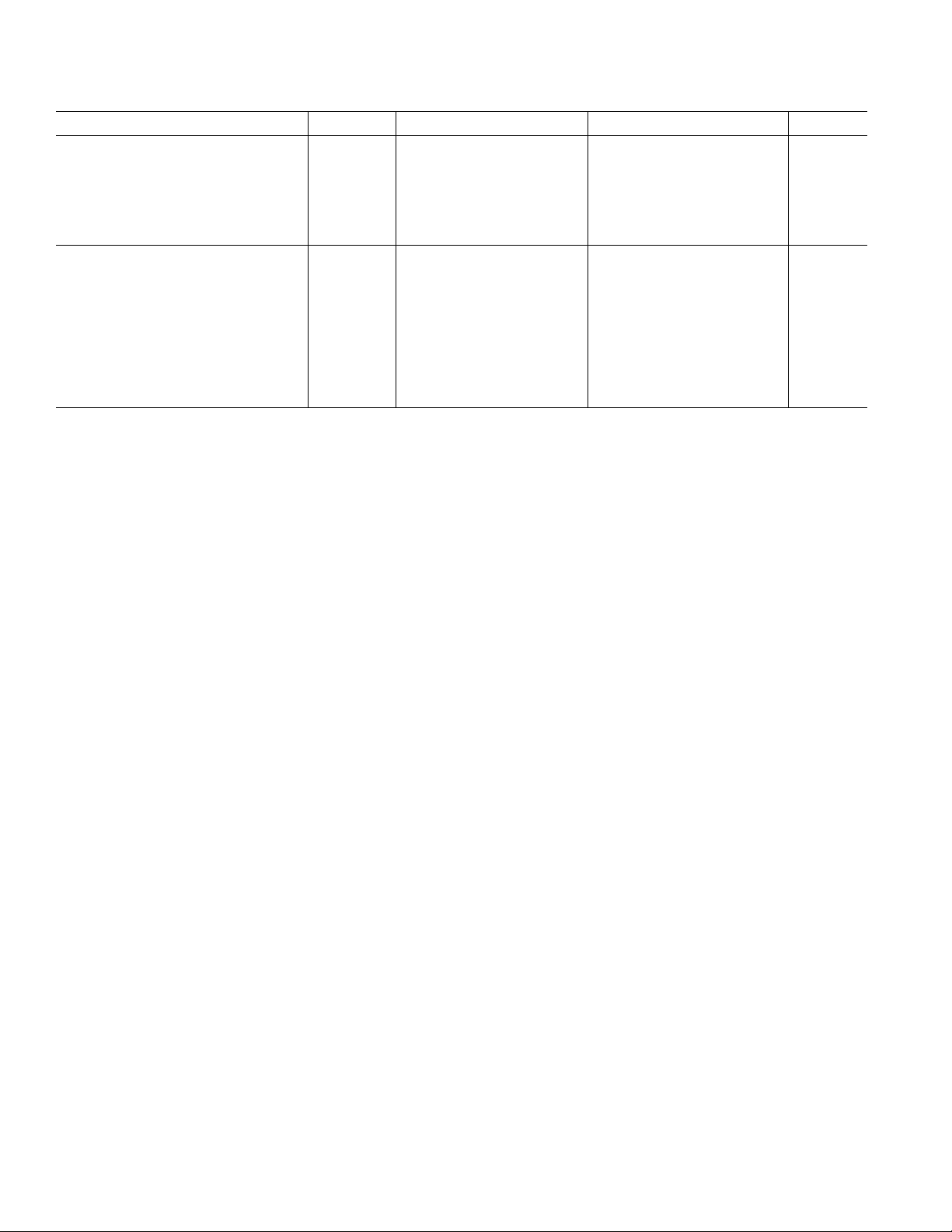

ADP3422–SPECIFICATIONS

(continued)

Parameter Symbol Conditions Min Typ Max Unit

LOW-SIDE DRIVE CONTROL

Output Voltage (CMOS Output) V

Output Current I

DRVLSD

DRVLSD

DPRSLP = H 0.4 V

DPRSLP = L 0.7 V

V

DRVLSD

= 1.5 V

CC

V

CC

V

DPRSLP = L +0.4 mA

DPRSLP = H –0.4 mA

OVER/REVERSE VOLTAGE

PROTECTION

Over-Voltage Threshold V

COREFB,OVPVCOREFB

V

Reverse-Voltage Threshold V

COREFB,RVPVCOREFB

V

Output Current (Open Drain Output) I

CLAMP

V

V

V

NOTES

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

Two test conditions:

1. PWRGD is OK but forced to fail by applying an out-of-the-CoreGood-window voltage (V

after the moment that BOM or DPRSLP is asserted/deasserted. PWRGD should not fail immediately, only with the specified blanking delay time.

2. PWRGD is forced to fail (V

BOM or DPRSLP is asserted/deasserted. PWRGD should not go high immediately, only with the specified blanking delay time.

3

Guaranteed by characterization.

4

Measured from 50% of VID code transition amplitude to the point where V

5

40 mV p-p amplitude impulse with 20 mV overdrive. Measured from the input threshold intercept point to 50% of the output voltage swing.

6

Measured between the 30% and 70% points of the output voltage swing.

Specifications subject to change without notice.

COREFB,BAD

= 1.0 V at V

= 1.25 V setting) but gets into the CoreGood-window (V

VID

Rising 2.0 2.2 V

Falling 1.8 V

COREFB

Falling –0.3 V

Rising –0.05 V

COREFB

= 1.5 V

CLAMP

= 2.2 V 10 µA

COREFB

COREFB

DACOUT

= V

settles within ± 1% of its steady state value.

= 1.25 V 1 4 mA

DACOUT

COREFB,BAD

= 1.0 V at V

= 1.25 V setting) to the COREFB pin right

VID

COREFB,GOOD

= 1.25 V) right after the moment that

–4–

REV. 0

ADP3422

ABSOLUTE MAXIMUM RATINGS*

PIN CONFIGURATION

Input Supply Voltage (VCC) . . . . . . . . . . . . . . –0.3 V to +7 V

UVLO Input Voltage . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

All Other Inputs/Outputs . . . . . . . . . –0.3 V to (VCC + 0.3 V)

Operating Ambient Temperature Range . . . . . . . 0°C to 85°C

Junction Temperature Range . . . . . . . . . . . . . . . 0°C to 150°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98°C/W

θ

JA

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . 300°C

*This is a stress rating only; operation beyond these limits can cause the device to

be permanently damaged.

ORDERING GUIDE

Temperature Package Package

HYSSET

CPUSET

FSHIFT

DSHIFT

BSHIFT

VID4 (MSB)

VID3

VID2

VID1

VID0 (LSB)

BOM

DSLP

DPRSLP

PWRGD

1

2

3

4

5

6

ADP3422

7

TOP VIEW

(Not to Scale)

8

9

10

11

12

13

14

Model Range Description Option

ADP3422JRU 0°C to 85°C Thin Shrink Small RU-28

Outline (TSSOP)

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the ADP3422 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

28

CS–

CS+

27

REG

26

RAMP

25

VCC

24

23

OUT

GND

22

21

DACOUT

20

COREFB

SS

19

18

SWFB

17

DRVLSD

16

CLAMP

15

SD

WARNING!

ESD SENSITIVE DEVICE

REV. 0

–5–

Loading...

Loading...