Analog Devices ADP3415 b Datasheet

Dual MOSFET Driver

with Bootstrapping

ADP3415

FEATURES

All-in-One Synchronous Buck Driver

One PWM Signal Generates Both Drives

Anticross Conduction Protection Circuitry

Programmable Transition Delay

Zero-Crossing Synchronous Drive Control

Synchronous Override Control

Undervoltage Lockout

Shutdown Quiescent Current <100 A

APPLICATIONS

Mobile Computing CPU Core Power Converters

Multiphase Desktop CPU Supplies

Single-Supply Synchronous Buck Converters

Standard-to-Synchronous Converter Adaptations

GENERAL DESCRIPTION

The ADP3415 is a dual MOSFET driver optimized for driving

two N-channel FETs that are the two switches in the nonisolated

synchronous buck power converter topology. Each driver size is

optimized for performance in notebook PC regulators for CPUs

in the 20 A range. The high-side driver can be bootstrapped atop

the switched node of the buck converter as needed to drive the

upper switch and is designed to accommodate the high voltage

slew rate associated with high performance, high frequency

switching. The ADP3415 features an overlapping protection

circuit (OPC); undervoltage lockout (UVLO) that holds the

switches off until the driver is assured of having sufficient voltage

for proper operation; a programmable transition delay; and a

synchronous drive disable pin. The quiescent current, when the

device is disabled, is less than 100 µA.

The ADP3415 is specified over the extended commercial

temperature range of 0°C to 100°C and is available in a 10-lead

MSOP package.

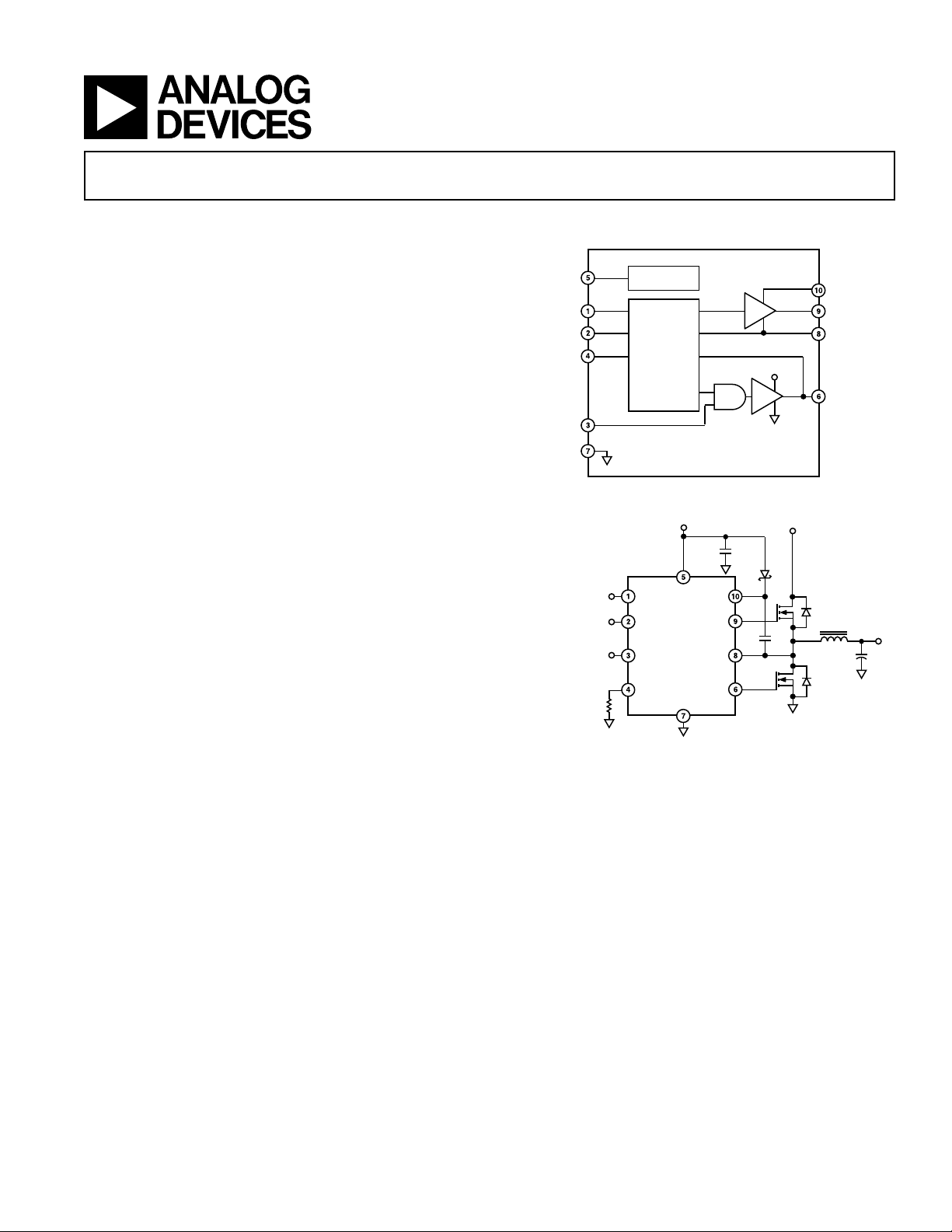

FUNCTIONAL BLOCK DIAGRAM

VCC

IN

SD

DLY

DRVLSD

GND

FROM DUTY RATIO

MODULATOR

FROM SYSTEM

ENABLE CONTROL

FROM SYSTEM

STATE LOGIC

Figure 1. Typical Application Circuit

UVLO

OVERLAP

PROTECTION

CIRCUIT

5V

VCC

IN

SD

ADP3415

DRVLSD

DLY

GND

BST

DRVH

SW

DRVL

ADP3415

VCC

V

DCIN

BST

DRVH

SW

DRVL

V

OUT

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

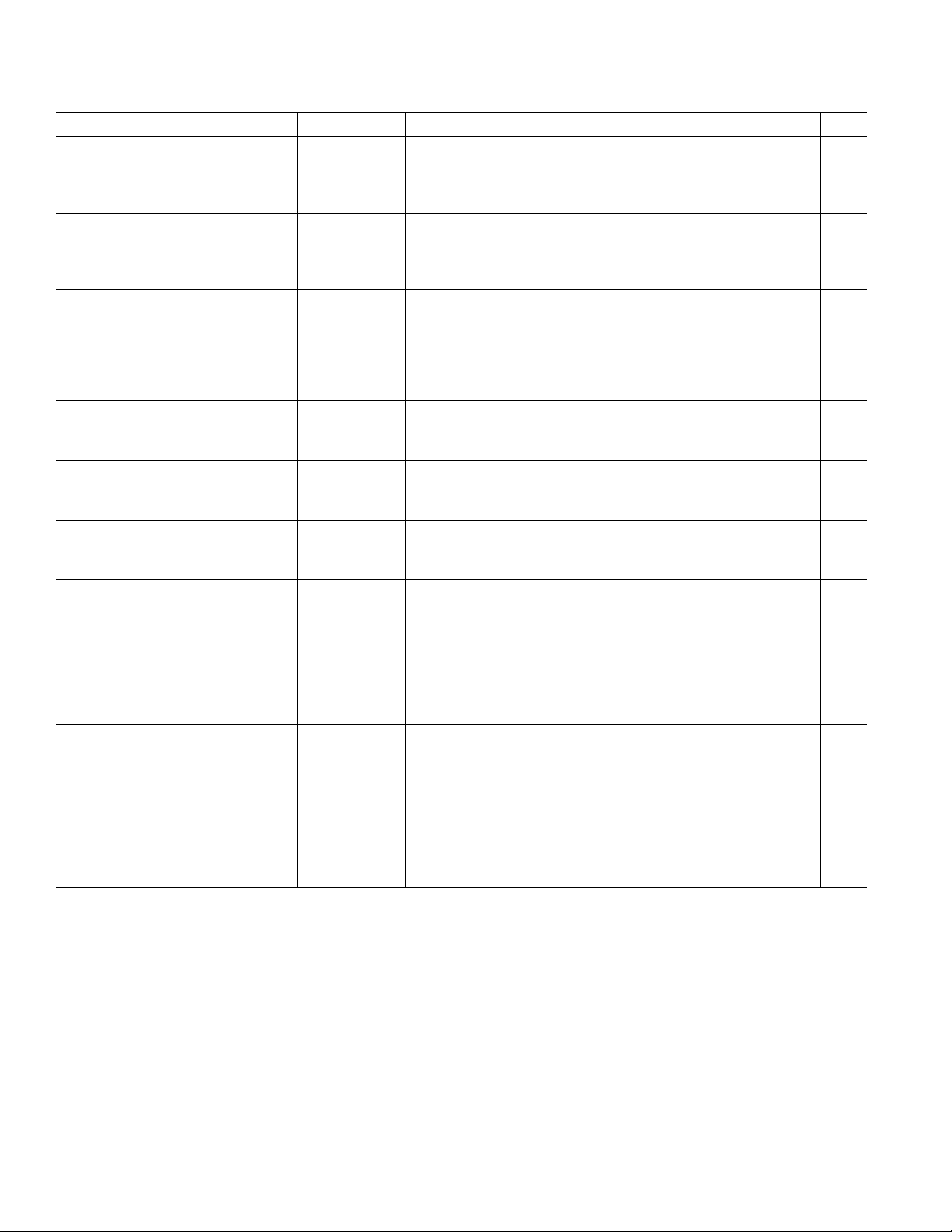

ADP3415–SPECIFICATIONS

(TA = 0ⴗC to 100ⴗC, VCC = 5 V, V

1

unless otherwise noted.)

– VSW = 5 V, SD = 5 V, C

BST

DRVH

= C

DRVL

= 3 nF,

Parameter Symbol Conditions Min Typ Max Unit

SUPPLY (VCC)

Quiescent Current

2

I

CCQ

Shutdown Mode VSD = 0.8 V 30 65 µA

Operating Mode VSD = 5 V, No Switching 1.2 2 mA

UNDERVOLTAGE LOCKOUT

(UVLO)

UVLO Threshold V

UVLO Hysteresis V

CCUVLO

CCHUVLO

3.9 4.15 4.5 V

0.05 V

LOW-SIDE DRIVER SHUTDOWN

(DRVLSD)

Input Voltage High

Input Voltage Low

Propagation Delay

(See Figure 3) tpdh

SHUTDOWN (SD)

Input Voltage High

Input Voltage Low

INPUT (IN)

Input Voltage High

Input Voltage Low

3

3, 4

3

3

3

3

3

V

IH

V

IL

tpdl

V

IH

V

IL

V

IH

V

IL

DRVLSD

DRVLSD

2.0 V

0.8 V

20 50 ns

10 30 ns

2.0 V

0.8 V

2.0 V

0.8 V

THERMAL SHUTDOWN (THSD)

THSD Threshold T

THSD Hysteresis T

SD

HSD

TJ = T

TJ = T

A

A

165 °C

10 °C

HIGH-SIDE DRIVER (DRVH)

Output Resistance, DRVH–BST 1.5 3.5 Ω

Output Resistance, DRVH–SW 0.85 2.0 Ω

DRVH Transition Times

(See Figure 4) tf

DRVH Propagation Delay

(See Figure 4) tpdl

4

4, 5

tr

DRVH

DRVH

tpdh

DRVH

DRVH

V

– VSW = 4.6 V 20 30 ns

BST

25 35 ns

V

– VSW = 4.6 V, V

BST

R

≥ 120 kΩ 100 200 ns

DLY

= 0 V 10 22 40 ns

DLY

40 70 ns

LOW-SIDE DRIVER (DRVL)

Output Resistance, DRVL–VCC 1.6 3.0 Ω

Output Resistance, DRVL–GND 1.0 3.0 Ω

DRVL Transition Times

(See Figure 4) tf

DRVL Propagation Delay

(See Figure 4) tpdl

SW Transition Timeout

Zero-Crossing Threshold V

NOTES

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

Including I

3

The signal source driving the pin must have 70 µA (typ) pull-down strength to make a high-to-low transient, and 20 µA (typ) pull-up strength to make a low-to-high

transient. The pin does not represent load (<100 nA) in static low (<0.8 V) and static high (>2.0 V) logic states (see TPC 3.) The pin can be driven with standard

TTL logic level source.

4

Guaranteed by characterization.

5

For propagation delays, tpdh refers to the specified signal going high, tpdl refers to it going low.

6

Propagation delay measured until DRVL begins its transition.

7

The turn-on of DRVL is initiated after IN goes low by either VSW crossing a ~1.6 V threshold or by expiration of t

Specifications subject to change without notice.

quiescent current.

BSTQ

4

7

4, 5, 6

tr

DRVL

DRVL

tpdh

t

SWTO

ZC

DRVL

DRVL

V

– VSW = 4.6 V 25 40 ns

BST

V

– VSW = 4.6 V 20 30 ns

BST

V

– VSW = 4.6 V 10 30 38 ns

BST

V

– VSW = 4.6 V 10 25 ns

BST

V

– VSW = 4.6 V 130 300 ns

BST

1.6 V

.

SWTO

REV. B–2–

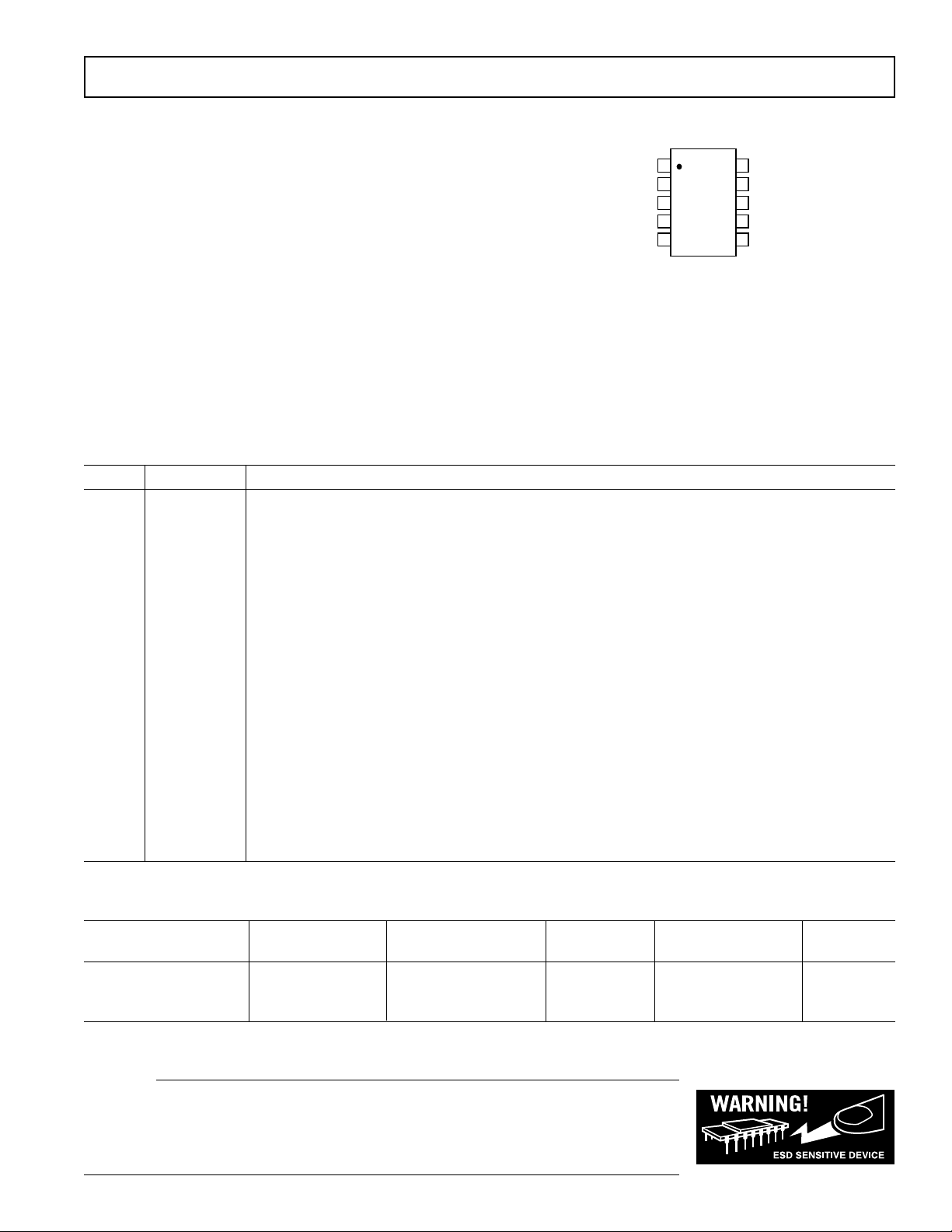

ADP3415

TOP VIEW

(Not to Scale)

10

9

8

7

6

1

2

3

4

5

IN

SD

DRVLSD

DLY

BST

DRVH

SW

GND

ADP3415

VCC

DRVL

ABSOLUTE MAXIMUM RATINGS*

PIN CONFIGURATION

VCC to GND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

BST to GND . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +30 V

BST to SW . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

SW to GND . . . . . . . . . . . . . . . . . . . . . . . . . –2.0 V to +25 V

SD, IN, DRVLSD to GND . . . . . . . . . . . . . . –0.3 V to +7.3 V

Operating Ambient Temperature Range . . . . . . 0°C to 100°C

Operating Junction Temperature Range . . . . . . 0°C to 125°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155°C/W

JA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40°C/W

JC

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . 300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability. Absolute maximum

ratings apply individually only, not in combination. Unless otherwise specified, all

other voltages are referenced to GND.

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1IN TTL-Level Input Signal. Has primary control of the drive outputs.

2 SD Shutdown. When high, this pin enables normal operation. When low, DRVH and DRVL are forced low

and the supply current (I

) is minimized as specified.

CCQ

3 DRVLSD Drive-Low Shutdown. When DRVLSD is low, DRVL is kept low. When DRVLSD is high, DRVL is

enabled and controlled by IN and by the adaptive OPC function.

4 DLY High-Side Turn-On Delay. A resistor from this pin to ground programs an extended delay from turn-off

of the lower FET to turn-on of the upper FET.

5 VCC Input Supply. This pin should be bypassed to GND with a ~10 µF ceramic capacitor.

6 DRVL Synchronous Rectifier Drive. Output drive for the lower (synchronous rectifier) FET.

7GND Ground. Should be directly connected to the ground plane, close to the source of the lower FET.

8SWThis pin should be connected to the buck switching node, close to the upper FET’s source. It is the

floating return for the upper FET drive signal. Also, it is used to monitor the switched voltage for the

OPC function.

9 DRVH Buck Drive. Output drive for the upper (buck) FET.

10 BST Floating Bootstrap Supply for the Upper FET. A capacitor connected between BST and SW pins holds

this bootstrapped supply voltage for the high-side FET driver as it is switched. The capacitor should be

an MLC type and should have substantially greater capacitance (e.g., ~ 20×) than the input capacitance

of the upper FET.

ORDERING GUIDE

Temperature Package Package Quantity

Model Guide Description Option per Reel Branding

ADP3415LRM-REEL 0°C to 100°C MSOP RM-10 3,000 P1E

ADP3415LRM-REEL7 0°C to 100°C MSOP RM-10 1,000 P1E

ADP3415LRMZ-REEL* 0°C to 100°C MSOP RM-10 3,000 P1E

*Z = Pb-free part.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

ADP3415 features proprietary ESD protection circuitry, permanent damage may occur on devices

–3–

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. B

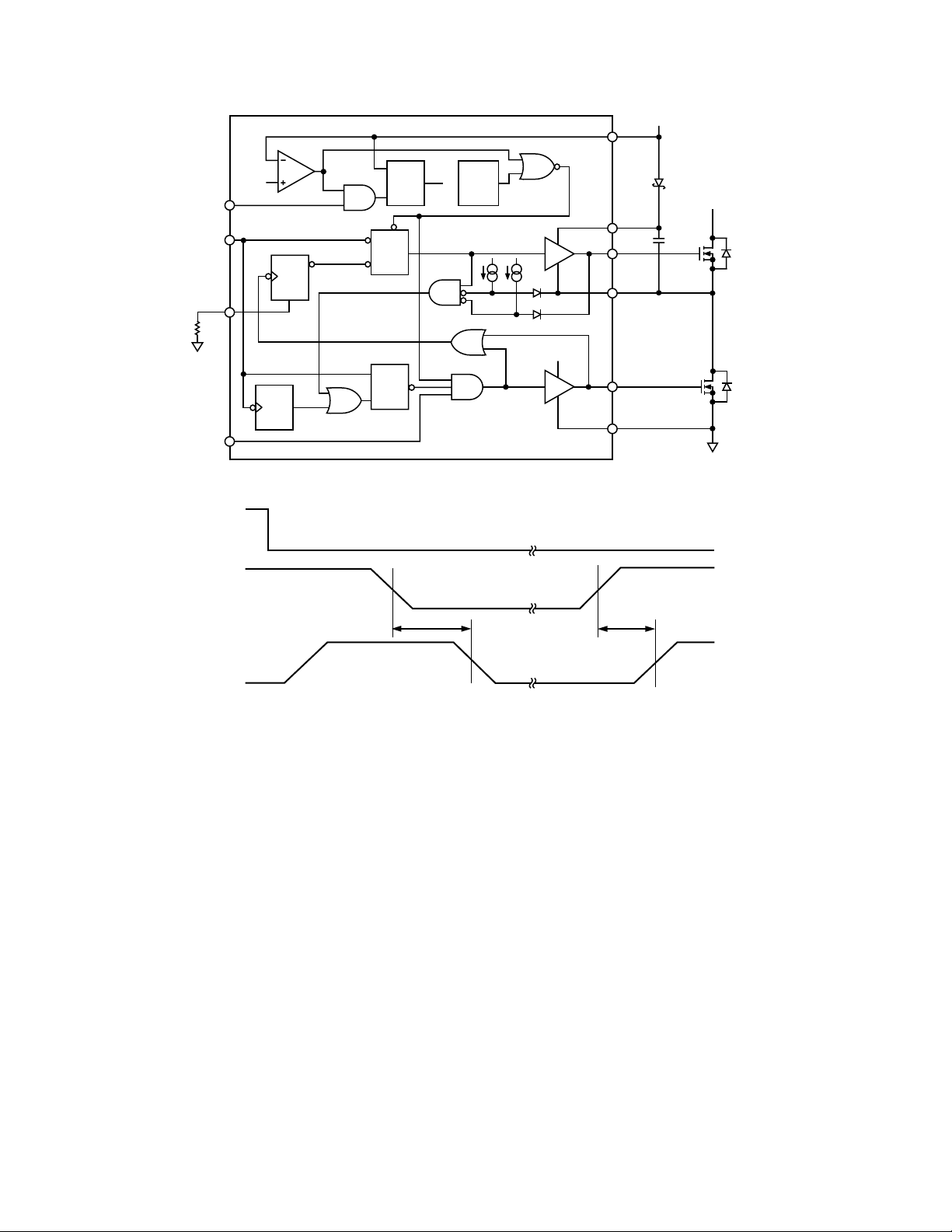

ADP3415

D

R

DLY

DRVLSD

SD

DLY

VCC

VCC

UVLO

V

UVLOTH

IN

DRVH

T

ON

DLY

SET

DRVL

T

ON

DLY

R

S

R

S

EN

CLR

BIAS

Q

Q

BIAS

THERM

SD

THSD

VCC

VTOK

BST

DRVH

SW

DRVL

GND

D

BST

V

DCIN

+

C

BST

Q1

Q2

ADP3415

Figure 2. Functional Block Diagram

IN

RVLSD

DRVL

Figure 3.

DRVLSD

tpdl

DRVLSD

Propagation Delay

tpdh

DRVLSD

REV. B–4–

Loading...

Loading...