Analog Devices ADP3413 a Datasheet

Dual Bootstrapped MOSFET Driver

a

FEATURES

All-In-One Synchronous Buck Driver

Bootstrapped High Side Drive

One PWM Signal Generates Both Drives

Anticross-Conduction Protection Circuitry

Pulse-by-Pulse Disable Control

APPLICATIONS

Multiphase Desktop CPU Supplies

Mobile Computing CPU Core Power Converters

Single-Supply Synchronous Buck Converters

Standard-to-Synchronous Converter Adaptations

GENERAL DESCRIPTION

The ADP3413 is a dual MOSFET driver optimized for driving

two N-channel MOSFETs which are the two switches in a

nonisolated synchronous buck power converter. Each of the

drivers is capable of driving a 3000 pF load with a 20 ns propagation delay and a 30 ns transition time. One of the drivers can

be bootstrapped and is designed to handle the high voltage

slew rate associated with “floating” high side gate drivers.

The ADP3413 includes overlapping drive protection (ODP)

to prevent shoot-through current in the external MOSFETs.

The OD Pin provides high speed control to quickly turn off

both gate drives.

The ADP3413 is specified over the commercial temperature

range of 0°C to 70°C and is available in an 8-lead SOIC package.

ADP3413

VCC

with Output Disable

ADP3413

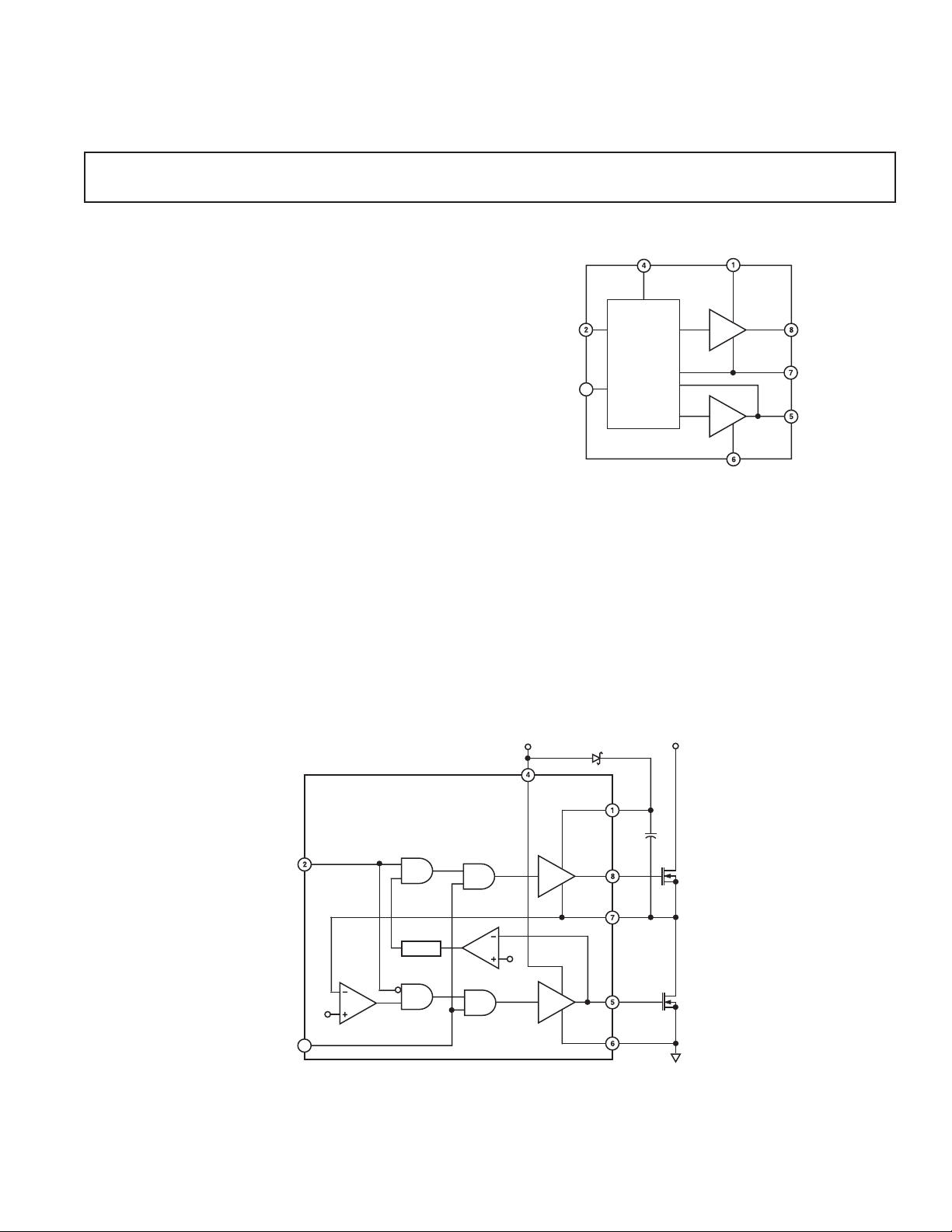

FUNCTIONAL BLOCK DIAGRAM

VCC

IN

OVERLAP

PROTECTION

CIRCUIT

3

OD

ADP3413

7V

D1

BST

12V

BST

DRVH

SW

DRVL

PGND

IN

DELAY

1V

3

OD

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

Figure 1. General Application Circuit

C

BST

DRVH

SW

+1V

DRVL

PGND

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

Q1

Q2

1

ADP3413–SPECIFICATIONS

Parameter Symbol Conditions Min Typ Max Unit

SUPPLY

Supply Voltage Range VCC 4.15 7.5 V

Quiescent Current ICC

OD INPUT

Input Voltage High

Input Voltage Low

2

2

Propagation Delay Time tpdl

PWM INPUT

Input Voltage High

Input Voltage Low

2

2

HIGH SIDE DRIVER

Output Resistance, Sourcing Current V

Output Resistance, Sinking Current V

Transition Times

Propagation Delay

3

(See Figure 2) tr

3, 4

(See Figure 2) tpdh

LOW SIDE DRIVER

Output Resistance, Sourcing Current VCC = 5 V 3.0 5.0 Ω

Output Resistance, Sinking Current VCC = 5 V 1.5 3.0 Ω

3

Transition Times

Propagation Delay

NOTES

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

Logic inputs meet typical CMOS I/O conditions for source/sink current (~1 µA).

3

AC specifications are guaranteed by characterization but not production tested.

4

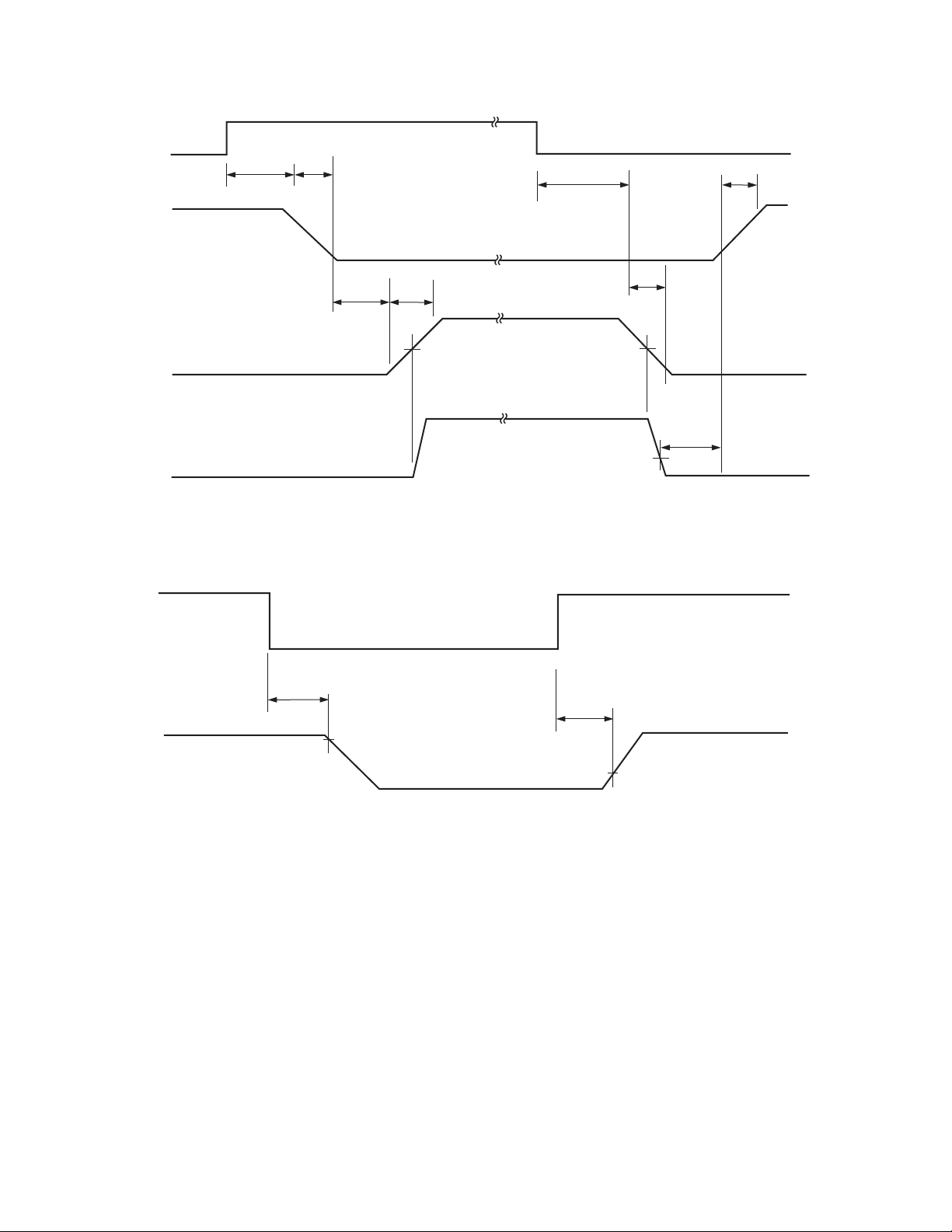

For propagation delays, “tpdh” refers to the specified signal going high; “tpdl” refers to it going low.

Specifications subject to change without notice.

(See Figure 2) tr

3, 4

(See Figure 2) tpdh

tpdh

DRVH

tf

DRVH

tpdl

DRVL

tf

DRVL

tpdl

Q

OD

OD

DRVH

DRVH

DRVL

DRVL

(TA = 0ⴗC to 70ⴗC, VCC = 7 V, BST = 4 V to 26 V, OD > 2 V, unless otherwise noted.)

12 mA

2.0 V

0.8 V

15 30 ns

15 30 ns

2.3 V

0.8 V

– VSW = 5 V 3.0 5.0 Ω

BST

V

– VSW = 7 V 2.0 3.5 Ω

BST

– VSW = 5 V 1.25 2.5 Ω

BST

– VSW = 7 V 1.0 2.5 Ω

V

BST

V

– VSW = 7 V, C

BST

V

– VSW = 7 V, C

BST

V

– V

BST

BST

– V

SW

SW

V

= 7 V 65 86 ns

= 7 V 22 32 ns

= 3 nF 36 47 ns

LOAD

= 3 nF 20 30 ns

LOAD

VCC = 7 V 2.0 3.5 Ω

VCC = 7 V 1.0 2.5 Ω

VCC = 7 V, C

VCC = 7 V, C

= 3 nF 27 35 ns

LOAD

= 3 nF 19 26 ns

LOAD

VCC = 7 V 30 35 ns

VCC = 7 V 17 25 ns

–2–

REV. A

ADP3413

ABSOLUTE MAXIMUM RATINGS*

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +8 V

BST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +30 V

BST to SW . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +8 V

SW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –5.0 V to +25 V

OD, IN . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to VCC + 0.3 V

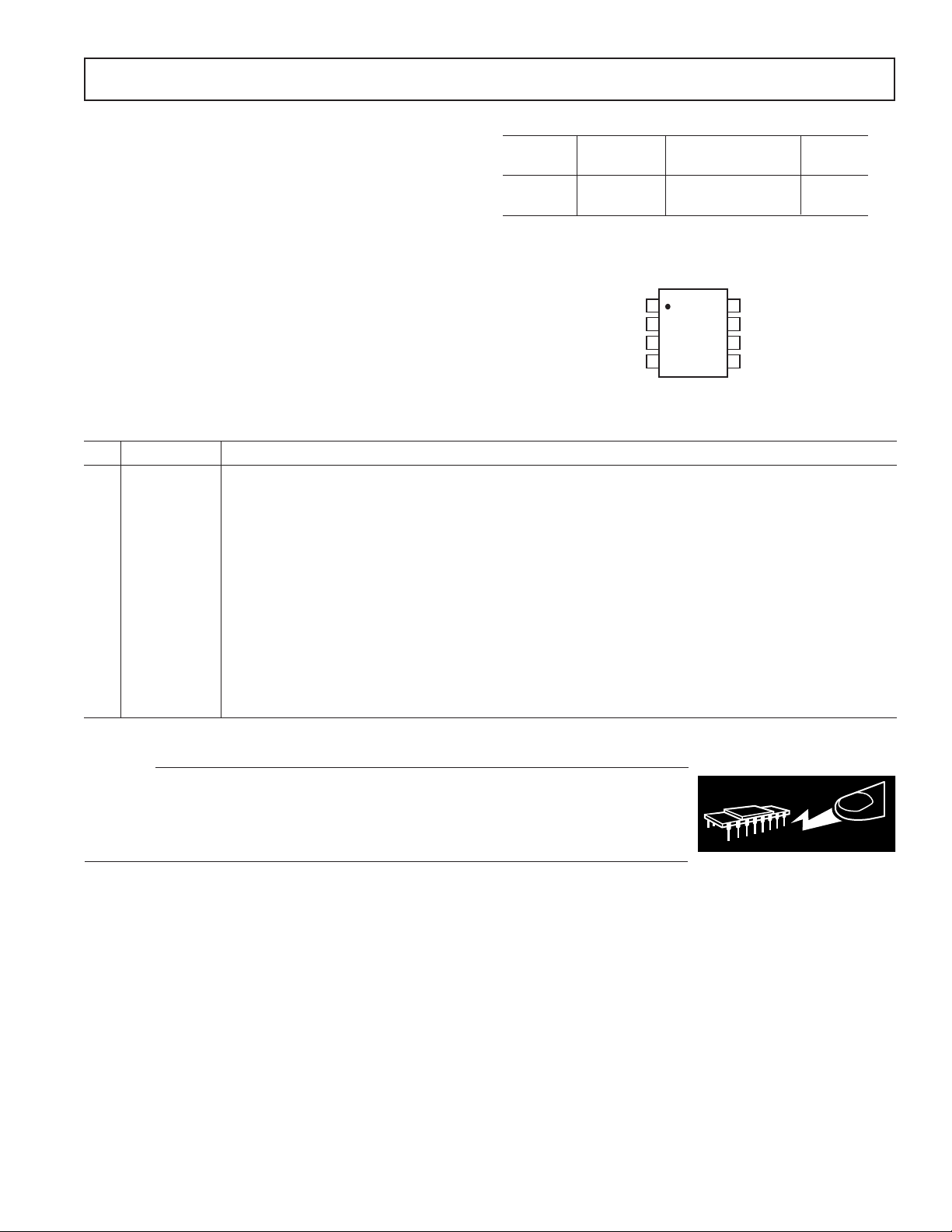

Model Range Description Option

ADP3413JR 0°C to 70°C8-Lead Standard SOIC-8

ORDERING GUIDE

Temperature Package Package

Small Outline (SOIC)

Operating Ambient Temperature Range . . . . . . . 0°C to 70°C

Operating Junction Temperature Range . . . . . . 0°C to 125°C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155°C/W

θ

JA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40°C/W

θ

JC

PIN CONFIGURATION

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . 300°C

*This is a stress rating only; operation beyond these limits can cause the device to

be permanently damaged. Unless otherwise specified, all voltages are referenced

to PGND.

BST

OD

VCC

IN

2

ADP3413

3

TOP VIEW

(Not To Scale)

4

8

7

6

5

DRVH

SW

PGND

DRVL

1

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1 BST Floating Bootstrap Supply for the Upper MOSFET. A capacitor connected between BST and SW Pins

holds this bootstrapped voltage for the high side MOSFET as it is switched. The capacitor should be

chosen between 100 nF and 1 F.

2IN TTL-level input signal that has primary control of the drive outputs.

3 OD Output Disable. When low, this pin disables normal operation, forcing DRVH and DRVL low.

4 VCC Input Supply. This pin should be bypassed to PGND with ~1 µF ceramic capacitor.

5 DRVL Synchronous Rectifier Drive. Output drive for the lower (synchronous rectifier) MOSFET.

6 PGND Power Ground. Should be closely connected to the source of the lower MOSFET.

7SW This pin is connected to the buck-switching node, close to the upper MOSFET’s source. It is the floating

return for the upper MOSFET drive signal. It is also used to monitor the switched voltage to prevent turnon of the lower MOSFET until the voltage is below ~1 V. Thus, according to operating conditions, the

high low transition delay is determined at this pin.

8 DRVH Buck Drive. Output drive for the upper (buck) MOSFET.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the ADP3413 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

WARNING!

ESD SENSITIVE DEVICE

ADP3413

DRVL

IN

DRVL

tf

DRVL

tpdh

DRVHtrDRVH

tpdl

DRVH

tf

DRVH

tr

DRVL

tpdl

DRVH-SW

SW

V

TH

V

TH

tpdh

DRVL

1V

Figure 2. Nonoverlap Timing Diagram (Timing Is Referenced to the 90% and 10% Points Unless Otherwise Noted)

OD

tpdl

DRVH

OR

DRVL

OD

90%

tpdh

OD

10%

Figure 3. Output Disable Timing Diagram

–4–

REV. A

Loading...

Loading...