Analog Devices ADP3203JRU-1.0-RL7, ADP3203JRU-1.0-RL, ADP3203JRU-0.85-RL Datasheet

PRELIMINARY TECHNICAL DATA

2-Phase IMVP-II & IMVP-III

a

Core Controller for Mobile CPUs

Preliminary Technical Data ADP3203

FEATURES

Pin Selectable 1 or 2-Phase Operation

Backward Compatible to IMVP-II

Excellent Static and Dynamic Current Sharing

Superior Load Transient Response with ADOPT

TM

Optimal Positioning Technology

Noise-Blanking for Speed and Stability

Synchronous Rectifier Control for Extended Battery

Life

Cycle-by-Cycle Current Limiting

Hiccup or Latched Overload Protection

Transient-Glitch-Free Power Good

Soft Start Eliminates Power-On In-Rush Current Surge

Two-Level Over-Voltage and Reverse-Voltage

Protection

APPLICATIONS

IMVP II-III Core DC/DC Converters

Fixed Voltage Mobile CPU Core DC/DC Converters

Notebook/Laptop Power Supplies

Programmable Output Power Supplies

GENERAL DESCRIPTION

The ADP3203

is a 1 or 2-phase hysteretic peak current

DC-DC buck converter controller dedicated to power a

mobile processor's core. The optimized low voltage design is

powered from the 3.3 V system supply and draws only

10 µA maximum in shutdown. The nominal output voltage

is set by a 5-bit VID code. To accommodate the transition

time required by the newest processors for on-the-fly VID

changes, the ADP3203 features high-speed operation to

allow a minimized inductor size that results in the fastest

change of current to the output. To further allow for the

minimum number of output capacitors to be used, the

ADP3203 features active voltage positioning with ADOPT

TM

optimal compensation to ensure a superior load transient

response. The output signal interfaces with the ADP3415

MOSFET driver that is optimized for high speed and high

efficiency for driving both the top and bottom MOSFETs of

the buck converter. The ADP3203 is capable of controlling

the synchronous rectifier to extend battery lifetime in light

load conditions.

HYSSET

DSHIFT

BSHIFT

PWRGD

DPRSLP

DSLP

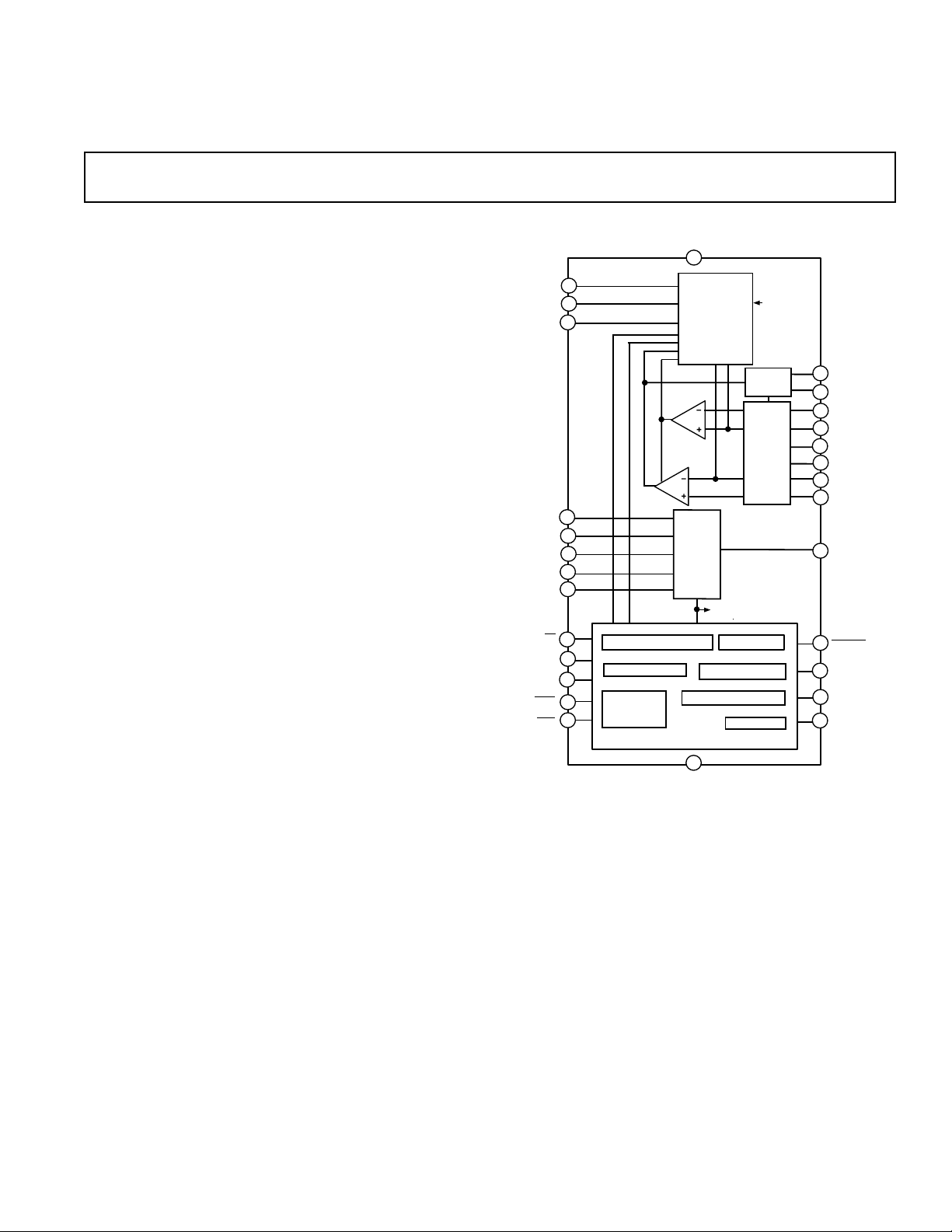

FUNCTIONAL BLOCK DIAGRAM

VCC

24

HYSTERESIS

SHIFT-MUX

CLIM

EN

CORE

5-BIT VID

DAC

&

FIXED

REF

SS-HICCUP TIMER & OCP

PM MODULE

19

GND

SETTING

&

VR

SR CONTROL

COREGD MONITOR

VID4

VID3

VID2

VID1

VID0

SD

BOM

ADP3203

1

2

3

4

5

6

7

8

BOM

13

ENABLE _UVLO MAIN BIAS

12

PWRGD BLANKER

11

10

9

VID MUX &

SELECTOR

DSLP

SHIFT

VR

PHASE

SPLITER

CURRENT

SENSE

MUX

OVP & RVP

21

20

23

22

27

28

25

26

18

15

17

16

14

OUT2

OUT1

CS2

CS1

CS+

CSRAMP

REG

DACOUT

DRVLSD

COREFB

SS

CLAMP

REV. PrD 1/02

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A.

Tel:781/329-4700 www.analog.com

Fax:781/326-8703 ©ANALOG DEVICES, INC., 2002

PRELIMINARY TECHNICAL DATA

= =

( TA

= 25 °C, High (H) = VCC, Low (L) = 0 V, VCC = 3.3 V, SD = H, V

= =

1

ADP3203–SPECIFICATIONS

V

(≡

V

DAC

DACOUT

CSS = 47 nF, R

), V

PWRGD

= V

REG

= 680

= V

CS–

VID

ΩΩ

Ω to 1.2 V, R

ΩΩ

= 1.25 V, R

CLAMP

= 100 k

OUT

= 5.1 k

ΩΩ

Ω, C

ΩΩ

ΩΩ

Ω to VCC, HYSSET, BSHIFT,

ΩΩ

OUT

= 10 pF,

DSHIFT are open, BOM = H, DSLP = H, DPRSLP = L, unless otherwise noted) Current sunk by a pin has a positive sign, sourced by a pin has a

negative sign. Negative sign is disregarded for min and max values.

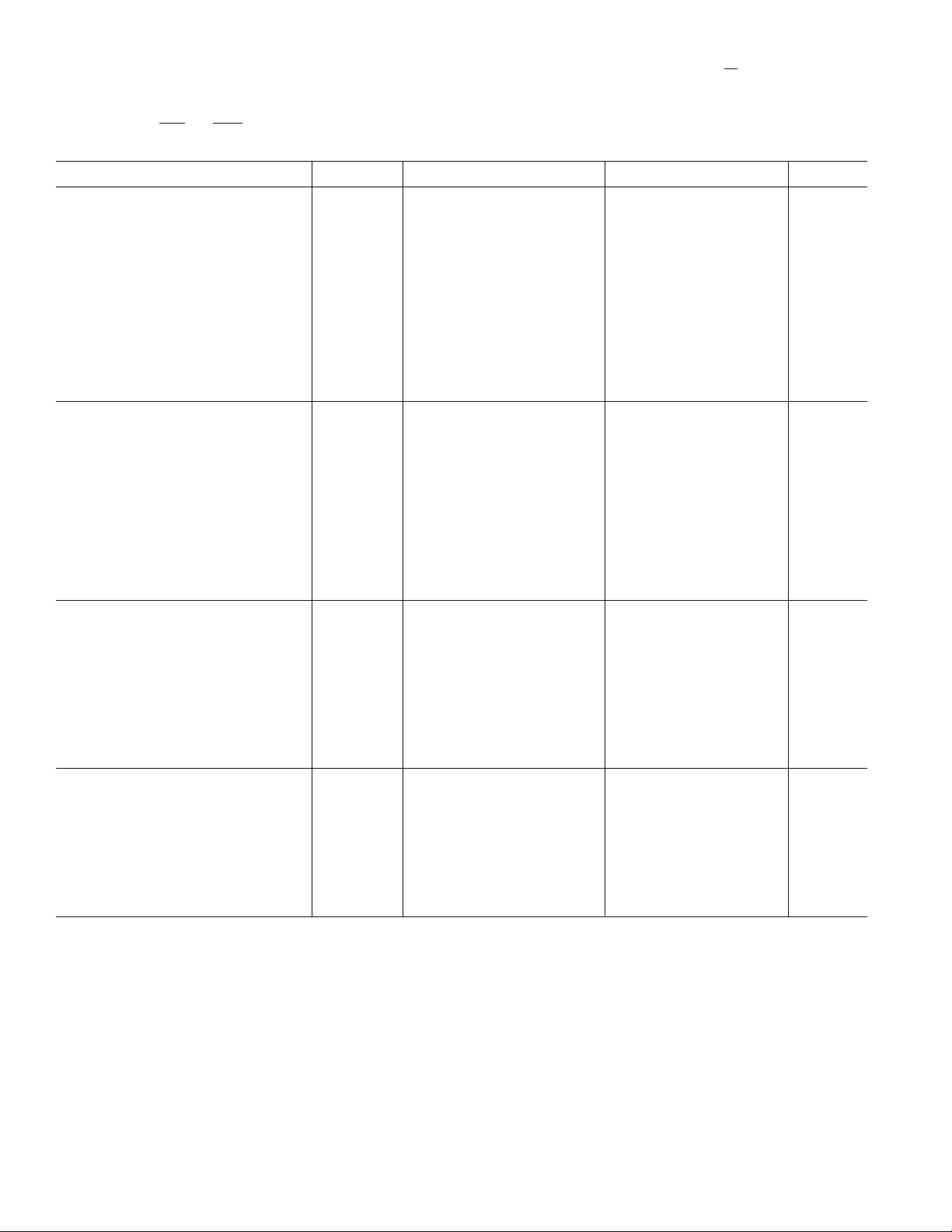

Parameter Symbol Conditions Min Typ Max Units

SUPPLY-UVLO-SHUTDOWN

Normal Supply Current I

UVLO Supply Current I

Shutdown Supply Current I

CC

CCUVLO

CCSD

SD = L, 3.0 V

≤≤

≤ VCC

≤≤

≤≤

≤ 3.6 V 10 µA

≤≤

715 mA

425 µA

UVLO Threshold SD = H

VCC ramping up, VSS= 0 V 2.9 V

VCC ramping down, 2.65 V

V

floating

SS

50 mV

UVLO Hysteresis V

V

CCH

V

CCL

CCHYS

COREFB

=

Shutdown Threshold (CMOS Input) V

SDTH

VCC/2 V

POWERGOOD-CORE FEEDBACK

Core Feedback Threshold Voltage V

Power Good Output Voltage V

COREFBH

PWRGD

(open drain output) V

Masking Time

2

t

PWRGD,MSK

6

0.9 V < V

V

COREFB

V

COREFB

V

COREFB

V

COREFB

V

COREFB

COREFB

VCC =

< 1.675 V

DAC

ramping up 1.12 V

ramping down 1.10 V

ramping up 0.88 V

ramping down 0.86 V

= V

DACOUT

= 0.8 V

DACOUT

0.95 V

0 0.8 V

DAC

DAC

DAC

DAC

CC

1.14 V

1.12 V

0.90 V

0.88 V

V

CC

DAC

DAC

DAC

DAC

V

V

V

V

V

3.3 V 100 µs

SOFT-START/HICCUP TIMER

Charge/Discharge Current

I

SS

Soft-Start Enable/Hiccup

Termination Threshold V

V

SSENDWN

V

Soft-Start Termination/Hiccup V

SSENUP

SSTERM

Enable Threshold

VSS = 0 V

= 0.5 V 0.5 µA

V

SS

V

= 1.25 V,

REG

= V

RAMP

VSS ramping down 80 200 mV

7

VSS ramping up 150 mV

V

= V

RAMP

COREFB

COREFB

= 1.27 V

= 1.27 V

–

16 µA

VSS ramping up 1.75 2.00 2.25 V

VID DAC

VID Input Threshold (CMOS Inputs) V

VID Input Current I

VID0..4

VID0..4

VID 0..4 = L 90 µA

VCC/2 V

(Internal Active Pull-up)

Output Voltage V

Accuracy ∆V

Settling Time

Notes:

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

Guaranteed by characterization.

3

Measured from 50% of VID code transition amplitude to the point where V

4

40 mVPP amplitude impulse with 20 mV overdrive. Measured from the input threshold intercept point to 50% of the output voltage swing.

5

Measured between the 30% and 70% points of the output voltage swing.

6

Two test conditions: 1)PWRGD is OK but forced to fail by applying an out-of-the-CoreGood-window voltage (V

the COREFB pin right after the moment that BOM or DPRSLP is asserted/de-asserted. PWRGD should not fail immediately only with the specified blanking

delay time. 2) PWRGD is forced to fail (V

(V

COREFB,GOOD

blanking delay time.

7

Guaranteed by design.

2

= 1.25 V) right after the moment that BOM or DPRSLP is asserted/de-asserted. PWRGD should not go high immediately only with the specified

COREFB,BAD

DAC

DAC/VDAC

3

t

DACS

= 1.0 V at V

See VID Code Table 1 0.600 1.750 V

0.850 V < V

0.600 V < V

∆V

= 0.5 V, C

DAC

DACOUT

= 1.25 V setting) but gets into the CoreGood-window

VID

< 1.750 V –1.0 +1.0 %

DAC

< 0.825 V –8.5 +8.5 mV

DAC

settles within ±1% of its steady state value.

= 10 nF 3.5 µs

DAC

= 1.0 V at V

COREFB,BAD

VID

= 1.25 V setting) to

–2–

REV. PrD

PRELIMINARY TECHNICAL DATA

ADP3203

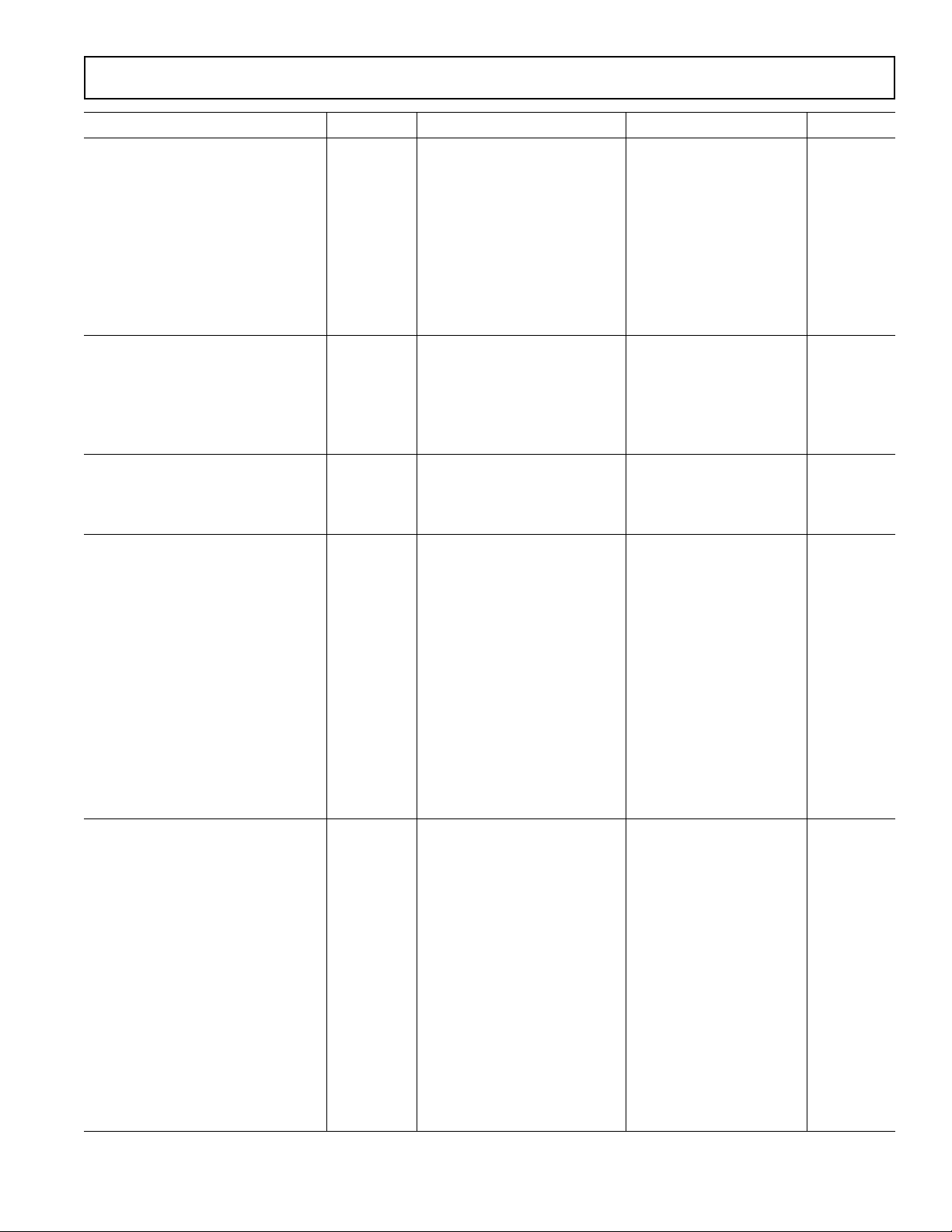

Parameter Symbol Conditions Min Typ Max Unit

CORE COMPARATOR

V

Input Offset Voltage (Ramp-Reg) V

Input Bias Current I

Output Voltage (OUT1,OUT2) V

Propagation Delay Time

Rise and Fall Time

Noise Blanking Time

2

2

2

CURRENT LIMIT

COMPARATOR

Input Offset Voltage V

Input Bias Current I

Propagation Delay Time

2

CURRENT SENSE MULTIPLEXER

Trans-Resistance R

Common Mode Voltage Range

7

HYSTERESIS SETTING

Hysteresis Current I

COREOS

, I

REG

RAMP

OUT_H

V

OUT_L

t

RMPOUT_PD

t

OUT_R

t

OUT_F

t

BLNK

CS+

t

CLPD

CS1-CS+

R

CS2-CS+

V

CS1

RAMP_H

-I

CSP_H

4

5

5

CLIMOS

, I

CS-

4

, Switch is ON 150 Ω

= V

CS2

, V

= 1.25 V ±1.5 mV

REG

V

REG

= V

= 1.25 V ±1 µA

RAMP

VCC = 3.0 V 2.5 3.0 V

VCC = 3.6 V 0 0.8 V

TA = 25°C 30 ns

T

= Full Range 40 ns

A

710ns

710ns

OUT L-H Transition 80 ns

OUT H-L Transition 120 ns

V

= 1.25 V ±4 ±6 mV

CS-

V

= 1.25 V

CS+

–5 –

3

µA

TA = 25° C 30 60 ns

TA = Full Range

50 100 ns

Switch is OFF 100 MΩ

02V

= 1.25 V

REG

V

= 1.23 V,BOM=H

RAMP

I

= 10 µA –8 –10 –12 µA

HYSSET

= 100 µA –80 –100 –120 µA

I

HYSSET

V

= 1.27 V, BOM = H

RAMP

I

= 10 µΑ 81012 µΑ

HYSSET

= 100 µΑ 80 100 120 µΑ

I

HYSSET

V

= 1.23 V, BOM = L

RAMP

I

= 10 µΑ –6.4 –8 –9.6 µΑ

HYSSET

= 100 µΑ –64 –80 –96 µΑ

I

HYSSET

V

= 1.27 V, BOM = L

RAMP

I

= 10 µΑ 64 8 96 µΑ

HYSSET

= 100 µΑ 64 80 96 µA

I

HYSSET

Hysteresis Reference Voltage V

CURRENT LIMIT SETTING

Hysteresis Current I

REV. PrD

HYSSET

CS–

V

= 1.23 V

RAMP

V

= V

=

REG

V

= 1.23 V BOM = H

CS+

I

HYSSET

I

HYSSET

V

= 1.27 V, BOM = H

CS+

I

HYSSET

I

HYSSET

V

= 1.23 V, BOM = L

CS+

I

HYSSET

I

HYSSET

V

= 1.27 V, BOM = L

CS+

I

HYSSET

I

HYSSET

V

CS–

= 10 µΑ

= 100 µΑ

= 10 µΑ

= 100 µΑ

= 10 µΑ

= 100 µΑ

= 10 µΑ

= 100 µΑ

–3–

COREFB

1.53 1.7 1.87 V

= 1.25 V

–27 –31.5 –36 µA

–268 –301.5 –335 µA

–18 –21.5 –25 µA

–178 –201.5 –225 µA

–21 –25.5 –30 µA

–212 –241.5 –271 µA

–14 –17.5 –21 µA

–140 –161.5 –183 µA

PRELIMINARY TECHNICAL DATA

1

ADP3203–SPECIFICATIONS

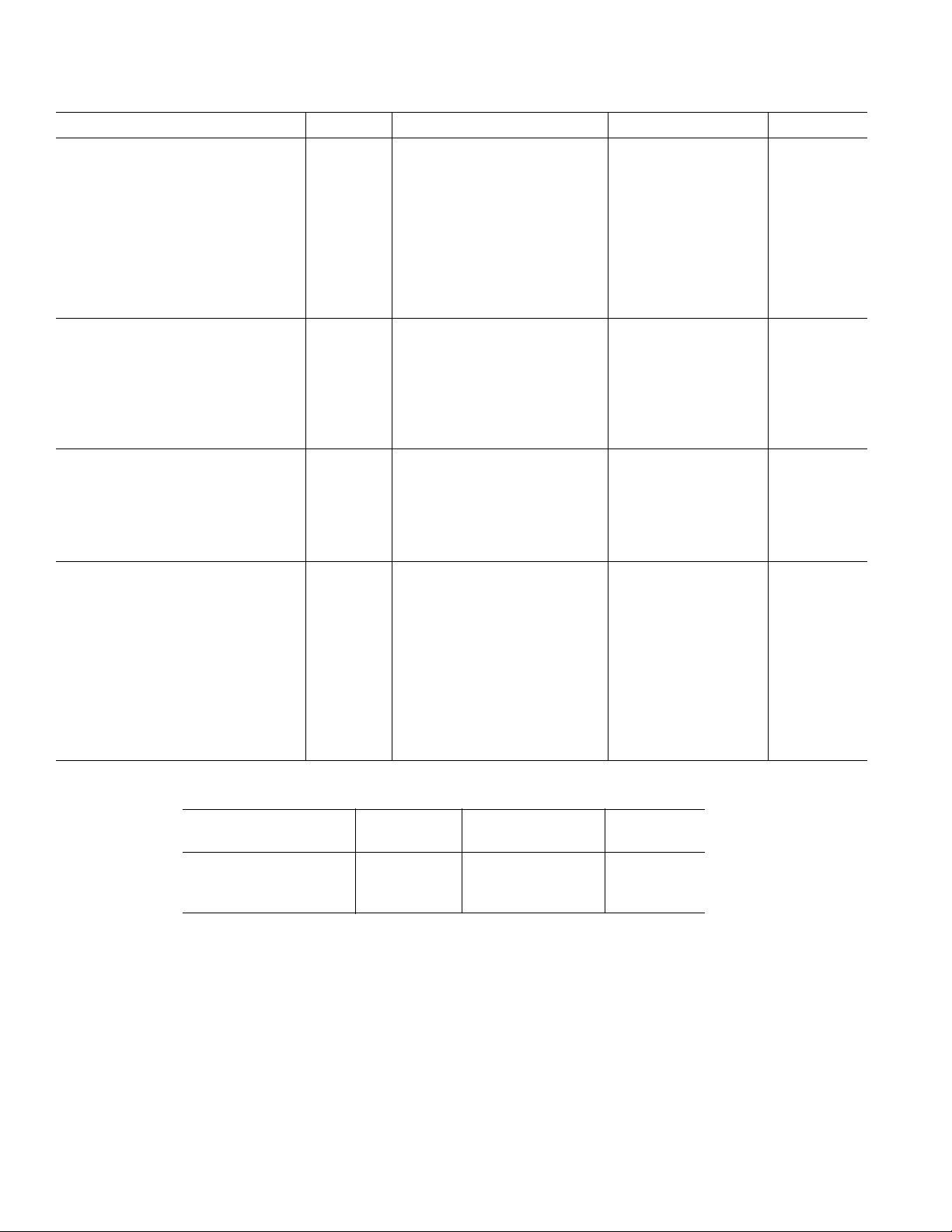

Parameter Symbol Conditions Min Typ Max Units

SHIFT SETTING

V

Battery-Shift Current I

Battery-Shift Reference Voltage V

DeepSleep-Shift Current I

DeepSleep-Shift Reference Voltage V

SHIFT CONTROL INPUTS

BOM Threshold V

(CMOS Input)

DSLP Threshold V

-Level CMOS Input)

(V

TT

DPRSLP Mode Threshold V

(CMOS Input)

LOW-SIDE DRIVE CONTROL

Output Voltage (CMOS Output) V

Output Current I

RAMPB,ICS+B

BSHIFT

RAMPD,ICS+D

DSHIFT

BOM

DSLP

DPRSLP

DRVLSD

DRVLSD

= 1.25 V –90 –100 –110 µA

VID

= 12.5 k, BOM = L

R

BSHIFT

DSLP = H

V

DAC

V

= 1.25 V –90 –100 –110 µA

VID

R

= 12.5 k, BOM = H

DSHIFT

V

DSLP = L

V

DAC

V

VCC/2 V

0.9 V

VCC/2 V

DPRSLP = H 0 0.4 V

DPRSLP = L 0.7 V

V

= 1.5 V

DRVLSD

DPRSLP = L 0.5 mA

CC

V

CC

V

DPRSLP = H –0.5 mA

OVER/REVERSE VOLTAGE

PROTECTION-CORE FEEDBACK

Over-Voltage Threshold V

Reverse-Voltage Threshold V

Output Voltage (Open Drain Output) V

Output Current I

COREFB,OVPVCOREFB

COREFB,OVPVCOREFB

CLAMP

CLAMP

rising 2.0 V

falling 1.95 V

V

COREFB

falling –0.3 V

rising –0.1 V

V

COREFB

V

= 1.5 V, V

CLAMP

= V

V

COREFB

V

= 2.2 V 1 4 mA

COREFB

ORDERING GUIDE

DPRSLP Temperature Package

Model Voltage Range Option

ADP3203JRU-0.85-RL 0.85 V 0°C to 100°C TSSOP-28

ADP3203JRU-1.0-RL 1 V 0°C to 100°C TSSOP-28

ADP3203JRU-1.0-RL7 1 V 0°C to 100°C TSSOP-28

ABSOLUTE MAXIMUM RATINGS*

Input Supply Voltage (VCC) ............................. -0.3 V to +7 V

UVLO Input Voltage ......................................... -0.3 V to +7 V

All Other Inputs/Outputs ..................................... VCC + 0.3 V

Operating Ambient Temperature Range ........... 0°C to +100°C

Junction Temperature Range ............................ 0°C to +150°C

............................................................................... 98°C/W

θ

JA

Storage Temperature Range ............................ -65°C to 150°C

Lead Temperature (Soldering, 10 sec.) ........................ +300°C

*This is a stress rating only; operation beyond these limits can cause the device

to be permanently damaged.

DAC

= 1.25 V

VID

0.7 V

CC

V

CC

V

10 µA

–4–

REV. PrD

Loading...

Loading...