Analog Devices ADP3188 Datasheet

6-Bit Programmable 2-/3-/4-Phase

FEATURES

Selectable 2-, 3- or 4-phase operation at up to

1 MHz per phase

±9.5 mV worst-case differential sensing error over

temperature

Logic-level PWM outputs for interface to external

high power drivers

Active current balancing between all output phases

Built-in power good/crowbar blanking supports on-the-fly

VID code changes

6-bit digitally programmable 0.8375 V to 1.6 V output

Programmable short-circuit protection with

programmable latch-off delay

APPLICATIONS

Desktop PC power supplies for

Next-generation Intel processors

VRM modules

GENERAL DESCRIPTION

The ADP3188 is a highly efficient multiphase synchronous buck

switching regulator controller optimized for converting a 12 V

main supply into the core supply voltage required by high performance Intel® processors. It uses an internal 6-bit DAC to read

a voltage identification (VID) code directly from the processor,

which is used to set the output voltage between 0.8375 V and

1.6 V. It uses a multimode PWM architecture to drive the logiclevel outputs at a programmable switching frequency that can

be optimized for VR size and efficiency. The phase relationship

of the output signals can be programmed to provide 2-, 3-, or

4-phase operation, allowing the construction of up to four

complementary buck switching stages.

Synchronous Buck Controller

ADP3188

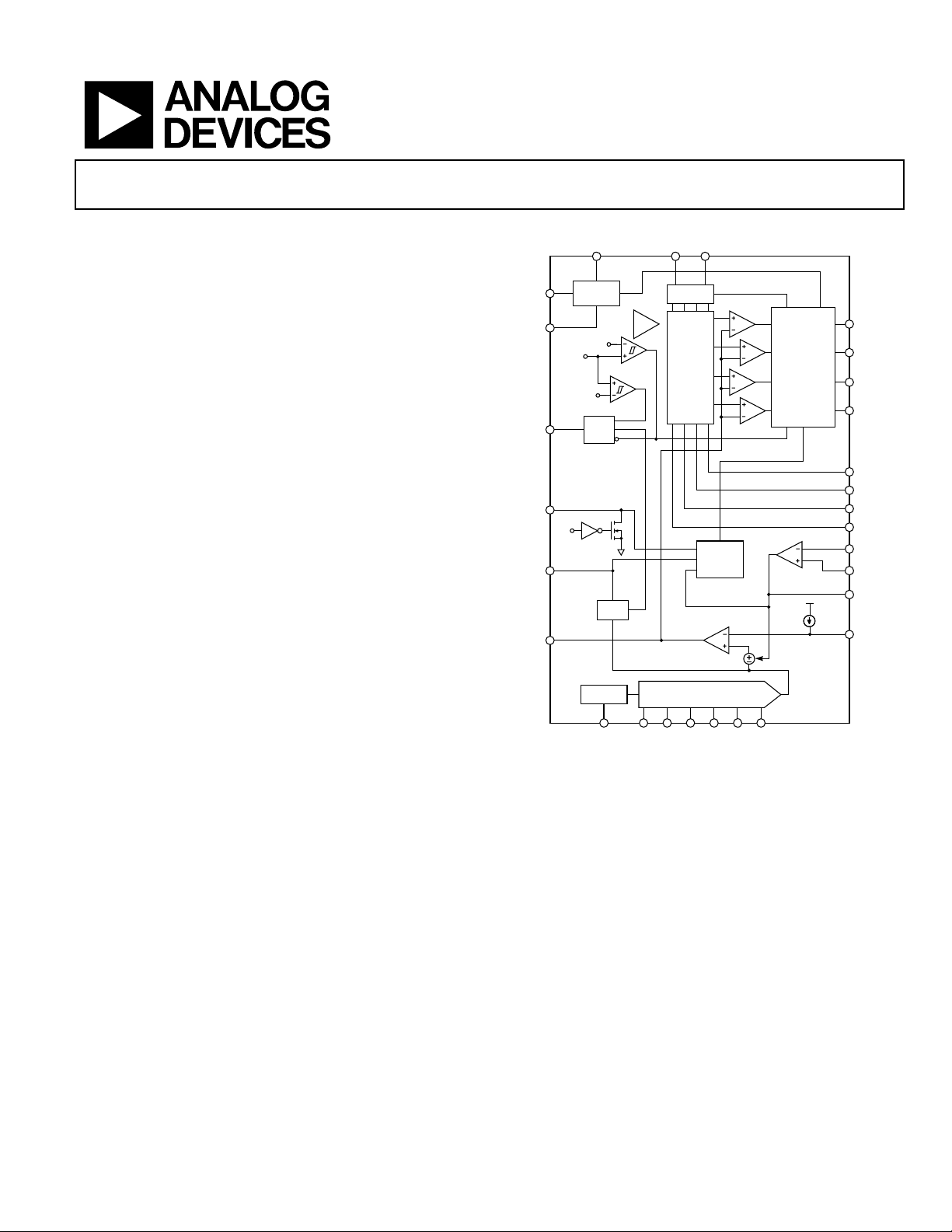

FUNCTIONAL BLOCK DIAGRAM

GND

PWRGD

ILIMIT

DELAY

COMP

EN

ADP3188

11

19

DAC+150mV

CSREF

DAC-250mV

10

15

EN

12

9

VCC

28

UVLO

SHUTDOWN

AND BIAS

DELAY

START

PRECISION

REFERENCE

7

FBRTN

SOFT

VID41VID32VID23VID1

RAMPADJ

14

OSCILLATOR

CURRENT

BALANCING

CIRCUIT

RT

13

CURRENT

LIMIT

CIRCUIT

VID

DAC

4

Figure 1.

RESET

CMP

RESET

CMP

2-/3-/4-PHASE

DRIVER LOGIC

RESET

CMP

RESET

CMP

CROWBAR CURRENT

6

5

VID5

VID0

LIMIT

ENSET

27

26

25

24

23

22

21

20

17

16

18

8

PWM1

PWM2

PWM3

PWM4

SW1

SW2

SW3

SW4

CSSUM

CSREF

CSCOMP

FB

04835-0-001

The ADP3188 also includes programmable no-load offset and

slope functions to adjust the output voltage as a function of the

load current so that it is always optimally positioned for a system

transient. The ADP3188 also provides accurate and reliable

short-circuit protection, adjustable current limiting, and a delayed

power good output that accommodates on-the-fly output voltage

changes requested by the CPU.

The ADP3188 is specified over the commercial temperature

range of 0°C to 85°C and is available in a 28-lead TSSOP package.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

ADP3188

TABLE OF CONTENTS

Specifications..................................................................................... 3

Inductor Selection...................................................................... 15

Test Circuits....................................................................................... 5

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Function Description .............................. 7

Typical Performance Characteristics ............................................. 8

Theory of Operation ........................................................................ 9

Start-Up Sequence........................................................................ 9

Master Clock Frequency.............................................................. 9

Output Voltage Differential Sensing .......................................... 9

Output Current Sensing .............................................................. 9

Active Impedance Control Mode............................................. 10

Current Control Mode and Thermal Balance ........................10

Voltage Control Mode................................................................ 10

Soft Start ...................................................................................... 10

Current Limit, Short-Circuit, and Latch-Off Protection....... 11

Designing an Inductor............................................................... 16

Selecting a Standard Inductor .............................................. 16

Output Droop Resistance.......................................................... 16

Inductor DCR Temperature Correction ................................. 17

Output Offset.............................................................................. 17

C

Selection ............................................................................. 18

OUT

Power MOSFETs......................................................................... 18

Ramp Resistor Selection............................................................ 20

COMP Pin Ramp ....................................................................... 20

Current Limit Setpoint.............................................................. 20

Feedback Loop Compensation Design.................................... 20

C

Selection and Input Current di/dt Reduction.................. 22

IN

Tuning the ADP3188 ................................................................. 22

DC Loadline Setting .............................................................. 22

AC Loadline Setting............................................................... 23

Dynamic VID.............................................................................. 11

Power Good Monitoring ...........................................................12

Output Crowbar ......................................................................... 13

Output Enable and UVLO ........................................................ 13

Application Information................................................................ 15

Setting the Clock Frequency ..................................................... 15

Soft Start and Current Limit Latch-Off Delay Times........... 15

REVISION HISTORY

Revision 0: Initial Version

Initial Transient Setting......................................................... 23

Layout and Component Placement ......................................... 24

General Recommendations .................................................. 24

Power Circuitry Recommendations.................................... 24

Signal Circuitry Recommendations .................................... 24

Outline Dimensions....................................................................... 25

Ordering Guide .......................................................................... 25

Rev. 0 | Page 2 of 28

ADP3188

SPECIFICATIONS

VCC = 12 V, FBRTN = GND, TA = 0°C to 85°C, unless otherwise noted.1

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

ERROR AMPLIFIER

Output Voltage Range2 V

Accuracy VFB

Line Regulation

Input Bias Current IFB 14 15.5 17

FBRTN Current I

Output Current I

Gain Bandwidth Product GBW

Slew Rate C

VID INPUTS

Input Low Voltage V

Input High Voltage V

Input Current, Input Voltage Low I

Input Current, Input Voltage High I

Pull-Up Resistance R

Internal Pull-Up Voltage 0.9 1.1 V

VID Transition Delay Time2 VID code change to FB change 400 ns

No CPU Detection Turn-Off Delay

Time

2

OSCILLATOR

Frequency Range2 f

Frequency Variation f

Output Voltage VRT

RAMPADJ Output Voltage V

RAMPADJ Input Current Range I

CURRENT SENSE AMPLIFIER

Offset Voltage V

Input Bias Current I

Gain Bandwidth Product GBW

Slew Rate C

Input Common-Mode Range CSSUM and CSREF 0 2.7 V

Positioning Accuracy

Output Voltage Range 0.05 2.7 V

Output Current I

CURRENT BALANCE CIRCUIT

Common-Mode Range V

Input Resistance R

Input Current I

Input Current Matching

0.7 3.1 V

COMP

Relative to nominal DAC output,

−9.5 +9.5 mV

referenced to FBRTN,

CSSUM = CSCOMP, Figure 2

∆V

FB

VCC = 10 V to 14 V 0.05 %

µA

100 140

FBRTN

O(ERR)

(ERR)

IL(VID)

IH(VID)

VID(X) = 0 V −25 −35

IL(VID)

VID(X) = 1.25 V 5 15

IH(VID)

35 60 85

VID

FB forced to V

COMP = FB 20 MHz

= 10 pF 25

COMP

0.4 V

0.8 V

VID code change to 11111 to PWM

– 3% 500

OUT

400 ns

µA

µA

V/µs

µA

µA

kΩ

going low

0.25 4 MHz

OSC

PHASE

RAMPADJ

0 100

RAMPADJ

CSSUM – CSREF, Figure 3 −1.75 +1.75 mV

OS(CSA)

= 25°C, RT = 250 kΩ, 4-phase

T

A

= 25°C, RT = 115 kΩ, 4-phase

T

A

= 25°C, RT = 75 kΩ, 4-phase

T

A

= 100 kΩ to GND

R

T

RAMPADJ – FB −50 +50 mV

= 25°C to 85°C, CSSUM – CSREF,

T

A

155 200 245 kHz

400 kHz

600 kHz

1.9 2.0 2.1 V

µA

−1.5 +1.5 mV

Figure 3

BIAS(CSSUM)

∆V

CSCOMP

SW(X)

∆I

−50 +50 nA

10 MHz

(CSA)

= 10 pF 10

CSCOMP

FB

Figure 4 −77 −80 −83 mV

500

SW(X)CM

SW(X)

−600 +200 mV

SW(X) = 0 V 20 30 40

SW(X) = 0 V 4 7 10

SW(X)

SW(X) = 0 V −5 +5 %

V/µs

µA

kΩ

µA

Rev. 0 | Page 3 of 28

ADP3188

Parameter Symbol Conditions Min Typ Max Units

CURRENT LIMIT COMPARATOR

Output Voltage

Normal Mode V

Shutdown Mode V

Output Current, Normal Mode I

ILIMIT(NM)

ILIMIT(SD)

ILIMIT(NM)

Maximum Output Current2 60

Current Limit Threshold Voltage VCL

Current Limite Setting Ratio VCL/I

DELAY Normal Mode Voltage V

DELAY Overcurrent Threshold V

Latch-Off Delay Time t

DELAY(NM)

DELAY(OC)

DELAY

SOFT START

Output Current, Soft-Start Mode I

Soft-Start Delay Time t

DELAY(SS)

DELAY(SS)

ENABLE INPUT

Input Low Voltage V

Input High Voltage V

Input Current, Input Voltage Low I

Input Current, Input Voltage High I

0.4 V

IL(EN)

0.8 V

IH(EN)

EN = 0 V −1 +1

IL(EN)

EN = 1.25 V 10 25

IH(EN)

POWER GOOD COMPARATOR

Undervoltage Threshold V

Overvoltage Threshold V

Output Low Voltage V

PWRGD(UV)

PWRGD(OV)

OL(PWRGD)

Power Good Delay Time

During Soft Start

2

VID Code Changing 100 250

VID Code Static 200 ns

Crowbar Trip Point V

CROWBAR

Crowbar Reset Point Relative to FBRTN 450 550 650 mV

Crowbar Delay Time t

CROWBAR

VID Code Changing 100 250

VID Code Static 400 ns

PWM OUTPUTS

Output Low Voltage V

Output High Voltage V

OL(PWM)

OH(PWM)

SUPPLY

DC Supply Current 5 10 mA

UVLO Threshold Voltage V

VCC rising 6.5 6.9 7.3 V

UVLO

UVLO Hysteresis 0.7 0.9 1.1 V

1

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

2

Guaranteed by design or bench characterization, not tested in production.

2.9 3 3.1 V

400 mV

12

µA

EN > 0.8 V, R

EN < 0.4 V, I

EN > 0.8 V, R

= 250 kΩ

ILIMIT

= -100 µA

ILIMIT

= 250 kΩ

ILIMIT

µA

– V

V

CSREF

ILIMIT

R

= 250 kΩ

DELAY

R

R

DELAY

DELAY

= 250 kΩ

= 250 kΩ, C

, R

CSCOMP

= 250 kΩ

ILIMIT

10.4

= 12 nF

DELAY

During startup, DELAY < 2.4 V 15 20 25

R

DELAY

= 250 kΩ, C

DELAY

= 12 nF,

105 125 145 mV

mV/µA

2.9 3 3.1 V

1.7 1.8 1.9 V

1.5 ms

µA

1 ms

VID code = 011111

µA

µA

Relative to nominal DAC output −180 −250 −300 mV

Relative to nominal DAC output 90 150 200 mV

I

PWRGD(SINK)

R

= 4 mA 225 400 mV

= 250 kΩ, C

DELAY

DELAY

= 12 nF,

1 ms

VID code = 011111

µs

Relative to nominal DAC output 90 150 200 mV

Overvoltage to PWM going low

µs

I

PWM(SINK)

I

PWM(SOURCE)

= −400 µA

= 400 µA

160 500 mV

4.0 5 V

Rev. 0 | Page 4 of 28

ADP3188

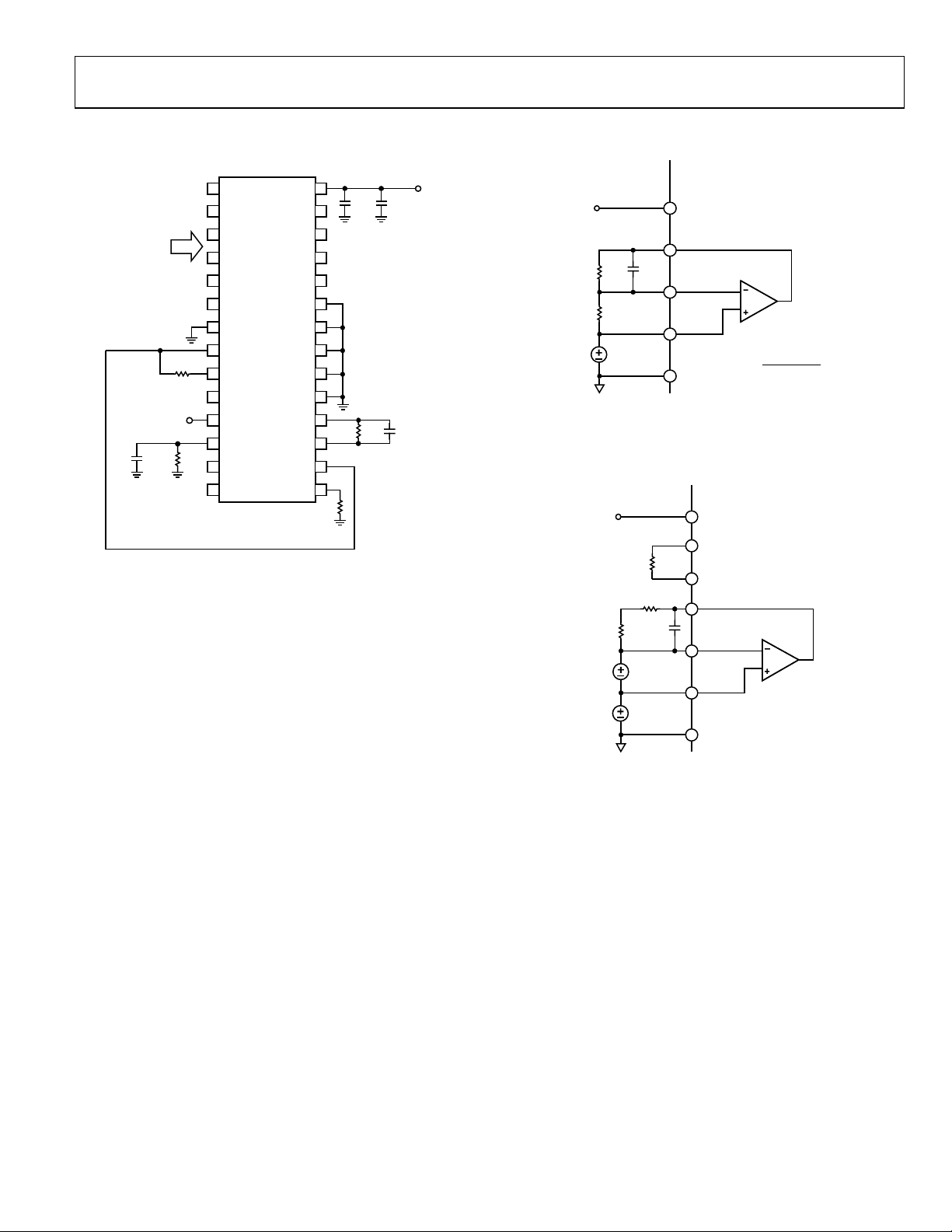

TEST CIRCUITS

6-BIT CODE

12nF

ADP3188

1.25V

250kΩ

1kΩ

1

VID4

2

VID3

3

VID2

4

VID1

5

VID0

6

VID5

7

FBRTN

8

FB

9

COMP

10

PWRGD

11

EN

12

DELAY

13

RT

14

RAMPADJ

VCC

PWM1

PWM2

PWM3

PWM4

SW1

SW2

SW3

SW4

GND

CSCOMP

CSSUM

CSREF

ILIMIT

28

27

26

25

24

23

22

21

20

19

18

17

16

15

250kΩ

+

1µF 100n F

20kΩ

Figure 2. Closed-Loop Output Voltage Accuracy

100nF

12V

04835-0-005

12V

39kΩ

1kΩ

1.0V

Figure 3. Current Sense Amplifier V

12V

10kΩ

200kΩ

200kΩ

∆V

1.0V

100nF

100nF

ADP3188

VCC

28

CSCOMP

18

CSSUM

17

CSREF

16

GND

19

VCC

28

8

9

CSCOMP

18

CSSUM

17

CSREF

16

GND

19

VOS =

ADP3188

FB

COMP

CSCOMP – 1V

40

OS

04835-0-006

∆VFB= FB

∆V = 80mV

– FB

∆V = 0mV

04835-0-007

Figure 4. Positioning Voltage

Rev. 0 | Page 5 of 28

ADP3188

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VCC −0.3 V to +15 V

FBRTN −0.3 V to +0.3 V

VID0 – VID5, EN, DELAY, ILIMIT, CSCOMP,

RT, PWM1 – PWM4, COMP

SW1 – SW4 −5 V to +25 V

All Other Inputs and Outputs −0.3 V to VCC + 0.3 V

Storage Temperature −65°C to +150°C

Operating Ambient Temperature Range 0°C to 85°C

Operating Junction Temperature 125°C

Thermal Impedance (θJA)

Lead Temperature

Soldering (10 sec) 300°C

Infrared (15 sec) 260°C

−0.3 V to 5.5 V

100°C/W

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability. Absolute maximum ratings apply individually

only, not in combination. Unless otherwise specified all other

voltages re referenced to GND.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 6 of 28

ADP3188

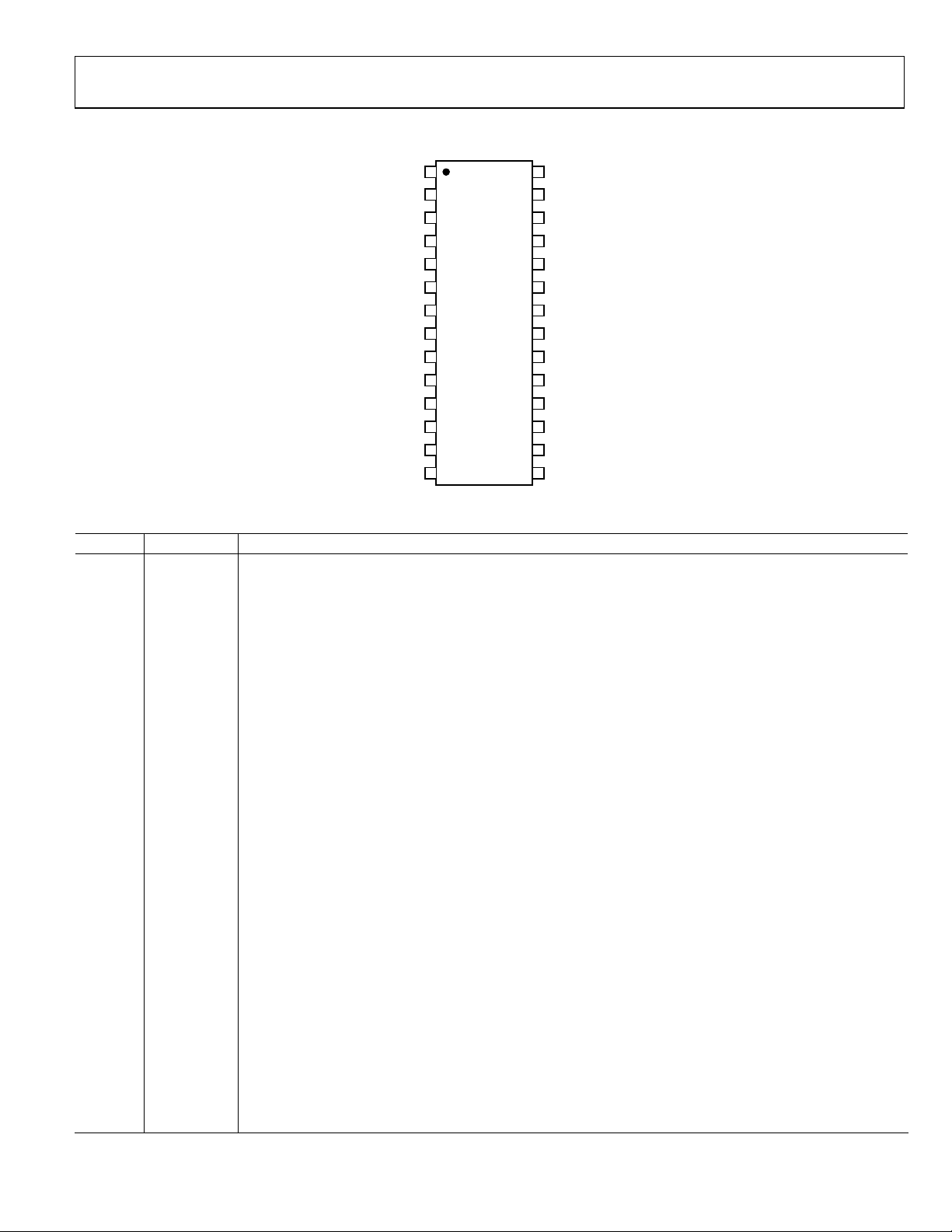

PIN CONFIGURATION AND FUNCTION DESCRIPTION

1

VID4

2

VID3

3

VID2

4

VID1

5

VID0

ADP3188

6

VID5

FBRTN

FB

COMP

PWRGD

EN

DELAY

RT

RAMPADJ

7

8

9

10

11

12

13

14

TOP VIEW

(Not to Scale)

Figure 5. Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 to 6 VID4 to VID0,

VID5

Voltage Identification DAC Inputs. These six pins are pulled up to an internal reference, providing a Logic 1 if left

open. When in normal operation mode, the DAC output programs the FB regulation voltage from 0.8375 V to

1.6 V (see Table 4). Leaving all of the VID pins open results in the ADP3188 going into No CPU mode, shutting off

its PWM outputs and pulling the PWRGD output low.

7 FBRTN Feedback Return. VID DAC and error amplifier reference for remote sensing of the output voltage.

8 FB Feedback Input. Error amplifier input for remote sensing of the output voltage. An external resistor between this

pin and the output voltage sets the no-load offset point.

9 COMP Error Amplifier Output and Compensation Point.

10 PWRGD Power Good Output. Open-drain output that signals when the output voltage is outside the proper operating

range.

11 EN Power Supply Enable Input. Pulling this pin to GND disables the PWM outputs and pulls the PWRGD output low.

12 DELAY Soft-Start Delay and Current Limit Latch-Off Delay Setting Input. An external resistor and capacitor connected

between this pin and GND sets the soft-start ramp-up time and the overcurrent latch-off delay time.

13 RT Frequency Setting Resistor Input. An external resistor connected between this pin and GND sets the oscillator

frequency of the device.

14 RAMPADJ PWM Ramp Current Input. An external resistor from the converter input voltage to this pin sets the internal

PWM ramp.

15 ILIMIT Current Limit Setpoint/Enable Output. An external resistor from this pin to GND sets the current limit threshold

of the converter. This pin is actively pulled low when the ADP3188 EN input is low, or when VCC is below its

UVLO threshold, to signal to the driver IC that the driver high-side and low-side outputs should go low.

16 CSREF Current Sense Reference Voltage Input. The voltage on this pin is used as the reference for the current sense

amplifier and the power good and crowbar functions. This pin should be connected to the common point of the

output inductors.

17 CSSUM Current Sense Summing Node. External resistors from each switch node to this pin sum the average inductor

currents together to measure the total output current.

18 CSCOMP Current Sense Compensation Point. A resistor and a capacitor from this pin to CSSUM determine the slope of the

load line and the positioning loop response time.

19 GND Ground. All internal biasing and the logic output signals of the device are referenced to this ground.

20 to 23 SW4 to SW1 Current Balance Inputs. Inputs for measuring the current level in each phase. The SW pins of unused phases

should be left open.

24 to 27 PWM4 to

PMW1

Logic-Level PWM Outputs. Each output is connected to the input of an external MOSFET driver such as the

ADP3418. Connecting the PWM3 and/or PWM4 outputs to GND causes that phase to turn off, allowing the

ADP3188 to operate as a 2-, 3-, or 4-phase controller.

28 VCC Supply Voltage for the Device.

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VCC

PWM1

PWM2

PWM3

PWM4

SW1

SW2

SW3

SW4

GND

CSCOMP

CSSUM

CSREF

ILIMIT

04835-0-002

Rev. 0 | Page 7 of 28

ADP3188

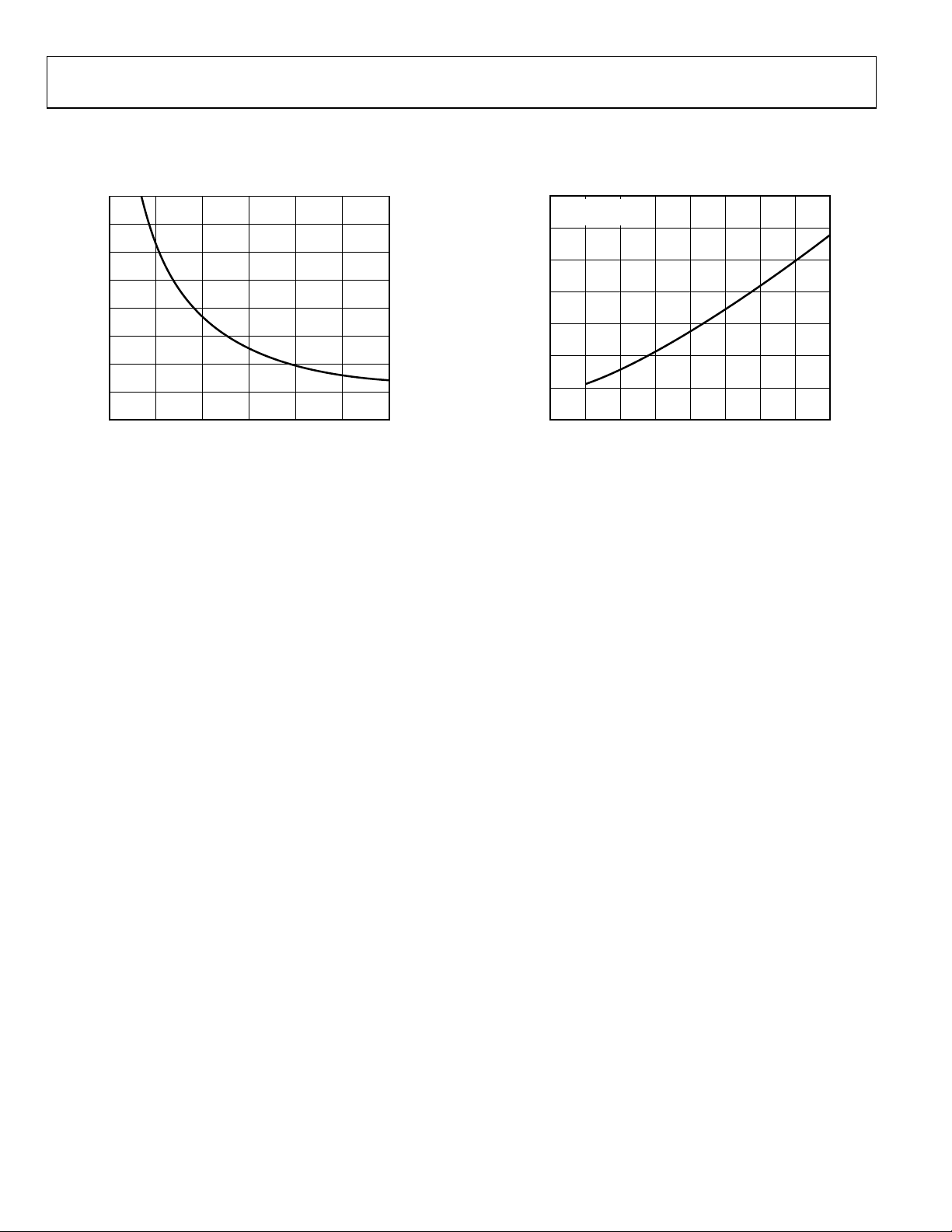

TYPICAL PERFORMANCE CHARACTERISTICS

4

3

2

1

MASTER CLOCK FREQUENCY (MHz)

5.3

TA = 25°C

4-PHASE OPERATION

5.2

5.1

5.0

4.9

4.8

SUPPLY CURRENT (mA)

4.7

0

0 50 100 150 200 250 300

Figure 6. Master Clock Frequency vs. R

RT VALUE (kΩ)

T

04835-0-003

4.6

0 0.5 1 1.5 2 2.5 3 3.5 4

OSCILLATOR FREQUENCY (MHz)

Figure 7. Supply Current vs. Oscillator Frequency

04835-0-004

Rev. 0 | Page 8 of 28

ADP3188

THEORY OF OPERATION

The ADP3188 combines a mulitmode, fixed frequency PWM

control with mulitphase logic outputs for use in 2-, 3- and

4-phase synchronous buck CPU core supply power converters.

The internal VID DAC is designed to interface with the Intel

6-bit VRD/VRM 10 and 10.1 compatible CPUs. Multiphase

operation is important for producing the high currents and low

voltages demanded by today’s microprocessors. Handling the

high currents in a single-phase converter would place high

thermal demands on the components in the system such as the

inductors and MOSFETs.

The multimode control of the ADP3188 ensures a stable, high

performance topology for

• Balancing currents and thermals between phases

• High speed response at the lowest possible switching

frequency and output decoupling

• Minimizing thermal switching losses due to lower

frequency operation

• Tight load line regulation and accuracy

• High current output for up to 4-phase operation

• Reduced output ripple due to multiphase cancellation

• PC board layout noise immunity

• Ease of use and design due to independent component

selection

• Flexibility in operation for tailoring design to low cost or

high performance

START-UP SEQUENCE

During start-up, the number of operational phases and their

phase relationship is determined by the internal circuitry that

monitors the PWM outputs. Normally, the ADP3188 operates as

a 4-phase PWM controller. Grounding the PWM4 pin programs

3-phase operation, and grounding the PWM3 and PWM4 pins

programs 2-phase operation.

When the ADP3188 is enabled, the controller outputs a voltage

on PWM3 and PWM4, which is approximately 675 mV. An

internal comparator checks each pin’s voltage versus a threshold

of 300 mV. If the pin is grounded, it is below the threshold and

the phase is disabled. The output resistance of the PWM pin is

approximately 5 kΩ during this detection time. Any external

pull-down resistance connected to the PWM pin should not be

less than 25 kΩ to ensure proper operation. PWM1 and PWM2

are disabled during the phase detection interval, which occurs

during the first two clock cycles of the internal oscillator. After

this time, if the PWM output is not grounded, the 5 kΩ

resistance is removed. and it switches between 0 V and 5 V. If

the PWM output was grounded, it remains off.

The PWM outputs are logic-level devices intended for driving

external gate drivers such as the ADP3418. Since each phase is

monitored independently, operation approaching 100% duty

cycle is possible. Also, more than one output can be on at the

same time for overlapping phases.

MASTER CLOCK FREQUENCY

The clock frequency of the ADP3188 is set with an external

resistor connected from the RT pin to ground. The frequency

follows the graph in Figure 6. To determine the frequency per

phase, the clock is divided by the number of phases in use. If

PWM4 is grounded, then divide the master clock by 3 for the

frequency of the remaining phases. If PWM3 and 4 are grounded,

then divide by 2. If all phases are in use, divide by 4.

OUTPUT VOLTAGE DIFFERENTIAL SENSING

The ADP3188 combines differential sensing with a high accuracy

VID DAC and reference and a low offset error amplifier. This

maintains a worst-case specification of ±9.5 mV differential

sensing error over its full operating output voltage and temperature range. The output voltage is sensed between the FB and

FBRTN pins. FB should be connected through a resistor to the

regulation point, usually the remote sense pin of the microprocessor. FBRTN should be connected directly to the remote

sense ground point. The internal VID DAC and precision

reference are referenced to FBRTN, which has a minimal

current of 100 µA to allow accurate remote sensing. The internal

error amplifier compares the output of the DAC to the FB pin to

regulate the output voltage.

OUTPUT CURRENT SENSING

The ADP3188 provides a dedicated current sense amplifier

(CSA) to monitor the total output current for proper voltage

positioning versus load current and for current limit detection.

Sensing the load current at the output gives the total average

current being delivered to the load, which is an inherently more

accurate method than peak current detection or sampling the

current across a sense element such as the low-side MOSFET.

This amplifier can be configured several ways depending on the

objectives of the system:

• Output inductor DCR sensing without a thermistor for

lowest cost

• Output inductor DCR sensing with a thermistor for

improved accuracy with tracking of inductor temperature

• Sense resistors for highest accuracy measurements

Rev. 0 | Page 9 of 28

Loading...

Loading...