ANALOG DEVICES ADP3162 Service Manual

查询ADP3162供应商查询ADP3162供应商

5-Bit Programmable 2-Phase

a

FEATURES

ADOPT™ Optimal Positioning Technology for Superior

Load Transient Response and Fewest Output

Capacitors

Complies with VRM 8.5 with Lowest System Cost

Active Current Balancing Between Both Output Phases

5-Bit Digitally Programmable 1.05 V to 1.825 V Output

Dual Logic-Level PWM Outputs for Interface to

External High-Power Drivers

Total Output Accuracy ⴞ0.8% Over Temperature

Current-Mode Operation

Short Circuit Protection

Power Good Output

Overvoltage Protection Crowbar Protects

Microprocessors with No Additional

External Components

APPLICATIONS

Desktop PC Power Supplies for:

Intel Tualatin Processors

VRM Modules

Synchronous Buck Controller

ADP3162

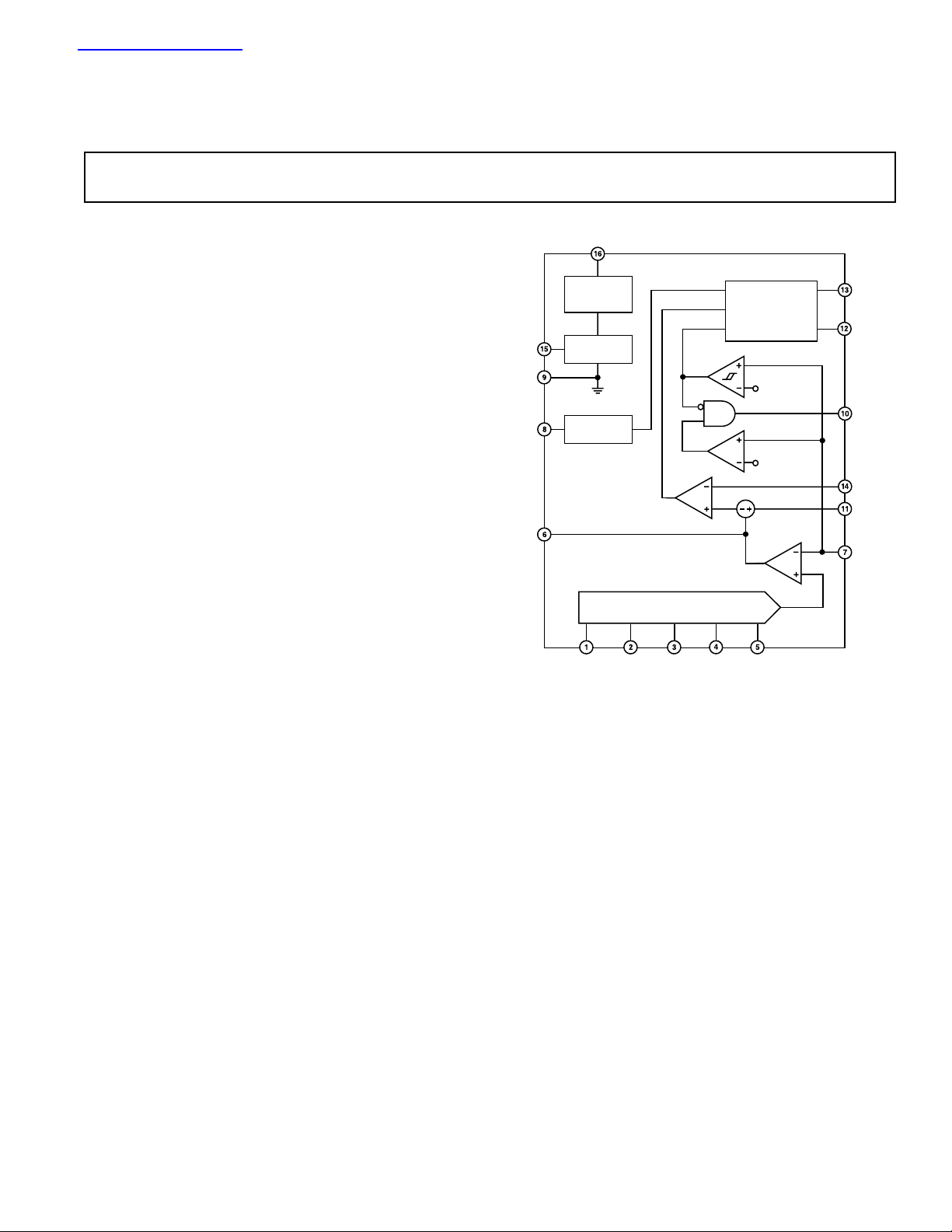

FUNCTIONAL BLOCK DIAGRAM

VCC

CROWBAR

CMP1

RESET

CMP3

CMP2

CMP

SET

CMP

2-PHASE

DRIVER

LOGIC

DAC+24%

DAC–18%

g

m

REF

GND

CT

COMP

UVLO

& BIAS

3.0V

REFERENCE

OSCILLATOR

ADP3162

PWM1

PWM2

PWRGD

CS–

CS+

FB

GENERAL DESCRIPTION

The ADP3162 is a highly efficient dual output synchronous

buck switching regulator controller optimized for converting a

5 V or 12 V main supply into the core supply voltage required by

high-performance processors such as Tualatin. The ADP3162

uses an internal 5-bit DAC to read a voltage identification (VID)

code directly from the processor, which is used to set the output

voltage between 1.05 V and 1.825 V. The ADP3162 uses a

current mode PWM architecture to drive two logic-level outputs

at a programmable switching frequency that can be optimized

for VRM size and efficiency. The output signals are 180 degrees

out of phase, allowing for the construction of two complementary

buck switching stages. These two stages share the dc output

current to reduce overall output voltage ripple. An active current balancing function ensures that both phases carry equal

portions of the total load current, even under large transient

loads, to minimize the size of the inductors.

VID

DAC

VID3 VID2 VID1 VID0 VID25

The ADP3162 also uses a unique supplemental regulation technique called active voltage positioning to enhance load transient

performance. Active voltage positioning results in a dc/dc converter

that meets the stringent output voltage specifications for high

performance processors, with the minimum number of output

capacitors and smallest footprint. Unlike voltage-mode and

standard current-mode architectures, active voltage positioning

adjusts the output voltage as a function of the load current so

that it is always optimally positioned for a system transient. The

ADP3162 also provides accurate and reliable short circuit protection and adjustable current limiting.

The ADP3162 is specified over the commercial temperature

range of 0°C to 70°C and is available in a 16-lead narrow body

SOIC package.

ADOPT is a trademark of Analog Devices, Inc.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

1

ADP3162–SPECIFICATIONS

(VCC = 12 V, I

Parameter Symbol Conditions Min Typ Max Unit

FEEDBACK INPUT

Accuracy V

FB

1.05 V Output Figure 1 1.042 1.050 1.058 V

1.5 V Output Figure 1 1.488 1.500 1.512 V

1.825 V Output Figure 1 1.811 1.825 1.839 V

Line Regulation ∆V

Input Bias Current I

FB

Crowbar Trip Threshold V

FB

CROWBAR

VCC = 10 V to 14 V 0.05 %

Percent of Nominal DAC Voltage 114 124 134 %

Crowbar Reset Threshold Percent of Nominal DAC Voltage 50 60 70 %

Crowbar Response Time t

FB Low Foldback Threshold V

CROWBAR

FB(LOW)

Overvoltage to PWM Going Low 300 ns

REFERENCE

Output Voltage V

Output Current I

REF

REF

0 ≤ I

REF

VID INPUTS

Input Low Voltage V

Input High Voltage V

Input Current I

Pull-Up Resistance R

IL(VID)

IH(VID)

VID

VID

VID(x) = 0 V 280 400 µA

Internal Pull-Up Voltage 2.7 3 3.3 V

OSCILLATOR

Maximum Frequency

Frequency Accuracy f

CT Charge Current I

2

f

CT(MAX)

CT

CT

TA = 25°C, CT = 91 pF 430 500 570 kHz

TA = 25°C, VFB in Regulation 130 150 170 µA

TA = 25°C, VFB = 0 V 26 36 46 µA

ERROR AMPLIFIER

Output Resistance R

Transconductance g

Output Current I

Maximum Output Voltage V

Output Disable Threshold V

–3 dB Bandwidth BW

O(ERR)

m(ERR)

O(ERR)

COMP(MAX)

COMP(OFF)

ERR

FB = 0 V 1 mA

FB Forced to V

COMP = Open 500 kHz

CURRENT SENSE

Threshold Voltage V

CS(TH)

CS+ = VCC, 69 79 89 mV

FB Forced to V

0.8 V ≤ COMP ≤ 1 V 0 15 mV

FB ≤ 375 mV 37 47 58 mV

1 V ≤ V

CS+ = CS– = VCC 0.5 5 µA

CS+ – (CS–) ≥ 89 mV 50 ns

∆V

COMP

/∆V

CS

Input Bias Current I

Response Time t

V

CS(FOLD)

n

i

, I

CS+

CS

CS–

to PWM Going Low

POWER GOOD COMPARATOR

Undervoltage Threshold V

Overvoltage Threshold V

Output Voltage Low V

PWRGD(UV)

PWRGD(OV)

OL(PWRGD)

Percent of Nominal Output 76 82 88 %

Percent of Nominal Output 114 124 134 %

I

PWRGD(SINK)

Response Time 200 ns

PWM OUTPUTS

Output Voltage Low V

Output Voltage High V

Output Current I

Duty Cycle Limit

2

OL(PWM)

OH(PWM)

PWM

DC Per Phase, Relative to f

I

PWM(SINK)

I

PWM(SOURCE)

= 150 A, TA = 0ⴗC to 70ⴗC, unless otherwise noted.)

REF

550 nA

425 500 575 mV

≤ 300 µA 2.952 3.0 3.048 V

300 µA

0.6 V

2.2 V

12 17 kΩ

2000 kHz

200 kΩ

2.0 2.2 2.45 mmho

– 3% 3.0 V

OUT

640 800 880 mV

– 3%

OUT

≤ 3 V 25 V/V

COMP

= 100 µA 30 200 mV

= 400 µA 100 500 mV

= 400 µA 4.5 5.0 5.5 V

0.4 1 mA

CT

50 %

–2–

REV. A

ADP3162

WARNING!

ESD SENSITIVE DEVICE

Parameter Symbol Conditions Min Typ Max Unit

SUPPLY

DC Supply Current

Normal Mode I

UVLO Mode I

UVLO Threshold Voltage V

CC

CC(UVLO)

UVLO

VCC ≤ V

, VCC Rising 220 400 µA

UVLO

UVLO Hysteresis 0.1 0.4 0.6 V

NOTES

1

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2

Guaranteed by design, not tested in production.

Specifications subject to change without notice.

3.8 5.5 mA

5.9 6.4 6.9 V

ABSOLUTE MAXIMUM RATINGS*

VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +15 V

CS+, CS– . . . . . . . . . . . . . . . . . . . . . . –0.3 V to VCC + 0.3 V

All Other Inputs and Outputs . . . . . . . . . . . . . –0.3 V to +10 V

Operating Ambient Temperature Range . . . . . . . 0°C to 70°C

Operating Junction Temperature . . . . . . . . . . . . . . . . . . 125°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

θ

JA

Two-Layer Board . . . . . . . . . . . . . . . . . . . . . . . . . . 125°C/W

Four-Layer Board . . . . . . . . . . . . . . . . . . . . . . . . . . 81°C/W

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . . 300°C

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

*This is a stress rating only; operation beyond these limits can cause the device to

be permanently damaged. Unless otherwise specified, all voltages are referenced

to GND.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

ADP3162JR 0°C to 70°C Narrow Body SOIC R-16A (SO-16)

PIN CONFIGURATION

VID3

VID2

VID1

VID0

VID25

COMP

FB

CT

1

2

3

4

ADP3162

TOP VIEW

5

(Not to Scale)

6

7

8

16

15

14

13

12

11

10

9

VCC

REF

CS–

PWM1

PWM2

CS+

PWRGD

GND

PIN FUNCTION DESCRIPTIONS

Pin Mnemonic Function

1–4, VID3 –VID0, Voltage Identification DAC Inputs.

5 VID25 These pins are pulled up to an internal

reference, providing a Logic 1 if left open.

The DAC output programs the FB regulation voltage from 1.05 V to 1.825 V.

6 COMP Error Amplifier Output and Compensation

Point. The voltage at this output programs

the output current control level between

CS+ and CS–.

7 FB Feedback Input. Error amplifier input for

remote sensing of the output voltage.

8 CT External capacitor CT connection to ground

sets the frequency of the device.

9 GND Ground. All internal signals of the ADP3162

are referenced to this ground.

10 PWRGD Open drain output that signals when the out-

put voltage is in the proper operating range.

11 CS+ Current Sense Positive Node. Positive input

for the current comparator. The output

current is sensed as a voltage at this pin with

respect to CS–.

12 PWM2 Logic-level output for the Phase 2 driver.

13 PWM1 Logic-level output for the Phase 1 driver.

14 CS– Current Sense Negative Node. Negative

input for the current comparator.

15 REF 3.0 V Reference Output.

16 VCC Supply Voltage for the ADP3162.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the ADP3162 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

ADP3162

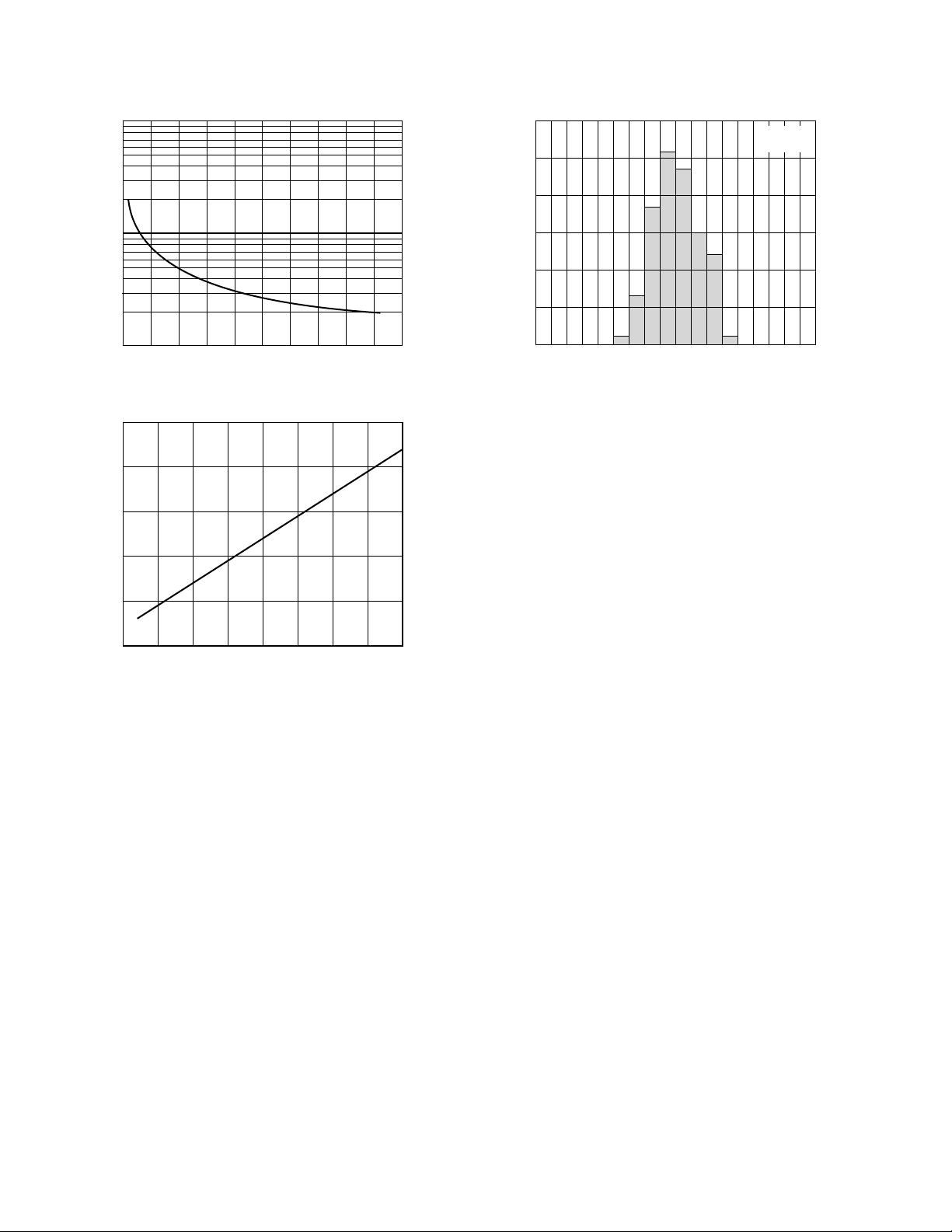

–Typical Performance Characteristics

10000

1000

OSCILLATOR FREQUENCY – kHz

100

0

100

200 300 400 500

CT CAPACITOR – pF

TPC 1. Oscillator Frequency vs. Timing Capacitor

4.10

4.05

4.00

3.95

30

25

20

15

10

NUMBER OF PARTS – %

5

0

–0.5 0.5

OUTPUT ACCURACY – % OF NOMINAL

0

TA = 25⬚C

V

OUT

= 1.6V

TPC 3. Output Accuracy Distribution

SUPPLY CURRENT – mA

3.90

3.85

0 2000

250 500 750 1250 1500 1750

OSCILLATOR FREQUENCY – kHz

1000

TPC 2. Supply Current vs. Oscillator Frequency

–4–

REV. A

Loading...

Loading...